Изобретение относится к вычислительной технике, к устройствам обработки (квантования по времени) электрических случайных сигналов и может быть использовано при регистрации параметров, которые применяются в процессе дальнейшего анализа для восстановления исходной зависимости.

Известен адаптивный временной дискретизатор, содержащий блоки памяти, блоки определения приращений, пороговый элемент, блок выборки-хранения, генератор пилообразного напряжения, ключ, блоки умножения, сумматор, компаратор, счетчик и масштабирующие элементы (Авт. свид. СССР №1275477, кл. G06G 7/02, 1988).

Недостатком этого устройства является низкая точность аппроксимации из-за линейного ее характера.

Наиболее близким аналогом (прототипом) является адаптивный временной дискретизатор, содержащий блок выборки-хранения, генератор пилообразного напряжения, компаратор, запоминающий элемент, пороговый элемент, блоки умножения, масштабирующие элементы, квадраторы, сумматоры, блоки возведения в степень, блоки осреднения, счетчик времени дискретизатора, блок вычитания по модулю, блоки вычитания, элементы задержки, коммутатор и ключ (авт. свид. СССР №1791822, кл. G06G 7/02, 1990).

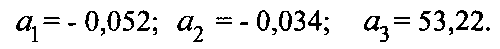

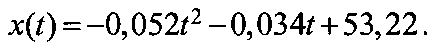

Это устройство позволяет несколько повысить точность аппроксимации путем применения метода аппроксимации кривыми второго порядка. Выражение для аппроксимационной функции x(t) имеет вид:

где - а 1, а 2 и а 3 - коэффициенты аппроксимационной функции, определяемые методом наименьших квадратов по трем предшествующим значениям дискретизируемого сигнала (х(ti), i=0, 1, 2) и трем значениям времени дискретизации сигнала (ti, i=0, 1, 2).

Недостатками этого устройства являются:

- не всегда приемлемая точность аппроксимации;

- сложность устройства (содержит 110 элементов) из-за необходимости реализации метода наименьших квадратов.

Техническим результатом заявленного изобретения является повышение точности аппроксимации и упрощение устройства.

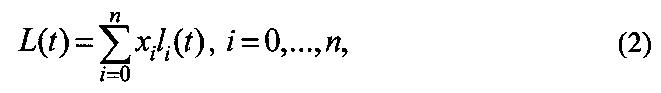

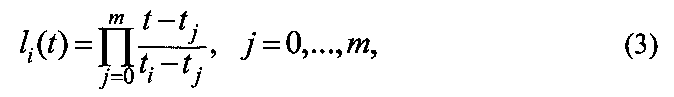

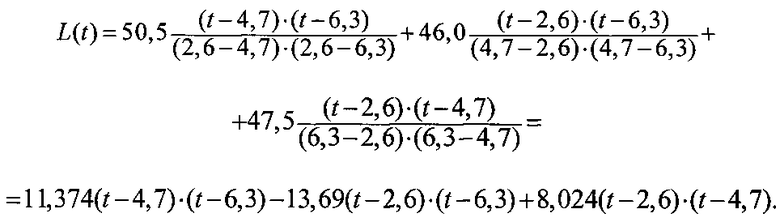

Повышение точности аппроксимации и упрощение устройства можно достичь путем использования полинома Лагранжа L(t), который имеет следующий вид:

где xi - i-e значение, используемое для аппроксимации;

n - количество точек аппроксимации;

m - максимальное значение показателя степени аргумента t.

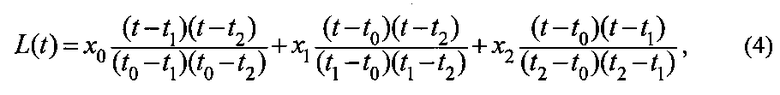

Учитывая формулы (2) и (3) для случая трех точек аппроксимации и m=2, можно записать:

где х0 и t0 - значения функции и аргумента первой точки аппроксимации;

x1 и t1 - значения функции и аргумента второй точки аппроксимации;

х2 и t2 - значения функции и аргумента третьей точки аппроксимации.

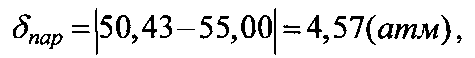

Далее осуществляется количественная оценка качества аппроксимации путем вычисления разности δ между прогнозируемым значением L(tпр) и его реальным значением x(tпр):

Затем сравнивается величина δ с ее допустимым значением  . Если

. Если  , то результат аппроксимации положительный и значение L(tпр) можно фиксировать как рабочее значение дискретизации случайного сигнала и использовать для дальнейших действий.

, то результат аппроксимации положительный и значение L(tпр) можно фиксировать как рабочее значение дискретизации случайного сигнала и использовать для дальнейших действий.

Для наглядной иллюстрации и проверки предложенного подхода необходимо рассмотреть числовой пример.

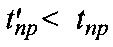

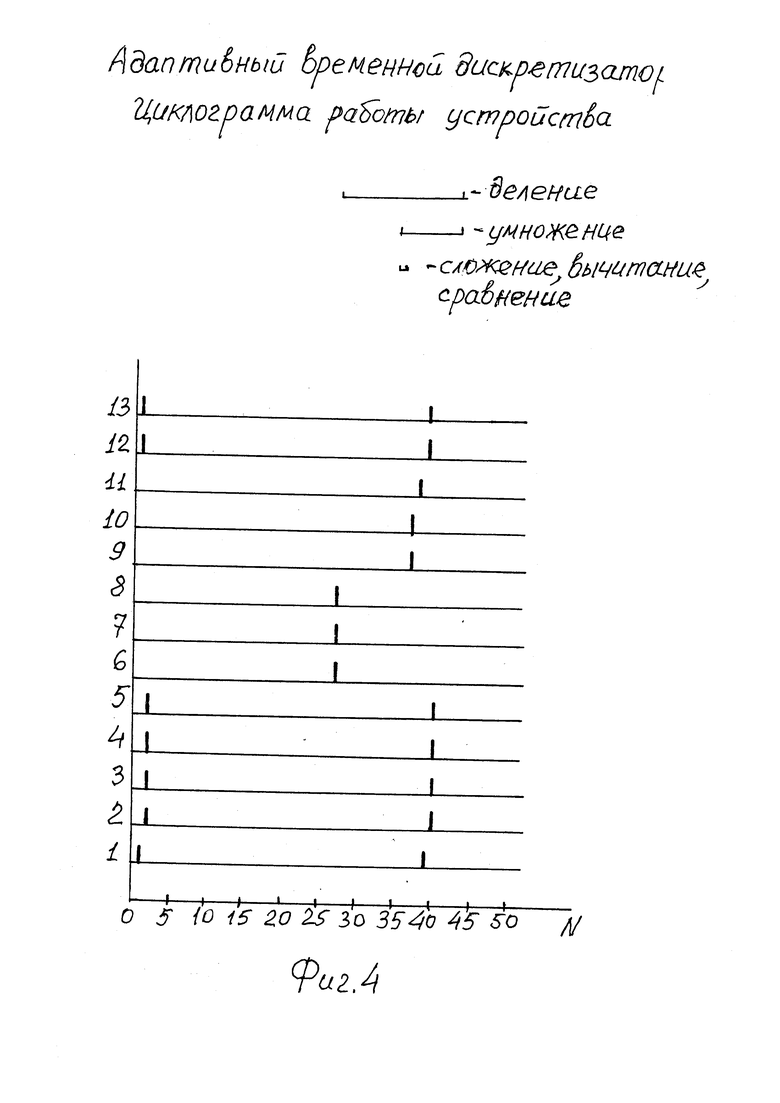

На фиг. 1 представлен случайный сигнал  , характеризующий изменение по времени давления наддува. Анализ этого процесса показывает, что имеют место следующие значения величины ti и xi: t0=2,60 мин, х0=50,5 атм; t1=4,70 мин, x1=46,0 атм; t2=6,30 мин, х2=47,5 атм; tпр=7,0 мин, хпр=55,0 атм.

, характеризующий изменение по времени давления наддува. Анализ этого процесса показывает, что имеют место следующие значения величины ti и xi: t0=2,60 мин, х0=50,5 атм; t1=4,70 мин, x1=46,0 атм; t2=6,30 мин, х2=47,5 атм; tпр=7,0 мин, хпр=55,0 атм.

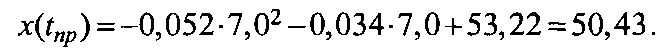

Коэффициенты квадратного трехчлена можно определить с помощью расчетных формул, приведенных в прототипах. Учитывая координаты трех точек, будем иметь:

Тогда используя формулу (1), можно записать:

На основании формулы (5) можно записать выражение для вычисления разности δпар между прогнозируемым значением x(tпр) при аппроксимации параболическим трехчленом и реальным значением случайного сигнала:

что составляет 8,3% от этого реального значения.

Далее необходимо определить погрешность, которую дает аппроксимация с использованием полинома Лагранжа. Подставляя те же исходные данные в формулу (4), получим:

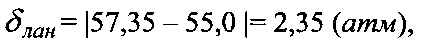

Подставляя в последнее выражение вместо t tпр=0,70, будем иметь L(tпр)=57,35. Используя формулу (5), можно вычислить разность δлан между прогнозируемым значением L(tпр) при аппроксимации полиномом Лагранжа и реальным значением случайного сигнала:

что составляет 4,3% от этого реального значения.

Сравнение величин δлан и δпар показывает, что δлан<δпар. Это подтверждает большую точность при аппроксимации с помощью полинома Лагранжа.

Технический результат достигается тем, адаптивный временной дискретизатор содержит с первого по одиннадцатый входные регистры, выходной регистр, с первого по двенадцатый элементы ИЛИ, с первого по девятый блоки умножения, первый и второй сумматоры, с первого по седьмой коммутаторы, с первого по четвертый элементы задержки (ЭЗ), первый, второй и третий блоки деления, с первого по девятый блоки вычитания, элемент НЕ, блок вычитания по модулю, первый и второй блоки сравнения, первый и второй блоки индикации, генератор тактовых импульсов и распределитель импульсов (РИ), тактовый вход которого соединен с выходом генератора тактовых импульсов, первый выход РИ - со входами записи первого, второго, третьего, пятого, шестого, седьмого, восьмого, десятого и одиннадцатого входных регистров, со второго по девятый выходы - со входами считывания соответственно шестого, седьмого, восьмого, девятого, первого, второго, третьего и четвертого входных регистров, десятый выход - со входом записи выходного регистра, одиннадцатый выход - со входом считывания одиннадцатого входного регистра, двенадцатый и тринадцатый, выходы - со входами записи четвертого и девятого входных регистров, первые входы с первого по восьмой элементов ИЛИ являются входами задания исходной информации, на которые поступают величины  и tпр, характеризующие соответственно значения первой, второй, третьей и прогнозируемой величин дискретизируемого случайного сигнала, первой, второй, третьей и прогнозируемой величин времени, соответствующих этим значениям сигнала, информационные входы десятого, пятого и одиннадцатого входных регистров являются входами задания исходной информации, на которые поступают значения

и tпр, характеризующие соответственно значения первой, второй, третьей и прогнозируемой величин дискретизируемого случайного сигнала, первой, второй, третьей и прогнозируемой величин времени, соответствующих этим значениям сигнала, информационные входы десятого, пятого и одиннадцатого входных регистров являются входами задания исходной информации, на которые поступают значения  и

и  , характеризующие соответственно уменьшенное значение времени прогнозирования дискретизируемого случайного сигнала, величину сигнала, соответствующего этому времени, и допустимое значение разности между его прогнозируемой величиной и реальным значением, выходы с первого по четвертый элементов ИЛИ соединены с информационными входами соответственно с первого по четвертый входных регистров, а вторые входы - с первыми выходами соответственно с первого по четвертый коммутаторов, информационные входы которых подключены к выходам соответственно со второго по пятый входных регистров, а вторые выходы первого и второго коммутаторов - к первым входам соответственно второго и третьего блокам умножения, вторые входы которых соединены с выходами соответственно первого и третьего блоков деления, а выходы - соответственно к первому входу первого сумматора и к входу первого ЭЗ, выход которого соединен с первым входом второго сумматора, выход которого подключен к входу второго ЭЗ и первому входу десятого элемента ИЛИ, а второй вход - к выходу первого сумматора, второй вход которого соединен с выходом первого блока умножения, первый вход которого подключен к выходу первого входного регистра, а второй вход - к выходу второго блока деления, входы делителя и делимого которого соединены с выходами соответственно четвертого и пятого блоков умножения, первые входы которых подключены к выходам соответственно второго и четвертого блоков вычитания, а вторые входы - к выходам соответственно первого и пятого блоков вычитания, выходы пятого, шестого, седьмого и восьмого элементов ИЛИ соединены с информационными входами соответственно шестого, седьмого, восьмого и девятого входных регистров, выходы седьмого, восьмого и девятого входных регистров подключены к информационным входам соответственно пятого, шестого и седьмого коммутаторов, первые выходы которых соединены со вторыми входами соответственно пятого, шестого и седьмого элементов ИЛИ, выход одиннадцатого входного регистра подключен к входу четвертого ЭЗ и к пороговому входу первого блока сравнения, выход которого соединен с входом элемента НЕ, первым входом двенадцатого элемента ИЛИ, с управляющими входами первого, второго, третьего, пятого, шестого и седьмого коммутаторов, а информационный вход - с выходом блока вычитания по модулю, первый и второй входы которого подключены к выходу соответственно девятого и десятого элементов ИЛИ, второй вход последнего из которых подключен к выходу второго ЭЗ, выход элемента НЕ соединен с управляющим входом четвертого коммутатора и входами считывания пятого и десятого входных регистров, выход последнего из которых подключен ко второму входу восьмого элемента ИЛИ, второй выход четвертого коммутатора соединен с третьим входом третьего элемента ИЛИ и с первыми входами девятого и одиннадцатого элементов ИЛИ, вторые входы которых подключены ко второму выходу третьего коммутатора, выход шестого входного регистра соединен с входами уменьшаемого первого и второго блоков вычитания и с входами вычитаемого третьего и шестого блоков вычитания, выходы двух последних из которых подключены к первым входам соответственно восьмого и шестого блоков умножения, второй вход которого соединен с выходом четвертого блока вычитания, а выход - с входом делимого третьего блока деления, вход делителя которого подключен к выходу девятого блока умножения, первый и второй входы которого соединены с выходами соответственно восьмого и девятого блоков вычитания, второй выход пятого коммутатора подключен к выходам вычитаемого первого и четвертого блоков вычитания и к входам уменьшаемого третьего и седьмого блоков вычитания, выход последнего из которых соединен со вторым входом восьмого блока умножения, выход которого подключен к входу делителя первого блока деления, вход делимого которого соединен с выходом седьмого блока умножения, первый и второй входы которого подключены к выходам соответственно пятого и шестого блоков вычитания, второй выход шестого коммутатора соединен с входами вычитаемого второго, пятого и седьмого блоков вычитания и с входами уменьшаемого девятого и восьмого блоков вычитания, вход вычитаемого последнего из которых подключен к выходу шестого входного регистра, второй выход седьмого коммутатора соединен с входами уменьшаемого четвертого, пятого и шестого блоков вычитания и с входом вычитаемого девятого блока вычитания, информационный вход выходного регистра подключен к выходу одиннадцатого элемента ИЛИ, выход - к входу первого блока индикации, а вход считывания - к выходу двенадцатого элемента ИЛИ, второй вход которого соединен с выходом второго блока сравнения, информационный вход которого через третий ЭЗ подключен к выходу блока вычитания по модулю, пороговый вход через четвертый ЭЗ - к выходу одиннадцатого входного регистра, а выход - к входу второго блока индикации.

, характеризующие соответственно уменьшенное значение времени прогнозирования дискретизируемого случайного сигнала, величину сигнала, соответствующего этому времени, и допустимое значение разности между его прогнозируемой величиной и реальным значением, выходы с первого по четвертый элементов ИЛИ соединены с информационными входами соответственно с первого по четвертый входных регистров, а вторые входы - с первыми выходами соответственно с первого по четвертый коммутаторов, информационные входы которых подключены к выходам соответственно со второго по пятый входных регистров, а вторые выходы первого и второго коммутаторов - к первым входам соответственно второго и третьего блокам умножения, вторые входы которых соединены с выходами соответственно первого и третьего блоков деления, а выходы - соответственно к первому входу первого сумматора и к входу первого ЭЗ, выход которого соединен с первым входом второго сумматора, выход которого подключен к входу второго ЭЗ и первому входу десятого элемента ИЛИ, а второй вход - к выходу первого сумматора, второй вход которого соединен с выходом первого блока умножения, первый вход которого подключен к выходу первого входного регистра, а второй вход - к выходу второго блока деления, входы делителя и делимого которого соединены с выходами соответственно четвертого и пятого блоков умножения, первые входы которых подключены к выходам соответственно второго и четвертого блоков вычитания, а вторые входы - к выходам соответственно первого и пятого блоков вычитания, выходы пятого, шестого, седьмого и восьмого элементов ИЛИ соединены с информационными входами соответственно шестого, седьмого, восьмого и девятого входных регистров, выходы седьмого, восьмого и девятого входных регистров подключены к информационным входам соответственно пятого, шестого и седьмого коммутаторов, первые выходы которых соединены со вторыми входами соответственно пятого, шестого и седьмого элементов ИЛИ, выход одиннадцатого входного регистра подключен к входу четвертого ЭЗ и к пороговому входу первого блока сравнения, выход которого соединен с входом элемента НЕ, первым входом двенадцатого элемента ИЛИ, с управляющими входами первого, второго, третьего, пятого, шестого и седьмого коммутаторов, а информационный вход - с выходом блока вычитания по модулю, первый и второй входы которого подключены к выходу соответственно девятого и десятого элементов ИЛИ, второй вход последнего из которых подключен к выходу второго ЭЗ, выход элемента НЕ соединен с управляющим входом четвертого коммутатора и входами считывания пятого и десятого входных регистров, выход последнего из которых подключен ко второму входу восьмого элемента ИЛИ, второй выход четвертого коммутатора соединен с третьим входом третьего элемента ИЛИ и с первыми входами девятого и одиннадцатого элементов ИЛИ, вторые входы которых подключены ко второму выходу третьего коммутатора, выход шестого входного регистра соединен с входами уменьшаемого первого и второго блоков вычитания и с входами вычитаемого третьего и шестого блоков вычитания, выходы двух последних из которых подключены к первым входам соответственно восьмого и шестого блоков умножения, второй вход которого соединен с выходом четвертого блока вычитания, а выход - с входом делимого третьего блока деления, вход делителя которого подключен к выходу девятого блока умножения, первый и второй входы которого соединены с выходами соответственно восьмого и девятого блоков вычитания, второй выход пятого коммутатора подключен к выходам вычитаемого первого и четвертого блоков вычитания и к входам уменьшаемого третьего и седьмого блоков вычитания, выход последнего из которых соединен со вторым входом восьмого блока умножения, выход которого подключен к входу делителя первого блока деления, вход делимого которого соединен с выходом седьмого блока умножения, первый и второй входы которого подключены к выходам соответственно пятого и шестого блоков вычитания, второй выход шестого коммутатора соединен с входами вычитаемого второго, пятого и седьмого блоков вычитания и с входами уменьшаемого девятого и восьмого блоков вычитания, вход вычитаемого последнего из которых подключен к выходу шестого входного регистра, второй выход седьмого коммутатора соединен с входами уменьшаемого четвертого, пятого и шестого блоков вычитания и с входом вычитаемого девятого блока вычитания, информационный вход выходного регистра подключен к выходу одиннадцатого элемента ИЛИ, выход - к входу первого блока индикации, а вход считывания - к выходу двенадцатого элемента ИЛИ, второй вход которого соединен с выходом второго блока сравнения, информационный вход которого через третий ЭЗ подключен к выходу блока вычитания по модулю, пороговый вход через четвертый ЭЗ - к выходу одиннадцатого входного регистра, а выход - к входу второго блока индикации.

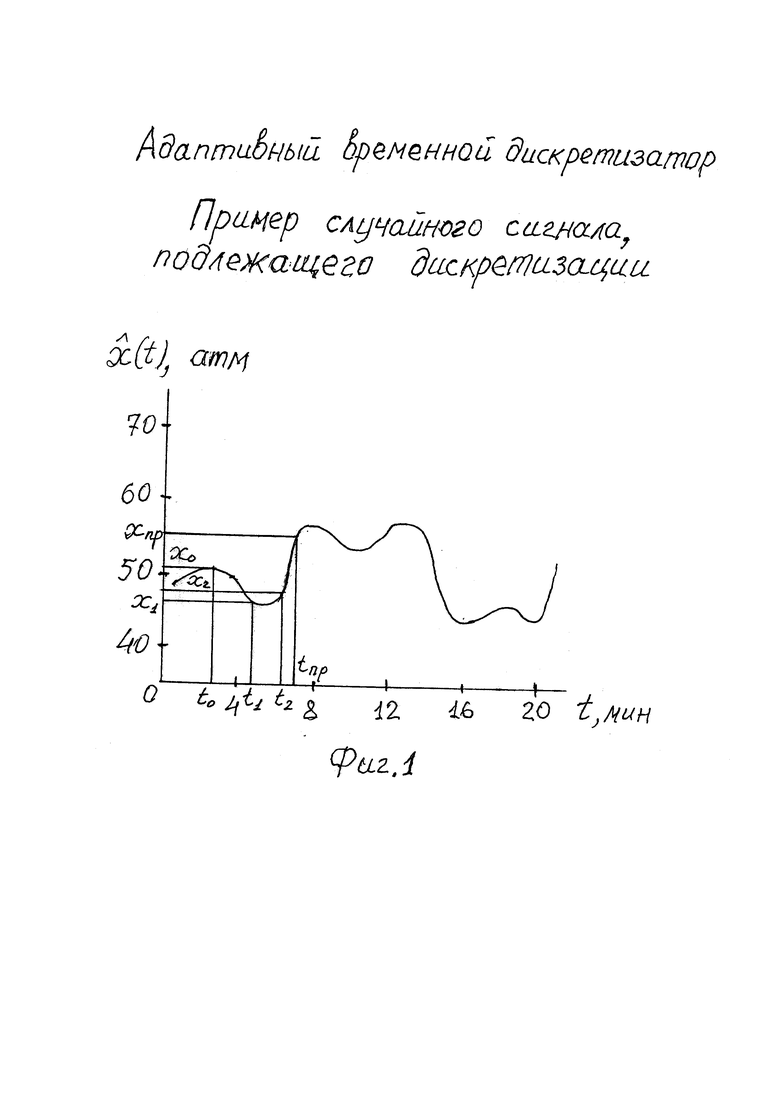

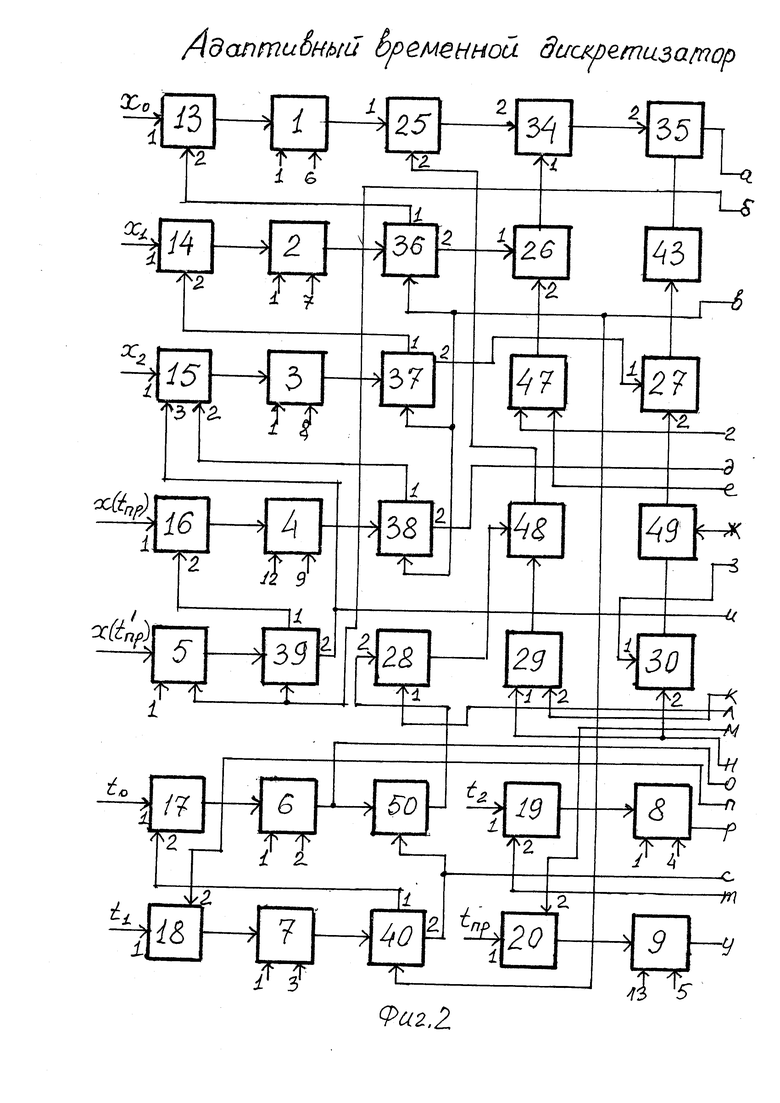

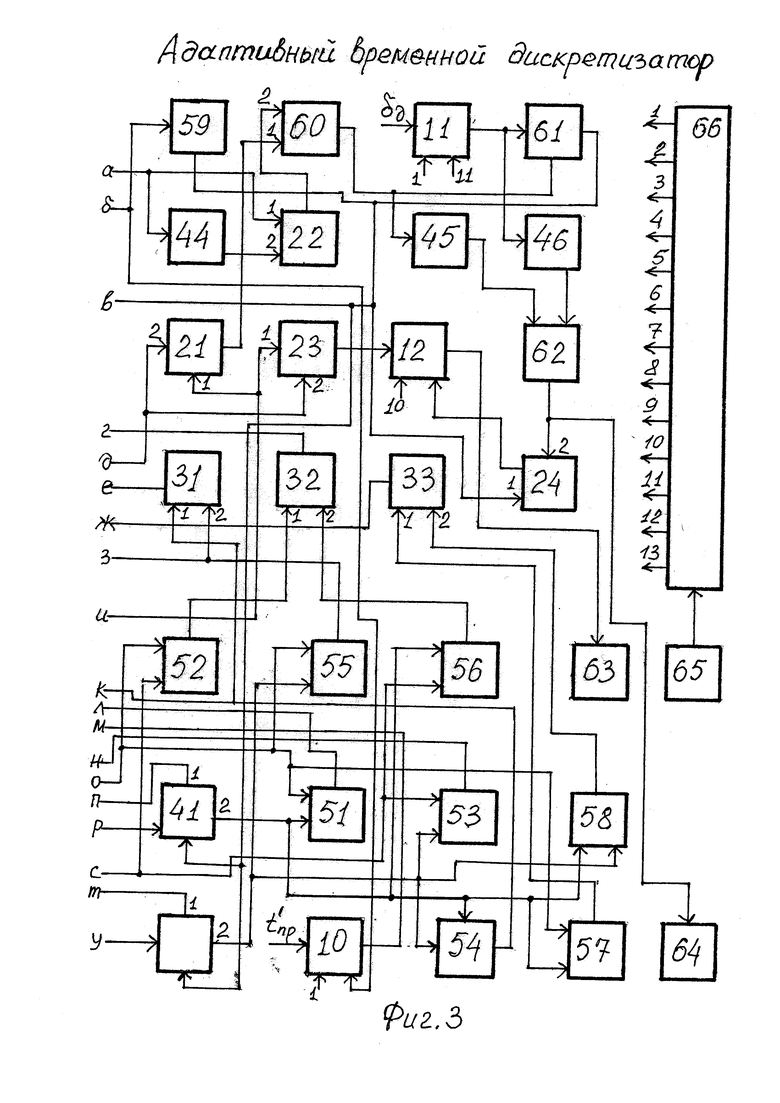

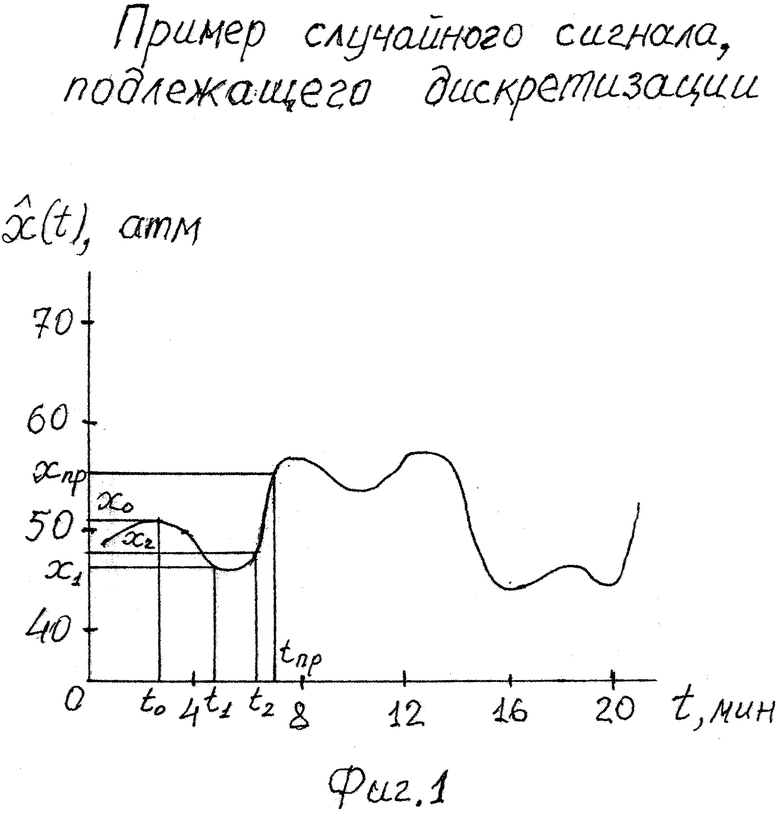

На фиг. 1 представлен случайный сигнал  , характеризующий изменение по времени давления наддува; на фиг. 2 и 3 изображена функциональная схема адаптивного временного дискретизатора (для ликвидации громоздкости связи между РИ и управляющими входами соответствующих блоков показаны не полностью, а обозначены путем нумерации входов и выходов); на фиг. 4 представлена циклограмма работы заявленного устройства (на оси ординат обозначены номера выходов РИ, а на оси абсцисс - число тактов), причем длительность различных вычислительных операций (сложение, вычитание и сравнение - один такт, умножение - восемь тактов, деление - шестнадцать тактов) - в верхней части фиг. 4.

, характеризующий изменение по времени давления наддува; на фиг. 2 и 3 изображена функциональная схема адаптивного временного дискретизатора (для ликвидации громоздкости связи между РИ и управляющими входами соответствующих блоков показаны не полностью, а обозначены путем нумерации входов и выходов); на фиг. 4 представлена циклограмма работы заявленного устройства (на оси ординат обозначены номера выходов РИ, а на оси абсцисс - число тактов), причем длительность различных вычислительных операций (сложение, вычитание и сравнение - один такт, умножение - восемь тактов, деление - шестнадцать тактов) - в верхней части фиг. 4.

Адаптивный временной дискретизатор (фиг. 2 и 3) содержит первый 1, второй 2, третий 3, четвертый 4, пятый 5, шестой 6, седьмой 7, восьмой 8, девятый 9, десятый 10 и одиннадцатый 11 входные регистры, выходной регистр 12, первый 13, второй 14, третий 15, четвертый 16, пятый 17, шестой 18, седьмой 19, восьмой 20, девятый 21, десятый 22, одиннадцатый 23 и двенадцатый 24 элементы ИЛИ, первый 25, второй 26, третий 27, четвертый 28, пятый 29, шестой 30, седьмой 31, восьмой 32 и девятый 33 блоки умножения, первый 34 и второй 35 сумматоры, первый 36, второй 37, третий 38, четвертый 39, пятый 40, шестой 41 и седьмой 42 коммутаторы, первый 43, второй 44, третий 45 и четвертый 46 ЭЗ, первый 47, второй 48 и третий 49 блоки деления, первый 50, второй 51, третий 52, четвертый 53, пятый 54, шестой 55, седьмой 56, восьмой 57 и девятый 58 блоки вычитания, элемент НЕ 59, блок 60 вычитания по модулю, первый 61 и второй 62 блоки сравнения, первый 63 и второй 64 блоки индикации, генератор 65 тактовых импульсов и распределитель 66 импульсов.

Адаптивный временной дискретизатор работает следующим образом (фиг. 2 и 3). На первые входы первого 13, второго 14, третьего 15, четвертого 16, пятого 17, шестого 18, седьмого 19 и восьмого 20 элементов ИЛИ подаются значения  и tпр, характеризующие соответственно значения первой, второй, третьей и прогнозируемой величин дискретизируемого случайного сигнала, первой, второй, третьей и прогнозируемой величин времени, соответствующих этим значениям сигнала. С выходов этих блоков перечисленные значения направляются на информационные входы соответственно первого 1, второго 2, третьего 3, четвертого 4, шестого 6, седьмого 7, восьмого 8 и девятого 9 входных регистров. При этом управляющий сигнал на входы записи этих регистров, кроме четвертого и девятого, подается с первого выхода РИ 66, темп работы которого задается генератором 65 тактовый импульсов. Управляющий сигнал на входы записи четвертого 4 и девятого 9 регистров засылается соответственно с двенадцатого и тринадцатого выходов РИ 66.

и tпр, характеризующие соответственно значения первой, второй, третьей и прогнозируемой величин дискретизируемого случайного сигнала, первой, второй, третьей и прогнозируемой величин времени, соответствующих этим значениям сигнала. С выходов этих блоков перечисленные значения направляются на информационные входы соответственно первого 1, второго 2, третьего 3, четвертого 4, шестого 6, седьмого 7, восьмого 8 и девятого 9 входных регистров. При этом управляющий сигнал на входы записи этих регистров, кроме четвертого и девятого, подается с первого выхода РИ 66, темп работы которого задается генератором 65 тактовый импульсов. Управляющий сигнал на входы записи четвертого 4 и девятого 9 регистров засылается соответственно с двенадцатого и тринадцатого выходов РИ 66.

На информационные входы десятого 10, пятого 5 и одиннадцатого 11 входных регистров направляются величины  ,

,  и

и  , характеризирующие соответственно уменьшенное значение времени прогнозирования дискретизируемого случайного сигнала, величину сигнала, соответствующего этому времени, и допустимое значение разности между его прогнозируемой величиной и реальным значением. При этом управляющий сигнал на входы записи этих регистров подается с первого выхода РИ 66.

, характеризирующие соответственно уменьшенное значение времени прогнозирования дискретизируемого случайного сигнала, величину сигнала, соответствующего этому времени, и допустимое значение разности между его прогнозируемой величиной и реальным значением. При этом управляющий сигнал на входы записи этих регистров подается с первого выхода РИ 66.

По сигналам со второго, третьего, четвертого и пятого выходов РИ 66 на входы считывания соответственно шестого 6, седьмого 7, восьмого 8 и девятого 9 входных регистров величины t0, t1, t2 и tпр засылаются на следующие блоки: t0 - на входы уменьшаемого первого 50 и второго 51 блоков вычитания и на входы вычитаемого третьего 52 и шестого 55 блоков вычитания; t1, t2 и tпр - на информационные входы соответственно пятого 40, шестого 41 и седьмого 42 коммутаторов. Все коммутаторы дискретизатора настроены следующим образом: при наличии управляющего сигнал информация из коммутатора будет исходить из первого выхода, а при его отсутствии - из второго выхода.

Значение t1 со второго выхода пятого коммутатора 40 поступает на входы вычитаемого первого 50 и четвертого 53 блоков вычитания и на входы уменьшаемого третьего 52 и седьмого 56 блоков вычитания. Величина t2 со второго выхода шестого коммутатора 41 подается на входы вычитаемого второго 51, пятого 54 и седьмого 56 блоков вычитания и на входы уменьшаемого восьмого 57 и девятого 58 блоков вычитания. Значение tпр со второго выхода седьмого коммутатора 42 засылается на входы уменьшаемого четвертого 53, пятого 54 и шестого 55 блоков вычитания и на вход вычитаемого девятого блока 58 вычитания. Следует отметить, что блоки с 28-го по 33-й и с 47-го по 58-й позволяют вычислить дробные сомножители первого, второго и третьего слагаемых формулы (4). Дробные сомножители этих слагаемых подаются на вторые входы первого 25, второго 26 и третьего 28 блоков умножения с выходов соответственно второго 48, первого 47 и третьего 49 блоков деления.

По сигналу с шестого выхода РИ 66 на вход считывания первого входного регистра 1 значение х0 направляется на первый вход первого блока 25 умножения, с выхода которого первое слагаемое формулы (4) поступает на второй вход первого сумматора 34. После управляющего сигнала с седьмого выхода РИ 66 на вход считывания второго входного регистра 2 величина х1 засылается на информационный вход первого коммутатора 36, со второго выхода которого это значение подается на первый вход второго блока 26 умножения. С выхода этого блока величина второго слагаемого формулы (4) направляется на первый вход первого сумматора 34, с выхода которого сумма первых двух слагаемых этой формулы поступает на второй вход второго сумматора. По сигналу с восьмого выхода РИ 66 на вход считывания третьего входного регистра 3 значение х2 засылается на информационный вход второго коммутатора 37, со второго выхода которого эта величина подается на первый вход третьего блока 27 умножения. С выхода этого блока значение третьего слагаемого формулы (4) направляется на первый вход второго сумматора 35 через первый ЭЗ для обеспечения одновременности поступления сигналов на входы блока 35, с выхода которого величина L(tпр), определяемая по формуле (4), поступает на вход второго ЭЗ 44 и на первый вход десятого элемента ИЛИ 22. С выхода блока 22 значение L(tпр) засылается на второй вход блока 60 вычитания по модулю.

После управляющего сигнала с девятого выхода РИ 66 на вход считывания четвертого входного регистра 4 величина x(tпр) направляется на информационный вход третьего коммутатора 38, со второго выхода которого это значение подается на вторые входы девятого 21 и одиннадцатого 23 элементов ИЛИ. С выхода блока 21 величина x(tпр) засылается на первый вход блока 60 вычитания по модулю, с выхода которого значение δ, определяемое по формуле (5), поступает на информационный вход первого блока 61 сравнения. С выхода блока 23 величина x(tпp) подается на информационный вход выходного регистра 12, на вход записи которого управляющий сигнал подается с десятого выхода РИ 66.

По сигналу с одиннадцатого выхода РИ 66 на вход считывания одиннадцатого входного регистра 11 значение  направляется на пороговый вход первого блока 61 сравнения и через четвертый ЭЗ 46 - на пороговый вход второго блока 62 сравнения. Блоки 61 и 62 настроены следующим образом. Если

направляется на пороговый вход первого блока 61 сравнения и через четвертый ЭЗ 46 - на пороговый вход второго блока 62 сравнения. Блоки 61 и 62 настроены следующим образом. Если  , то на выходах этих блоков появится управляющий сигнал. В случае когда

, то на выходах этих блоков появится управляющий сигнал. В случае когда  , управляющий сигнала будет отсутствовать. Следовательно, если

, управляющий сигнала будет отсутствовать. Следовательно, если  , то управляющий сигнал с выхода блока 61, проходя через двенадцатый элемент ИЛИ 24, на вход считывания выходного регистра 12 обеспечивает вывод с выхода блока 12 на вход первого блока 63 индикации значения x(tпр), которое можно использовать как опорное значение при адаптивной дискретизации. Кроме того, сигнал с выхода первого блока 61 сравнения будет воздействовать на управляющие входы первого 36, второго 37, третьего 38, пятого 40, шестого 41 и седьмого 42 коммутаторов. Это позволит выводить информацию с первых выходов этих коммутаторов, что обеспечит сдвиг опорных точек для дальнейшей работы: x1 будет играть роль x0, х2 будет выполнять функцию x1, x(tпр) заменит х2, а вместо x(tпр) будет введено новое значение. Такая же процедура произойдет и с величинами t1, t2 и tпр. В дальнейшем работа дискретизатора будет осуществляться по уже описанной схеме.

, то управляющий сигнал с выхода блока 61, проходя через двенадцатый элемент ИЛИ 24, на вход считывания выходного регистра 12 обеспечивает вывод с выхода блока 12 на вход первого блока 63 индикации значения x(tпр), которое можно использовать как опорное значение при адаптивной дискретизации. Кроме того, сигнал с выхода первого блока 61 сравнения будет воздействовать на управляющие входы первого 36, второго 37, третьего 38, пятого 40, шестого 41 и седьмого 42 коммутаторов. Это позволит выводить информацию с первых выходов этих коммутаторов, что обеспечит сдвиг опорных точек для дальнейшей работы: x1 будет играть роль x0, х2 будет выполнять функцию x1, x(tпр) заменит х2, а вместо x(tпр) будет введено новое значение. Такая же процедура произойдет и с величинами t1, t2 и tпр. В дальнейшем работа дискретизатора будет осуществляться по уже описанной схеме.

Если  , то отсутствие управляющего сигнала на выходе первого блока 61 управления приведет к наличию управляющего сигнала на выходе элемента НЕ 59, что обеспечит считывание из пятого 5 и десятого 10 входных регистров значение

, то отсутствие управляющего сигнала на выходе первого блока 61 управления приведет к наличию управляющего сигнала на выходе элемента НЕ 59, что обеспечит считывание из пятого 5 и десятого 10 входных регистров значение  и

и  . Причем следует иметь ввиду, что

. Причем следует иметь ввиду, что  . В дальнейшем эти величины будут фигурировать вместо x(tпр) и tпр и все расчеты будут проведены по уже описанной схеме. В случае когда в этом варианте работы дискретизатора

. В дальнейшем эти величины будут фигурировать вместо x(tпр) и tпр и все расчеты будут проведены по уже описанной схеме. В случае когда в этом варианте работы дискретизатора  , на выходе второго блока 62 управления появится управляющий сигнал, который обеспечит появление в первом блоке 63 индикации значения

, на выходе второго блока 62 управления появится управляющий сигнал, который обеспечит появление в первом блоке 63 индикации значения  и загорание зеленой лампочки во втором блоке 64 индикации. Это будет свидетельствовать об успешном завершении этапа адаптивной дискретизации. Если в этом варианте работы

и загорание зеленой лампочки во втором блоке 64 индикации. Это будет свидетельствовать об успешном завершении этапа адаптивной дискретизации. Если в этом варианте работы  , то на выходе блока 62 управляющий сигнал будет отсутствовать, информация в первый блок 63 поступать не будет и во втором блоке 64 индикации загорится красная лампочка, что будет говорить о необходимости пересчета, изменения исходных данных, например уменьшения значения tпр, то есть сокращения интервала дискретизации. Порядок функционирования блоков дискретизатора представлен на циклограмме его работы (фиг. 4).

, то на выходе блока 62 управляющий сигнал будет отсутствовать, информация в первый блок 63 поступать не будет и во втором блоке 64 индикации загорится красная лампочка, что будет говорить о необходимости пересчета, изменения исходных данных, например уменьшения значения tпр, то есть сокращения интервала дискретизации. Порядок функционирования блоков дискретизатора представлен на циклограмме его работы (фиг. 4).

Таким образом, технический результат достигается не за счет математического аппарата, а за счет технических средств (блоков и элементов), упомянутых в процессе описания работы устройства, осуществляющего повышение точности аппроксимации и упрощение устройства.

Промышленная применимость изобретения обосновывается тем, что оно может быть использовано в разных областях (отраслях) при дискретизации случайных сигналов, когда необходимо сокращение объема измерительной информации.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ ФУНКЦИИ РАСПРЕДЕЛЕНИЯ СЛУЧАЙНЫХ ВЕЛИЧИН И ЕЕ ТОЛЕРАНТНЫХ ГРАНИЦ ПО МАЛЫМ ВЫБОРКАМ | 2014 |

|

RU2553120C1 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ ЭФФЕКТИВНОСТИ | 2006 |

|

RU2306598C1 |

| Адаптивный временной дискретизатор | 1990 |

|

SU1791822A1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОЙ ОЦЕНКИ ФАЗОВОЙ НАПРЯЖЕННОСТИ РЕСПОНДЕНТА | 2012 |

|

RU2492520C1 |

| УСТРОЙСТВО ДЛЯ ТЕХНИКО-ЭКОНОМИЧЕСКОЙ ОЦЕНКИ ВЫПОЛНЕНИЯ НАУЧНО-ИССЛЕДОВАТЕЛЬСКИХ И ОПЫТНО-КОНСТРУКТОРСКИХ РАБОТ | 2011 |

|

RU2470365C1 |

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ЗАДАЧ НЕЛИНЕЙНОГО СТОХАСТИЧЕСКОГО ПРОГРАММИРОВАНИЯ | 1991 |

|

RU2006933C1 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ ВЫПОЛНЕНИЯ НАУЧНО-ИССЛЕДОВАТЕЛЬСКИХ И ОПЫТНО-КОНСТРУКТОРСКИХ РАБОТ | 2009 |

|

RU2410750C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ФУНКЦИЙ ЦЕННОСТИ ЕДИНИЧНЫХ ОЦЕНОЧНЫХ ПОКАЗАТЕЛЕЙ СЛОЖНЫХ ТЕХНИЧЕСКИХ СИСТЕМ | 2010 |

|

RU2445687C1 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ ЭФФЕКТИВНОСТИ | 2001 |

|

RU2178201C1 |

| Устройство для контроля параметров | 1990 |

|

SU1728869A1 |

Изобретение относится к вычислительной технике, к устройствам обработки (квантования по времени) электрических случайных сигналов и может быть использовано при регистрации параметров, которые применяются в процессе дальнейшего анализа для восстановления исходной зависимости. Техническим результатом является повышение точности и упрощение устройства. Это устройство содержит входные регистры, выходной регистр, элементы ИЛИ, блоки умножения, сумматоры, коммутаторы, элементы задержки, блоки деления, блоки вычитания, элемент НЕ, блок вычитания по модулю, блоки сравнения, блоки индикации, генератор тактовых импульсов и распределитель импульсов. 4 ил.

Адаптивный временной дискретизатор, содержащий с первого по одиннадцатый входные регистры, выходной регистр, с первого по двенадцатый элементы ИЛИ, с первого по девятый блоки умножения, первый и второй сумматоры, с первого по седьмой коммутаторы, с первого по четвертый элементы задержки (ЭЗ), первый, второй и третий блоки деления, с первого по девятый блоки вычитания, элемент НЕ, блок вычитания по модулю, первый и второй блоки сравнения, первый и второй блоки индикации, генератор тактовых импульсов и распределитель импульсов (РИ), тактовый вход которого соединен с выходом генератора тактовых импульсов, первый выход РИ - со входами записи первого, второго, третьего, пятого, шестого, седьмого, восьмого, десятого и одиннадцатого входных регистров, со второго по девятый выходы - со входами считывания соответственно шестого, седьмого, восьмого, девятого, первого, второго, третьего и четвертого входных регистров, десятый выход - со входом записи выходного регистра, одиннадцатый выход - со входом считывания одиннадцатого входного регистра, двенадцатый и тринадцатый выходы - со входами записи четвертого и девятого входных регистров, первые входы с первого по восьмой элементов ИЛИ являются входами задания исходной информации, на которые поступают величины x0,x1,x2,x(tпр),t0,t1,t2 и tпр, характеризующие соответственно значения первой, второй, третьей и прогнозируемой величин дискретизируемого случайного сигнала, первой, второй, третьей и прогнозируемой величин времени, соответствующих этим значениям сигнала, информационные входы десятого, пятого и одиннадцатого входных регистров являются входами задания исходной информации, на которые поступают значения tпр, x(tпр) и δд, характеризующие соответственно уменьшенное значение времени прогнозирования дискретизируемого случайного сигнала, величину сигнала, соответствующего этому времени, и допустимое значение разности между его прогнозируемой величиной и реальным значением, выходы с первого по четвертый элементов ИЛИ соединены с информационными входами соответственно с первого по четвертый входных регистров, а вторые входы - с первыми выходами соответственно с первого по четвертый коммутаторов, информационные входы которых подключены к выходам соответственно со второго по пятый входных регистров, а вторые выходы первого и второго коммутаторов - к первым входам соответственно второго и третьего блокам умножения, вторые входы которых соединены с выходами соответственно первого и третьего блоков деления, а выходы - соответственно к первому входу первого сумматора и к входу первого ЭЗ, выход которого соединен с первым входом второго сумматора, выход которого подключен к входу второго ЭЗ и первому входу десятого элемента ИЛИ, а второй вход - к выходу первого сумматора, второй вход которого соединен с выходом первого блока умножения, первый вход которого подключен к выходу первого входного регистра, а второй вход - к выходу второго блока деления, входы делителя и делимого которого соединены с выходами соответственно четвертого и пятого блоков умножения, первые входы которых подключены к выходам соответственно второго и четвертого блоков вычитания, а вторые входы - к выходам соответственно первого и пятого блоков вычитания, выходы пятого, шестого, седьмого и восьмого элементов ИЛИ соединены с информационными входами соответственно шестого, седьмого, восьмого и девятого входных регистров, выходы седьмого, восьмого и девятого входных регистров подключены к информационным входам соответственно пятого, шестого и седьмого коммутаторов, первые выходы которых соединены со вторыми входами соответственно пятого, шестого и седьмого элементов ИЛИ, выход одиннадцатого входного регистра подключен к входу четвертого ЭЗ и к пороговому входу первого блока сравнения, выход которого соединен с входом элемента НЕ, первым входом двенадцатого элемента ИЛИ, с управляющими входами первого, второго, третьего, пятого, шестого и седьмого коммутаторов, а информационный вход - с выходом блока вычитания по модулю, первый и второй входы которого подключены к выходу соответственно девятого и десятого элементов ИЛИ, второй вход последнего из которых подключен к выходу второго ЭЗ, выход элемента НЕ соединен с управляющим входом четвертого коммутатора и входами считывания пятого и десятого входных регистров, выход последнего из которых подключен ко второму входу восьмого элемента ИЛИ, второй выход четвертого коммутатора соединен с третьим входом третьего элемента ИЛИ и с первыми входами девятого и одиннадцатого элементов ИЛИ, вторые входы которых подключены ко второму выходу третьего коммутатора, выход шестого входного регистра соединен с входами уменьшаемого первого и второго блоков вычитания и с входами вычитаемого третьего и шестого блоков вычитания, выходы двух последних из которых подключены к первым входам соответственно восьмого и шестого блоков умножения, второй вход которого соединен с выходом четвертого блока вычитания, а выход - с входом делимого третьего блока деления, вход делителя которого подключен к выходу девятого блока умножения, первый и второй входы которого соединены с выходами соответственно восьмого и девятого блоков вычитания, второй выход пятого коммутатора подключен к выходам вычитаемого первого и четвертого блоков вычитания и к входам уменьшаемого третьего и седьмого блоков вычитания, выход последнего из которых соединен со вторым входом восьмого блока умножения, выход которого подключен к входу делителя первого блока деления, вход делимого которого соединен с выходом седьмого блока умножения, первый и второй входы которого подключены к выходам соответственно пятого и шестого блоков вычитания, второй выход шестого коммутатора соединен с входами вычитаемого второго, пятого и седьмого блоков вычитания и с входами уменьшаемого девятого и восьмого блоков вычитания, вход вычитаемого последнего из которых подключен к выходу шестого входного регистра, второй выход седьмого коммутатора соединен с входами уменьшаемого четвертого, пятого и шестого блоков вычитания и с входом вычитаемого девятого блока вычитания, информационный вход выходного регистра подключен к выходу одиннадцатого элемента ИЛИ, выход - к входу первого блока индикации, а вход считывания - к выходу двенадцатого элемента ИЛИ, второй вход которого соединен с выходом второго блока сравнения, информационный вход которого через третий ЭЗ подключен к выходу блока вычитания по модулю, пороговый вход через четвертый ЭЗ - к выходу одиннадцатого входного регистра, а выход - к входу второго блока индикации.

| Адаптивный временной дискретизатор | 1990 |

|

SU1791822A1 |

| Адаптивный временной дискретизатор | 1988 |

|

SU1645971A1 |

| Адаптивный временной дискретизатор | 1987 |

|

SU1522242A1 |

| Адаптивный временной дискретизатор | 1985 |

|

SU1275477A1 |

Авторы

Даты

2016-05-10—Публикация

2015-02-12—Подача