Изобретение относится к локационным устройствам и может использоваться в системах обнаружения квазидетерминированных сигналов.

Известен оптимальный адаптивный обнаружитель сигналов, который содержит генератор сигнала, перемножитель, первый и второй квадраторы, первый и второй интеграторы, вычитатель, делитель, реле, при этом вход обнаружителя соединен с входом первого квадратора и первым входом перемножителя, второй вход которого соединен с выходом генератора сигнала, а выход соединен с входом первого интегратора, выход которого соединен с входом квадратора, выход первого квадратора соединен с входом второго интегратора, выход которого соединен с первыми входами делителя и вычитателя, второй вход вычитателя соединен с выходом второго квадратора, а выход вычитателя соединен с вторым входом делителя, выход которого соединен с входом реле, выход которого является выходом обнаружителя [Репин В.Г. и Тартаковский Г.П. Статистический синтез при априорной неопределенности и адаптация информационных систем. М.: Сов. радио, 1911, с.284, рис.12.7].

Недостатком этого обнаружителя является то. что он является оптимальным в условиях обнаружения квазидетерминированных сигналов с неизвестной амплитудой в шуме с неизвестной интенсивностью. Однако в условиях наличия мешающих детерминированных протяженных сигналов условия оптимальности данного обнаружителя нарушаются, теряется качество обнаружения, не обеспечивается стабилизация уровня ложных тревог.

Наиболее близким по технической сущности и достигаемому положительному эффекту к предлагаемому обнаружителю является цифровой адаптивный обнаружитель квазидетерминированных сигналов, содержащий первый квадратор, выход которого соединен с входом первой цифровой линии задержки с N выходами, а вход является входом обнаружителя и соединен с входом второй цифровой линии задержки с N выходами, выходы которой соединены с первой группой N входов N-входового перемножителя, вторая группа N входов которого соединена с группой N выходов цифрового запоминающего устройства, N выходов N-входового перемножителя соединены с N входами первого N-входового сумматора, N выходов первой цифровой линии задержки соединены с N входами второго N-входового сумматора, вход третьей цифровой линии задержки объединен с входом обнаружителя, а N выходов соединены с N входами третьего N-входового сумматора, выход которого соединен с входом второго квадратора, выход которого соединен с первым входом первого делителя, второй вход которого соединен с (N+4)-м выходом цифрового запоминающего устройства, а выход соединен с вторым входом первого вычитателя и первым входом сумматора, первый вход первого вычитателя соединен с выходом второго N-входового сумматора и вторым входом второго вычитателя, (N+1)-й выход цифрового запоминающего устройства соединен с вторым входом второго делителя, первый вход которого соединен с выходом первого N-входового сумматора и первым входом второго перемножителя, второй вход которого соединен с выходом второго делителя и входом третьего квадратора, выход которого соединен с первыми входами первого и третьего перемножителей, вторые входы которых соответственно соединены с (N+2)-м и (N+3)-м выходами цифрового запоминающего устройства, выход первого перемножителя соединен с вторым входом третьего вычитателя, первый вход которого соединен с выходом второго перемножителя, выход третьего вычитателя соединен с вторым входом сумматора, выход которого соединен с первым входом четвертого вычитателя, второй вход которого соединен с выходом третьего делителя, первый вход которого соединен с выходом третьего перемножителя, а второй вход соединен с (N+4)-м выходом цифрового запоминающего устройства, выход четвертого вычитателя соединен с вторым входом четвертого делителя, первый вход которого соединен с выходом первого вычитателя, а выход соединен с входом порогового устройства, выход которого является выходом обнаружителя [Патент РФ №2048681 от 20.11.1995 г. «Цифровой адаптивный обнаружитель» Межлумов Г.М.].

Недостатком данного обнаружителя является то, что в нем не учитываются фазочастотные составляющие сигналов, что может быть полезным для селекции сигналов и определения скоростных характеристик объектов. Также в данном обнаружителе априорно полагается Гауссовская функция правдоподобия при альтернативных гипотезах. В случае если это условие не выполняется, может не обеспечиваться стабилизация уровня ложных тревог и падает качество характеристик обнаружения.

Таким образом, основными недостатками прототипа являются: отсутствие учета фазочастотных составляющих сигналов и недостаточная устойчивость характеристик обнаружителя в изменяющихся условиях наблюдения.

Задачей изобретения является реализация обнаружения квазидетерминированных сигналов с учетом их фазочастотных характеристик и в условиях неизвестной плотности вероятности принимаемых отсчетов с обеспечением стабилизации уровня ложных тревог.

Поставленная задача достигается тем, что в цифровой адаптивный обнаружитель квазидетерминированных сигналов, содержащий первую, вторую, цифровые линии задержки с N выходами, N-входовой перемножитель, запоминающее устройство, N входовой сумматор, делитель, пороговое устройство, при этом, вход обнаружителя соединен с входом первой цифровой линии задержки с N выходами, выходы которой соединены с первой группой N входов N-входового перемножителя, вторая группа N входов которого соединена с группой N выходов цифрового запоминающего устройства, выход делителя соединен с входом порогового устройства, выход которого является выходом обнаружителя, дополнительно введен второй вход обнаружителя, образующий совместно с первым входом обнаружителя первый фазочастотный канал и параллельно введено K-1 таких же фазочастотных каналов, а в каждом фазочастотном канале дополнительно введены второй N-входовой перемножитель, (N+1)-входовой перемножитель, первый и второй 2N-входовой сумматор, первый и второй (N+1)-входовой сумматор, первый и второй N-входовой вычитатель, при этом, N выходов цифрового запоминающего устройства соединены с N входами (N+1)-входового перемножителя, N+1 вход которого соединен с N+1 выходом цифрового запоминающего устройства, второй вход обнаружителя соединен с входом второй цифровой линии задержки с N выходами, выходы которой соединены с первыми N входами второго N-входового перемножителя, вторые N входов которого соединены с N выходами (N+1)-входового перемножителя, N выходов N-входового перемножителя соединены с первыми N входами первого 2N-входного сумматора и второго 2N-входового сумматора, а также с вычитающими N входами N-входового вычитателя, N выходов второго N-входового перемножителя соединены с вторыми N входами первого 2N-входового сумматора и второго 2N-входового сумматора, а также с вторыми N входами N-входового вычитателя, N выходов которого соединены с N входами N-входового сумматора и N входами второго N-входового квадратора, N выходов которого соединены с N входами второго (N+1)-входового сумматора, N+1 вход которого соединен с выходом N-входового сумматора, а выход второго (N+1) входового сумматора соединен с вторым входом делителя, первый вход которого соединен с выходом первого (N+1)-входового сумматора, N+1 вход которого соединен с выходом первого 2N-входового сумматора, а N входов соединены с N выходами первого N-входового квадратора, N входов которого соединены с N выходами второго 2N-входового сумматора.

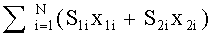

На чертеже представлена структурная схема предлагаемого цифрового адаптивного обнаружителя.

Цифровой адаптивный обнаружитель содержит первую 1, вторую 2 цифровые линии задержки с N выходами, N-входовой перемножитель 3, запоминающее устройство 4, N-входовой сумматор 5, делитель 6, пороговое устройство 7, второй 8 N-входовой перемножитель, (N+1)-входовой перемножитель 9, первый 10, второй 11 2N-входовой сумматор, первый 12, второй 13 (N+1)-входовой сумматор, первый 14, второй 15 N-входовой квадратор, N-входовой вычитатель 16.

Цифровой адаптивный обнаружитель работает следующим образом.

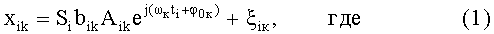

На вход обнаружителя поступают цифровые отсчеты принимаемой реализации:

S - огибающая полезного сигнала, определяемая диаграммой направленности антенны и параметрами способа обзора пространства;

bik - флуктуационный множитель амплитуды полезного сигнала;

Aik постоянная детерминированная амплитуда полезного сигнала в к-ом фильтровом канале;

ωк - частота к - го фильтрового канала; ср0к - начальная фаза;

ti- i-й временной отсчет; ξiк - i-й помеховый отсчет.

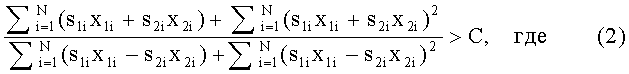

Так как отсчеты xik являются комплексными, то обработка осуществляется на основе квадратурных каналов. При этом на первый вход обнаружителя поступают принимаемые отсчеты первого пространственного канала, а на второй вход соответственно принимаемые отсчеты второго пространственного канала. Обработка осуществляется в К параллельных фильтровых фазочастотных каналах, каждый из которых соответствует определенному фазовому набегу Δφ=Δtiωк. В каждом фильтровом канале реализуется следующий алгоритм обработки:

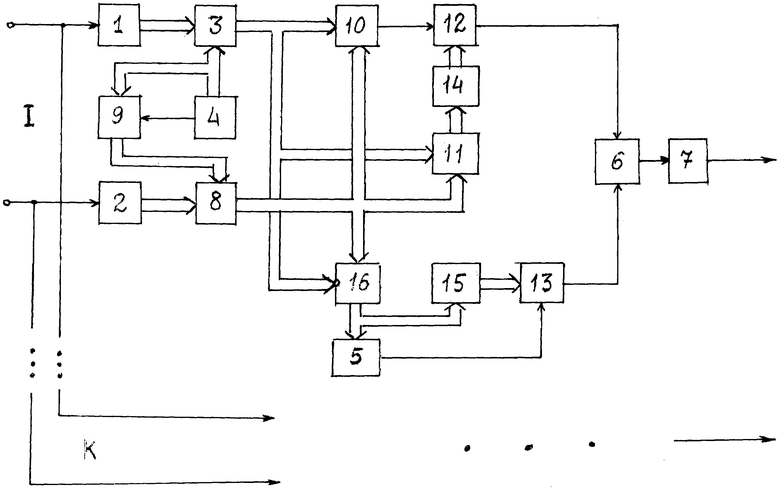

x1i - принимаемые отсчеты первого пространственного канала; x2i - принимаемые отсчеты второго пространственного канала; C - постоянный порог принятия решения. В числителе находится сумма оценок первого и второго начальных моментов суперпозиции первого и второго пространственных каналов при гипотезе наличия сигнала. В знаменателе находится сумма оценок первого и второго начальных моментов суперпозиции первого и второго пространственных каналов при гипотезе отсутствия сигнала. Оценки находятся в текущем временном «окне» размера N определяемом  . В каждом фильтровом канале цифровые отсчеты входной реализации первого и второго пространственных каналов поступают соответственно на первую 1 и вторую 2 цифровые линии задержки с N выходами. На N выходах этих линий задержки формируется текущее временное «окно», определяемое параметрами диаграмм направленности пространственных каналов, параметрами способа обзора пространства и параметрами временной дискретизации входной реализации. В N-входовом перемножителе 3 осуществляется перемножение выборки отсчетов текущего временного «окна» на весовые коэффициенты, соответствующие нормированной огибающей полезного сигнала, с соответствующим фазовым доворотом каждого временного отсчета «окна» на величину, определяемую конкретным фазочастотным каналом. В N+1-входовом перемножителе 9 осуществляется фазовый доворот весовой выборки текущего «окна» на величину, определяемую относительным запаздыванием второго пространственного канала к первому пространственному каналу исходя из реализованной организации обзора пространства, с соответствующим временным разнесением пространственных каналов (диаграмм направленности) то есть

. В каждом фильтровом канале цифровые отсчеты входной реализации первого и второго пространственных каналов поступают соответственно на первую 1 и вторую 2 цифровые линии задержки с N выходами. На N выходах этих линий задержки формируется текущее временное «окно», определяемое параметрами диаграмм направленности пространственных каналов, параметрами способа обзора пространства и параметрами временной дискретизации входной реализации. В N-входовом перемножителе 3 осуществляется перемножение выборки отсчетов текущего временного «окна» на весовые коэффициенты, соответствующие нормированной огибающей полезного сигнала, с соответствующим фазовым доворотом каждого временного отсчета «окна» на величину, определяемую конкретным фазочастотным каналом. В N+1-входовом перемножителе 9 осуществляется фазовый доворот весовой выборки текущего «окна» на величину, определяемую относительным запаздыванием второго пространственного канала к первому пространственному каналу исходя из реализованной организации обзора пространства, с соответствующим временным разнесением пространственных каналов (диаграмм направленности) то есть

а на выходе второго 13 N+1-входового сумматора сформирован отсчет соответствующий операции:

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ АДАПТИВНЫЙ ОБНАРУЖИТЕЛЬ | 1993 |

|

RU2048681C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПОЛУЧЕНИЯ ЭНЕРГИИ | 2012 |

|

RU2493430C1 |

| СПОСОБ И УСТРОЙСТВО ПРОГНОЗА ВОЗМОЖНОСТИ ВОЗНИКНОВЕНИЯ ЦУНАМИ И ОПРЕДЕЛЕНИЯ ЕГО ЭПИЦЕНТРА | 2010 |

|

RU2473930C2 |

| СПОСОБ И УСТРОЙСТВО ПОЛУЧЕНИЯ ЭЛЕКТРОЭНЕРГИИ | 2011 |

|

RU2473816C1 |

| СПОСОБ И УСТРОЙСТВО ПОЛУЧЕНИЯ ЭЛЕКТРОЭНЕРГИИ | 2010 |

|

RU2446362C2 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПОЛУЧЕНИЯ ЭНЕРГИИ | 2010 |

|

RU2435071C1 |

| ОБНАРУЖИТЕЛЬ СИГНАЛОВ | 1991 |

|

RU2106652C1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ ШУМОВЫХ ГИДРОАКУСТИЧЕСКИХ СИГНАЛОВ НА ОСНОВЕ КВАДРАТУРНОГО ПРИЕМНИКА | 2013 |

|

RU2549207C2 |

| ЦИФРОВОЙ ОБНАРУЖИТЕЛЬ ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ | 2018 |

|

RU2693930C1 |

| Цифровое устройство селекции движущихся целей | 1984 |

|

SU1841294A1 |

Изобретение направлено на обнаружение квазидетерминированных гармоничных сигналов с неизвестными параметрами и известной огибающей на фоне шумов с неизвестной функцией распределения. Обнаружитель является адаптивным, обеспечивает стабилизацию уровня ложных тревог и учитывает фазочастотные характеристики принимаемых реализаций, что и является достигаемым техническим результатом. Количество оцениваемых параметров сведено к минимуму, что позволяет работать в условиях небольших интервалов пространственно-временной однородности. 1 ил.

Цифровой адаптивный обнаружитель квазидетерминированных сигналов, содержащий первую, вторую цифровые линии задержки с N выходами, N-входовой перемножитель, запоминающее устройство, N-входовой сумматор, делитель, пороговое устройство, при этом вход обнаружителя соединен с входом первой цифровой линии задержки с N выходами, выходы которой соединены с первой группой N входов N-входового перемножителя, вторая группа N входов которого соединена с группой N выходов цифрового запоминающего устройства, выход делителя соединен с входом порогового устройства, выход которого является выходом обнаружителя, отличающийся тем, что введен второй вход обнаружителя, образующий совместно с первым входом обнаружителя первый фазочастотный канал и параллельно введено K-1 таких же фазочастотных каналов, а в каждом фазочастотном канале дополнительно введены второй N-входовой перемножитель, (N+1)-входовой перемножитель, первый и второй 2N-входовой сумматор, первый и второй (N+1)-входовой сумматор, первый и второй N-входовой вычитатель, при этом N выходов цифрового запоминающего устройства соединены с N входами (N+1)-входового перемножителя, N+1 вход которого соединен с N+1 выходом цифрового запоминающего устройства, второй вход обнаружителя соединен с входом второй цифровой линии задержки с N выходами, выходы которой соединены с первыми N входами второго N-входового перемножителя, вторые N входов которого соединены с N выходами (N+1)-входового перемножителя, N выходов N-входового перемножителя соединены с первыми N входами первого 2N-входового сумматора и второго 2N-входового сумматора, а также с вычитающими N входами N-входового вычитателя, N выходов второго N-входового перемножителя соединены с вторыми N входами первого 2N-входового сумматора и второго 2N-входового сумматора, а также с вторыми N входами N-входового вычитателя, N выходов которого соединены с N входами N-входового сумматора и N входами второго N-входового квадратора, N выходов которого соединены с N входами второго (N+1)-входового сумматора, N+1 вход которого соединен с выходом N-входового сумматора, а выход второго (N+1)-входового сумматора соединен с вторым входом делителя, первый вход которого соединен с выходом первого (N+1)-входового сумматора, N+1 вход которого соединен с выходом первого 2N-входового сумматора, а N входов соединены с N выходами первого N-входового квадратора, N входов которого соединены с N выходами второго 2N-входового сумматора.

| ЦИФРОВОЙ АДАПТИВНЫЙ ОБНАРУЖИТЕЛЬ | 1993 |

|

RU2048681C1 |

| ОБНАРУЖИТЕЛЬ СИГНАЛОВ | 1998 |

|

RU2173468C2 |

| RU 93002638 A, 20.04.1996 | |||

| СЛЕДЯЩИЙ ИЗМЕРИТЕЛЬ С ОБНАРУЖИТЕЛЕМ МАНЕВРА И АДАПТИВНОЙ КОРРЕКЦИЕЙ ПРОГНОЗА | 2005 |

|

RU2296348C2 |

| РАНГОВЫЙ АДАПТИВНЫЙ ПОСЛЕДОВАТЕЛЬНЫЙ ОБНАРУЖИТЕЛЬ СИГНАЛОВ | 1996 |

|

RU2100822C1 |

| US 7990311 B2, 02.08.2011 | |||

| WO 2011053850 A2, 02.08.2011 | |||

| JP 2012112934 A, 14.06.2012 | |||

| JP 2012103197 A, 31.05.2012. | |||

Авторы

Даты

2013-10-27—Публикация

2012-06-15—Подача