Изобретение относится к радиотехнике и может использоваться в когерентно-импульсных радиолокационных станциях.

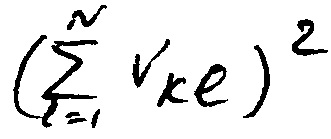

Известно цифровое устройство для подавления пассивных помех (см. Адаптивные устройства подавления пассивных помех в когерентно-импульсных РЛС УВД, Иванов Ю.В., Родионов Ю.В., Зарубежная радиоэлектроника 4, 1980 г., стр. 38), содержащее два квадратурных канала с последовательно соединенными фазовыми детекторами, аналого-цифровыми преобразователями и цифровыми фильтрами. Кроме когерентного гетеродина с фазовращателем на π/2 в устройство входит блок определения фазовой ошибки, входы которого подключены к первым элементам задержки цифровых фильтров квадратурных каналов, а выход через интегратор подключен ко входу управления перестраиваемого цифрового фазовращателя, включенного между когерентным гетеродином и фазовыми детекторами. Блок определения фазовой ошибки вырабатывает сигнал, пропорциональный доплеровской разности фаз сигналов помехи за период повторения РЛС. Этот сигнал после усреднения в интеграторе управляет фазой напряжения когерентного гетеродина. При этом совмещается "провал" скоростной характеристики цифрового устройства СДЦ с максимумом смещенного спектра флюктуаций движущейся пассивной помехи. Однако данное устройство имеет недостаток, заключающийся в том, что адаптивные свойства устройства ограничиваются учетом только доплеровской разности фазы помехи. Коэффициент же корреляции помехи не учитывается, что снижает эффективность подавления движущихся пассивных помех. Данного недостатка лишено цифровое устройство для подавления пассивных помех (авт. свид. СССР № 809018, МКИ G01S 7/36), содержащее два квадратурных канала, каждый из которых состоит из пяти перемножителей, сумматора и последовательно соединенных блоков памяти, причем входы и выходы первого блока памяти подключены к блоку измерения аргумента межпериодного коэффициента корреляции помехи  (межпериодной доплеровской разности фазы помехи), выходы которого подключены к последовательно соединенным блоку измерения модуля межпериодного коэффициента корреляции ρК и блоку вычисления весового коэффициента g2. Блок измерения аргумента межпериодного коэффициента корреляции своим выходом также подключен параллельно к функциональному преобразователю, на выходе которого образуются

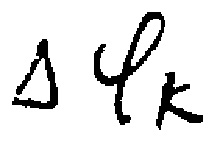

(межпериодной доплеровской разности фазы помехи), выходы которого подключены к последовательно соединенным блоку измерения модуля межпериодного коэффициента корреляции ρК и блоку вычисления весового коэффициента g2. Блок измерения аргумента межпериодного коэффициента корреляции своим выходом также подключен параллельно к функциональному преобразователю, на выходе которого образуются  и

и  и вычислительному блоку, на выходе которого образуются

и вычислительному блоку, на выходе которого образуются  и

и  . Поступающие с выходов первых блоков памяти цифровые коды xК-1, yК-1 умножаются в одних перемножителях на весовой коэффициент g2, а затем в других перемножителях на

. Поступающие с выходов первых блоков памяти цифровые коды xК-1, yК-1 умножаются в одних перемножителях на весовой коэффициент g2, а затем в других перемножителях на  и

и  . Цифровые коды, поступающие с выходов вторых блоков памяти, xК-2, yК-2 в перемножителях умножаются на

. Цифровые коды, поступающие с выходов вторых блоков памяти, xК-2, yК-2 в перемножителях умножаются на  и

и  . Таким образом осуществляется векторный поворот квадратурных составляющих на угол, соответствующий доплеровскому набегу фазы помехи за период повторения РЛС.

. Таким образом осуществляется векторный поворот квадратурных составляющих на угол, соответствующий доплеровскому набегу фазы помехи за период повторения РЛС.

Однако данное устройство имеет недостаток, заключающийся в том, что в нем не компенсируются сигналы, отраженные от дискретных медленно движущихся пассивных помех (типа "ангелов"). Это обусловлено инерционностью устройства, связанной с усреднением оценки доплеровской разности фаз  , в блоке измерения аргумента межпериодного коэффициента корреляции по конечному числу элементов разрешения по дальности. Уменьшение же постоянной времени усреднения может привести к компенсации сигналов и от полезных целей. То есть рассматриваемое устройство имеет недостаточную эффективность в условиях воздействия дискретных медленно перемещающихся пассивных помех.

, в блоке измерения аргумента межпериодного коэффициента корреляции по конечному числу элементов разрешения по дальности. Уменьшение же постоянной времени усреднения может привести к компенсации сигналов и от полезных целей. То есть рассматриваемое устройство имеет недостаточную эффективность в условиях воздействия дискретных медленно перемещающихся пассивных помех.

Целью изобретения является повышение эффективности подавления дискретных пассивных медленно движущихся помех. Поставленная цель достигается тем, что в цифровое устройство для подавления пассивных помех, содержащее измеритель модуля и аргумента коэффициента корреляции, блок вычисления весового коэффициента, первый вход которого соединен с первым выходом измерителя модуля и аргумента коэффициента корреляции, первый функциональный преобразователь, второй функциональный преобразователь первый и второй каналы обработки, каждый из которых содержит выходной алгебраический сумматор, первый перемножитель, выход которого соединен с первым входом выходного алгебраического сумматора, а первый вход соединен с первым выходом второго функционального преобразователя, второй перемножитель, выход которого соединен с вторым входом выходного алгебраического сумматора, а первый вход соединен с вторым выходом второго функционального преобразователя, третий перемножитель, выход которого соединен с третьим входом выходного алгебраического сумматора, а первый вход соединен с первым выходом первого функционального преобразователя, четвертый перемножитель, первый вход которого соединен с выходом блока вычисления весового коэффициента, последовательно соединенные первый блок оперативной памяти, вход которого является входом соответствующего канала обработки, второй блок оперативной памяти и пятый перемножитель, выход которого соединен с четвертым входом алгебраического выходного сумматора, а первый вход соединен со вторым выходом первого функционального преобразователя, вход и выход первого блока оперативной памяти первого и второго каналов обработки соединены с первым и третьим, вторым и четвертым входами измерителя модуля и аргумента коэффициента корреляции, второй вход каждого четвертого перемножителя соединен с выходом первого блока оперативной памяти того же канала, выход второго блока оперативной памяти каждого канала соединен с вторым входом третьего перемножителя другого канал, второй и четвертый входы выходного алгебраического сумматора первого канала обработки являются суммирующими, а третий - вычитающим, третий и четвертый входы выходного алгебраического сумматора второго канала обработки являются суммирующими, а первый вычитающим, введены соединенные последовательно третий блок оперативной памяти, вход которого соединен с вторым выходом измерителя модуля и аргумента коэффициента корреляции и входом второго функционального преобразователя, а выход соединен со входом первого функционального преобразователя, сумматор-вычитатель, другой вход которого соединен с вторым выходом измерителя и аргумента коэффициента корреляции и пороговый блок, выход которого соединен с вторым входом блока вычисления весового коэффициента, а другой вход соединен с третьим выходом измерителя модуля и аргумента коэффициента корреляции и третьим входом блока вычисления весового коэффициента, вход каждого канала обработки соединен с вторым входом первого перемножителя другого канала, в каждом канале обработки вход канала обработки соединен с вторым входом второго перемножителя, выход четвертого перемножителя соединен с пятым входом выходного алгебраического сумматора, пятые входы выходных алгебраических сумматоров являются суммирующими, первый вход выходного алгебраического сумматора первого канала обработки является суммирующим, второй вход выходного алгебраического сумматора второго канала обработки является суммирующим.

Заявителю не известны технические решения, в которых бы использовалась указанная в отличительной части формулы совокупность существенных признаков, дающая положительный эффект, указанный в цели изобретения.

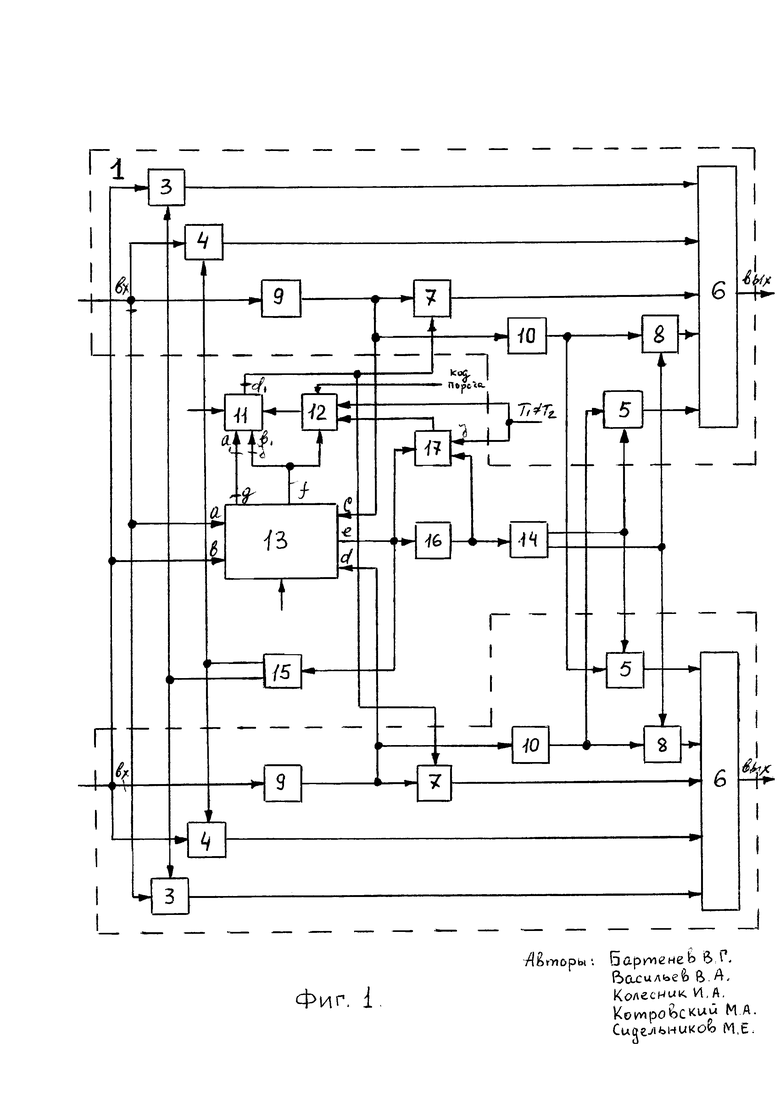

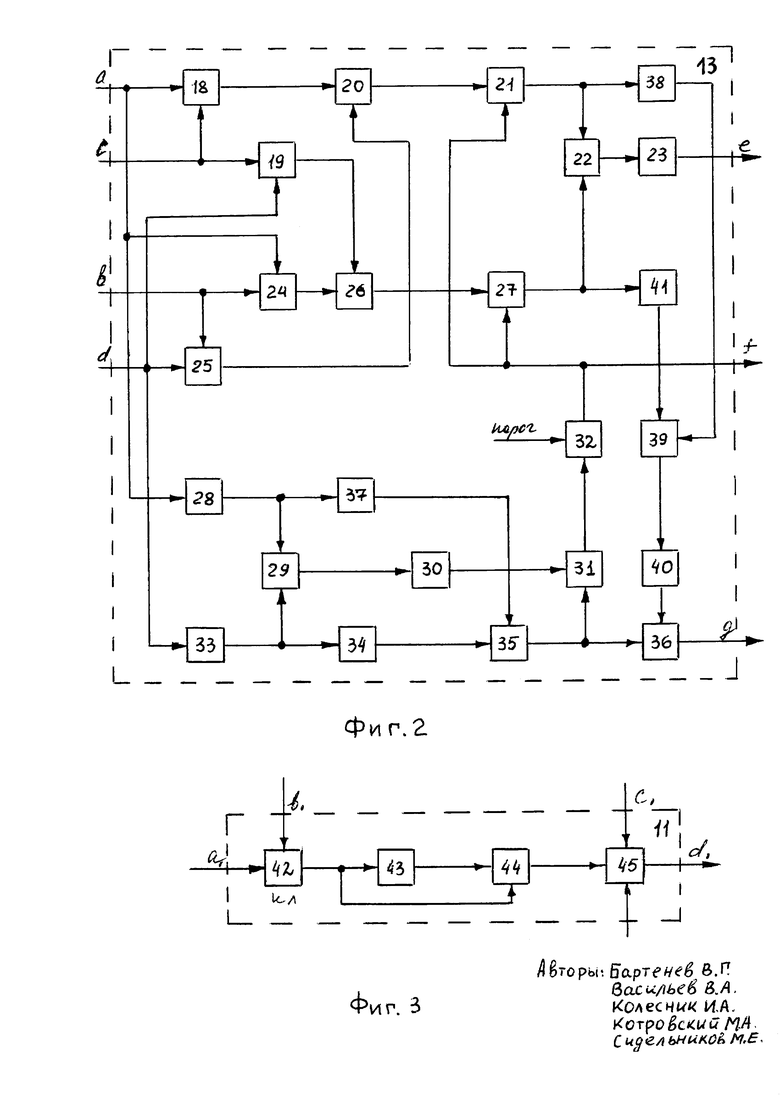

На фиг. 1 приведена структурная электрическая схема предлагаемого устройства; на фиг. 2 - структурная электрическая схема измерителя модуля и аргумента межпериодного коэффициента корреляции; на фиг. 3 - структурная электрическая схема блока вычисления весового коэффициента.

На фиг. 1, 2, 3 приняты следующие обозначения:

1 - первый канал обработки;

2 - второй канал обработки;

3 - первый перемножитель;

4 - второй перемножитель;

5 - третий перемножитель;

6 - выходной алгебраический сумматор;

7 - четвертый перемножитель;

8 - пятый перемножитель;

9 - первый блок оперативной памяти;

10 - второй блок оперативной памяти;

11 - блок вычисления весового коэффициента;

12 - пороговый блок;

13 - измеритель модуля и аргумента коэффициента корреляции;

14 - первый функциональный преобразователь;

15 - второй функциональный преобразователь;

16 - третий блок оперативной памяти;

17 - сумматор-вычитатель;

18 - шестой перемножитель;

19 - восьмой перемножитель;

20 - первый сумматор;

21 - первый блок усреднения;

22 - первый делитель;

23 - блок вычисления арктангенса;

24 - седьмой перемножитель;

25 - девятый перемножитель;

26 - вычитатель;

27 - второй блок усреднения;

28 - первый квадратор;

29 - второй сумматор;

30 - первый блок извлечения корня;

31 - второй делитель;

32 - блок сравнения с порогом и анализа протяженности пассивной помехи;

33 - второй квадратор;

34 - третий блок усреднения;

35 - третий сумматор;

36 - третий делитель;

37 - четвертый блок усреднения;

38 - третий квадратор;

39 - четвертый сумматор;

40 - второй блок извлечения корня;

41 - четвертый квадратор;

42 - коммутатор;

43 - четвертый блок оперативной памяти;

44 - пятый сумматор;

45 - блок инвертирования.

Устройство для подавления пассивных помех содержит первый и второй каналы обработки 1 и 2, каждый из которых содержит выходной алгебраический сумматор 6, первый перемножитель 3, выход которого соединен с первым входом выходного алгебраического сумматора 6, второй перемножитель 4, выход которого соединен с вторым входом выходного алгебраического сумматора 6, третий перемножитель 5, выход которого соединен с третьим входом выходного алгебраического сумматора 6, четвертый перемножитель 7, выход которого подключен к пятому входу выходного алгебраического сумматора 6, пятый перемножитель 8, выход которого подключен к четвертому входу выходного алгебраического сумматора 6 и два последовательно включенных первого и второго блоков 9 и 10 оперативной памяти. Устройство для подавления пассивных помех содержит также измеритель 13 модуля и аргумента межпериодного коэффициента корреляции, входы которого подключены ко входам и выходам первых блоков 9 оперативной памяти первого и второго каналов обработки 1 и 2. Первый выход измерителя 13 соединен со входом блока 11 вычисления весового коэффициента. Второй выход измерителя 13 подключен ко входам третьего блока 16 оперативной памяти, сумматора-вычитателя 17 и второго функционального преобразователя 15. Выход третьего блока 16 оперативной памяти соединен со входами первого функционального преобразователя 14 и сумматора-вычитателя 17. Выход сумматора-вычитателя 17 через пороговый блок 12 подключен ко входу скоростного признака блока 11 вычисления весового коэффициента.

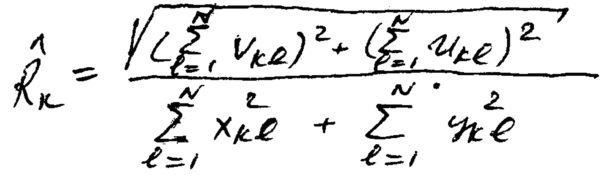

Выходы первого и второго функциональных преобразователей 14 и 15, а также выход блока 11 вычисления весового коэффициента подключены к соответствующим входам первого, второго, третьего, четвертого и пятого перемножителей, первого и второго каналов обработки. Измеритель 13 модуля и аргумента межпериодного коэффициента корреляции содержит соединенные последовательно шестой перемножитель 18, первый сумматор 20, первый блок 21 усреднения, первый делитель 22, и блок 23 вычисления арктангенса, выход которого является выходом оценки аргумента межпериодного коэффициента корреляции. Измеритель 13 также содержит последовательно соединенные первый квадратор 28, второй сумматор 29, первый блок 30 извлечения корня, второй делитель 31, блок 32 сравнения с порогом и анализа протяженности пассивной помехи, на выходе которого формируется признаки протяженности. Выход блока 32 подключен ко входам управления первого и второго блоков усреднения 21 и 27, выходы которых через квадраторы 38 и 41 подключены ко входам четвертого сумматора 39. Выход четвертого сумматора 39 через второй блок 40 извлечения корня подключен к третьему делителю 36, выход которого является выходом оценки модуля коэффициента корреляции.

В измерителе 13 имеются последовательно соединенные второй квадратор 33, третий блок усреднения 34, третий сумматор 35, выход которого соединен с другими входами второго делителя 31 и третьего делителя 36, последовательно соединенные седьмой перемножитель 24, вычитатель 26, выход которого подключен ко второму блоку 27 усреднения. Четвертый блок усреднения 37 включен между выходом первого квадратора 28 и входом третьего сумматора 35. Блок 11 вычисления весового коэффициента содержит последовательно соединенные коммутатор 42, четвертый блок оперативной памяти 43, пятый сумматор 44 и блок инвертирования 45.

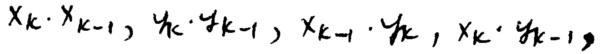

Устройство работает следующим образом. Цифровые коды отраженных сигналов xК, yК к-того периода повторения со входа устройства поступают в первые блоки 9 оперативной памяти, на измеритель 13 модуля и аргумента межпериодного коэффициента корреляции, а также на вторые входы первого и второго перемножителей 3 и 4. Коды задержанных на период повторения сигналов xК-1, yК-1 с выхода первых блоков 9 оперативной памяти также поступают в измеритель 13. При этом на выходе шестого, седьмого, восьмого и девятого перемножителей 18, 24, 19, 25 измерителя 13, образуются произведения кодов сигналов текущего зондирования на коды сигналов предыдущего зондирования

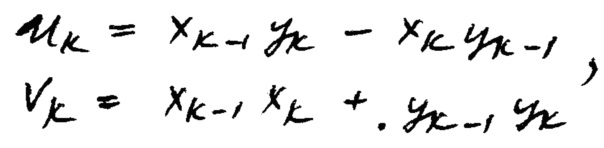

которые после сложения в 20 и вычитания в 26 дают соответственно величины

После усреднения  и

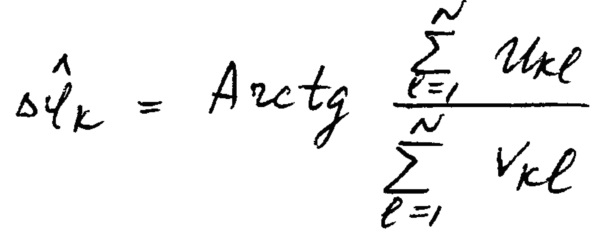

и  в блоках 21 и 27 по N элементам дальности (N выбирается для протяженной пассивной помехи равным 4 или 8, а для дискретной пассивной помехи, равным единице) и деления в делителе 22 на выходе блока 23 вычисления арктангенса получается оценка аргумента межпериодного коэффициента корреляции-доплеровского набега фазы за период повторения РЛС

в блоках 21 и 27 по N элементам дальности (N выбирается для протяженной пассивной помехи равным 4 или 8, а для дискретной пассивной помехи, равным единице) и деления в делителе 22 на выходе блока 23 вычисления арктангенса получается оценка аргумента межпериодного коэффициента корреляции-доплеровского набега фазы за период повторения РЛС

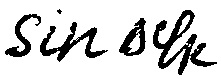

Со второго выхода измерителя 13 оценка величины набега фазы помехи  за к-тый период повторения поступает на вход второго функционального преобразователя 15, на выходе которого образуются

за к-тый период повторения поступает на вход второго функционального преобразователя 15, на выходе которого образуются  и

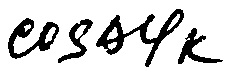

и  , поступающие соответственно на первые входы первого и второго перемножителей 3 и 4. Задержанный код оценки аргумента

, поступающие соответственно на первые входы первого и второго перемножителей 3 и 4. Задержанный код оценки аргумента  с выхода третьего блока 16 оперативной памяти поступает на вход первого функционального преобразователя 14, на выходе которого образуются

с выхода третьего блока 16 оперативной памяти поступает на вход первого функционального преобразователя 14, на выходе которого образуются  и

и  , поступающие соответственно на первые входы третьего и пятого перемножителей 5 и 8.

, поступающие соответственно на первые входы третьего и пятого перемножителей 5 и 8.

В первом и втором перемножителях 3 и 4 коды сигналов, соответствующие текущему зондированию xК, yК, подвергаются двумерному повороту на угол  в положительном направлении. В третьем и пятом перемножителях 5 и 8 коды xК-2, yК-2, поступающие с выхода вторых блоков 10 оперативной памяти, т.е. задержанные на два периода повторения подвергаются также двумерному повороту на угол

в положительном направлении. В третьем и пятом перемножителях 5 и 8 коды xК-2, yК-2, поступающие с выхода вторых блоков 10 оперативной памяти, т.е. задержанные на два периода повторения подвергаются также двумерному повороту на угол  , но в отрицательном направлении. Двумерный поворот квадратурных составляющих на угол

, но в отрицательном направлении. Двумерный поворот квадратурных составляющих на угол  и угол

и угол  , компенсирует доплеровские сдвиги фазы помехи и обеспечивает синфазность сигналов текущего зондирования xК, yК и сигналов, задержанных на два периода повторения xК-2, yК-2 с сигналами, задержанными на период повторения xК-1, yК-1, которые с выходов первых блоков 9 оперативной памяти подаются на второй вход четвертых перемножителей 7. На первый вход четвертых перемножителей подается код весового коэффициента g2.

, компенсирует доплеровские сдвиги фазы помехи и обеспечивает синфазность сигналов текущего зондирования xК, yК и сигналов, задержанных на два периода повторения xК-2, yК-2 с сигналами, задержанными на период повторения xК-1, yК-1, которые с выходов первых блоков 9 оперативной памяти подаются на второй вход четвертых перемножителей 7. На первый вход четвертых перемножителей подается код весового коэффициента g2.

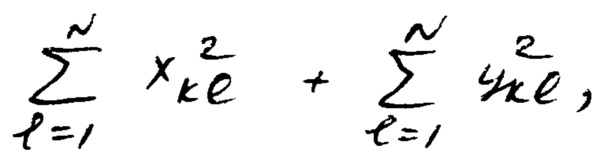

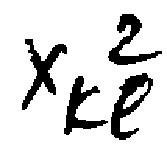

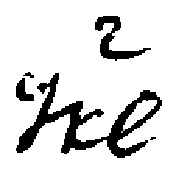

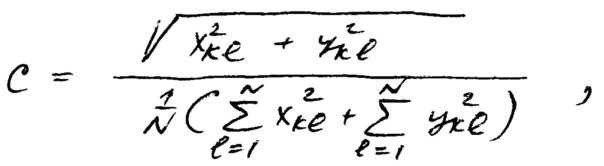

Остановимся подробнее на формировании весового коэффициента g2. В измерителе 13 коды незадержанных сигналов xК, yК после возведения в квадрат в первом и втором квадраторах 28 и 33, усреднения в третьем и четвертом блоках 34 и 37 суммируются в третьем сумматоре 35, что дает сумму

пропорциональную мощности помехи, код которой поступает на один из входов второго и третьего делителей 31 и 36. На другой вход второго делителя 31 поступает код, полученный после объединения квадратов  и

и  во втором сумматоре 29 и извлечение квадратного корня в первом блоке извлечения корня 30. В результате деления в 31 получается код величины

во втором сумматоре 29 и извлечение квадратного корня в первом блоке извлечения корня 30. В результате деления в 31 получается код величины

характеризующей превышение уровня отраженного сигнала в каждом отдельном элементе дальности над средней мощностью сигналов в N элементах дальности. Деление на N производится автоматически благодаря тому, что N выбирается равным 4=22 или 8=23, т.е. код делителя подается со сдвигом на два разряда или на три разряда влево. Код величины С поступает в блок 32 сравнения с порогом и анализа протяженности помехи. В блоке 32 производится сравнение кода величины С с кодом порога в каждом элементе дальности для того, чтобы определить принадлежность каждой отдельной выборки эхо-сигнала к шуму (если порог не превышен) или к сигналу цели, пассивной помехи (если порог превышен). Полученный признак превышение шумового уровня в виде логической единицы заносится в сдвиговый регистр, состоящий из N последовательно включенных разрядов. К выходам каждого разряда подключены входы N схемы И. При наличии во всех N элементах дальности (N разрядах регистра) логической единицы вырабатывается признак протяженности пассивной помехи, который заносится в буферное оперативное запоминающее устройство. При этом для упреждения информации о протяженности пассивной помехи на N элементов дальности считывание из ОЗУ признаков протяженности пассивной помехи производится по адресу, на N меньшем, чем адрес записи.

Признак протяженности пассивной помехи выдается на выход блока 32 и используется как для управления режимом работы первого и второго блоков усреднения 21 и 27 (при наличии лог. 1 N=4 или 8, при наличии лог. 0 N=1), так и для управления режимом работы блока вычисления весового коэффициента 11.

На другой вход делителя 36 поступает код, полученный после объединения квадратов  и

и  в четвертом сумматоре 39 и извлечения квадратного корня во втором блоке 40 извлечения корня. В результате деления получается код оценки модуля межпериодного коэффициента корреляции.

в четвертом сумматоре 39 и извлечения квадратного корня во втором блоке 40 извлечения корня. В результате деления получается код оценки модуля межпериодного коэффициента корреляции.

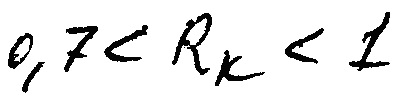

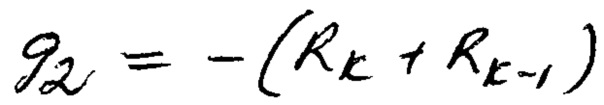

По величине этой оценки в блоке вычисляется оптимальная величина весового коэффициента g2, обеспечивающая предельное подавление помехи с данным коэффициентом корреляции нерекурсивным фильтром второго порядка как для постоянного периода повторения, так и для вобулированной последовательности импульсов. Для протяженных помех с реальными значениями модулей коэффициента корреляции  оптимальная величина для невобулированной последовательности импульсов, т.е.

оптимальная величина для невобулированной последовательности импульсов, т.е.  для вобулированной последовательности импульсов с чередующимися периодами

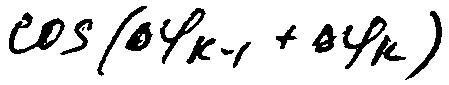

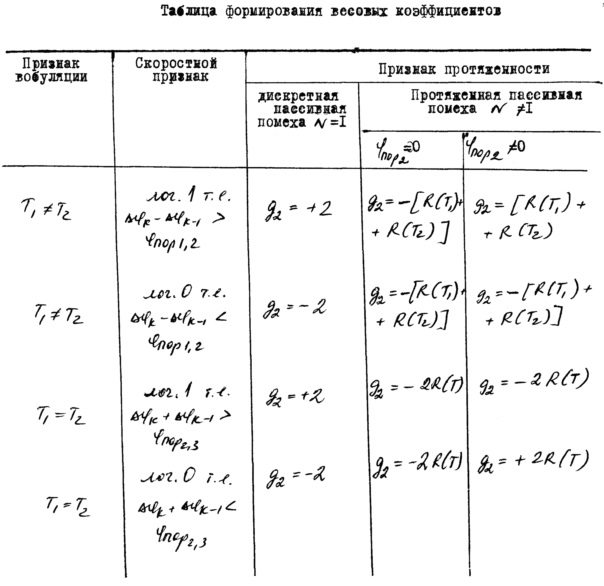

для вобулированной последовательности импульсов с чередующимися периодами  Формирование оптимального весового коэффициента в блоке 11 производится по-разному в зависимости от признака протяженности пассивной помехи, поступающего на вход 3, и от скоростного признака, поступающего на вход 2. Со входа и выхода третьего блока 16 оперативной памяти коды

Формирование оптимального весового коэффициента в блоке 11 производится по-разному в зависимости от признака протяженности пассивной помехи, поступающего на вход 3, и от скоростного признака, поступающего на вход 2. Со входа и выхода третьего блока 16 оперативной памяти коды  и

и  поступают в сумматор-вычитатель 17. По сигналу управления для невобулированной последовательности импульсов производится суммирование

поступают в сумматор-вычитатель 17. По сигналу управления для невобулированной последовательности импульсов производится суммирование  , а для вобулированной последовательности вычитание

, а для вобулированной последовательности вычитание  . В пороговом блоке 12 модуль суммы или разности аргументов межпериодного коэффициента корреляции сравнивается с порогом, величина которого меняется в зависимости от признака протяженности пассивной помехи. Для протяженной пассивной помехи этот порог равен

. В пороговом блоке 12 модуль суммы или разности аргументов межпериодного коэффициента корреляции сравнивается с порогом, величина которого меняется в зависимости от признака протяженности пассивной помехи. Для протяженной пассивной помехи этот порог равен  , для дискретной помехи

, для дискретной помехи  при наличии вобуляции и

при наличии вобуляции и  при отсутствии вобуляции, коды порогов хранятся в ПЗУ порогового блока 12. Следует заметить, что, если для протяженной пассивной помехи

при отсутствии вобуляции, коды порогов хранятся в ПЗУ порогового блока 12. Следует заметить, что, если для протяженной пассивной помехи  может равняться нулю, то для дискретной пассивной помехи

может равняться нулю, то для дискретной пассивной помехи  должно быть всегда больше нуля, так как в противном случае будет производиться подавление и полезного сигнала цели.

должно быть всегда больше нуля, так как в противном случае будет производиться подавление и полезного сигнала цели.

Зафиксированное превышение порога в блоке 12 в виде скоростного признака поступает в блок 11 вычисления весового коэффициента. На входе блока 11 включен коммутатор 42, управляемый кодом признака протяженности пассивной помехи. Для протяженной пассивной помехи коммутатор передает код модуля межпериодного коэффициента корреляции в четвертый блок 43 оперативной памяти. Задержанные и незадержанные коды модулей межпериодных коэффициентов корреляции смежных периодов суммируются в пятом сумматоре 44 и поступают в блок инвертирования 45. Для дискретной пассивной помехи (на входе 3 логический 0) на выходе коммутатора формируется код 1. Задержанная и незадержанная единица после сложения в 44 дают 2. Блок инвертирования 45 работает на инвертирование знака кода, поступающего на его вход только при отсутствии скоростного признака (логический ноль на входе 2). То есть если скорость пассивной помехи мала, то скоростной признак не вырабатывается, g2=-2, что соответствует режиму двукратного вычитания, если же скоростной признак вырабатывается, то g2=+2, что соответствует режиму когерентного сложения. Следует подчеркнуть, что если вырабатывается признак протяженной помехи, a  блок инвертирования работает без учета скоростного признака, т.е.

блок инвертирования работает без учета скоростного признака, т.е.  .

.

В таблице ниже приведены значения весовых коэффициентов, формируемых в блоке 11 в зависимости от признака протяженности пассивной помехи, скоростного признака и наличия или отсутствия вобуляции периода повторения РЛС.

Остановимся на вопросах практической реализации предложенного устройства. Все перемножители, делители, входящие в устройство, а также сумматоры, вычитатели могут быть построены на готовых интегральных микросхемах, например серии 1802. Для построения всех блоков оперативной памяти следует использовать микросхемы ОЗУ с произвольной выборкой. Для адресации ОЗУ с произвольной выборкой в блоки оперативной памяти входят адресные счетчики, тактируемые импульсами синхронизации с частотой дискретизации, поступающими до синхронизатора РЛС (на фиг. 1 не показано). Начало тактирования совпадает по времени с импульсами запуска РЛС. Причем объем ОЗУ должен выбираться с учетом наиболее протяженного по времени из периодов повторения вобулированной последовательности. Первый и второй функциональные преобразователи типа sin/cos, а также блок вычисления Arctg, квадраторы и блоки извлечения квадратного корня реализуется на программируемых постоянных запоминающих устройствах, например, в микросхемах серии 556. Все блоки усреднения представляют собой многоразрядные регистры последовательного сдвига, с параллельных выходов разрядов которых коды поступают на входы сумматоров. Тактирование регистров сдвига производятся импульсами синхронизации, поступающими от синхронизатора РЛС (на фиг. 1 не показано). Первый и второй блоки 21 и 27 усреднения в свой состав также включают и коммутатор, управляемый кодом признака протяженности, подключающий выход блока усреднения к его входу. Пороговый блок 12 представляет собой многоразрядный цифровой компаратор, на один вход которого подается текущий код, а на другой вход - код порога, который поступает от РЛС с выхода постоянного запоминающего устройства, с хранящимися в нем кодами порогов. Выбор кода порога производится изменением кода адреса подаваемого на ПЗУ. О построении блока сравнения с порогом и анализа протяженности помех говорилось при рассмотрении работы устройства. Дополнительно заметим, что сравнение кодов в этом блоке также производится с помощью цифрового компаратора. Критерий N из N, который реализован на N-разрядном регистре сдвига и N входовой схеме И является наиболее жестким и в некоторых случаях может быть заменен критерием K из N, где K выбирается на практике с учетом выбранного N и степени нестационарности пассивной помехи. Для упорядочивания признаков протяженности помехи в блок 32 сравнения с порогом и анализа протяженности введено буферное оперативное запоминающее устройство, состоящее из двух частей. Первая половина буферного ОЗУ в данном периоде повторения работает в режиме записи, а вторая - в режиме считывания. В следующем периоде повторения режимы ОЗУ меняются. При этом адресация каждой половины ОЗУ производится своим счетчиком, который при записи и считывании имеет смещение в N тактирующих импульсов. Тактирующие импульсы с частотой дискретизаций поступают с синхронизатора РЛС. Поскольку буферное ОЗУ хранит лишь одноразрядную информацию объем его невелик. От синхронизатора РЛС поступает также сигнал управления Т1≠Т2 на пороговый блок 12 и сумматор-вычитатель 17.

Коммутатор 42 реализуется по схеме мультиплекса на два входа, на одном из которых действует входной код на втором постоянный код единицы. Блок 45 инвертирования производит лишь инверсию кода знакового разряда с помощью схемы 2И-НЕ. На один вход схемы 2И-НЕ подается знаковый разряд текущего кода, а на другой объединенный по И признак скорости в код С1 и признак  вход е1. Таким образом, в схеме 2И-НЕ происходит инвертирование знака (т.е. вместо логического нуля на выходе логическая 1) при наличии хотя бы одного логического нуля на входах схемы 2И-НЕ, объединяющей признак скорости и признак

вход е1. Таким образом, в схеме 2И-НЕ происходит инвертирование знака (т.е. вместо логического нуля на выходе логическая 1) при наличии хотя бы одного логического нуля на входах схемы 2И-НЕ, объединяющей признак скорости и признак  , т.е. в соответствии с приведенной таблицей.

, т.е. в соответствии с приведенной таблицей.

Сравнительный анализ эффективности предложенного устройства с известным производился по характеристикам обнаружения полезного сигнала на фоне пассивных помех методом статистического моделирования. При этом доплеровский набег фазы за период повторения полезного сигнала задавался равным π, а доплеровский набег фазы сигнала помехи равным π/8. Межпериодный коэффициент корреляции дискретной пассивной помехи, занимающей один элемент дальности, составлял 0,95. Форма спектра флюктуаций помехи гауссова. Вероятность ложной тревоги была выбрана 10-8. Результаты расчетов показали, что при использовании вобуляции (9%) выигрыш в пороговом сигнале для предложенного устройства по сравнению с известным ранее для вероятности правильного обнаружения 0,5 составлял около 6 дБ, а при использовании постоянного периода повторения 3 дБ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство селекции движущихся целей для радиолокатора с вобуляцией периода повторения | 1984 |

|

SU1841287A1 |

| Устройство селекции движущихся целей для наземного когерентно-импульсного радиолокатора | 1983 |

|

SU1841286A1 |

| АДАПТИВНЫЙ РЕЖЕКТОР ПАССИВНЫХ ПОМЕХ | 2015 |

|

RU2599621C1 |

| АДАПТИВНЫЙ ВЫЧИСЛИТЕЛЬ ДЛЯ РЕЖЕКТИРОВАНИЯ ПОМЕХ | 2015 |

|

RU2582874C1 |

| ВЫЧИСЛИТЕЛЬ ДЛЯ РЕЖЕКЦИИ ПОМЕХ | 2017 |

|

RU2680824C1 |

| ВЫЧИСЛИТЕЛЬ ДЛЯ КОМПЕНСАЦИИ ПОМЕХ | 2017 |

|

RU2679974C1 |

| ВЫЧИСЛИТЕЛЬ ДЛЯ РЕЖЕКТИРОВАНИЯ ПОМЕХ | 2017 |

|

RU2680202C1 |

| ВЫЧИСЛИТЕЛЬ ДЛЯ РЕЖЕКТОРНОЙ ФИЛЬТРАЦИИ ПОМЕХ | 2017 |

|

RU2686634C1 |

| ВЫЧИСЛИТЕЛЬ ДЛЯ ПОДАВЛЕНИЯ ПОМЕХ | 2017 |

|

RU2686643C1 |

| АДАПТИВНЫЙ РЕЖЕКТОРНЫЙ ФИЛЬТР | 2017 |

|

RU2660645C1 |

Изобретение относится к области радиолокации и может быть использовано в когерентно-импульсных РЛС. Достигаемый технический результат - повышение эффективности подавленияэхо-сигналов медленно движущихся точечных отражателей. Указанный результат достигается за счет того, что устройство селекции содержит определенным образом соединенные между собой два квадратурных канала обработки, каждый из которых содержит сумматор, пять перемножителей, а также два блока задержки на период повторения, ключ, вычислитель весового коэффициента, управляемый инвертор, измеритель модуля и аргумента коэффициента межпериодной корреляции, два синусно-косинусных преобразователя, дополнительный блок задержки на период повторения, сумматор-вычитатель и пороговый блок. 1 з.п. ф-лы, 3 ил., 1 табл.

1. Цифровое устройство селекции движущихся целей, содержащее два квадратурных канала обработки, каждый из которых содержит сумматор, первый, второй и третий перемножители, выходы которых соединены соответственно с прямым, с прямым и инверсным входами сумматора, последовательно соединенные первый блок задержки на период повторения и четвертый перемножитель и последовательно соединенные второй блок задержки на период повторения и пятый перемножитель, выход которого соединен с инверсным входом сумматора, последовательно соединенные ключ, вычислитель весового коэффициента и управляемый инвертор, выход которого соединен с вторыми входами четвертых перемножителей обоих квадратурных каналов обработки, измеритель модуля и аргумента коэффициента межпериодной корреляции, выход модуля и выход сигнала "протяженная помеха" которого соединены соответственно с входом и управляющим входом ключа, первый синусно-косинусный преобразователь, синусный выход которого соединен с вторыми входами третьих перемножителей, а косинусный выход - с вторыми входами пятых перемножителей обоих квадратурных каналов обработки, и второй синусно-косинусный преобразователь, вход которого соединен с выходом аргумента измерителя модуля и аргумента коэффициента межпериодной корреляции, синусный выход второго синусно-косинусного преобразователя соединен с вторыми входами первых перемножителей, а косинусный выход - с вторыми входами вторых перемножителей обоих квадратурных каналов обработки, причем соединенные между собой вход первого блока задержки на период повторения первого квадратурного канала обработки и первый вход измерителя модуля и аргумента коэффициента межпериодной корреляции являются первым входом цифрового устройства селекции движущихся целей, соединенные между собой вход первого блока задержки на период повторения второго квадратурного канала обработки и второй вход измерителя модуля и аргумента коэффициента межпериодной корреляции являются вторым входом цифрового устройства селекции движущихся целей, выходы первых блоков задержки на период повторения первого и второго квадратурных каналов обработки соединены с входами соответствующих вторых блоков задержки на период повторения и соответственно с третьим и четвертым входами измерителя модуля и аргумента коэффициента межпериодной корреляции, выход второго блока задержки на период повторения каждого квадратурного канала обработки соединен с первым входом третьего перемножителя другого канала, отличающееся тем, что, с целью повышения эффективности подавления эхо-сигналов медленно движущихся точечных отражателей, введены блок задержки на период повторения, сумматор-вычитатель и пороговый блок, причем выход аргумента измерителя модуля и аргумента коэффициента межпериодной корреляции соединен входом сумматора-вычитателя и через блок задержки на период повторения с другим входом сумматора-вычитателя и с входом первого синусно-косинусного преобразователя, выход сумматора-вычитателя соединен через пороговый блок с управляющим входом управляемого инвертора, выход сигнала "протяженная помеха" измерителя модуля и аргумента коэффициента межпериодной корреляции соединен с входом переключения порогов порогового блока, соединенные между собой управляющие входы сумматора-вычитателя и порогового блока являются входом сигнала "вобуляция периода повторения" цифрового устройства селекции движущихся целей, первый вход первого перемножителя первого квадратурного канала обработки и первый вход второго перемножителя второго канала соединены с вторым входом цифрового устройства селекции движущихся целей, а первый вход первого перемножителя второго квадратурного канала обработки и первый вход второго перемножителя первого канала соединены с первым входом цифрового устройства селекции движущихся целей и в каждом квадратурном канале обработки выход четвертого перемножителя соединен с прямым входом сумматора.

2. Цифровое устройство по п. 1, отличающееся тем, что вычислитель весового коэффициента содержит последовательно соединенные блок задержки на период повторения и сумматор, второй вход которого соединен с входом блока задержки на период повторения.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| свид | |||

| Цифровое устройство для подав-лЕНия пАССиВНыХ пОМЕХ | 1979 |

|

SU809018A1 |

Авторы

Даты

2018-12-06—Публикация

1984-10-22—Подача