ОБЛАСТЬ ТЕХНИКИ

Настоящее изобретение относится к схеме пикселя и устройству отображения, оснащенному таковой, а подробнее к устройству отображения с активной матрицей.

УРОВЕНЬ ТЕХНИКИ

Мобильный терминал, такой как мобильный телефон или мобильная игровая машина, в общем, использует жидкокристаллическое устройство отображения в качестве своего средства отображения. В дополнение, поскольку мобильный телефон приводится в действие аккумуляторной батареей, решительно требуется снижать энергопотребление. Поэтому информация, такая как время или остаточный уровень батареи, которую необходимо постоянно отображать, отображается на отражательной вспомогательной панели. В дополнение, в последнее время как нормальное отображение в виде полноцветного отображения, так и отражательное постоянное отображение требуется реализовать на одной и той же основной панели.

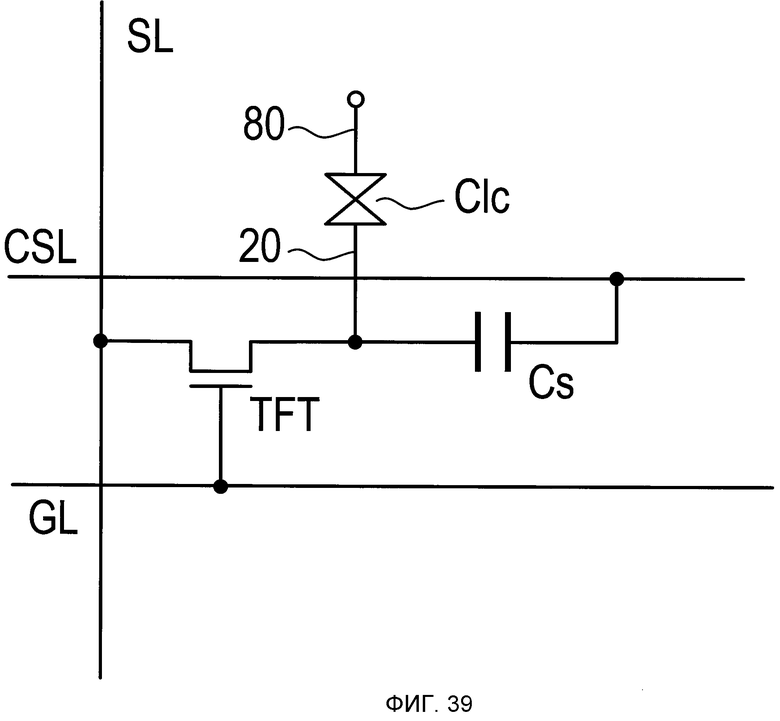

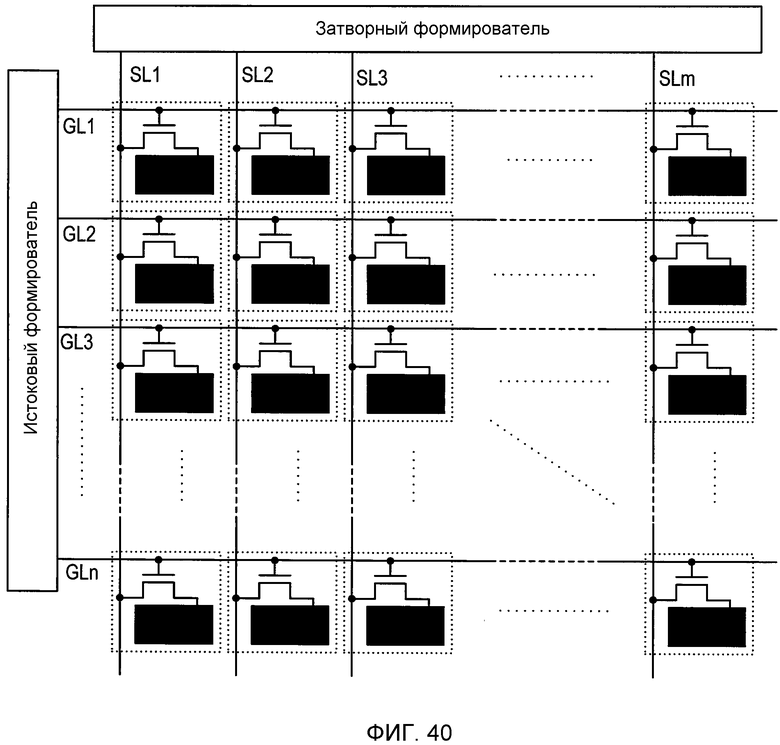

Фиг. 39 показывает эквивалентную схему для схемы пикселя обычного жидкокристаллического устройства отображения с активной матрицей. В дополнение, фиг. 40 показывает пример схемной компоновки жидкокристаллического устройства отображения с активной матрицей, имеющего m×n пикселей. В дополнение, каждое из чисел m и n имеет значение два или большего целого числа.

Как показано на фиг. 40, переключающий элемент, состоящий из тонкопленочного транзистора (TFT), предусмотрен в каждой точке пересечения m истоковых линий SL1, SL2, …, SLm и n линий GL1, GL2, …, GLn сканирования. На фиг. 39 истоковые линии SL1, SL2, …, SLm представлены истоковой линией SL, и подобным образом, линии GL1, GL2, …, GLn сканирования представлены линией GL сканирования.

Как показано на фиг. 39, емкостной элемент Clc жидкого кристалла и вспомогательный емкостной элемент Cs соединены параллельно через TFT. Емкостной элемент Clc жидкого кристалла имеет слоистую структуру, в которой жидкокристаллический слой предусмотрен между пиксельным электродом 20 и противоположным электродом 80. Противоположный электрод также указывается ссылкой как общий электрод.

В дополнение, на фиг. 40, что касается схемы пикселя, показаны просто TFT и пиксельный электрод (черная прямоугольная часть).

Вспомогательная емкость Cs имеет один конец (один электрод), присоединенный к пиксельному электроду 20, и другой конец (другой электрод), присоединенный к линии CSL вспомогательной емкости, и предусмотрена для стабилизации напряжения пиксельных данных, удерживаемого на пиксельном электроде 20. Вспомогательная емкость Cs имеет эффект предотвращения флуктуации напряжения пиксельных данных, удерживаемого на пиксельном электроде, вследствие пикового тока TFT, флуктуации электрической емкости емкостного элемента Clc жидкого кристалла между черным отображением и белым отображением, обусловленной анизотропией диэлектрической проницаемости молекул жидкого кристалла, и флуктуации напряжения, порожденной через паразитную емкость между пиксельным электродом и окружающей проводкой. Посредством последовательного управления напряжением линии сканирования TFT, присоединенный к линии сканирования, включается, и напряжение пиксельных данных, подаваемое на истоковую линию, записывается на соответствующем пиксельном электроде, в отношении каждой линии сканирования.

Что касается нормального отображения в качестве полноцветного отображения, даже когда контент отображения является неподвижными изображениями, один и тот же контент отображения повторно записывается в том же самом пикселе в отношении каждого кадра. Таким образом, напряжение пиксельных данных, удерживаемое на пиксельном электроде, обновляется, так что флуктуация напряжения пиксельных данных минимизируется, и может поддерживаться высококачественное отображение неподвижного изображения.

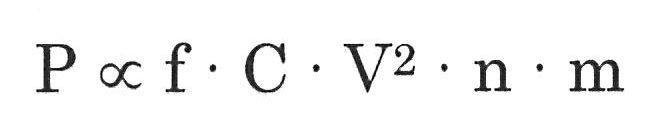

Энергопотребление для возбуждения жидкокристаллического устройства отображения, главным образом, большей частью обусловлено энергопотреблением для возбуждения истоковой линии истоковым формирователем, и грубо выражено выражением отношения, показанным в следующей формуле 1, при этом P представляет энергопотребление, f представляет частоту обновления (количество раз для выполнения действия обновления в течение одного кадра за единицу времени), C представляет допустимую нагрузку, возбуждаемую истоковым формирователем, V представляет напряжение возбуждения истокового формирователя, n представляет количество линий сканирования, а m представляет количество истоковых линий. Здесь, действие обновления означает действие для подачи напряжения на пиксельный электрод через истоковую линию наряду с поддержанием контента отображения.

(Формула 1)

Между тем, в случае постоянного отображения, поскольку контент отображения является неподвижными изображениями, не всегда нужно обновлять напряжение пиксельных данных в отношении каждого кадра. Поэтому, для того чтобы дополнительно снижать энергопотребление, частота обновления снижается на время этого постоянного отображения. Однако когда частота обновления понижена, напряжение пиксельных данных, удерживаемое на пиксельном электроде, флуктуирует вследствие тока утечки TFT. Флуктуация напряжения приводит к флуктуации яркости отображения (коэффициента пропускания жидкого кристалла) каждого пикселя, и это распознается в качестве мерцания. В дополнение, поскольку средний потенциал понижается в каждом периоде кадра, качество отображения могло бы понижаться, так что достаточный контраст не может обеспечиваться.

Здесь, в качестве способа для решения проблемы, что качество отображения снижается вследствие снижения частоты обновления, и для одновременного сокращения энергопотребления при постоянном отображении неподвижного изображения остаточного уровня аккумуляторной батареи или отображения времени, раскрыта конфигурация в следующем патентном документе 1. Согласно конфигурации, раскрытой в патентном документе 1, жидкокристаллическое отображение может быть реализовано посредством как пропускающей, так и отражательной функций, и, более того, часть памяти предусмотрена в схеме пикселя в области пикселей, в которой может быть предоставлено жидкокристаллическое отображение. Эта часть памяти удерживает информацию, которая должна отображаться в части отражательного жидкокристаллического отображения, в качестве сигнала напряжения. Во время отражательного жидкокристаллического отображения информация, соответствующая этому напряжению, отображается, когда схема пикселя считывает напряжение, удерживаемое в части памяти.

Согласно патентному документу 1, поскольку часть памяти состоит из SRAM (статического ОЗУ (оперативного запоминающего устройства)), и сигнал напряжения удерживается статично, действие обновления не нужно, так что качество отображения может поддерживаться, и одновременно снижается энергопотребление.

ДОКУМЕНТ ПРЕДШЕСТВУЮЩЕГО УРОВНЯ ТЕХНИКИ

Патентный документ

Патентный документ 1: Японская нерассмотренная патентная публикация № 2007-334224

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

ПРОБЛЕМЫ, КОТОРЫЕ ДОЛЖНЫ БЫТЬ РЕШЕНЫ ИЗОБРЕТЕНИЕМ

Однако, когда вышеописанная конфигурация применяется в жидкокристаллическом устройстве отображения, таком как мобильный телефон, необходимо предусматривать часть памяти для хранения пиксельных данных в отношении каждого пикселя или каждой группы пикселей, в дополнение к вспомогательному емкостному элементу для удерживания напряжения пиксельных данных, служащих в качестве аналоговой информации во время нормального действия. Это вызывает увеличение количества элементов и количества сигнальных линий, которые должны быть сформированы на подложке массива (подложке активной матрицы) в части отображения жидкокристаллического устройства отображения, так что светосила снижается в проницаемом режиме. В дополнение, когда схема возбуждения с изменением полярности для выполнения возбуждения переменного тока (AC) для жидкого кристалла предусмотрена вместе с вышеприведенной частью памяти, светосила дополнительно снижается. Таким образом, когда светосила снижается вследствие увеличения количества элементов и сигнальных линий, яркость изображения отображения снижается в режиме нормального отображения.

В дополнение, по меньшей мере два оттенка предполагается в вышеприведенном режиме постоянного отображения, но требуется реализовать многоцветное отображение в режиме постоянного отображения. Однако, когда такой режим отображения реализован в традиционной конфигурации, количество требуемых частей памяти увеличивается, как и следовало ожидать, и, соответственно, дополнительно увеличивается количество элементов и количество сигнальных линий.

Настоящее изобретение было сделано ввиду вышеприведенных проблем, и цель настоящего изобретения состоит в том, чтобы предоставить схему пикселя и устройство отображения, в которых предотвращено ухудшение жидкокристаллического отображения, и предотвращено снижение качества отображения при низком энергопотреблении без снижения светосилы, и в особенности предоставлена возможность выполнять действие обновления в режиме многоцветного отображения наряду с предотвращением увеличения количества элементов и сигнальных линий.

СРЕДСТВО ДЛЯ РЕШЕНИЯ ПРОБЛЕМЫ

Для того чтобы добиться вышеприведенной цели, схема пикселя согласно настоящему изобретению включает в себя:

часть элемента отображения, включающую в себя единичный элемент отображения, внутренний узел, составляющий часть части элемента отображения, для удерживания напряжения пиксельных данных, приложенного к части элемента отображения,

первую переключающую схему для передачи напряжения пиксельных данных, поданного с сигнальной линии данных, на внутренний узел через по меньшей мере предопределенный переключающий элемент,

вторую переключающую схему для передачи напряжения, поданного с сигнальной линии данных, на внутренний узел без протекания через предопределенный переключающий элемент, и

схему управления для удерживания предопределенного напряжения, соответствующего напряжению пиксельных данных, удерживаемому внутренним узлом на одном конце первого емкостного элемента, и управления включением/отключением второй переключающей схемы, в которой

вторая переключающая схема является последовательной цепью, включающей в себя первый транзисторный элемент, имеющий первый вывод, второй вывод и управляющий вывод для управления соединением между первым и вторым выводами, и диодный элемент,

схема управления является последовательной цепью, содержащей второй транзисторный элемент, имеющий первый вывод, второй вывод и управляющий вывод для управления соединением между первым и вторым выводами, и первый емкостной элемент,

один конец каждой из первой и второй переключающих схем присоединен к сигнальной линии данных,

другой конец каждой из первой и второй переключающих схем, и первый вывод второго транзисторного элемента присоединены к внутреннему узлу,

диодный элемент обладает функцией выпрямления из сигнальной линии данных на внутренний узел,

управляющий вывод первого транзисторного элемента, второй вывод второго транзисторного элемента и один конец первого емкостного элемента присоединены друг к другу для формирования выходного узла схемы управления,

управляющий вывод второго транзисторного элемента присоединен к первой линии управления, и

другой конец первого емкостного элемента присоединен ко второй линии управления.

В это время предопределенный переключающий элемент может включать в себя третий транзисторный элемент, имеющий первый вывод, второй вывод и управляющий вывод для управления соединением между первым и вторым выводами, и управляющий вывод может быть присоединен к сигнальной линии сканирования.

В дополнение, вторая переключающая схема является последовательной цепью, включающей в себя первый транзисторный элемент, диодный элемент и четвертый транзисторный элемент, имеющей первый вывод, второй вывод и управляющий вывод для управления соединением между первым и вторым выводами, и его управляющий вывод может быть присоединен ко второй линии управления или третьей линии управления, отличной от второй линии управления.

В дополнение, в вышеприведенной конфигурации, первая переключающая схема может быть последовательной цепью, включающей в себя четвертый транзисторный элемент во второй переключающей схеме и предопределенный переключающий элемент, или последовательной цепью, включающей в себя пятый транзисторный элемент, имеющий управляющий вывод, присоединенный к управляющему выводу четвертого транзисторного элемента во второй переключающей схеме, и предопределенный переключающий элемент.

Более того, в дополнение к вышеприведенной конфигурации, схема пикселя согласно настоящему изобретению, имеющему другие характеристики, дополнительно включает в себя второй емкостной элемент, имеющий один конец, присоединенный к внутреннему узлу, и другой конец, присоединенный к четвертой линии управления или линии предопределенного постоянного напряжения.

В дополнение, согласно устройству отображения по настоящему изобретению, массив схем пикселя включает в себя вышеприведенные схемы пикселя, скомпонованные в направлении строки и направлении столбца, сигнальная линия данных предусмотрена в отношении каждого из столбцов, один конец первой переключающей схемы в каждой из схем пикселя, скомпонованных в одном и том же столбце, присоединен к общей сигнальной линии данных, управляющий вывод второго транзисторного элемента в каждой из схем пикселя, скомпонованных в одной и той же строке или одном и том же столбце, присоединен к общей первой линии управления, и

другой конец первого емкостного элемента в каждой из схем пикселя, скомпонованных в одной и той же строке или одном и том же столбце, присоединен к общей второй линии управления, и устройство отображения включает в себя схему возбуждения сигнальных линий данных для возбуждения по отдельности сигнальных линий данных и схему возбуждения линий управления для возбуждения по отдельности первой и второй линий управления.

В дополнение к вышеприведенным характеристикам, согласно устройству отображения по настоящему изобретению, имеющему другие характеристики, предопределенный переключающий элемент является третьим транзисторным элементом, имеющим первый вывод, второй вывод и управляющий вывод для управления включением между первым и вторым выводами, и управляющий вывод присоединен к сигнальной линии сканирования,

сигнальная линия сканирования предусмотрена в отношении каждой из строк, и схемы пикселя, скомпонованные в одной и той же строке, присоединены к общей сигнальной линии сканирования, и

предусмотрена схема возбуждения сигнальных линий сканирования для возбуждения по отдельности сигнальных линий сканирования.

Здесь, когда вторая переключающая схема является последовательной цепью, включающей в себя первый транзисторный элемент, диодный элемент и четвертый транзисторный элемент, имеющей первый вывод, второй вывод и управляющий вывод для управления соединением между первым и вторым выводами, управляющий вывод четвертого транзисторного элемента в каждой из схем пикселя, скомпонованных в одной и той же строке или одном и том же столбце, может быть присоединен к общей второй линии управления. В качестве альтернативы, управляющий вывод четвертого транзисторного элемента может быть присоединен к общей третьей линии управления. В этом случае третья линия управления управляется схемой возбуждения линий управления.

В дополнение, в вышеприведенной конфигурации, первая переключающая схема может быть последовательной цепью, включающей в себя четвертый транзисторный элемент во второй переключающей схеме и третий транзисторный элемент, или последовательной цепью, включающей в себя пятый транзисторный элемент, имеющий управляющий вывод, присоединенный к управляющему выводу четвертого транзисторного элемента во второй переключающей схеме, и третий транзисторный элемент.

В дополнение к вышеприведенным характеристикам, согласно устройству отображения по настоящему изобретению, во время действия записи для записи по отдельности пиксельных данных в схемах пикселя, скомпонованных в одной выбранной строке,

схема возбуждения сигнальных линий сканирования прикладывает предопределенное напряжение выбранной строки к сигнальной линии сканирования в выбранной строке, чтобы включать третьи транзисторные элементы, скомпонованные в выбранной строке, и прикладывает предопределенное напряжение невыбранной строки к сигнальной линии сканирования в невыбранной строке, чтобы отключать третьи транзисторные элементы, скомпонованные в невыбранной строке, и

схема возбуждения сигнальных линий данных по отдельности прикладывает напряжение данных, соответствующее пиксельным данным, которые должны быть записаны в схеме пикселя в каждом столбце в выбранной строке, к сигнальным линиям данных.

Здесь, во время действия записи, предпочтительно, чтобы схема возбуждения линий управления прикладывала предопределенное напряжение к первой линии управления для включения второго транзисторного элемента.

В дополнение, согласно устройству отображения по настоящему изобретению, во время действия записи для записи по отдельности пиксельных данных в схемах пикселя, скомпонованных в одной выбранной строке,

схема возбуждения сигнальных линий сканирования прикладывает предопределенное напряжение выбранной строки к сигнальной линии сканирования в выбранной строке, чтобы включать третьи транзисторные элементы, скомпонованные в выбранной строке, и прикладывает предопределенное напряжение невыбранной строки к сигнальной линии сканирования в невыбранной строке, чтобы отключать третьи транзисторные элементы, скомпонованные в невыбранной строке,

схема возбуждения линий управления прикладывает предопределенное напряжение выбора ко второй линии управления, скомпонованной в выбранной строке, для включения четвертых транзисторных элементов, и прикладывает предопределенное напряжение отсутствия выбора ко второй линии управления в невыбранной строке для выключения четвертых транзисторных элементов, и

схема возбуждения сигнальных линий данных по отдельности прикладывает напряжение данных, соответствующее пиксельным данным, которые должны быть записаны в схеме пикселя в каждом столбце в выбранной строке, к сигнальным линиям данных.

В дополнение, когда управляющий вывод четвертого транзисторного элемента схемы пикселя присоединен к третьей линии управления, схема возбуждения линий управления может прикладывать напряжение выбора к третьей линии управления в выбранной строке, и прикладывать напряжение отсутствия выбора к третьей линии управления в невыбранной строке.

В дополнение, согласно устройству отображения по настоящему изобретению, внутренний узел каждой из схем пикселя в массиве схем пикселя удерживает одно состояние напряжения из числа множества дискретных состояний напряжения, в котором многочисленные оттенки реализованы разными состояниями напряжения, и во время действия самообновления для одновременной компенсации флуктуаций напряжения внутренних узлов посредством активизации вторых переключающих схем и схем управления во множестве схем пикселя,

схема возбуждения сигнальных линий сканирования прикладывает предопределенное напряжение к сигнальным линиям сканирования, присоединенным ко всем схемам пикселей в массиве схем пикселя, для отключения третьих транзисторных элементов,

схема возбуждения сигнальных линий данных прикладывает входное напряжение обновления, выдаваемое добавлением предопределенного первого напряжения настройки, соответствующего падению напряжения на второй переключающей схеме, к требуемому напряжению обновления, соответствующему состоянию напряжения целевого оттенка, который должен быть подвергнут действию обновления, к сигнальной линии данных, и

схема возбуждения линий управления прикладывает опорное напряжение обновления, выдаваемое добавлением предопределенного второго напряжения настройки, соответствующего падению напряжения на первой линии управления и внутреннем узле, к напряжению изоляции обновления, определенному промежуточным напряжением между состоянием напряжения оттенка, на одну ступень более низкого, чем целевой оттенок, и состоянием напряжения целевого оттенка, к первой линии управления, и прикладывает напряжение вольтодобавки, имеющее предопределенную амплитуду, ко второй линии управления, чтобы приложить изменение напряжения, обусловленное емкостной связью через первый емкостной элемент, к выходному узлу, и

когда состояние напряжения внутреннего узла выше, чем требуемое напряжение обновления, диодный элемент подвергается обратному смещению от сигнальной линии данных к внутреннему узлу, и сигнальная линия данных, и внутренний узел не соединены, когда состояние напряжения внутреннего узла ниже, чем напряжение изоляции обновления, флуктуации потенциала выходного узла, обусловленные прикладыванием напряжения вольтодобавки, подавляются, первый транзисторный элемент отключен, и сигнальная линия данных, и внутренний узел не соединены, и когда состояние напряжения внутреннего узла выше, чем напряжение изоляции обновления, и ниже, чем требуемое напряжение обновления, диодный элемент подвергнут прямому смещению от сигнальной линии данных к внутреннему узлу, флуктуация потенциала выходного узла не подавляется, первый транзисторный элемент включен, и требуемое напряжение обновления прикладывается к внутреннему узлу, так что действие обновления выполняется для схемы пикселя, имеющей внутренний узел, показывающий состояние напряжения целевого оттенка.

В дополнение, в качестве других характеристик, когда первая переключающая схема схемы пикселя включает в себя четвертый транзисторный элемент или пятый транзисторный элемент, схема возбуждения линий управления прикладывает предопределенное напряжение к третьей линии управления для включения четвертого транзисторного элемента и прикладывает напряжение вольтодобавки, имеющее предопределенную амплитуду, ко второй линии управления, чтобы прикладывать изменение напряжения, обусловленное емкостной связью через первый емкостной элемент, к выходному узлу для выполнения действия обновления для схемы пикселя, имеющей внутренний узел, показывающий состояние напряжения целевого оттенка.

В дополнение, в вышеприведенном случае, предпочтительно, чтобы предопределенное напряжение прикладывалось к третьей линии управления после того, как опорное напряжение обновления приложено к первой линии управления, и напряжение вольтодобавки приложено ко второй линии управления.

В дополнение к вышеприведенным характеристикам, в качестве других характеристик, при условии, что третий транзисторный элемент отключен, входное напряжение обновления прикладывается к сигнальной линии данных, и опорное напряжение обновления прикладывается к первой линии управления, действие для прикладывания напряжения вольтодобавки ко второй линии управления выполняется несколько раз наряду с изменением значений входного напряжения обновления и напряжения изоляции обновления, так что действие обновления последовательно выполняется для схем пикселя, имеющих внутренние узлы, показывающие состояния напряжения разных оттенков.

В это время напряжение вольтодобавки прикладывается, когда входное напряжение обновления и напряжение изоляции обновления изменяются количество раз, предусмотренное вычитанием единицы из количества оттенков, соответствующих количеству состояний напряжения, удерживаемых внутренним узлом каждой из схем пикселя в массиве схем пикселя.

В дополнение к вышеприведенным характеристикам, согласно устройству отображения по настоящему изобретению, имеющему другие характеристики, после завершения этапа обновления, включающего в себя действие, при котором действие для прикладывания напряжения вольтодобавки ко второй линии управления выполняется несколько раз наряду с изменением значений входного напряжения обновления и напряжения изоляции обновления при условии, что третий транзисторный элемент отключен, входное напряжение обновления прикладывается к сигнальной линии данных, а опорное напряжение обновления прикладывается к первой линии управления,

этап ожидания выполняется таким образом, что схема возбуждения сигнальных линий данных прикладывает напряжение, соответствующее минимальному значению состояния напряжения, удерживаемого внутренним узлом, к сигнальной линии данных, и схема возбуждения линий управления не прикладывает напряжение вольтодобавки ко второй линии управления и прикладывает напряжение к первой линии управления через по меньшей мере заданное время для включения второго транзисторного элемента независимо от состояния напряжения внутреннего узла.

В это время предпочтительно, чтобы после того, как этап ожидания выполняется в течение времени, которое в десять раз длиннее, чем у этапа обновления, этап обновления выполнялся еще раз.

В дополнение, в вышеприведенной конфигурации, предпочтительно, чтобы первое напряжение настройки являлось напряжением включения диодного элемента. В дополнение, предпочтительно, чтобы второе напряжение настройки являлось пороговым напряжением второго транзисторного элемента.

В дополнение, согласно настоящему изобретению, имеющему другие характеристики, во время действия самообновления,

при условии, что первый оттенок установлен в качестве целевого оттенка, входное напряжение обновления прикладывается к сигнальной линии данных, и

опорное напряжение обновления прикладывается к первой линии управления, напряжение вольтодобавки прикладывается ко второй линии управления, а затем,

с непрерывно приложенным напряжением вольтодобавки, второй оттенок, на одну ступень более высокий, чем первый оттенок, устанавливается в качестве целевого оттенка, опорное напряжение обновления, приложенное к первой линии управления, изменяется, а после этого изменяется входное напряжение обновления, приложенное к сигнальной линии данных, так что действие обновления последовательно выполняется для схем пикселя, имеющих внутренние узлы, показывающие состояния напряжения разных оттенков.

Таким образом, в случае, где существует оттенок, более высокий, чем второй оттенок,

после завершения действия обновления для второго оттенка, с непрерывно приложенным напряжением вольтодобавки, действие выполняется повторно таким образом, что более высокий на одну ступень оттенок устанавливается в качестве целевого оттенка, опорное напряжение обновления, приложенное к первой линии управления, изменяется, и после этого изменяется входное напряжение обновления, приложенное к сигнальной линии данных.

В дополнение, в вышеприведенном способе, когда управляющий вывод четвертого транзисторного элемента присоединен к общей третьей линии управления, в дополнение к прикладыванию напряжения вольтодобавки ко второй линии управления, предопределенное напряжение может прикладываться к третьей линии управления, чтобы включать четвертый транзисторный элемент. В это время после того, как целевой оттенок изменен во второй оттенок, напряжение вольтодобавки непрерывно прикладывается ко второй линии управления, и предопределенное напряжение непрерывно прикладывается к третьей линии управления для включения четвертого транзисторного элемента.

Таким образом, в случае, где существует оттенок, более высокий, чем второй оттенок,

после завершения действия обновления для второго оттенка, с непрерывно приложенными напряжением вольтодобавки и предопределенным напряжением для включения четвертого транзисторного элемента, действие выполняется повторно таким образом, что более высокий на одну ступень оттенок устанавливается в качестве целевого оттенка, опорное напряжение обновления, приложенное к первой линии управления, изменяется, и после этого изменяется входное напряжение обновления, приложенное к сигнальной линии данных.

Когда действие самообновления выполняется вышеприведенным способом, действие обновления для разных оттенков может выполняться наряду с предотвращением увеличения количества раз для изменения напряжения вольтодобавки, так что энергопотребление дополнительно снижается.

В дополнение, согласно устройству отображения по настоящему изобретению, имеющему другие характеристики, вторые линии управления, присоединенные к другим концам первых емкостных элементов схем пикселя, скомпонованных в строках с нечетными номерами или столбцах с нечетными номерами, электрически присоединены друг к другу,

вторые линии управления, присоединенные к другим концам первых емкостных элементов схем пикселя, скомпонованных в строках с четными номерами или столбцах с четными номерами, электрически присоединены друг к другу, и вторая линия управления, присоединенная к другому концу первого емкостного элемента каждой из схем пикселя, скомпонованных в строке с нечетным номером или столбце с нечетным номером, и вторая линия управления, присоединенная к другому концу первого емкостного элемента каждой из схем пикселя, скомпонованных в строке с четным номером или столбце с четным номером, электрически не присоединены друг к другу, и по отдельности возбуждаются схемой возбуждения линий управления.

В дополнение, согласно устройству отображения по настоящему изобретению, имеющему другие характеристики, вторые линии управления, присоединенные к другим концам первых емкостных элементов, и третьи линии управления, присоединенные к управляющим выводам четвертых транзисторных элементов, электрически присоединены друг к другу, соответственно, в схемах пикселя, скомпонованных в строках с нечетными номерами или столбцах с нечетными номерами,

вторые линии управления, присоединенные к другим концам первых емкостных элементов, и третьи линии управления, присоединенные к управляющим выводам четвертых транзисторных элементов, электрически присоединены друг к другу, соответственно, в схемах пикселя, скомпонованных в строках с четными номерами или столбцах с четными номерами,

вторая линия управления, присоединенная к другому концу первого емкостного элемента каждой из схем пикселя, скомпонованных в строке с нечетным номером или столбце с нечетным номером, и вторая линия управления, присоединенная к другому концу первого емкостного элемента каждой из схем пикселя, скомпонованных в строке с четным номером или столбце с четным номером, электрически не присоединены друг к другу и по отдельности возбуждаются схемой возбуждения линий управления, и

третья линия управления, присоединенная к управляющему выводу четвертого транзисторного элемента каждой из схем пикселя, скомпонованных в строке с нечетным номером или столбце с нечетным номером, и третья линия управления, присоединенная к управляющему выводу четвертого транзисторного элемента каждой из схем пикселя, скомпонованных в строке с четным номером или столбце с четным номером, электрически не присоединены друг к другу, и по отдельности возбуждаются схемой возбуждения линий управления.

Согласно устройству отображения по настоящему изобретению, имеющему другие характеристики, вывод, который противоположен выводу, присоединенному к внутреннему узлу, из выводов единичного элемента отображения, присоединен к общему электроду, и

запись выполняется таким образом, что, во время действия записи для записи пиксельных данных в схеме пикселя, полярность потенциала внутреннего узла, основанного на потенциале общего электрода, изменяется между схемами пикселя, скомпонованными в строке с нечетным номером или столбце с нечетным номером, и схемами пикселя, скомпонованными в строке с четным номером или столбце с четным номером.

Согласно устройству отображения по настоящему изобретению, имеющему другие характеристики, двум, высокому и низкому, напряжениям предоставлена возможность прикладываться к общему электроду, и

два, высокое и низкое, напряжения, которые должны прикладываться к общему электроду, переключаются между периодом для выполнения действия записи для схем пикселя, скомпонованных в строке с нечетным номером или столбце с нечетным номером, и периодом для выполнения действия записи для схем пикселя, скомпонованных в строке с четным номером или столбце с четным номером.

Согласно устройству отображения по настоящему изобретению, имеющему другие характеристики, действие обновления выполняется для схем пикселя, скомпонованных в строке с нечетным номером или столбце с нечетным номером, таким образом, что при условии, что одно из высокого и низкого напряжений прикладывается к общему электроду, третий транзисторный элемент отключается, и при условии, что входное напряжение обновления прикладывается к сигнальной линии данных, и опорное напряжение обновления прикладывается к первой линии управления, напряжение вольтодобавки прикладывается ко второй линии управления, присоединенной к строке с нечетным номером или столбцу с нечетным номером, и

действие обновления выполняется для схем пикселя, скомпонованных в строке с четным номером или столбце с четным номером, таким образом, что после того как напряжение, приложенное к общему электроду, переключается в другое из высокого и низкого напряжений, при условии, что входное напряжение обновления прикладывается к сигнальной линии данных, и опорное напряжение обновления прикладывается к первой линии управления, напряжение вольтодобавки прикладывается ко второй линии управления, присоединенной к строке с четным номером или столбцу с четным номером.

РЕЗУЛЬТАТ ИЗОБРЕТЕНИЯ

Согласно конфигурации настоящего изобретения, в дополнение к нормальному действию записи, действие (действие самообновления) для восстановления абсолютного значения напряжения между обоими концами части элемента отображения, в значение во время последнего действия записи, может выполняться вне зависимости от действия записи. В особенности, согласно настоящему изобретению, только схема пикселя, имеющая внутренний узел, который должен восстанавливаться в состояние напряжения целевого оттенка, может автоматически обновляться из числа схем пикселя, прикладыванием импульсного напряжения один раз, так что действие самообновления может выполняться в обстоятельствах, где многозначное состояние напряжения удерживается во внутреннем узле.

В случае, где скомпоновано множество схем пикселя, нормальное действие записи, в целом, выполняется в отношении каждой строки. Таким образом, необходимо возбуждать схему формирователя вплоть до количества раз, соответствующего количеству строк скомпонованных схем пикселя.

Согласно схеме пикселя по настоящему изобретению, действие обновления может выполняться для множества скомпонованных пикселей совместно в отношении каждого состояния напряжения, удерживаемого в ней, посредством выполнения действия самообновления. Поэтому количество раз, требуемое для возбуждения схемы возбуждения от начала до окончания действия обновления, может быть значительно сокращено, а энергопотребление может быть снижено.

Таким образом, поскольку необходимо по отдельности предусматривать часть памяти, такую как SRAM, в схеме пикселя, светосила почти совершенно не снижается в отличие от традиционной технологии.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

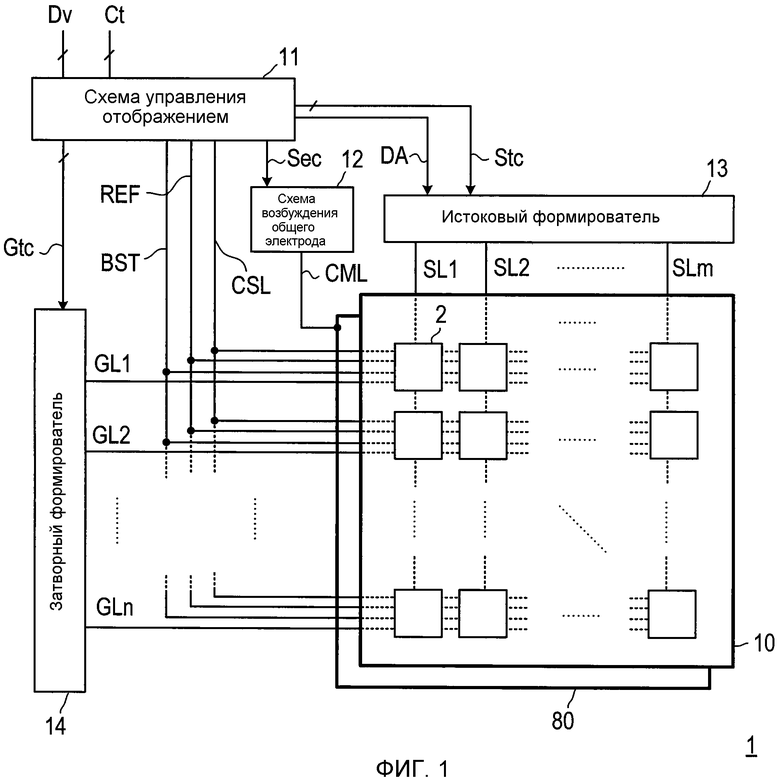

Фиг. 1 - структурная схема, показывающая один из примеров схематической конфигурации устройства отображения по настоящему изобретению.

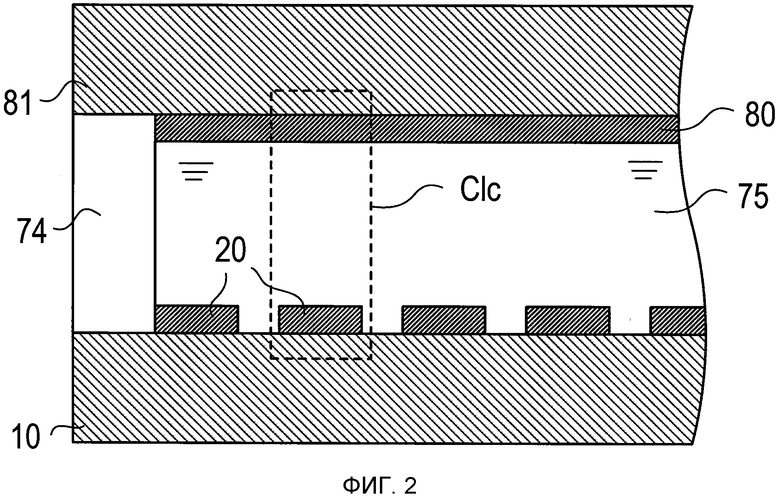

Фиг. 2 - принципиальная структурная схема в поперечном разрезе жидкокристаллического устройства отображения.

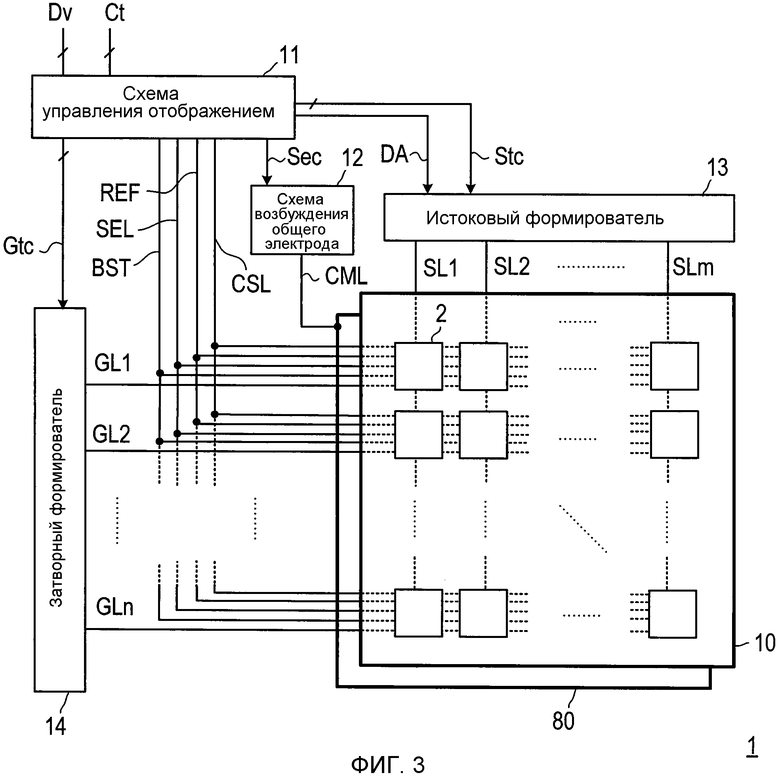

Фиг. 3 - структурная схема, показывающая один из примеров схематической конфигурации устройства отображения по настоящему изобретению.

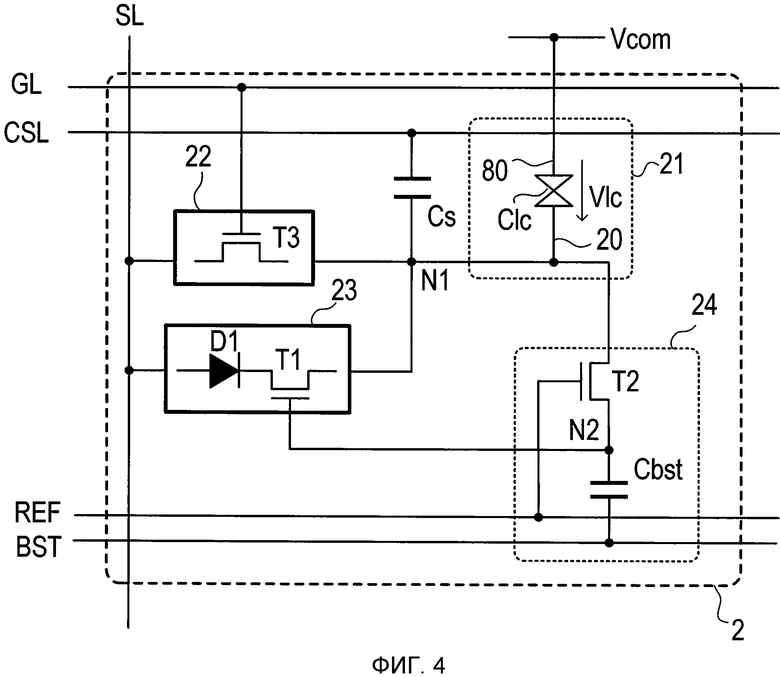

Фиг. 4 - принципиальная схема, показывающая базовую схемную конфигурацию схемы пикселя по настоящему изобретению.

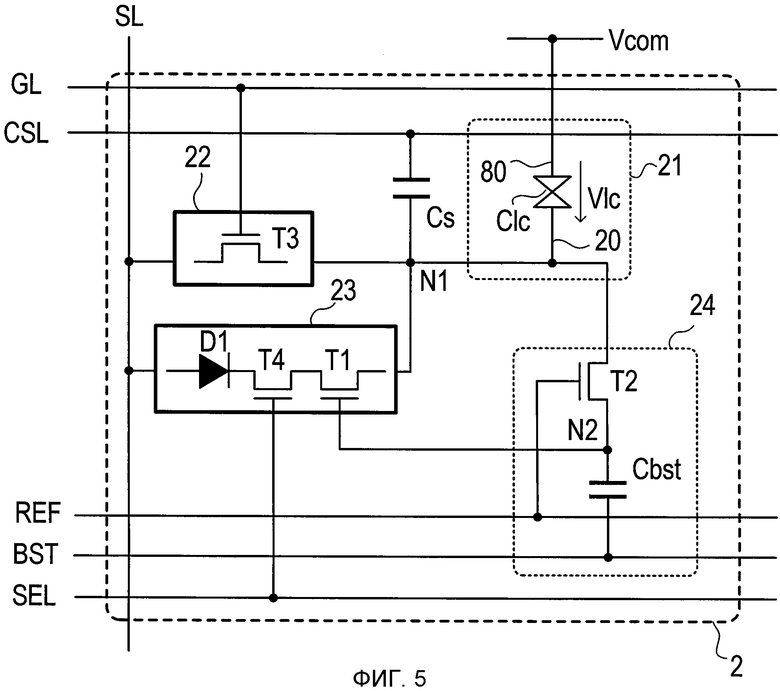

Фиг. 5 - принципиальная схема, показывающая еще одну базовую схемную конфигурацию схемы пикселя по настоящему изобретению.

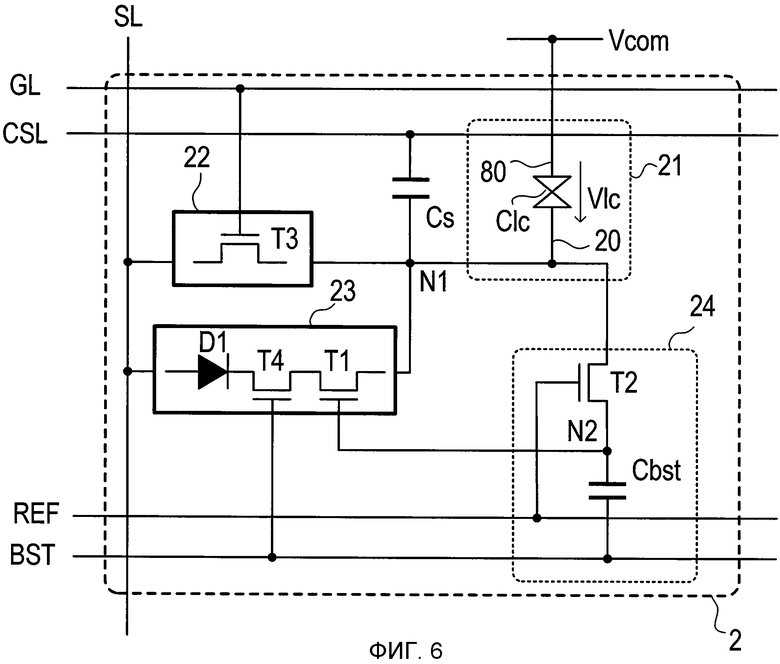

Фиг. 6 - принципиальная схема, показывающая еще одну базовую схемную конфигурацию схемы пикселя по настоящему изобретению.

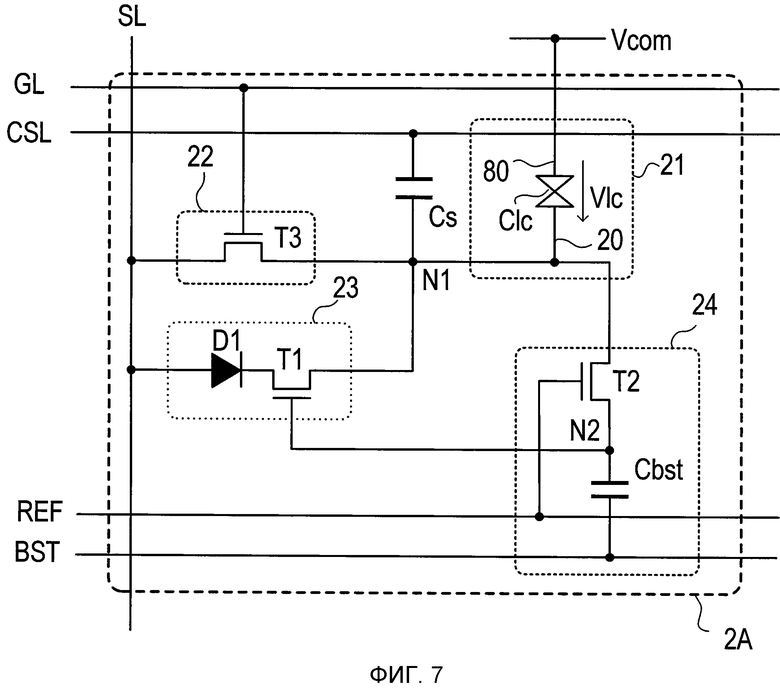

Фиг. 7 - принципиальная схема, показывающая пример схемной конфигурации первого типа из числа схем пикселя по настоящему изобретению.

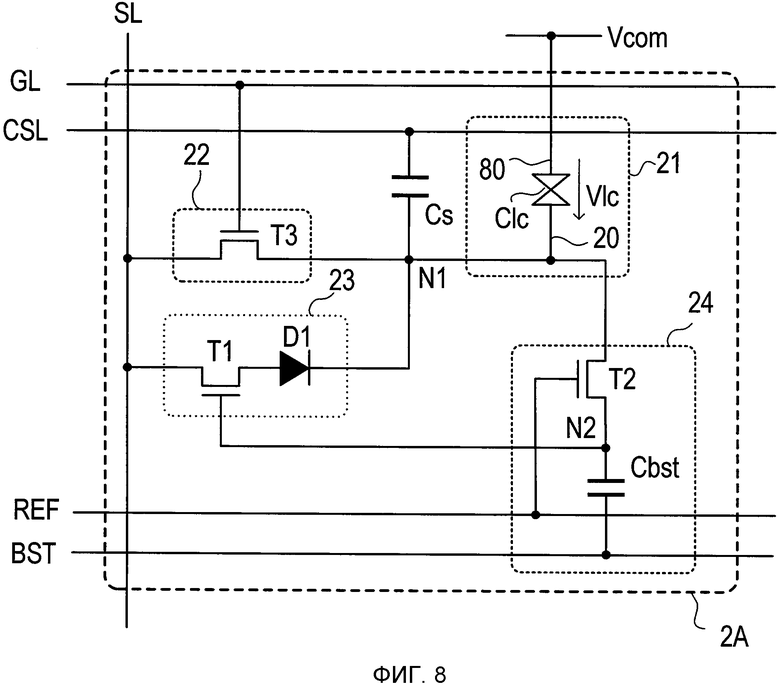

Фиг. 8 - принципиальная схема, показывающая еще один пример схемной конфигурации первого типа из числа схем пикселя по настоящему изобретению.

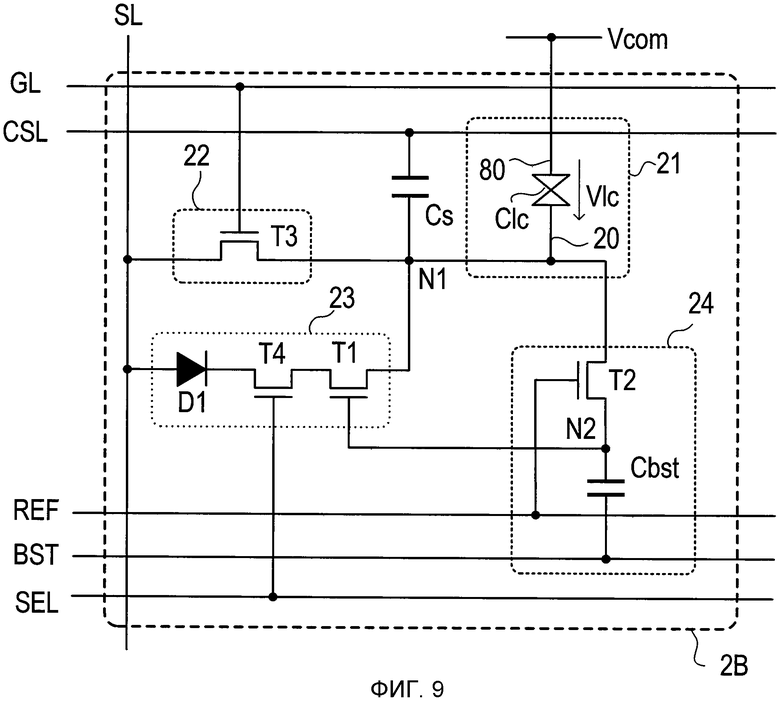

Фиг. 9 - принципиальная схема, показывающая пример схемной конфигурации второго типа из числа схем пикселя по настоящему изобретению.

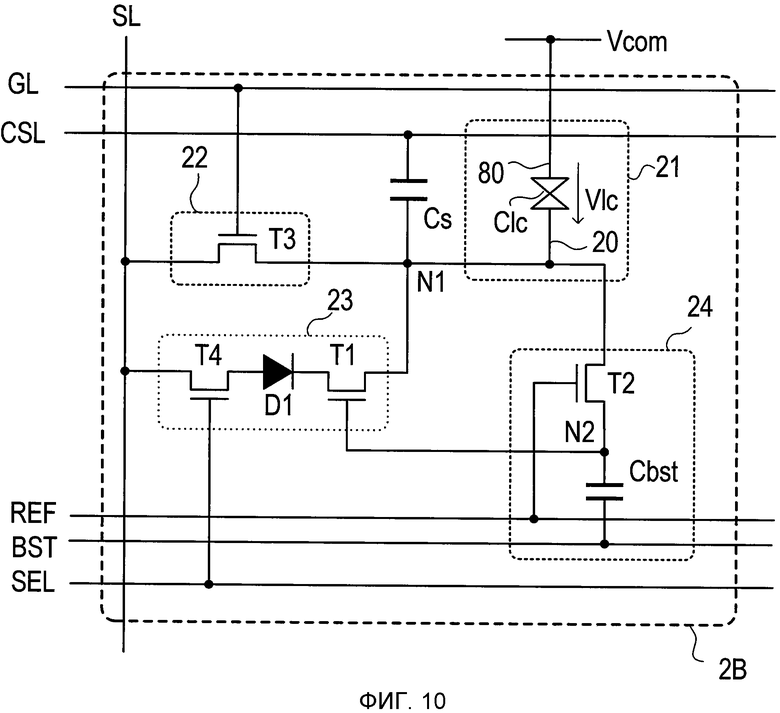

Фиг. 10 - принципиальная схема, показывающая пример схемной конфигурации второго типа из числа схем пикселя по настоящему изобретению.

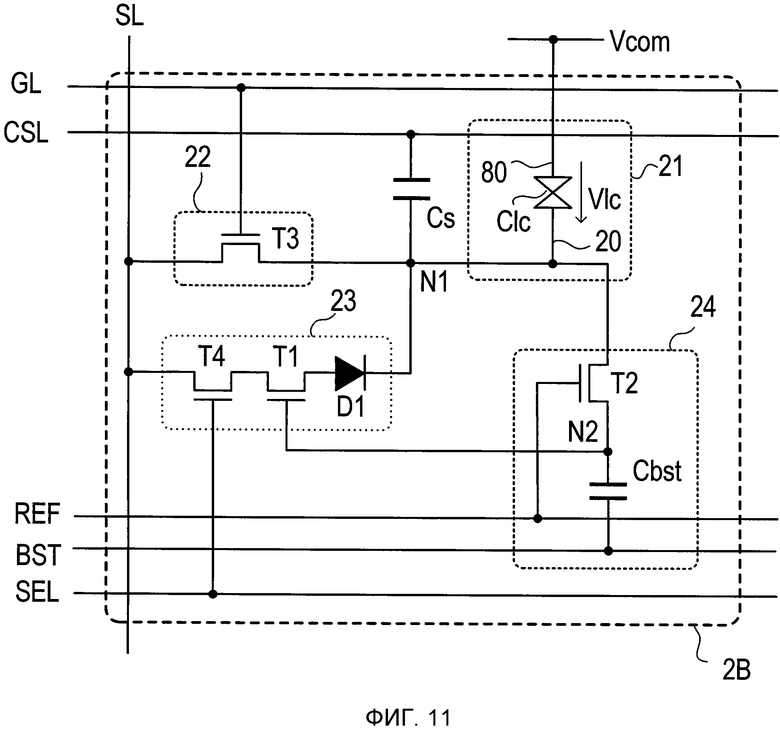

Фиг. 11 - принципиальная схема, показывающая пример схемной конфигурации второго типа из числа схем пикселя по настоящему изобретению.

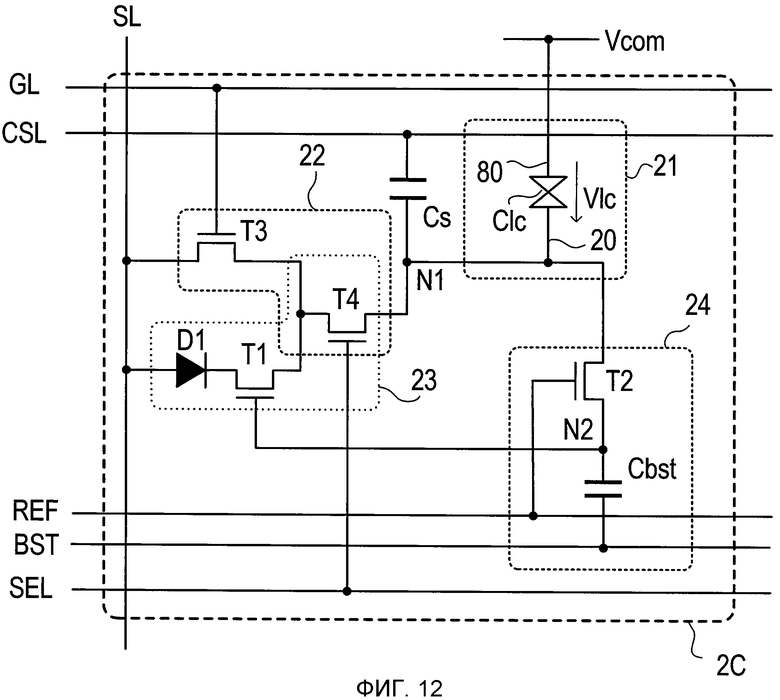

Фиг. 12 - принципиальная схема, показывающая пример схемной конфигурации второго типа из числа схем пикселя по настоящему изобретению.

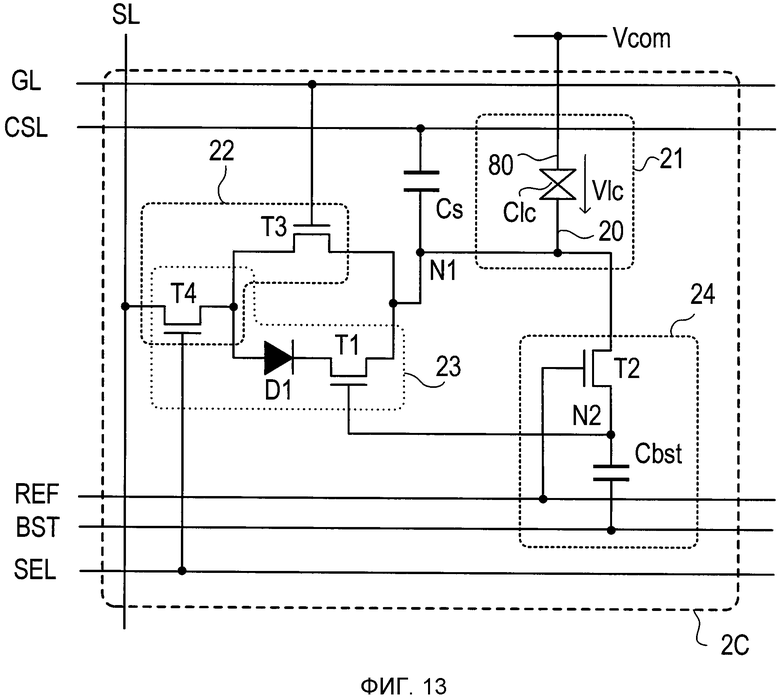

Фиг. 13 - принципиальная схема, показывающая пример схемной конфигурации второго типа из числа схем пикселя по настоящему изобретению.

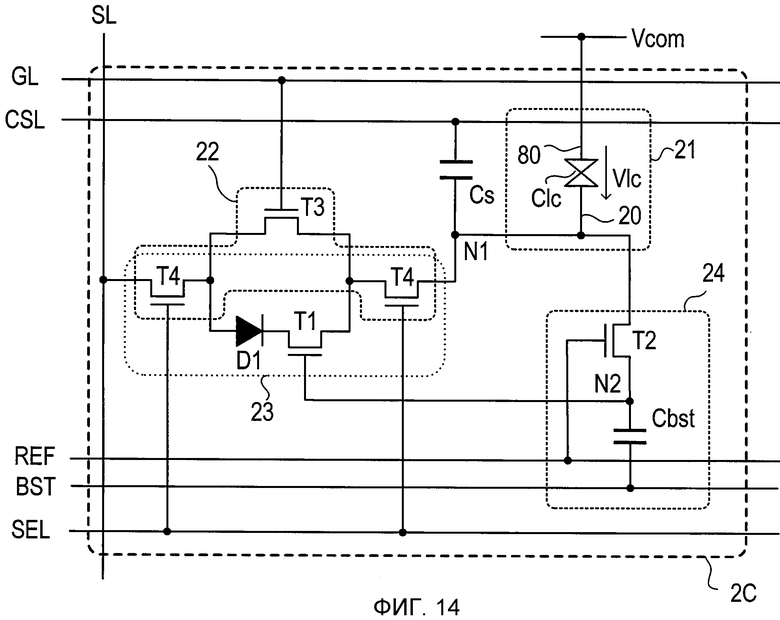

Фиг. 14 - принципиальная схема, показывающая пример схемной конфигурации второго типа из числа схем пикселя по настоящему изобретению.

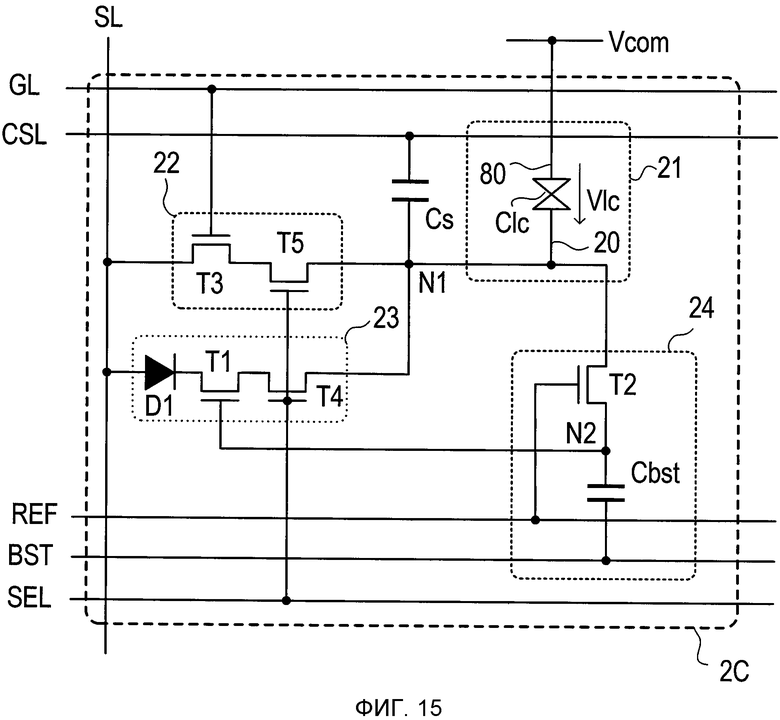

Фиг. 15 - принципиальная схема, показывающая пример схемной конфигурации второго типа из числа схем пикселя по настоящему изобретению.

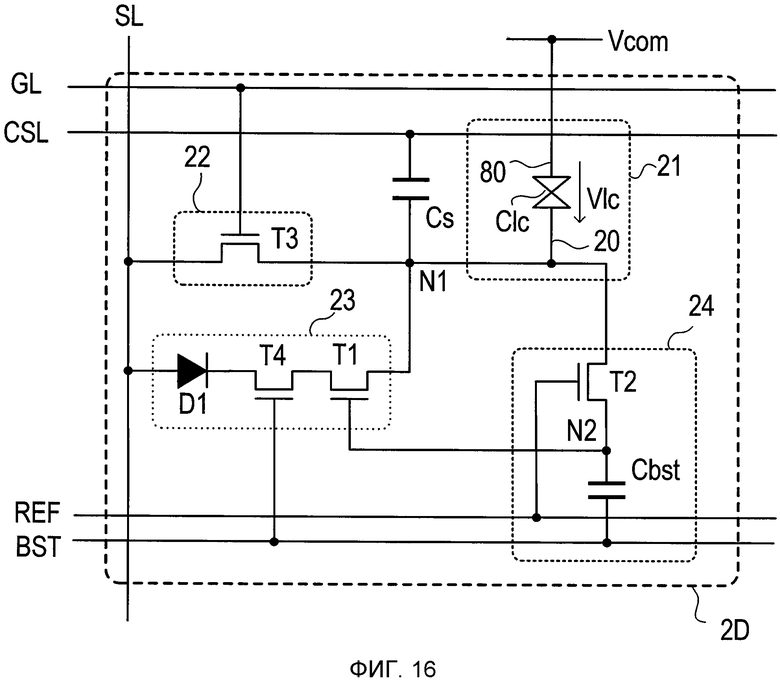

Фиг. 16 - принципиальная схема, показывающая пример схемной конфигурации третьего типа из числа схем пикселя по настоящему изобретению.

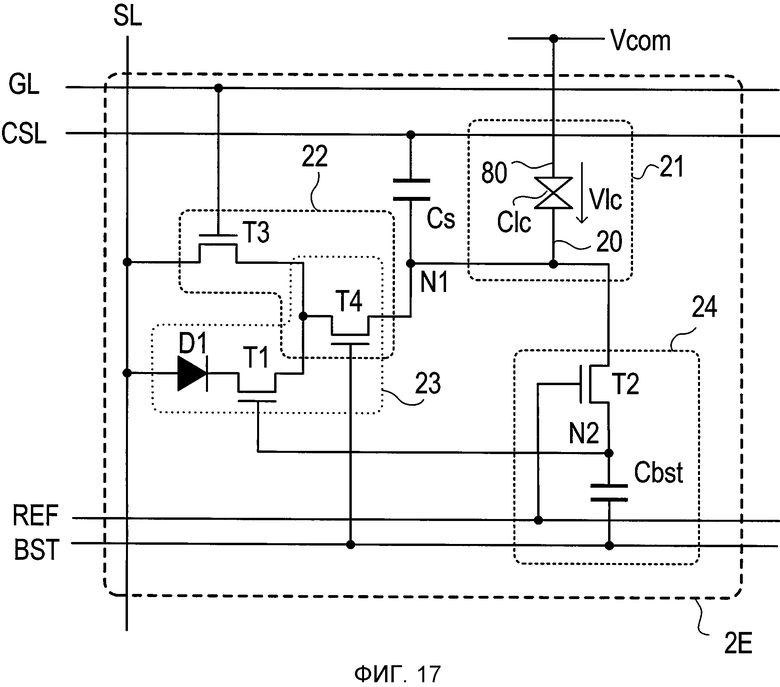

Фиг. 17 - принципиальная схема, показывающая пример схемной конфигурации третьего типа из числа схем пикселя по настоящему изобретению.

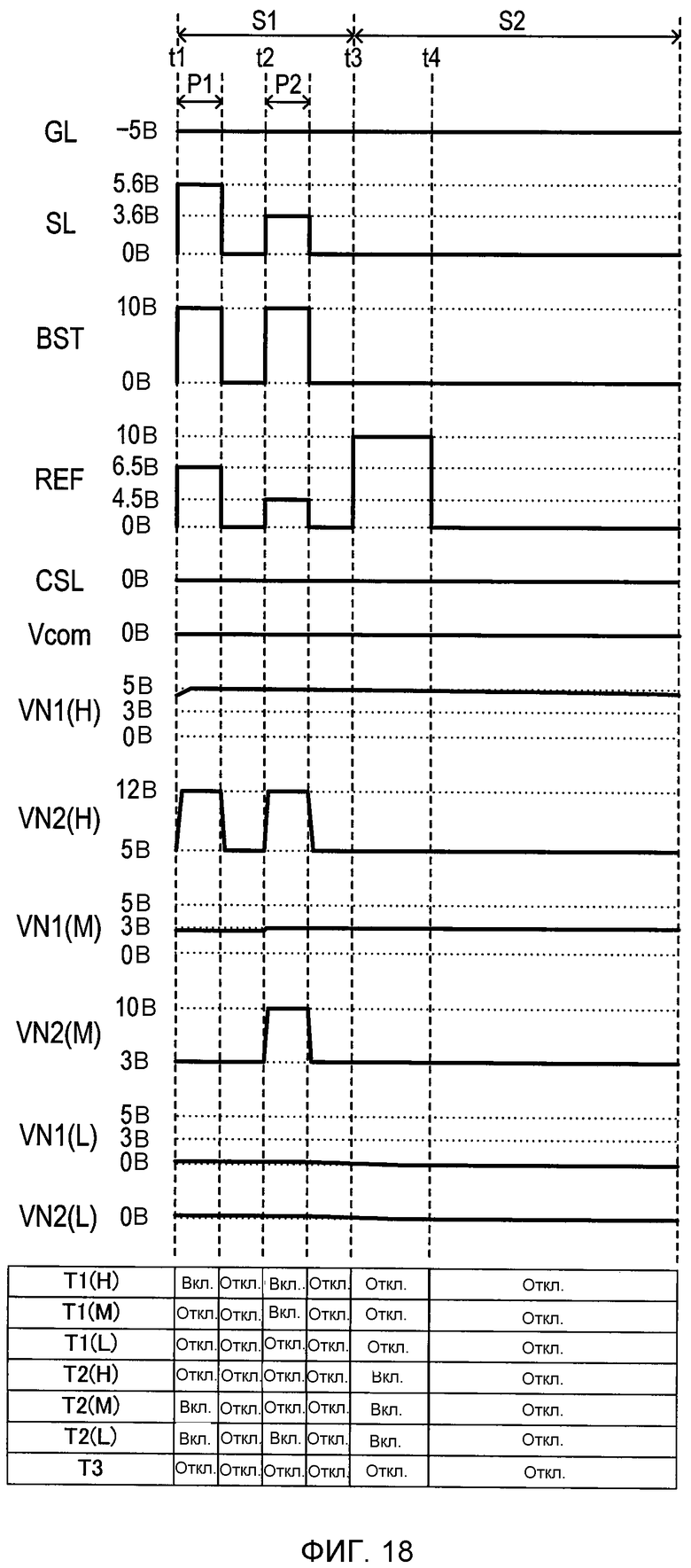

Фиг. 18 - временная диаграмма действия самообновления согласно второму варианту осуществления в схемах пикселя первого и третьего типа.

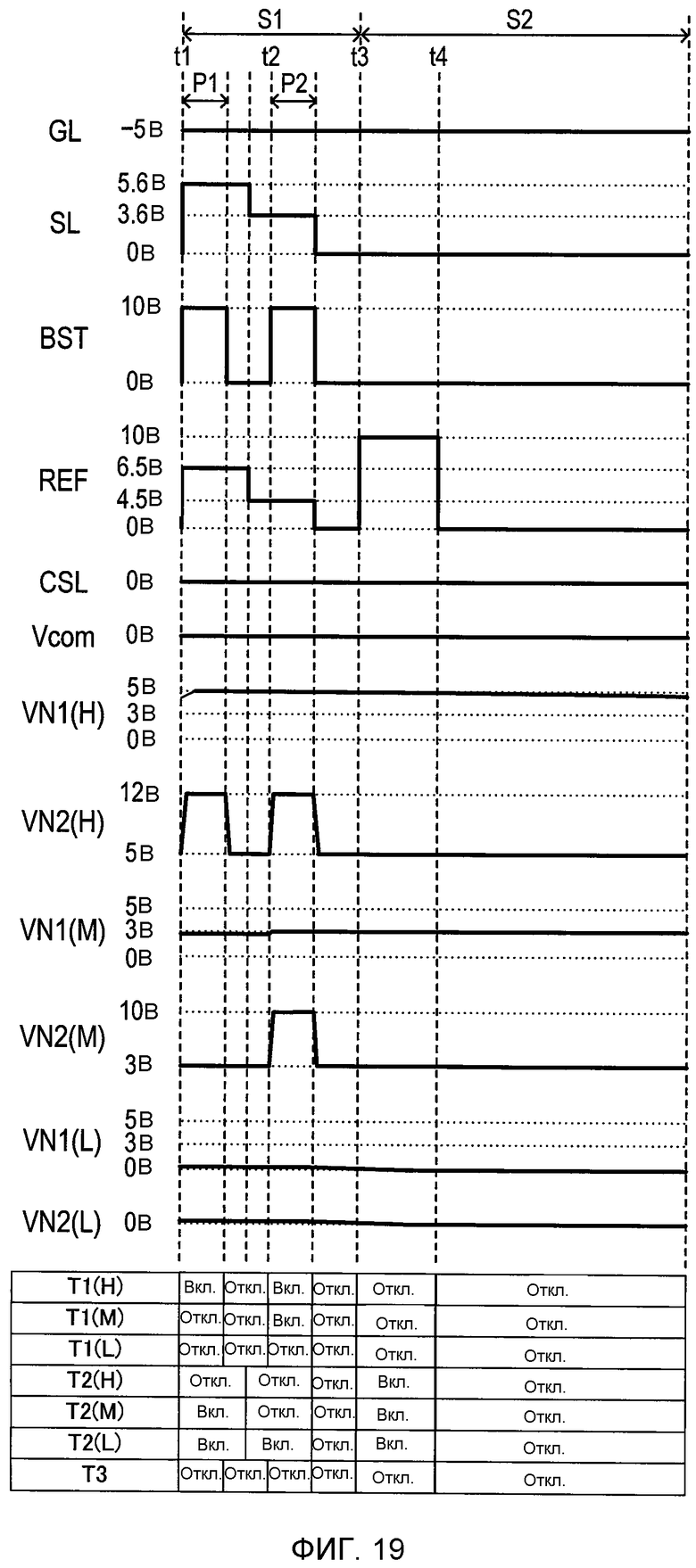

Фиг. 19 - еще одна временная диаграмма действия самообновления согласно второму варианту осуществления в схемах пикселя первого и третьего типа.

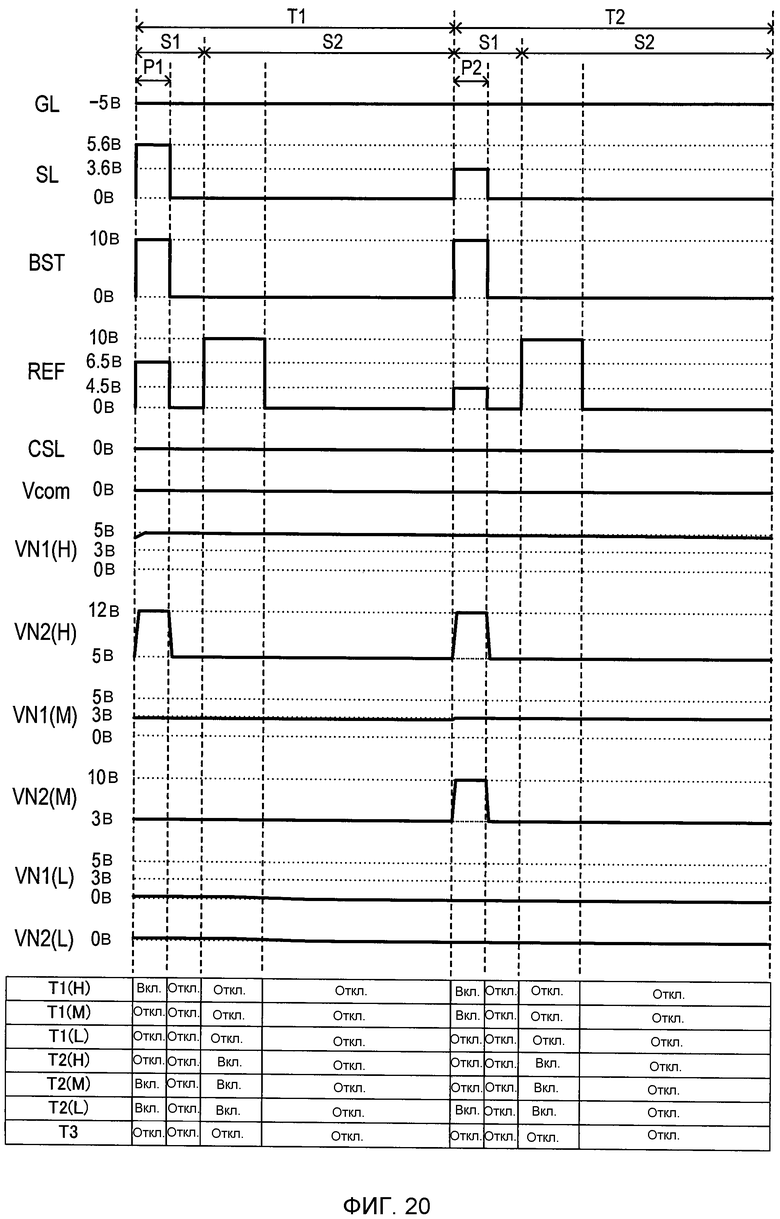

Фиг. 20 - еще одна временная диаграмма действия самообновления согласно второму варианту осуществления в схемах пикселя первого и третьего типа.

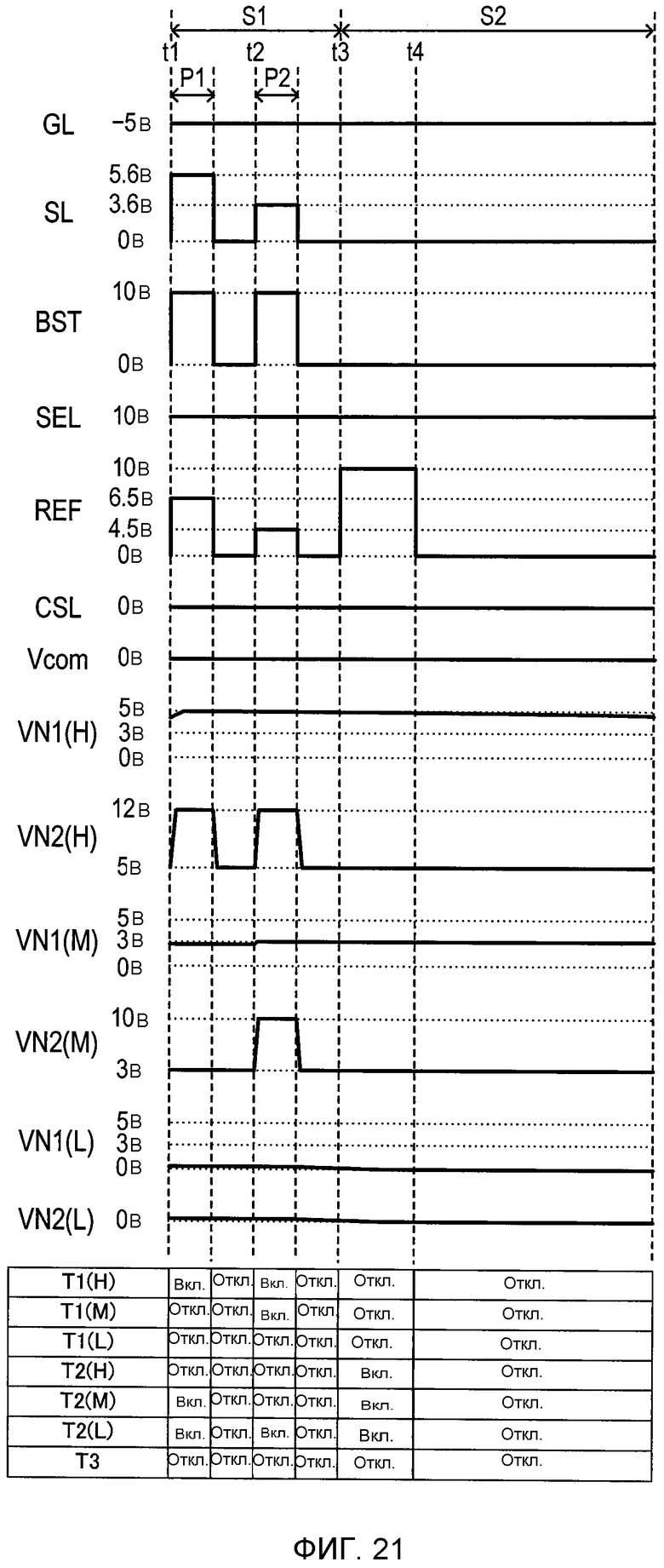

Фиг. 21 - временная диаграмма действия самообновления согласно второму варианту осуществления в схеме пикселя второго типа.

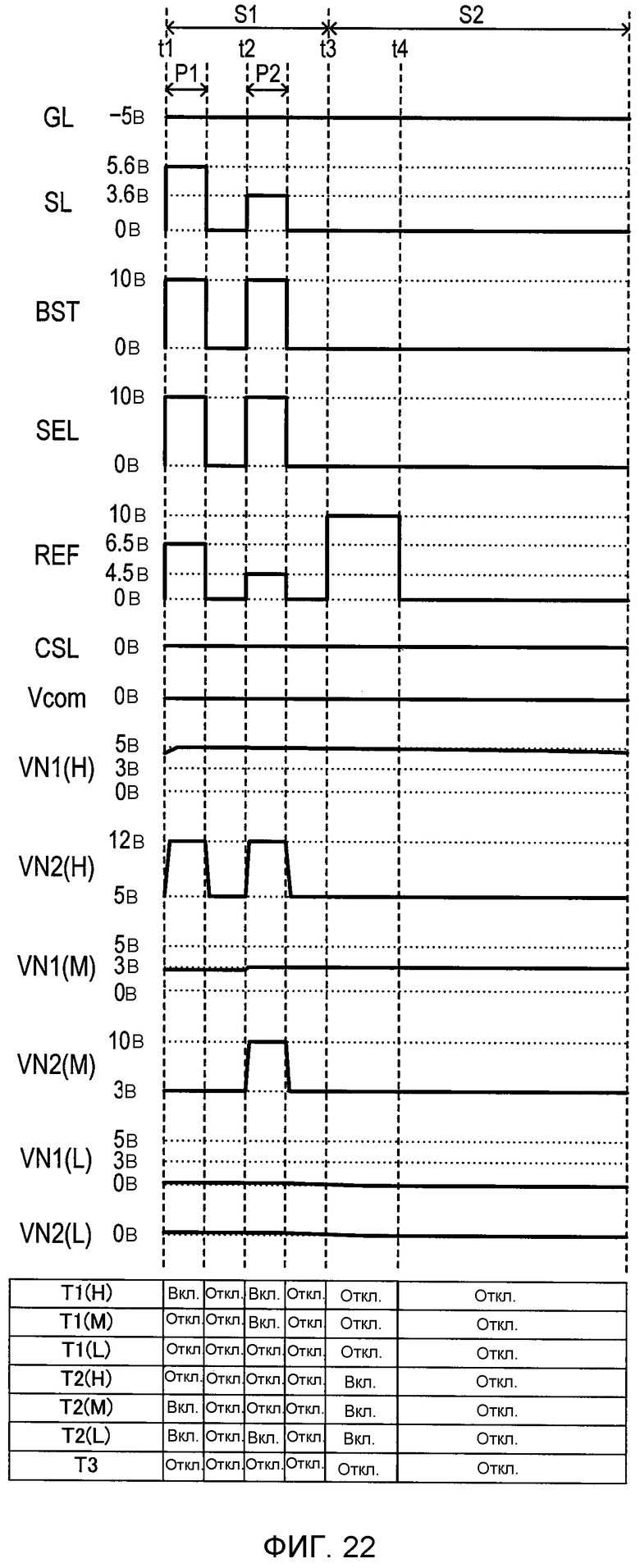

Фиг. 22 - еще одна временная диаграмма действия самообновления согласно второму варианту осуществления в схеме пикселя второго типа.

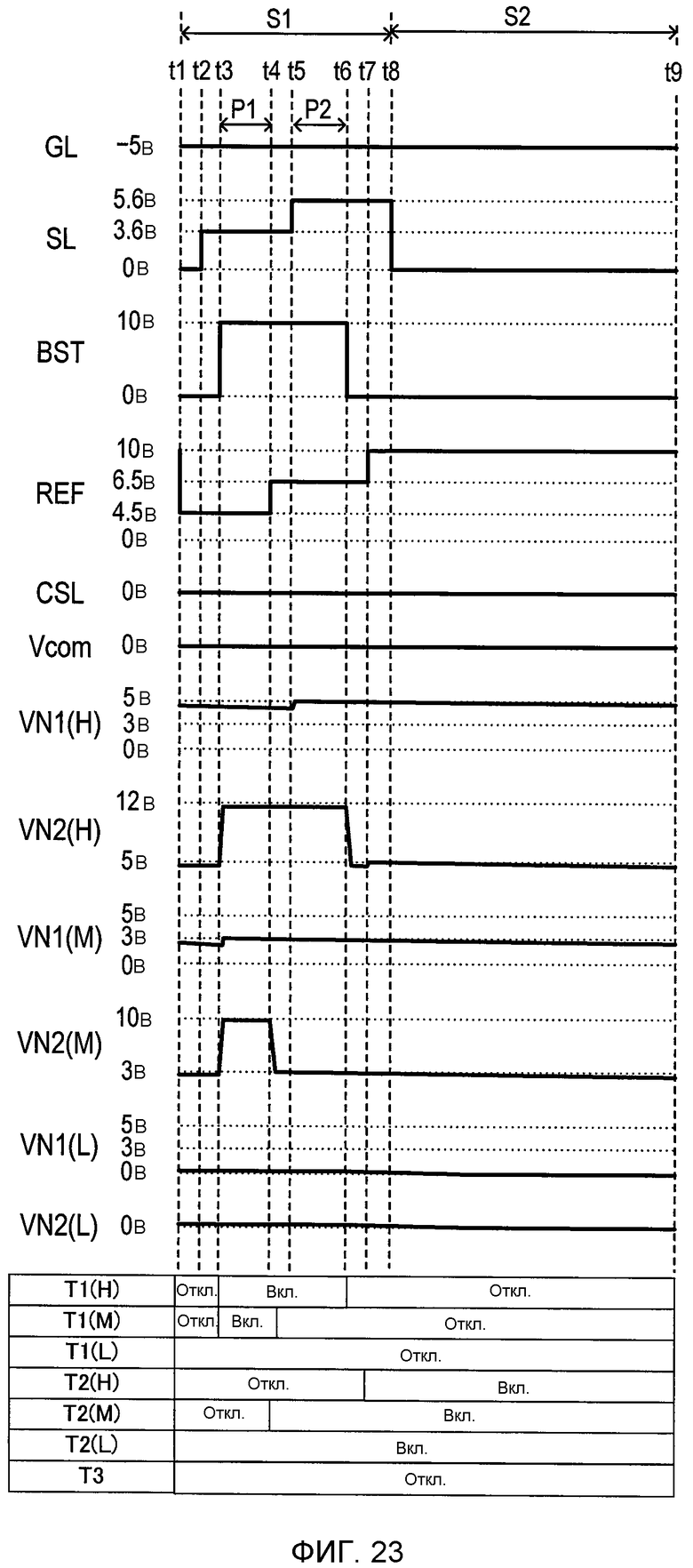

Фиг. 23 - временная диаграмма действия самообновления согласно третьему варианту осуществления в схеме пикселя первого типа.

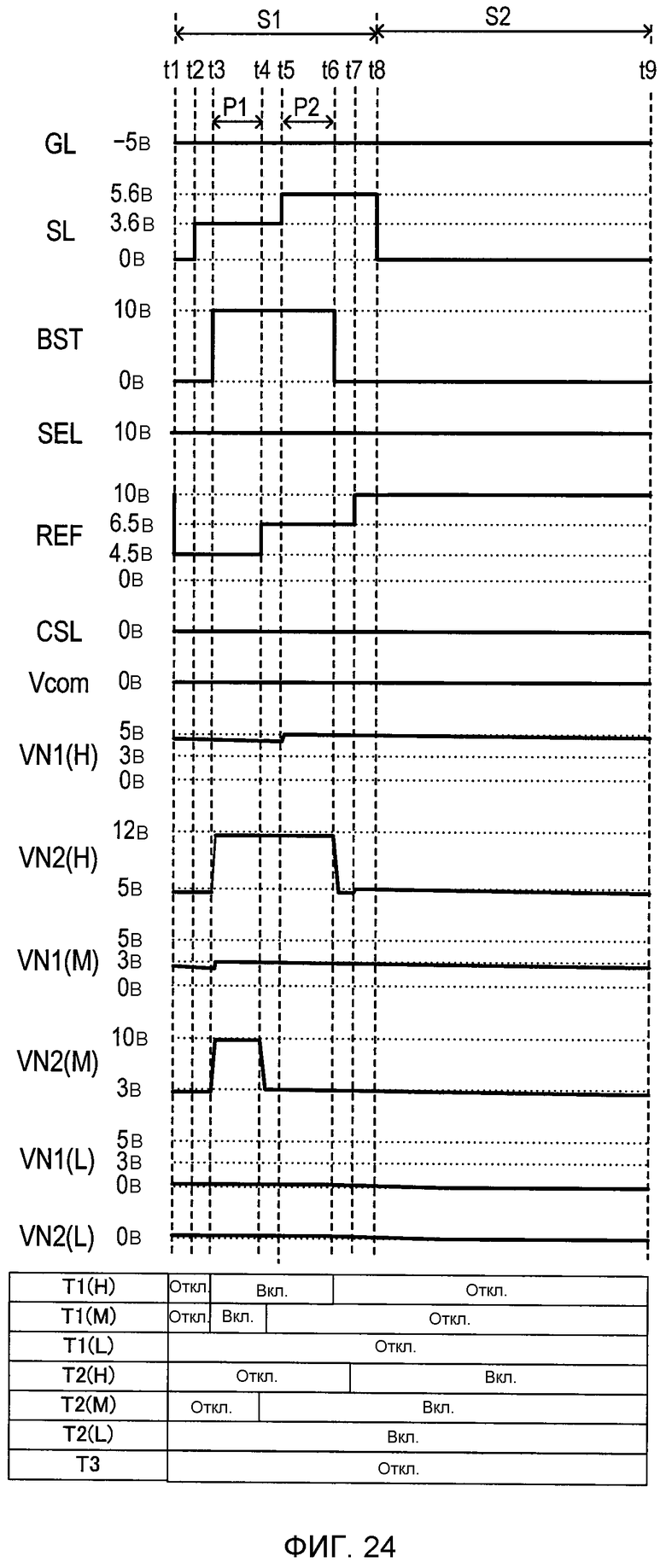

Фиг. 24 - временная диаграмма действия самообновления согласно третьему варианту осуществления в схеме пикселя второго типа.

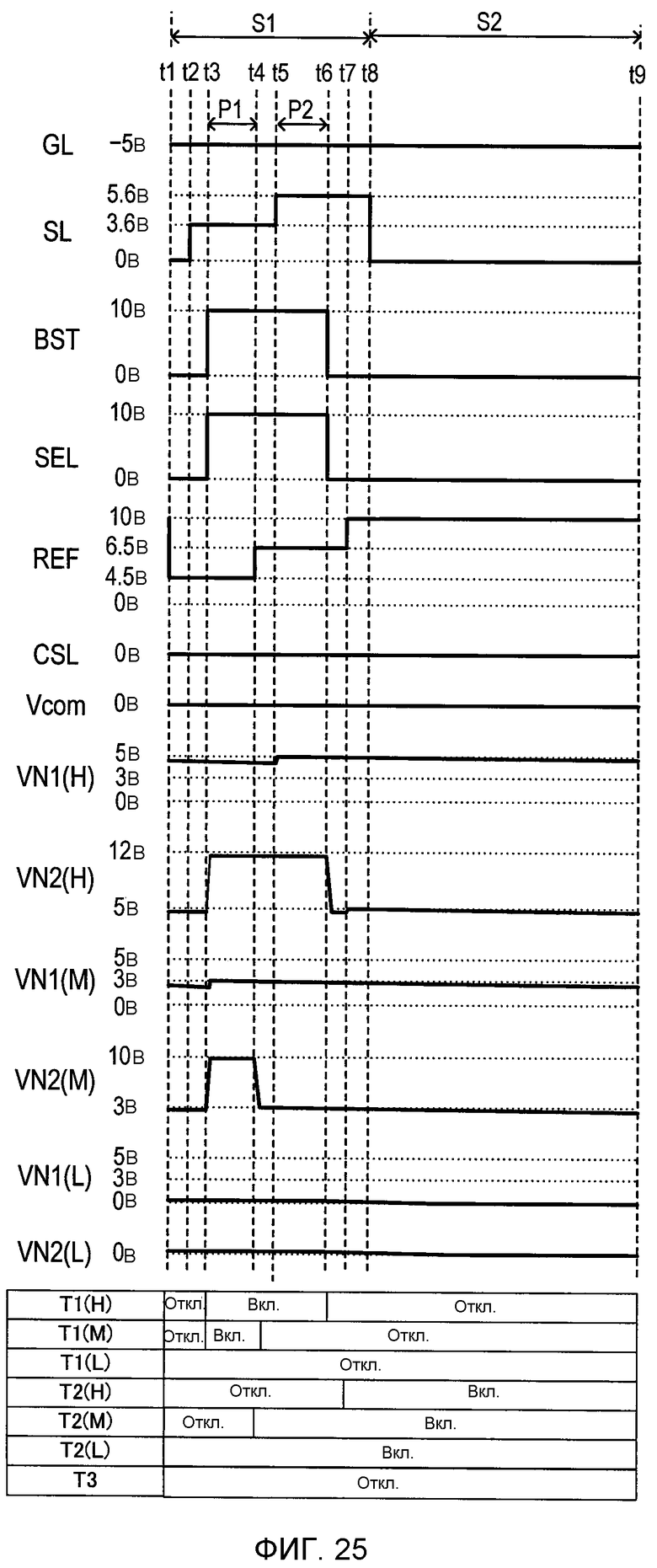

Фиг. 25 - еще одна временная диаграмма действия самообновления согласно третьему варианту осуществления в схеме пикселя второго типа.

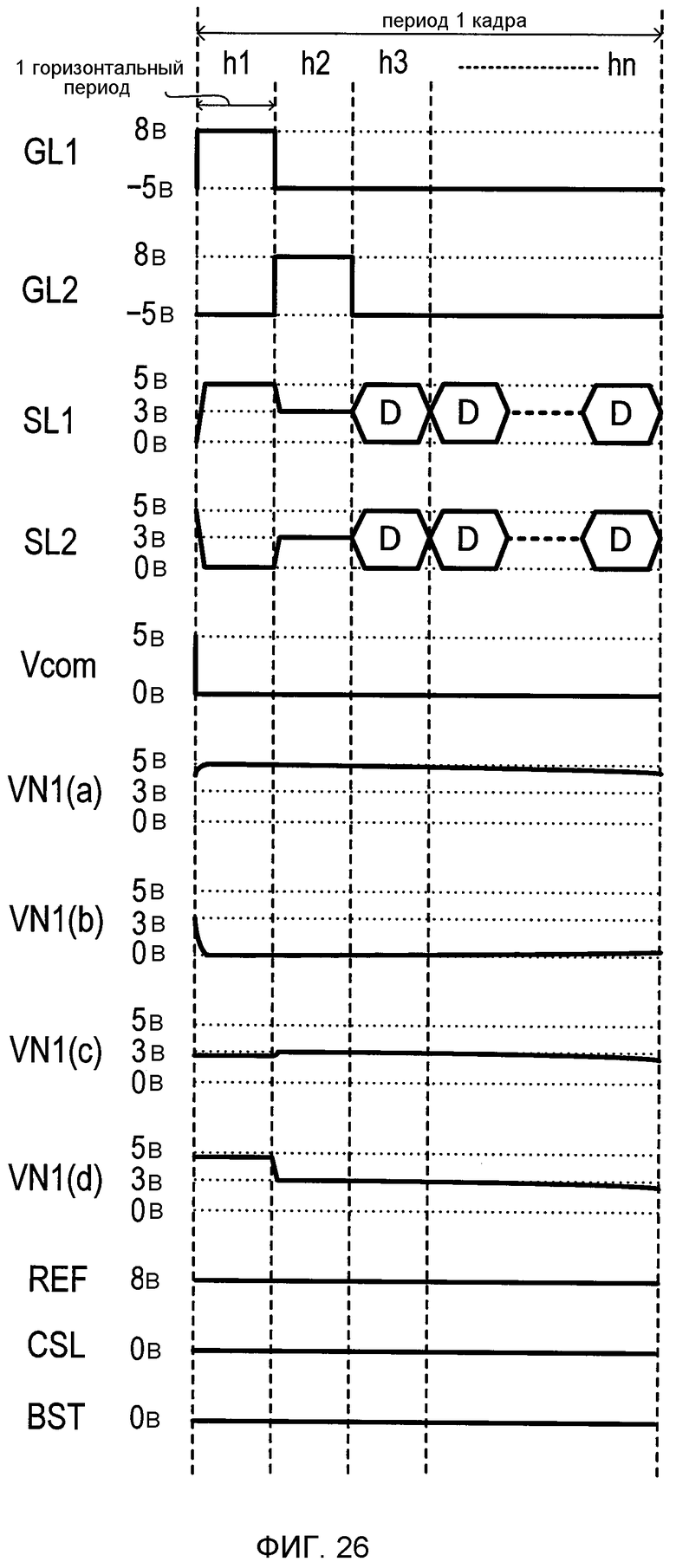

Фиг. 26 - временная диаграмма действия записи в режиме постоянного отображения в схеме пикселя первого типа.

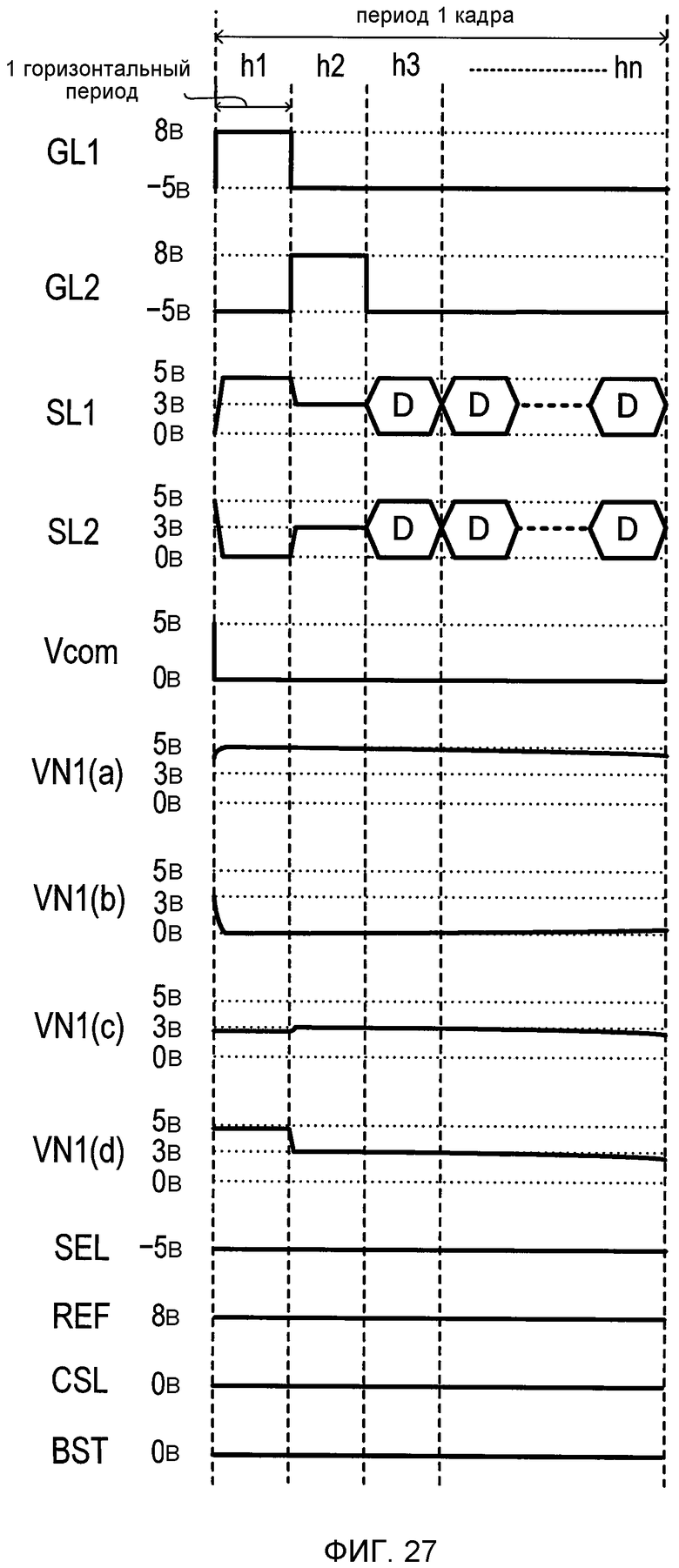

Фиг. 27 - временная диаграмма действия записи в режиме постоянного отображения в схеме пикселя второго типа.

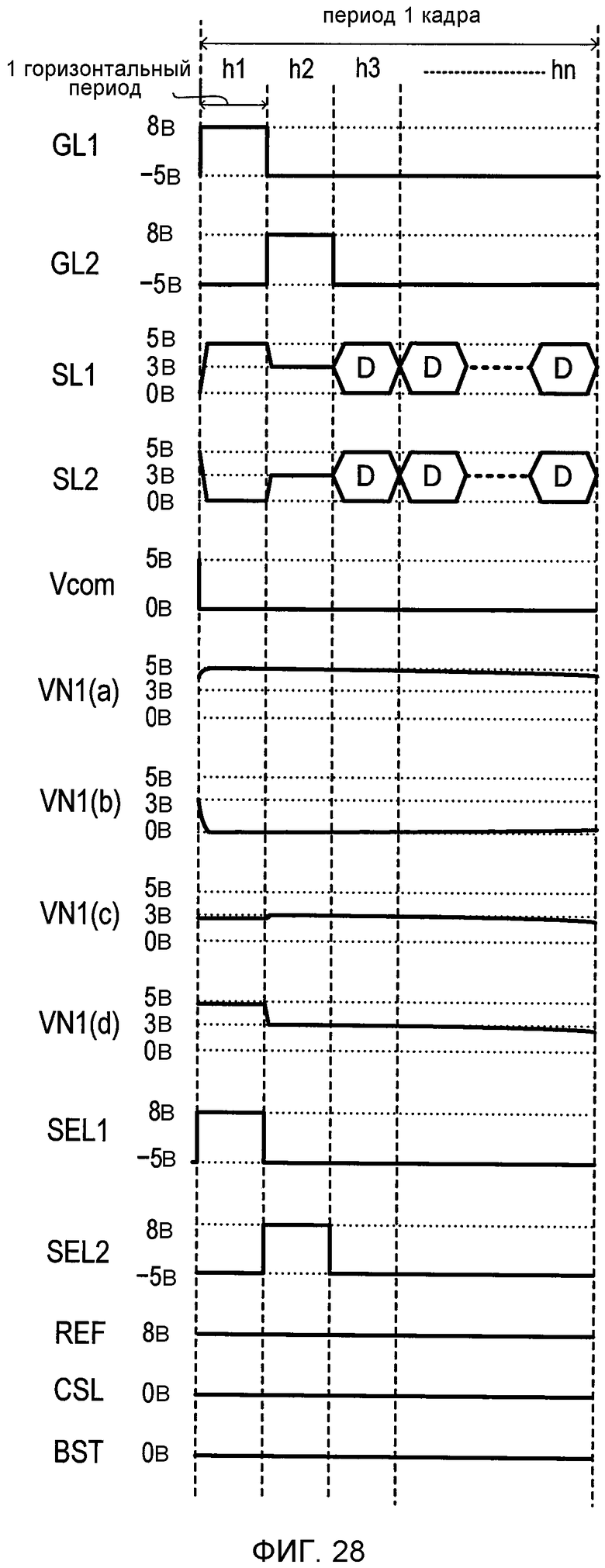

Фиг. 28 - временная диаграмма действия записи в режиме постоянного отображения в схеме пикселя второго типа.

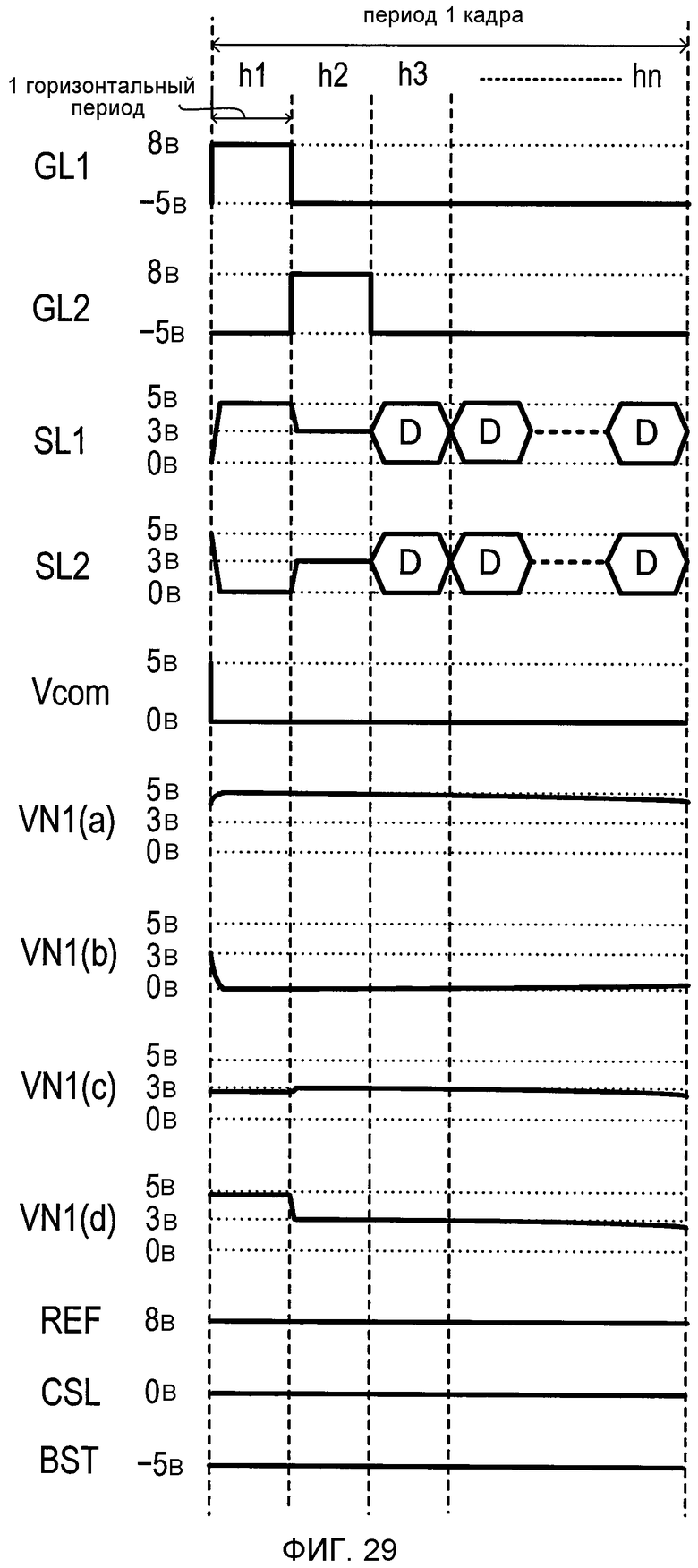

Фиг. 29 - временная диаграмма действия записи в режиме постоянного отображения в схеме пикселя третьего типа.

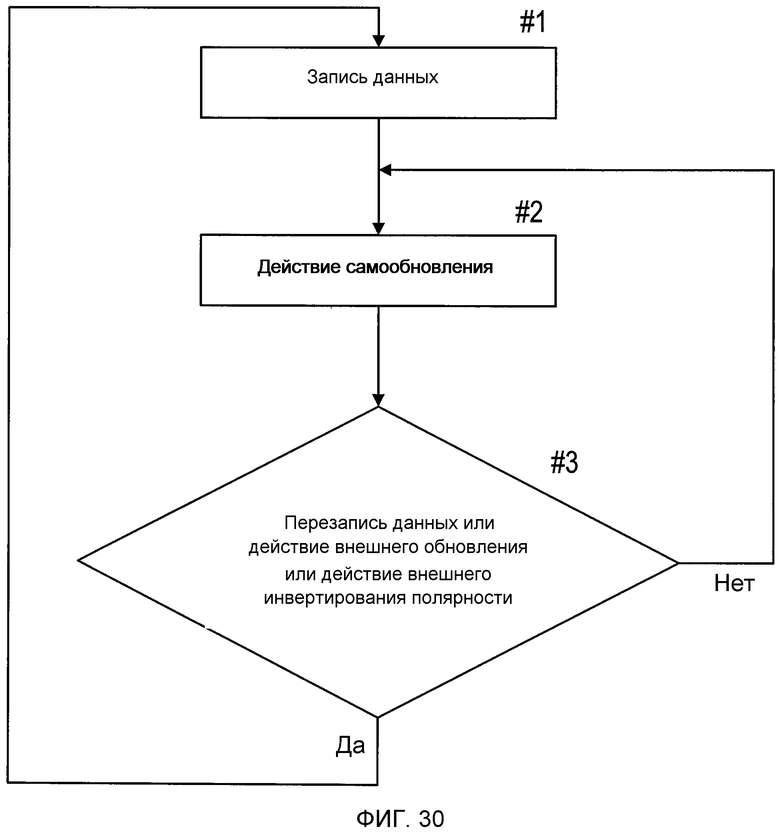

Фиг. 30 - блок-схема последовательности операций способа, показывающая процедуру действия записи и действия самообновления в режиме постоянного отображения.

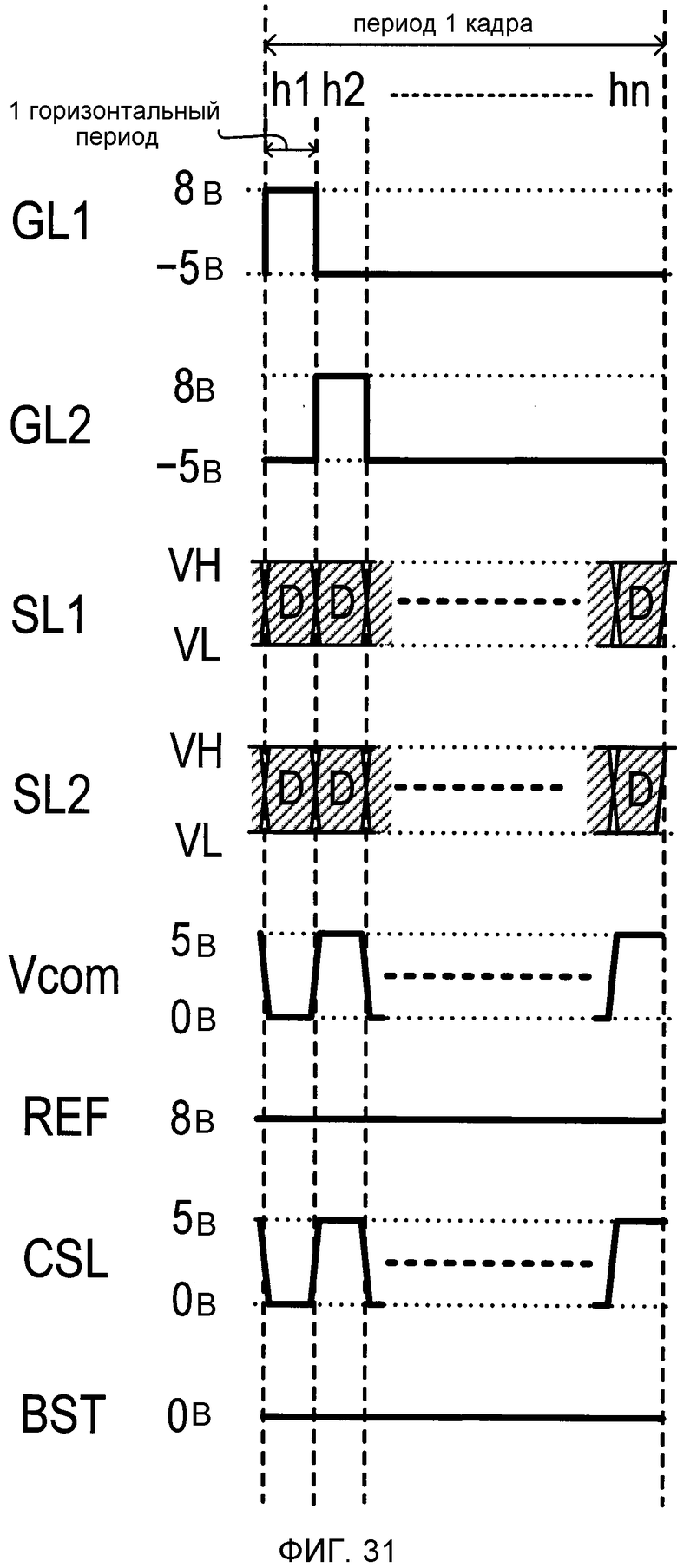

Фиг. 31 - один из примеров временной диаграммы действия записи в режиме нормального отображения в схеме пикселя первого типа.

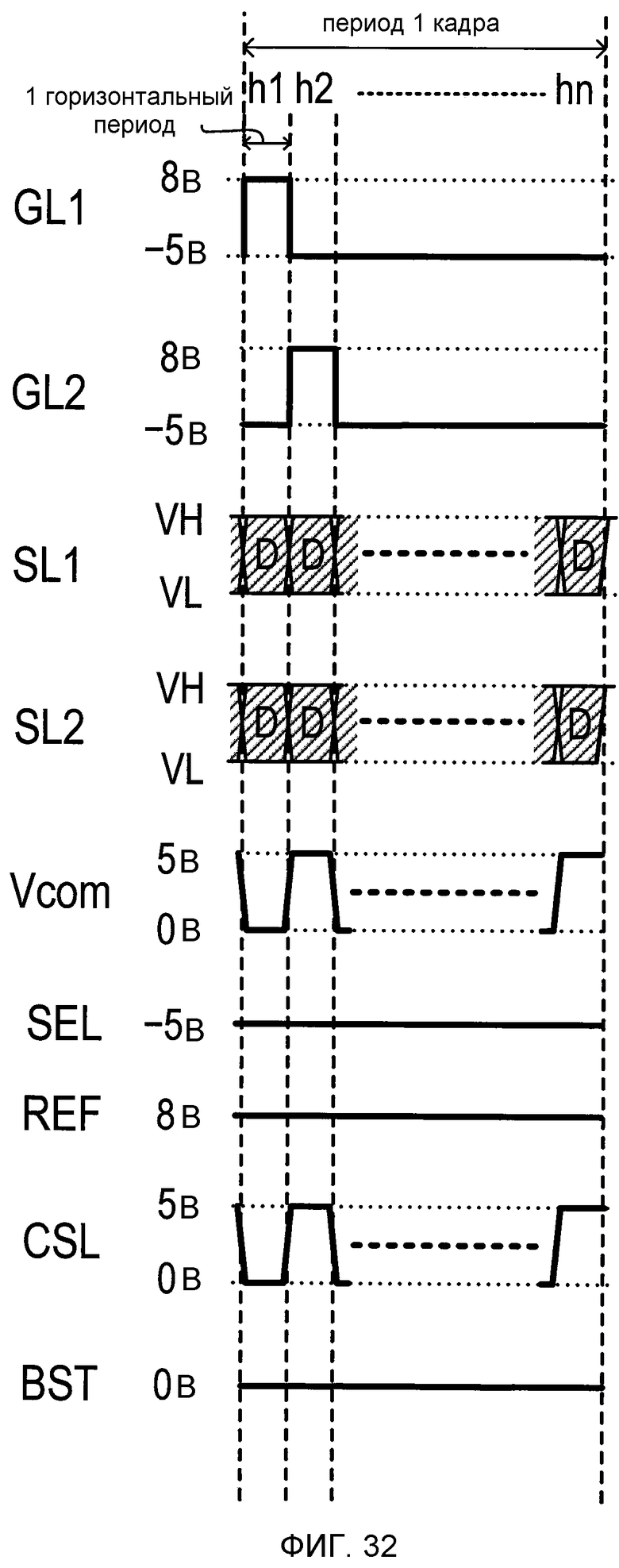

Фиг. 32 - один из примеров временной диаграммы действия записи в режиме нормального отображения в схеме пикселя второго типа.

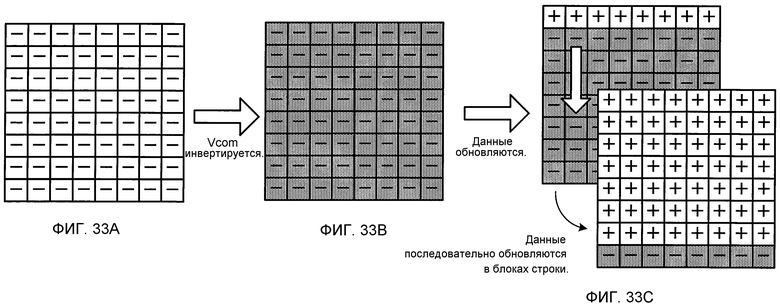

Фиг. 33 - схема концептуального представления для описания проблемы, предполагаемой при действии записи в режиме постоянного отображения.

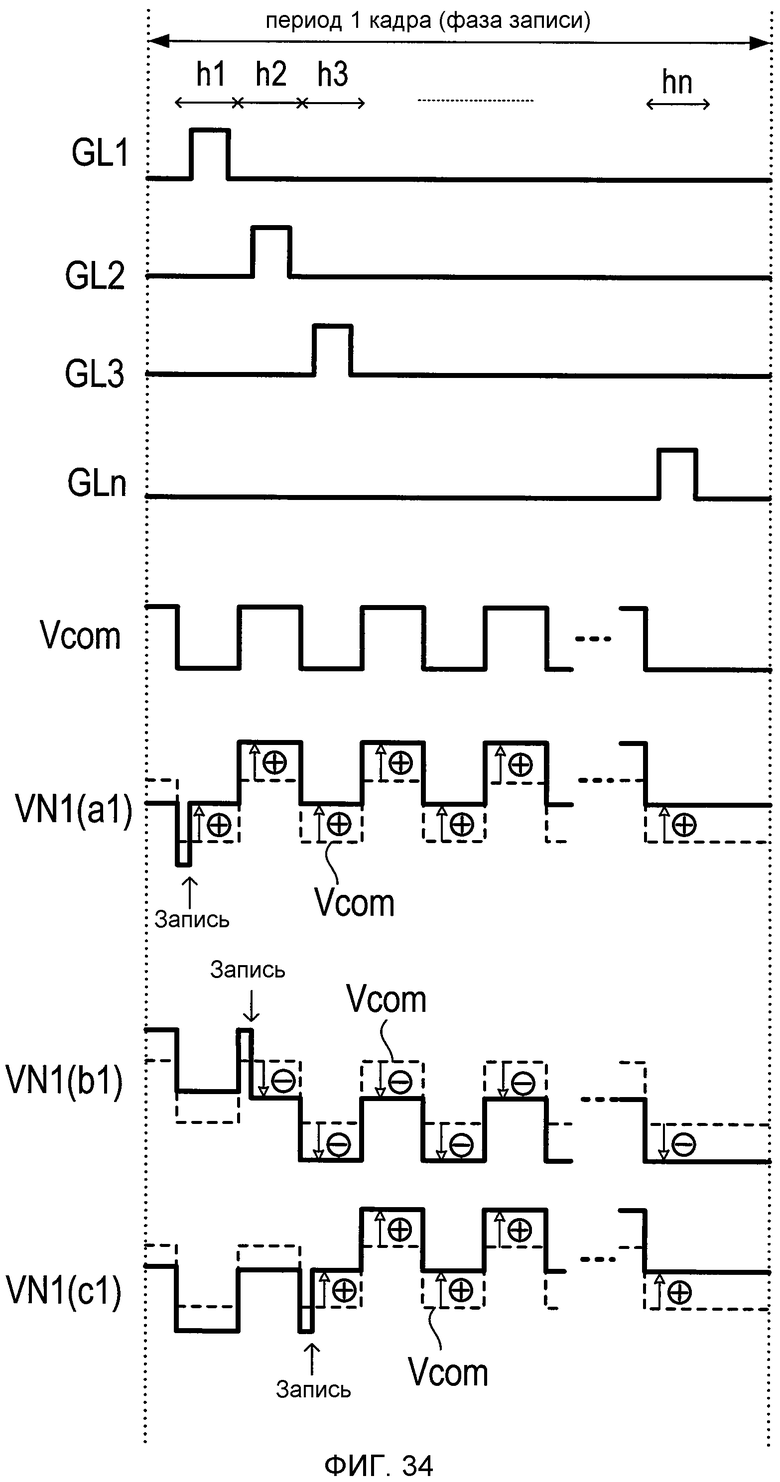

Фиг. 34 - один из примеров временной диаграммы действия записи в режиме постоянного отображения в седьмом варианте осуществления.

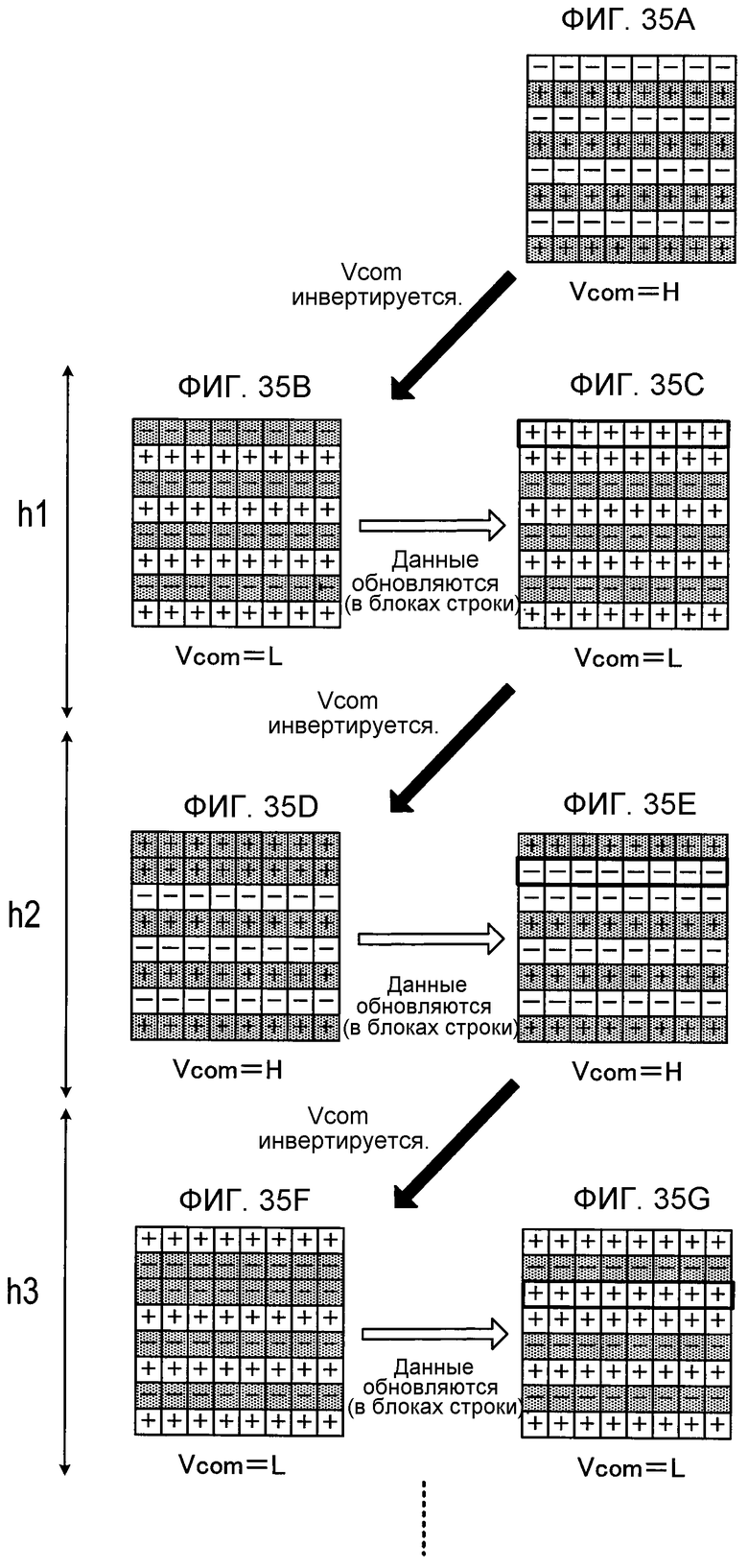

Фиг. 35 - схема концептуального представления, показывающая изменение полярности, когда выполняется действие записи в седьмом варианте осуществления.

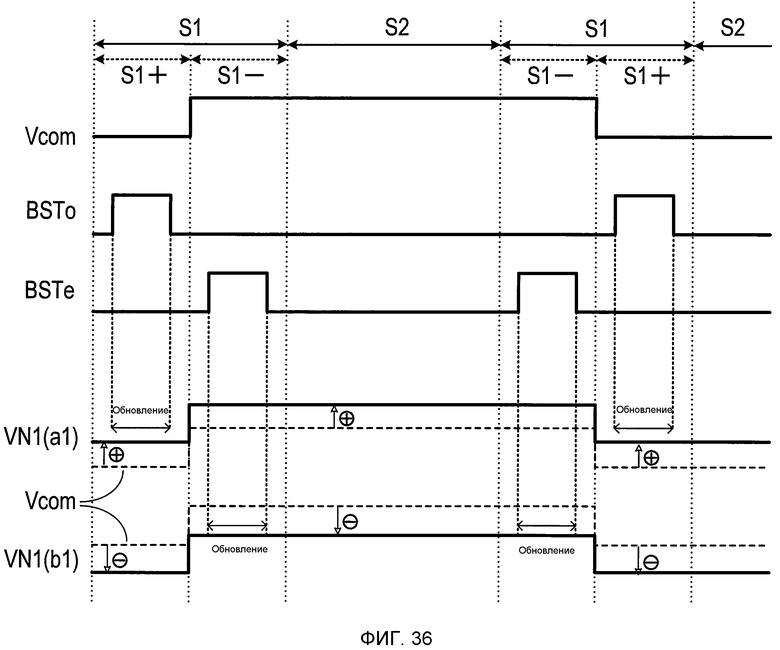

Фиг. 36 - временная диаграмма действия самообновления в седьмом варианте осуществления.

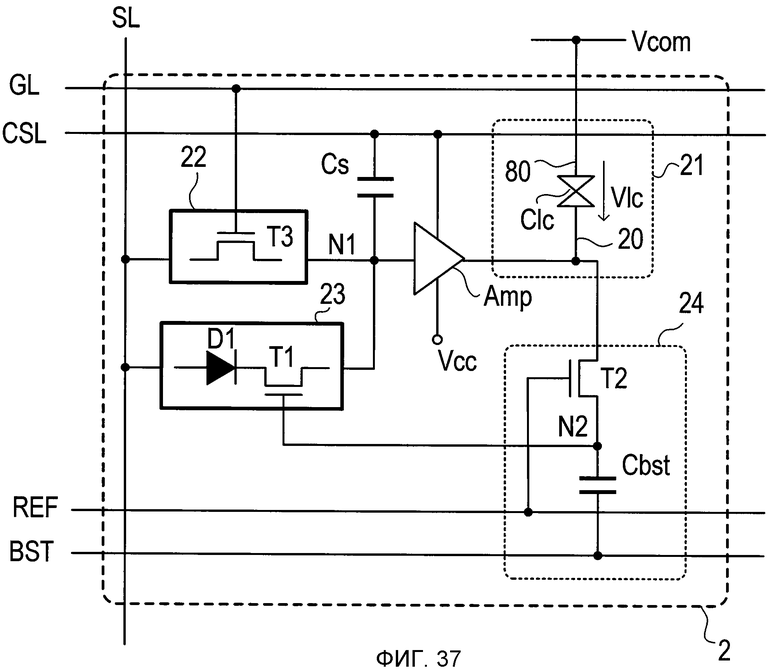

Фиг. 37 - принципиальная схема, показывающая еще одну другую базовую схемную конфигурацию схемы пикселя в настоящем изобретении.

Фиг. 38 - принципиальная схема, показывающая еще одну другую базовую схемную конфигурацию схемы пикселя в настоящем изобретении.

Фиг. 39 - эквивалентная принципиальная схема у схемы пикселя обычного жидкокристаллического устройства отображения с активной матрицей.

Фиг. 40 - структурная схема, показывающая пример схемной компоновки жидкокристаллического устройства отображения с активной матрицей, имеющего m×n пикселей.

ВАРИАНТ ДЛЯ ОСУЩЕСТВЛЕНИЯ ИЗОБРЕТЕНИЯ

В дальнейшем будет дано описание каждого варианта осуществления схемы пикселя и устройства отображения по настоящему изобретению со ссылкой на чертежи. В дополнение, такие же компоненты, как на фиг. 39 и 40, помечены идентичными ссылками.

[Первый вариант осуществления]

В первом варианте осуществления будет дано описание конфигураций устройства отображения по настоящему изобретению (в дальнейшем указываемого ссылкой просто как «устройство отображения») и схемы пикселя по настоящему изобретению (в дальнейшем указываемой ссылкой просто как «схема пикселя»).

<<Устройство отображения>>

Фиг. 1 показывает схематическую конфигурацию устройства 1 отображения. Устройство 1 отображения включает в себя подложку 10 активной матрицы, противоположный электрод 80, схему 11 управления отображением, схему 12 возбуждения противоположного электрода, истоковый формирователь 13, затворный формирователь 14 и различные сигнальные линии, которые будут описаны ниже. На подложке 10 активной матрицы множество схем 2 пикселя скомпонованы в направлениях строки и столбца соответственно и сформирован массив схем пикселя.

В дополнение, схема 2 пикселя показана в качестве блока на фиг. 1, с тем чтобы предотвратить то, что чертеж становится сложным. Более того, в описательных целях подложка 10 активной матрицы показана поверх противоположного электрода 80, с тем чтобы сделать ясным, что различные сигнальные линии сформированы на подложке 10 активной матрицы.

Согласно этому варианту осуществления устройство 1 отображения может осуществлять экранное отображение в двух режимах отображения, таких как режим нормального отображения и режим постоянного отображения, с одной и той же схемой 2 пикселя. В режиме нормального отображения движущееся изображение или неподвижное изображение отображаются в полном цвете и проницаемое жидкокристаллическое отображение производится с подсветкой. Между тем в режиме постоянного отображения в этом варианте осуществления три или более оттенков отображаются блоком схем пикселя, а три смежные схемы 2 пикселя выделены под три основных цвета (R, G, B (красный, зеленый, синий)) соответственно. Например, в случае, где количество оттенков имеет значение 3, отображаются 27 цветов, а в случае, где количество оттенков имеет значение 4, отображаются 64 цвета. Однако предполагаемое количество оттенков является меньшим, чем у режима нормального отображения.

В дополнение, в режиме постоянного отображения количество цветов отображения может быть увеличено модуляцией покрытия площади посредством дополнительного комбинирования множества наборов из трех смежных схем пикселя. Более того, режим постоянного отображения в этом варианте осуществления может использоваться при проницаемом жидкокристаллическом отображении и отражательном жидкокристаллическом отображении.

В последующем описании в описательных целях минимальная единица отображения, соответствующая одной схеме 2 пикселя, указывается ссылкой как «пиксель», а «пиксельные данные», которые должны записываться в каждую схему пикселя, являются данными оттенка каждого цвета в случае цветного отображения с тремя основными цветами (R, B, G). В случае цветного отображения, которое включает в себя данные яркости множества оттенков в дополнение к основным цветам, данные яркости также включены в пиксельные данные.

Фиг. 2 - схематический вид структуры в поперечном разрезе, показывающий взаимное расположение между подложкой 10 активной матрицы и противоположным электродом 80, и показывает конструкцию части 21 элемента отображения (обратитесь к фиг. 4), служащей в качестве компонента схемы 2 пикселя. Подложка 10 активной матрицы является светопроницаемой прозрачной подложкой, состоящей из стекла или пластмассы.

Как показано на фиг. 1, каждая из схем 2 пикселя, включающих в себя сигнальные линии, сформирована на подложке 10 активной матрицы. На фиг. 2 пиксельный электрод 20 показан в качестве представляющего компонент схемы 2 пикселя. Пиксельный электрод 20 состоит из светопроницаемого прозрачного проводящего материала, такого как ITO (легированный оловом оксид индия).

Светопроницаемая противоположная подложка 81 скомпонована, с тем чтобы быть противоположной подложке 10 активной матрицы, и жидкокристаллический слой 75 удерживается в зазоре между подложками. Поляризационные пластины (не показаны) прикреплены к наружной поверхности каждой подложки.

Жидкокристаллический слой 75 герметизирован герметизирующим материалом 74 в окружающей зоне обеих подложек. На противоположной подложке 81 противоположный электрод 80, состоящий из светопроницаемого прозрачного проводящего материала, такого как ITO, сформирован, с тем чтобы находиться напротив пиксельного электрода 20. Этот противоположный электрод 80 сформирован в качестве одиночной пленки, с тем чтобы распространяться почти по всей поверхности противоположной подложки 81. Здесь, единичный жидкокристаллический элемент Clc отображения (обратитесь к фиг. 4) состоит из одного пиксельного электрода 20, противоположного электрода и жидкокристаллического слоя 75, удерживаемого между ними.

Кроме того, устройство подсветки (не показано) скомпоновано на стороне задней поверхности подложки 10 активной матрицы и может испускать свет в направлении от подложки 10 активной матрицы на противоположную подложку 81.

Как показано на фиг. 1, сигнальные линии сформированы на подложке 10 активной матрицы в горизонтальном и вертикальном направлениях. Таким образом, схемы 2 пикселя сформированы в форме матрицы в точках пересечения m истоковых линий (SL1, SL2,..., SLm), тянущихся в вертикальном направлении (направлении столбца), n затворных линий (GL1, GL2,..., GLn), тянущихся в горизонтальном направлении (направлении строки). Каждое из чисел m и n является натуральным числом два или более. В дополнение, истоковые линии представлены «истоковой линией SL», а затворные линии представлены «затворной линией GL».

Здесь, истоковая линия SL соответствует «сигнальной линии данных», а затворная линия GL соответствует «сигнальной линии сканирования». В дополнение, истоковый формирователь 13 соответствует «схеме возбуждения сигнальных линий данных», затворный формирователь 14 соответствует «схеме возбуждения сигнальных линий сканирования», схема 12 возбуждения противоположного электрода соответствует «схеме подачи напряжения противоположного электрода», а схема 11 управления отображением частично соответствует «схеме возбуждения линий управления».

В дополнение, на фиг. 1 каждая из схемы 11 управления отображением и схемы 12 возбуждения противоположного электрода проиллюстрирована, с тем чтобы существовать независимо от истокового формирователя 13 и затворного формирователя 14, но схема 11 управления отображением и схема 12 возбуждения противоположного электрода могут быть включены в эти формирователи.

Согласно этому варианту осуществления опорная линия REF, линия CSL вспомогательной емкости и линия BST добавочного напряжения предусмотрены в качестве сигнальных линий для возбуждения схемы 2 пикселя, а также истоковой линии SL и затворной линии GL, описанных выше. В дополнение, в качестве еще одного примера конфигурации дополнительно может быть предусмотрена линия SEL выбора. Фиг. 3 показывает конфигурацию устройства отображения в этом случае.

Опорная линия REF, линия BST добавочного напряжения и линия SEL выбора соответствуют «первой линии управления», «второй линии управления» и «третьей линии управления» соответственно и возбуждаются схемой 11 управления отображением.

В дополнение, линия CSL вспомогательной емкости соответствует «четвертой линии управления» или «линии фиксированного напряжения» и возбуждается схемой 11 управления отображением в качестве одного из примеров.

Со ссылкой на фиг. с 1 по 3 каждая из опорной линии REF, линии BST добавочного напряжения и линии CSL вспомогательной емкости предусмотрена в каждой строке, с тем чтобы тянуться в направлении строки, и проводки каждой строки взаимно присоединены и объединены в периферийной части массива схем пикселя, но проводка в каждой строке может возбуждаться индивидуально, и общее напряжение может прикладывается к ней согласно режиму работы или каждая линия может быть предусмотрена в каждом столбце, с тем чтобы тянуться в направлении столбца. В своей основе каждая из опорной линии REF, линии BST добавочного напряжения и линии CSL вспомогательной емкости сконфигурирована, чтобы совместно использоваться множеством схем 2 пикселя. В дополнение, в случае где дополнительно предусмотрена линия SEL выбора, она может быть предусмотрена таким же образом, как у линии BST добавочного напряжения.

Схема 11 управления отображением управляет действием записи в режиме нормального отображения и режиме постоянного отображения и действием самообновления в режиме постоянного отображения, как будет описано ниже.

Во время действия обновления схема 11 управления отображением принимает сигнал Dv данных и сигнал Ct синхронизации, представляющие изображение, которое должно быть отображено, из внешнего источника сигнала и на основании сигналов Dv и Ct вырабатывает цифровой сигнал DA изображения и сигнал Stc управления синхронизацией стороны данных Gtc, который должен прикладываться к истоковому формирователю 14, и сигнал Sec управления противоположным напряжением, который должен прикладываться к схеме 12 возбуждения противоположного электрода, в качестве сигналов для отображения изображения на части 21 элемента отображения (обратитесь к фиг. 4) массива схем пикселя, и сигнальные напряжения, которые должны прикладываться к опорной линии REF, линии BST добавочного напряжения, линии CSL вспомогательной емкости, и выбору SEL (если он предусмотрен).

Истоковый формирователь 13 управляется схемой 11 управления отображением, с тем чтобы прикладывать истоковый сигнал, имеющий предопределенную амплитуду напряжения, к каждой истоковой линии SL с предопределенной привязкой по времени во время действия записи и действия самообновления.

Во время действия записи истоковый формирователь 13 вырабатывает напряжение, надлежащее для уровня напряжения противоположного напряжения Vcom, которое соответствует значению пикселя для одной линии отображения, представленной цифровым сигналом DA, в качестве истоковых сигналов Sc1, Sc2, …, Scm в отношении каждого горизонтального периода (также указываемого ссылкой как «период H») на основании цифрового сигнала DA изображения и сигнала Stc управления синхронизаций стороны данных. В качестве этого напряжения напряжение многочисленных оттенков предполагается в обоих из режима нормального отображения и режима постоянного отображения, но количество оттенков в режиме постоянного отображения является меньшим, чем в режиме нормального отображения, в этом варианте осуществления, и напряжение является (трехзначным) напряжением трех оттенков. Таким образом, эти истоковые сигналы прикладываются к соответствующим истоковым линиям SL1, SL2,…, SLm соответственно.

В дополнение, во время действия самообновления истоковый формирователь 13 управляется схемой 11 управления отображением, с тем чтобы прикладывать одно и то же напряжение ко всем истоковым линиям SL, присоединенным к целевым схемам 2 пикселя, с одной и той же привязкой по времени (подробности будут описаны позже).

Затворный формирователь 14 управляется схемой 11 управления отображением, с тем чтобы прикладывать затворный сигнал, имеющий предопределенную амплитуду напряжения, к каждой затворной линии GL с предопределенной привязкой по времени во время действия записи и действия самообновления. В дополнение, затворный формирователь 14 может быть сформирован на подложке 10 активной матрицы подобно схеме 2 пикселя.

Во время действия записи затворный формирователь 14 последовательно выбирает затворные линии GL1, GL2, …, GLn для приблизительно каждого горизонтального периода в каждом периоде кадра цифрового сигнала DA изображения, для того чтобы записывать истоковые сигналы Sc1, Sc2,..., Scm в каждой схеме 2 пикселя на основании сигнала Gtc управления синхронизацией стороны сканирования.

В дополнение, во время действия самообновления затворный формирователь 14 управляется схемой 11 управления отображением, с тем чтобы прикладывать одно и то же напряжение ко всем затворным линиям GL, присоединенным к целевым схемам 2 пикселя, с одной и той же привязкой по времени (подробности будут описаны позже).

Схема 12 возбуждения противоположного электрода прикладывает противоположное напряжение Vcom к противоположному электроду 80 через проводку CML противоположного электрода. Согласно этому варианту осуществления схема 12 возбуждения противоположного электрода выдает противоположное напряжение Vcom, так что оно попеременно переключается между предопределенным высоким уровнем (5 В) и предопределенным низким уровнем (0 В) в режиме нормального отображения и режиме постоянного отображения. Таким образом, действие для возбуждения противоположного электрода 80 наряду с переключением напряжения между высоким уровнем и низким уровнем указывается ссылкой как «противоположное возбуждение переменного тока».

Согласно «противоположному возбуждению переменного тока» в режиме нормального отображения противоположное напряжение Vcom переключается между высоким уровнем и низким уровнем в отношении каждого горизонтального периода и каждого периода кадра. То есть в определенном периоде кадра полярность напряжения между противоположным электродом 80 и пиксельным электродом 20 изменяется между двумя смежными горизонтальными периодами. В дополнение, в одном и том же горизонтальном периоде полярность напряжения между противоположным электродом 80 и пиксельным электродом 20 изменяется между двумя смежными периодами кадра.

Между тем в режиме постоянного отображения один и тот же уровень напряжения поддерживается в одном периоде кадра и полярность напряжения между противоположным электродом 80 и пиксельным электродом 20 изменяется между двумя смежными действиями записи.

Когда напряжение, имеющее одну и ту же полярность, непрерывно прикладывается между противоположным электродом 80 и схемой 20 пикселя, вызывается выжигание дефектов экрана отображения (поверхностное выжигание), так что необходимо действие инвертирования полярности, и когда применяется «противоположное возбуждение переменного тока», амплитуда напряжения, которое должно прикладываться к пиксельному электроду 20, может быть уменьшена при действии инвертирования полярности.

<<Схема пикселя>>

Затем, конфигурация схемы 2 пикселя будет описана со ссылкой на фиг. с 4 по 17. Фиг. с 4 по 6 показывает базовые схемные конфигурации схем 2 пикселя по настоящему изобретению. Схема 2 пикселя включает в себя часть 21 элемента отображения, включающую в себя единичный жидкокристаллический элемент Clc отображения, первую переключающую схему 22, вторую переключающую схему 23, схему 24 управления и вспомогательный емкостной элемент Cs подобно всем схемным конфигурациям. Вспомогательный емкостной элемент Cs соответствует «второму емкостному элементу».

В дополнение, базовая схемная конфигурация, показанная на фиг. 4, 5 и 6, показывает общие схемные конфигурации, в том числе базовые схемные конфигурации, принадлежащие к с первого по третий типам, которые будут описаны ниже. Поскольку единичный жидкокристаллический элемент Clc отображения уже был описан со ссылкой на фиг. 2, его описание опущено.

Пиксельный электрод 20 присоединен к одним концам первой переключающей схемы 22, второй переключающей схемы 23 и схемы 24 управления, в силу чего сформирован внутренний узел N1. Внутренний узел N1 удерживает напряжение пиксельных данных, подаваемое с сигнальной линии SL во время действия записи.

Вспомогательный емкостной элемент Cs имеет один конец, присоединенный к внутреннему узлу N1, и другой конец, присоединенный к линии CSL вспомогательной емкости. Этот вспомогательный емкостной элемент Cs дополнительно предусмотрен, так что внутренний узел N1 может стабильно удерживать напряжение пиксельных данных.

Один конец первой переключающей схемы 22, который не составляет внутренний узел N1, присоединен к истоковой линии SL. Первая переключающая схема 22 имеет транзистор T3, функционирующий в качестве переключающего элемента. Транзистор T3 является транзистором, чей управляющий вывод присоединен к затворной линии, и соответствует «третьему транзисторному элементу». Первая переключающая схема 22 отключена, а истоковая линия SL и внутренний узел N1 не соединены, когда по меньшей мере транзистор T3 отключен.

Один конец второй переключающей схемы 23, который не составляет внутренний узел N1, присоединен к истоковой линии SL. Вторая переключающая схема 23 является последовательной цепью, состоящей из транзистора T1 и диода D1. В дополнение, транзистор T1 является транзистором, чей управляющий вывод присоединен к выходному узлу N2 схемы 24 управления, и соответствует «первому транзисторному элементу». В дополнение, диод D1 выполняет действие выпрямления в направлении от истоковой линии SL к внутреннему узлу N1 и соответствует «диодному элементу». Диод D1 сформирован PN-переходом в этом варианте осуществления, но он может быть сформирован переходом Шотки или диодным соединением MOSFET (полевого транзистора с изолированным затвором) (MOSFET, в котором сток или исток присоединен к затвору).

В дальнейшем, как показано на фиг. 4, конфигурация, в которой вторая переключающая схема 23 является последовательной цепью, состоящей из транзистора T1 и диода D1, и транзистор T4 не включен в состав, указывается ссылкой как первый тип.

В отличие от первого типа, как показано на фиг. 5 и 6, вторая переключающая схема 23 может быть последовательной цепью, включающей в себя транзистор T4 в дополнение к транзистору T1 и диоду D1. В это время два типа предусмотрены на фиг. 5 и 6 соответственно в зависимости от сигнальной линии, к которой присоединен управляющий вывод транзистора T4. Согласно типу (второму типу) схемы пикселя, показанной на фиг. 5, линия SEL выбора дополнительно предусмотрена в дополнение к линии BST добавочного напряжения, и управляющий вывод транзистора T4 присоединен к линии SEL выбора. Между тем согласно типу (третьему типу) схемы пикселя, показанной на фиг. 6, управляющий вывод транзистора T4 присоединен к линии BST добавочного напряжения. В дополнение, линия SEL выбора не существует в первом типе, как и следовало ожидать. Транзистор T4 соответствует «четвертому транзисторному элементу».

В случае первого типа, когда транзистор T1 включен и разность потенциалов большая, чем напряжение включения, сформирована между обоими концами диода D1, вторая переключающая схема 23 включена в направлении от истоковой линии SL к внутреннему узлу N1. Между тем в случае второго и третьего типов, когда каждый из транзисторов T1 и T3 включен и разность потенциалов, большая чем напряжение включения, сформирована между обоими концами диода D1, вторая переключающая схема 23 включена в направлении от истоковой линии SL к внутреннему узлу N1.

Схема 24 управления является последовательной цепью, состоящей из транзистора T2 и емкостного элемента Cbst вольтодобавки. Первый вывод транзистора T2 присоединен к внутреннему узлу N1, а его управляющий вывод присоединен к опорной линии REF. В дополнение, второй вывод транзистора T2 присоединен к первому выводу емкостного элемента Cbst вольтодобавки и управляющему выводу транзистора T1, в силу чего формируется выходной узел N2. Второй вывод емкостного элемента Cbst вольтодобавки присоединен к линии BST добавочного напряжения. Транзистор T2 соответствует «второму транзисторному элементу».

Между тем один конец вспомогательного емкостного элемента Cs и один конец емкостного элемента Clc жидкого кристалла присоединены к внутреннему узлу N1. Для того чтобы предотвратить то, что ссылки становятся усложненными, электростатическая емкость вспомогательного емкостного элемента (указываемая ссылкой как «вспомогательная емкость») представлена посредством Cs, а электростатическая емкость емкостного элемента жидкого кристалла (указываемая ссылкой как «емкость жидкого кристалла») представлена посредством Cls. В это время общая емкость, которая является паразитной во внутреннем узле N1, то есть емкость Cp пикселя, в которой пиксельные данные записываются и удерживаются, приблизительно выражается суммой емкости Clc жидкого кристалла и вспомогательной емкости Cs (Cp = Clc + Cs).

В это время емкостной элемент Cbst вольтодобавки устанавливается так, что устанавливается Cbst << Cp, при этом Cbst представляет электростатическую емкость этого элемента (указываемую ссылкой как «емкость вольтодобавки»).

Когда транзистор T2 включен, выходной узел N2 удерживает напряжение согласно уровню напряжения внутреннего узла N1, но когда транзистор T2 отключен, он поддерживает исходное напряжение в открытом состоянии, даже когда уровень напряжения внутреннего узла N1 изменяется. Это исходное напряжение в открытом состоянии выходного узла N2 управляет включением/отключением транзистора T1 второй переключающей схемы 23.

Каждый из четырех видов транзисторов с T1 по T4 является тонкопленочным транзистором, таким как TFT на поликристаллическом кремнии или TFT на аморфном кремнии, который сформирован на подложке 10 активной матрицы, и один из первого и второго выводов соответствует электроду стока, а другой из них соответствует электроду истока, а управляющий вывод соответствует электроду затвора. В дополнение, каждый из транзисторов с T1 по T4 может состоять из одиночного транзисторного элемента, но в случае, где току утечки очень требуется подавляться, он может быть сконфигурирован из условия, чтобы несколько транзисторов были соединены последовательно и их управляющие выводы были присоединены друг к другу. В последующем описании работы схемы 2 пикселя предполагается, что каждый из транзисторов с T1 по T4 является TFT на поликристаллическом кремнии N-канального типа, а пороговое напряжение имеет значение около 2 В.

В дополнение, подобно транзисторам с T1 по T4 диод D1 также сформирован на подложке 10 активной матрицы. Согласно этому варианту осуществления диод D1 предусмотрен в качестве PN-перехода, состоящего из поликристаллического кремния.

<Первый тип>

Прежде всего будет дано описание схемы пикселя, принадлежащей к первому типу, в котором вторая переключающая схема 23 является последовательной цепью, состоящей из транзистора T1 и диода D1.

В это время, как описано выше, схемы 2A пикселя, показанные на фиг. 7 и 8, предполагаются в зависимости от конфигурации первой переключающей схемы 22.

Первая схема 2A пикселя, показанная на фиг. 7, имеет первую переключающую схему 22, состоящую только из транзистора T3.

Здесь, фиг. 7 показывает пример конфигурации, в котором вторая переключающая схема 23 является последовательной цепью, состоящей из диода D1 и транзистора T1, первый вывод транзистора T1 присоединен к внутреннему узлу N1, второй вывод транзистора T1 присоединен к выводу катода диода D1, а вывод анода диода D1 присоединен к истоковой линии SL, в качестве одного из примеров. Однако, как показано на фиг. 8, положения транзистора T1 и диода D1 могут быть поменяны в последовательной цепи. В дополнение, в качестве еще одной схемной конфигурации транзистор T1 может быть помещен между двумя диодами D1.

<Второй тип>

Затем будет дано описание схемы пикселя, принадлежащей ко второму типу, в котором схема 23 пикселя является последовательной цепью, состоящей из транзистора T1, диода D1 и транзистора T4, и управляющий вывод транзистора T4 присоединен к линии SEL выбора.

Во втором типе схемы 2B пикселя, показанные на фиг. с 9 по 11, и схемы 2C пикселя, показанные на фиг. с 12 по 15, предполагаются в зависимости от конфигурации первой переключающей схемы 22.

Согласно схеме 2B пикселя, показанной на фиг. 9, первая переключающая схема 22 состоит только из транзистора T3. В дополнение, подобно первому типу, что касается конфигурации второй переключающей схемы 23, вариантные схемы могут быть реализованы в зависимости от компоновки диода D1 (обратитесь к фиг. 10 и 11). В дополнение, положения транзисторов T1 и T4 могут быть изменены в схемах.

Схема 2C пикселя, показанная на фиг. 12, имеет первую переключающую схему 22, которая является последовательной цепью, состоящей из транзистора T3 и транзистора T4. Вариантная схема реализована, как показано на фиг. 13, посредством изменения компоновочного положения транзистора T4. В дополнение, вариантная схема может быть реализована, как показано на фиг. 14, посредством предоставления множества транзисторов T4.

Более того, как показано на фиг. 15, вместо транзистора T4 в первой переключающей схеме 22 вариантная схема может быть реализована из условия, чтобы транзистор T5 был присоединен к транзистору T4 через их управляющие выводы.

<Третий тип>

Затем будет дано описание схемы пикселя, принадлежащей к третьему типу, в котором схема 23 пикселя является последовательной цепью, состоящей из транзистора T1, диода D1 и транзистора T4, и управляющий вывод транзистора T4 присоединен к линии BST добавочного напряжения.

Схема пикселя третьего типа имеет конфигурацию, в которой управляющий вывод транзистора T4 присоединен к линии BST добавочного напряжения, а выбор SEL не предусмотрен по сравнению со схемой пикселя второго типа. Поэтому могут быть реализованы схемы пикселя, соответствующие схемам 2B пикселя, показанным на фиг. с 9 по 11, и схемам 2C пикселя, показанным на фиг. с 12 по 15. В качестве одного из примеров схема 2D пикселя, соответствующая схеме 2B пикселя, показанной на фиг. 9, показана на фиг. 16, и схема 2E пикселя, соответствующая схеме 2C пикселя, показанной на фиг. 12, показана на фиг. 17.

В дополнение, в вышеприведенном типе схем пикселя те же самые транзисторные элементы или диодные элементы соответственно могут быть соединены последовательно.

[Второй вариант осуществления]

Во втором варианте осуществления будет дано описание действия самообновления в каждой из схем пикселя с первого по третий типов со ссылкой на чертежи.

Действие самообновления означает действие в режиме постоянного отображения, выполняемое для множества схем 2 пикселя из условия, чтобы первые схемы 22 пикселя, вторые схемы 23 пикселя и схемы 24 управления активизировались в предопределенной последовательности, а потенциалы пиксельных электродов 20 (это также потенциалы внутренних узлов N1) восстанавливались в потенциалы оттенка, записанные при последнем действии записи, и для пикселей всех оттенков схемы пикселя совместно восстанавливались одновременно в отношении каждого оттенка. Действие самообновления является специфическим действием посредством схем с 2A по 2E пикселя в настоящем изобретении, и энергопотребление может быть значительно сокращено по сравнению с традиционным «действием внешнего обновления», при котором потенциал пиксельного электрода 20 восстанавливается выполнением нормального действия записи. В дополнение, вышеприведенный термин «одновременно» в «совместно одновременно» означает «в одно и то же время», имеющее временную длительность последовательности действий при действии самообновления.

Между тем в традиционном случае действие для инвертирования полярности только напряжения Vcl жидкого кристалла, приложенного между пиксельным электродом 20 и противоположным электродом 80, выполнялось наряду с поддержанием его абсолютного значения (действие внешнего инвертирования полярности) посредством выполнения действия записи. Когда это действие внешнего инвертирования полярности выполняется, полярность инвертируется и абсолютное значение напряжения Vcl жидкого кристалла обновляется состоянием во время последней записи. То есть инвертирование полярности и действие обновления выполняются одновременно. Поэтому оно нормально не выполняется для выполнения действия обновления с целью только обновления абсолютного значения напряжения Vcl жидкого кристалла без инвертирования полярности, но в дальнейшем такое действие обновления указывается ссылкой как «действие внешнего обновления» с целью сопоставления его с действием самообновления для удобства в описании.

В дополнение, в случае где действие обновления выполняется действием внешнего инвертирования полярности, действие записи выполняется по-прежнему.

То есть к тому же, когда сравнивается с этим традиционным способом, энергопотребление значительно снижается действием самообновления в этом варианте осуществления.

Как будет описано ниже, согласно действию самообновления в этом варианте осуществления все из схем пикселя устанавливаются в одинаковое состояние напряжения, но фактически при этом состоянии напряжения автоматически выбирается только схема пикселя, в которой внутренний узел N1 показывает состояние напряжения специфичного одного оттенка, и потенциал внутреннего узла N1 восстанавливается (обновляется). То есть, хотя напряжение прикладывается ко всем схемам пикселя, на практике потенциал внутреннего узла N1 обновляется в некоторых схемах пикселя и он не обновляется в других схемах пикселя во время прикладывания напряжения.

Поэтому, для того чтобы избежать путаницы в описании, термин «(действие) самообновления» и термин «(действие) обновления» должны умышленно различаться в последующем описании. Первый используется в широкой концепции, указывающей ссылкой на последовательность действий для восстановления потенциала внутреннего узла N1 каждой схемы пикселя. Между тем последний используется в узкой концепции, указывающей ссылкой на действие для фактического восстановления потенциала (потенциала внутреннего узла) пиксельного электрода. То есть согласно «действию самообновления» в этом варианте осуществления только внутренний узел, показывающий состояние напряжения специфичного одного оттенка, автоматически и избирательно «обновляется» установлением одного и того же состояния напряжения для всех схем пикселя. Таким образом, значение напряжения изменяется, с тем чтобы изменять оттенок в качестве цели «обновления», и напряжение прикладывается подобным образом, так что «обновление» выполняется для всех оттенков. Таким образом, согласно «действию самообновления» в этом варианте осуществления «действие обновления» выполняется в отношении каждого оттенка.

Напряжение прикладывается ко всем затворным линиям GL, истоковым линиям SL, опорным линиям REF, линиям CSL вспомогательной емкости и линиям BST добавочного напряжения, которые присоединены к схеме 2 пикселя, служащей в качестве цели действия самообновления, и к противоположному электроду 80 с одной и той же привязкой по времени. В случае схемы пикселя второго типа, имеющей линию SEL выбора, напряжение подобным образом прикладывается к линии SEL выбора.

Таким образом, при одной и той же привязке по времени одно и то же напряжение прикладывается ко всем затворным линиям GL, одно и то же напряжение прикладывается ко всем опорным линиям REF, одно и то же напряжение прикладывается ко всем линиям CSL вспомогательной емкости и одно и то же напряжение прикладывается ко всем линиям BST добавочного напряжения. Управление синхронизацией прикладывания напряжения выполняется схемой 11 управления отображением, показанной на фиг. 1, и индивидуальное прикладывание напряжения выполняется схемой 11 управления отображением, схемой 12 возбуждения противоположного электрода, истоковым формирователем 13 и затворным формирователем 14.

В режиме постоянного отображения в этом варианте осуществления, как описано в первом варианте осуществления, также предполагается, что (трехзначные) пиксельные данные (трех оттенков) удерживаются в блоке схем пикселя. В это время потенциал VN1 (это также потенциал пиксельного электрода 20), удерживаемый во внутреннем узле N1, показывает три состояния напряжения, такие как с первого по третье состояния напряжения.

Согласно этому варианту осуществления в качестве одного из примеров первое состояние напряжения (состояние высокого напряжения) устанавливается в 5 В, второе состояние напряжения (состояние среднего напряжения) устанавливается в 3 В и третье состояние напряжения (состояние низкого напряжения) устанавливается в 0 В.

В состоянии непосредственно перед выполнением действия самообновления предполагается, что есть пиксель, в котором пиксельный электрод 20 записан в первом состоянии напряжения, пиксель, в котором он записан во втором состоянии напряжения, и пиксель, в котором он записан в третьем состоянии напряжения.

Однако согласно действию самообновления в этом варианте осуществления напряжение прикладывается на основании одной и той же последовательности независимо от состояния напряжения пиксельного электрода 20, так что действие обновления может выполняться для всех схем пикселя. Это содержание будет описано со ссылкой на временную диаграмму и принципиальную схему.

В дополнение, в дальнейшем случай, где напряжение записано в первое состояние напряжения (напряжение высокого уровня) при последнем действии записи и напряжение высокого уровня должно восстанавливаться, указывается ссылкой как «случай H», случай, где напряжение записано во второе состояние напряжения (напряжение среднего уровня) при последнем действии записи и напряжение среднего уровня должно восстанавливаться, указывается ссылкой как «случай M», и случай, где напряжение записано в третье состояние напряжения (напряжение низкого уровня) при последнем действии записи и напряжение низкого уровня должно восстанавливаться, указывается ссылкой как «случай L».

В дополнение, как описано в первом варианте осуществления, предполагается, что пороговое напряжение каждого транзистора имеет значение 2 В. В дополнение, предполагается, что напряжение включения диода D1 имеет значение 0,6 В.

<Первый тип>

Прежде всего будет дано описание действия самообновления для схемы 2A пикселя первого типа, в которой вторая переключающая схема 23 является последовательной цепью, состоящей только из транзистора T1 и диода D1. Здесь предполагается схема 2A пикселя, показанная на фиг. 7.

Фиг. 18 показывает временную диаграмму действия самообновления первого типа.

Как показано на фиг. 18, действие самообновления поделено на два этапа S1 и S2, а этап S1 снабжен двумя фазами P1 и P2. Фиг. 18 иллюстрирует формы сигналов напряжения всех затворных линий GL, истоковых линий SL, линий BST добавочного напряжения, опорных линий REF, линий CSL вспомогательной емкости и линий BST добавочного напряжения, которые присоединены к схемам 2A пикселя, служащим в качестве цели действия самообновления, и форму сигнала напряжения противоположного напряжения Vcom. В дополнение, согласно этому варианту осуществления предполагается, что все схемы пикселя массива схем пикселя являются целью действия самообновления.

В дополнение, фиг. 18 показывает формы сигналов, показывающие изменения потенциала VN1 (напряжения пикселя) внутреннего узла N1, потенциал VN2 выходного узла N2 в каждом из случаев H, M и L и состояния включения/отключения транзисторов с T1 по T3 на каждом этапе и каждой фазе. Более того, фиг. 18 показывает случай в круглых скобках. Например, VN1 (H) - форма сигнала, показывающая изменение потенциала VN1 в случае H.

В дополнение, предполагается, что высокий уровень был записан в случае H, средний уровень был записан в случае M, а низкий уровень был записан в случае L в момент до момента времени (t1) для начала действия самообновления.

После того как действие записи было выполнено и истекло время, потенциал VN1 внутреннего узла N1 изменяется вследствие формирования тока утечки каждого транзистора в схеме пикселя. В случае H VN1 имеет значение 5 В непосредственно после действия записи, но это значение становится более низким, чем исходное значение после того, как истекло время. Подобным образом в случае M, VN1 имеет значение 3 В непосредственно после действия записи, но это значение становится более низким, чем исходное значение после того, как истекло время. В каждом из этих случаев H и M потенциал внутреннего узла N1 постепенно уменьшается со временем главным образом, так как ток утечки течет по направлению к более низкому потенциалу (такому как линия заземления) через транзистор в отключенном состоянии.

В дополнение, в случае L потенциал VN1 имеет значение 0 В непосредственно после действия записи, он мог бы немного подняться со временем. Это происходит потому, что, когда напряжение записи приложено к истоковой линии SL во время действия записи в другой схеме пикселя, и ток утечки протекает из истоковой линии SL во внутренний узел N1 через транзистор в отключенном состоянии даже в невыбранной схеме пикселя.

, что VN1(H) находится немного ниже, чем 5 В, VN1(M) находится немного ниже чем 3 В, а VN1(L) находится немного выше чем 0 В, в момент t1 времени. Это происходит потому, что учитывается вышеприведенная флуктуация потенциала.

Действие самообновления в этом варианте осуществления главным образом поделено на два этапа S1 и S2. Этап S1 соответствует «этапу обновления», а этап S2 соответствует «этапу ожидания».

На этапе S1, действие обновления непосредственно выполняется для случая H и случая M прикладыванием импульсных напряжений. Между тем, на этапе S2, действие обновления выполняется опосредованно для случая L прикладыванием постоянного напряжения в течение времени (такого как в десять раз или больше),более длительного, чем у этапа S1. В дополнение, термин «непосредственно выполняемый» означает, что внутренний узел N1 и истоковая линия SL соединены через вторую переключающую схему 23, так что напряжение, приложенное к истоковой линии SL, прикладывается к внутреннему узлу N1, и потенциал VN1 внутреннего узла устанавливается в требуемое значение. В дополнение, термин «опосредованно выполняемый» означает, что внутренний узел N1 и истоковая линия SL не соединены через вторую переключающую схему 23, но потенциал VN1 внутреннего узла N1 приводится ближе к требуемому значению посредством использования тока утечки, незначительно протекающего между внутренним узлом N1 и истоковой линией SL через первую переключающую схему 22 в отключенном состоянии.

В дополнение, на этапе S1, фаза P1 и P2 отличается в зависимости от того, обновляется ли случай H или M. На фиг. 18, в фазе P1, обновляется только внутренний узел N1 случая H (записи высокого напряжения), а на фазе P2, обновляется только внутренний узел N1 случая M (записи среднего напряжения). В дальнейшем, эта операция будет описана подробно.

«Этап S1/фаза P1»

На фазе P1, которая должна начинаться в момент t1 времени, напряжение, которое может полностью отключать транзистор T3, прикладывается к затворной линии GL. Здесь, напряжение имеет значение -5 В. В дополнение, во время выполнения действия самообновления транзистор T3 постоянно отключен, так что напряжение, приложенное к затворной линии GL, может оставаться неизменным во время действия самообновления.

Противоположное напряжение Vcom, приложенное к противоположному электроду 80, и напряжение, приложенное к линии CSL вспомогательной емкости, устанавливаются в 0 В. Здесь, напряжение не ограничено 0 В, и значение напряжения до момента t1 времени может поддерживаться как оно есть. В дополнение, эти напряжения также могут оставаться неизменными во время действия самообновления.