Область техники

Данное изобретение касается реализации технологии скремблирования и дескремблирования кадровой синхронизации в протоколе связи и, в частности, скремблирующего устройства и дескремблирующего устройства для параллельной кадровой синхронизации в сетях синхронной цифровой иерархии (Synchronous Digital Hierarchy, SDH)/синхронных оптических сетях (Synchronous Optical Network, SONET).

Предпосылки изобретения

В цифровой связи принимающий конец линии связи реализует восстановление тактовой синхронизации линии посредством схемы фазовой автоподстройки, реагирующей на изменения 1/0 в линии связи, выполняет битовую синхронизацию и доставляет информацию синхронизации посредством флага кадра, таким образом обеспечивая достижение кадровой синхронизации и дальнейшей синхронизации байтов. Принимающий конец может точно извлечь действительные пользовательские данные только тогда, когда достигнута тактовая синхронизация и кадровая синхронизация. Информация пользователей, которая должна быть передана во время процесса связи, является разнообразной, и если пользовательские данные содержат чрезмерно длинную последовательность с последовательными нулями или единицами, то это может вызвать нарушение работы схемы фазовой автоподстройки принимающей стороны, что приводит к возникновению битовых ошибок или даже ошибок в восстановлении данных; если же пользовательские данные включают информацию, идентичную флагу кадра, она может заставлять конечный автомат кадровой синхронизации принимающей стороны входить в ошибочное состояние или неоднократно колебаться во время инициализации, и поэтому возникнет проблема, состоящая в том, что корректная кадровая синхронизация не сможет быть реализована.

Скремблирование является способом, обычно используемым в цифровой связи, и его цель состоит в том, чтобы сделать данные, передаваемые в цифровой линии, рандомизированными (случайными), таким образом эффективно избегая вышеупомянутой проблемы. Рандомизирование данных линии связи может не только гарантировать, что в линии будет происходить достаточно много изменений 1/0 для восстановления синхронизации, но также позволяет в максимально возможной степени избежать появления флагов кадра в области информации пользователя. Реализация скремблирования включает выполнение линейных преобразований с использованием псевдослучайных последовательностей над информацией, которую требуется доставить, и генерирование скремблированных данных, то есть используется генератор псевдослучайной последовательности, чтобы произвести рандомизацию выходных данных линии; а принимающий конец использует те же самые псевдослучайные последовательности, чтобы выполнить обратную обработку и восстановить исходные данные, то есть выполняет процесс дескремблирования. Скремблирование может быть реализовано с использованием программного обеспечения или аппаратных средств. Однако, так как Скремблирование должно быть реализовано в режиме реального времени, Скремблирование и дескремблирование для относительно высокоскоростного канала обычно реализуют с использованием аппаратной схемы.

Псевдослучайная последовательность обычно образована последовательностями псевдослучайного кода (М). Так называемая псевдослучайная последовательность является рядом чисел, генерированных посредством арифметической операции согласно определенной функции вычисления, и этот ряд чисел близок к последовательностям случайных чисел. В скремблирующей/ дескремблирующей системе из псевдослучайных последовательностей обычно генерируют двоичные последовательности, чтобы выполнить скремблирующее/дескремблирующее вычисление.

Для скремблирования кадровой синхронизации на передающем конце реализуется функция XOR (исключающее ИЛИ) в отношении передаваемой информации данных и одной М-последовательности, чтобы гарантировать, что передаваемые скремблированные последовательности из единиц и нулей изменяются случайным образом. На принимающем конце, начиная с той же самой позиции, реализуют обратное вычисление для принятого потока информации с использованием той же самой М-последовательности, чтобы восстановить исходный поток информации. Для скремблирования кадровой синхронизации должна быть передана информация о состоянии М-последовательности, и система SDH использует байты А1, А2, которые также вызывают байтами кадрирования, в поле передачи в качестве шаблона кадровой синхронизации, чтобы достигнуть синхронизации кадров между передающим концом и принимающим концом. Кроме того, этот синхронный сигнал также используется в качестве синхронизирующей информации для самосинхронизирующейся схемы скремблирования/дескремблирования. На заголовке кадра как скремблирующая, так и дескремблирующая схема устанавливаются на 1, начальное состояние с начальным значением "все единицы" возвращается, и скремблирование запускается с одной и той же позиции и после первой строки заголовка секции, чтобы гарантировать синхронизацию между принимающим концом и передающим концом.

Благодаря прогрессу техники скорость передачи данных была многократно увеличена, и при использовании существующей последовательной обработки скремблирование/дескремблирование должно производиться на этой скорости передачи данных линии связи. Например, при скорости работы STM-16, равной 2,5 Гбит/с, скорости работы STM-64, равной 10 Гбит/с, или даже скорости работы STM-256, равной 40 Гбит/с, обычно используемых современной системой передачи SDH, требуется, чтобы скорость работы последовательного скремблера достигала 40 Гбит/с, чего, однако, очень трудно достигнуть в последовательном режиме. Поэтому должна использоваться параллельная схема скремблирования/дескремблирования, чтобы уменьшить рабочую частоту посредством расширения битовой разрядности, благодаря чему скремблер и дескремблер могут быть реализованы с использованием только схем с низкой скоростью работы. Здесь STM является сокращением от Synchronous Transport Module (синхронный транспортный модуль), который является модулем синхронной передачи, а STM-16, STM-64 и STM-256, соответственно, представляют собой различные типы модулей синхронной передачи.

Когда используется существующая параллельная схема скремблирования/дескремблирования, сначала скремблирующее уравнение представляется посредством последовательной схемы, а затем параллельный поток битов разлагается на суперпозицию каждого однобитового последовательного скремблирования, и структура параллельной схемы скремблирования/дескремблирования получается путем использования матричного метода или непосредственного выполнения итеративного вычисления. Для различных битовых разрядностей параллельных входных данных это требует соответственного выполнения вычислений, чтобы получить структуру схемы соответствующего параллельного скремблирования/дескремблирования. После того как параллельная битовая разрядность увеличивается, например, выше 256 битов, требуется громоздкое итеративное вычитание и очень длинная цепь комбинационной логики, и это приводит к тому, что задержка схемы является слишком большой, и частота обработки, требуемая параллельным сигналом, не может быть достигнута, и, таким образом, это неприменимо к высокоскоростной схеме со скоростью выше 40 Гбит/с.

Параллельный поток битов является видом параллельных данных, которые отличаются от последовательных данных. Так называемые последовательные данные - это данные, которые обрабатываются по одному биту; а так называемые параллельные данные обрабатываются согласно множеству битов. Все данные, передаваемые по линии связи, являются последовательными данными, но во время обработки берут последовательные n битов последовательных данных, чтобы их обработать, то есть последовательные данные преобразуют в параллельные данные из n битов. Существующее параллельно-последовательное/последовательно-параллельное преобразование означает описанное выше.

Таким образом, недостатки использования существующей параллельной схемы скремблирования/дескремблирования являются следующими: с одной стороны, требуется разработка соответствующих структур схем для параллельного скремблирования/дескремблирования, соответственно, для различных битовых разрядностей входных параллельных данных, и таким образом, схема имеет узкую область применения и не имеет универсальности, что неблагоприятно для ее продвижения и применения; с другой стороны, работа в реальном времени должна быть выполнена для М-последовательности, которая не является заданными и параллельными данными, и чем больше битовая разрядность входных параллельных данных, тем более сложной является итерация, которая должна быть выполнена в реальном времени; таким образом, сложность вычислений в реальном времени с такой итерацией довольно высока, что может привести к низкой скорости вычисления и, следовательно, понизить эффективность работы и частоту обработки параллельной схемы скремблирования/дескремблирования.

Сущность изобретения

Ввиду вышеизложенного, основная цель данного изобретения состоит в том, чтобы создать скремблирующее устройство и дескремблирующее устройство для параллельной кадровой синхронизации, которое может реализовать скремблирование и дескремблирование, соответственно. Данное изобретение применимо к параллельным данным с различными входными битовыми разрядностями, имеет универсальность и благоприятно для продвижения; при этом сложность вычислений уменьшается, а эффективность работы и частота обработки скремблирующего устройства и дескремблирующего устройства повышаются.

Чтобы достигнуть вышеупомянутой цели, техническая схема данного изобретения реализуется следующим образом:

скремблирующее устройство для параллельной кадровой синхронизации включает блок управления, устройство хранения данных и блок XOR; при этом

блок управления используется, чтобы считывать псевдослучайную последовательность из устройства хранения данных последовательно, и получать контент, соответствующий параллельным данным в псевдослучайной последовательности;

устройство хранения данных используется, чтобы хранить псевдослучайную последовательность, которая является заранее заданной, и вводить контент, соответствующий параллельным данным в псевдослучайной последовательности, в блок XOR;

блок XOR используется, чтобы выполнять обработку XOR поочередно для параллельных данных, которые вводятся последовательно, с контентом, соответствующим параллельным данным в псевдослучайной последовательности, полученной из устройства хранения данных, и затем выводить скремблированные данные.

При этом в ситуации, когда битовая разрядность параллельных данных равна Q, контент, соответствующий параллельным данным в псевдослучайной последовательности, представляет собой Q битов контента, соответствующего параллельным данным в псевдослучайной последовательности;

длина псевдослучайной последовательности равна T×Q, и состоит из Q битов псевдослучайного кода М-последовательностей; где Т является периодом цикла повторения М-последовательностей.

Блок управления также используется, чтобы по кругу, согласно Т, под управлением кадрового сигнала синхронизации, получать поочередно Q битов М-последовательностей, соответствующих параллельным данным в псевдослучайной последовательности.

Блок XOR также используется, чтобы выполнять обработку XOR поочередно для параллельных данных, которые вводятся последовательно, с Q битами М-последовательностей, соответствующих параллельным данным в псевдослучайной последовательности, пока обход T×Q битов М-последовательностей не завершается.

Конкретно, блок управления является генератором адреса, а устройство хранения данных является генератором М-последовательности.

Дескремблирующее устройство для параллельной кадровой синхронизации включает устройство хранения данных, блок управления, и блок XOR; при этом

блок управления используется, чтобы считывать псевдослучайную последовательность из устройства хранения данных последовательно и получать контент, соответствующий дескремблированным данным в псевдослучайной последовательности;

устройство хранения данных используется, чтобы хранить псевдослучайную последовательность, которая является заранее заданной, и вводить контент, соответствующий скремблированным данным в псевдослучайной последовательности, в блок XOR;

блок XOR используется, чтобы выполнять обработку XOR поочередно для скремблированных данных, которые вводятся последовательно, с контентом, соответствующим скремблированным данным в псевдослучайной последовательности, полученной из устройства хранения данных, и затем выводить параллельные данные, полученные после дескремблирования.

При этом в ситуации, когда битовая разрядность скремблированных данных равна Q, контент, соответствующий скремблированным данным в псевдослучайной последовательности, представляет собой Q битов контента, соответствующего скремблированным данным в псевдослучайной последовательности;

длина псевдослучайной последовательности равна T×Q, и она состоит из Q битов М-последовательностей; где Т является периодом цикла повторения М-последовательностей.

Блок управления также используется, чтобы по кругу, согласно Т, под управлением кадрового сигнала синхронизации получать поочередно Q битов М-последовательностей, соответствующих скремблированным данным в псевдослучайной последовательности.

Блок XOR также используется, чтобы выполнять обработку XOR поочередно для скремблированных данных, которые вводятся последовательно, с Q битами М-последовательностей, соответствующих скремблированным данным в псевдослучайной последовательности, пока обход T×Q битов М-последовательностей не завершается,

Конкретно, блок управления является генератором адреса, а устройство хранения данных является генератором М-последовательности,

Данное изобретение реализует скремблирующее устройство для параллельной кадровой синхронизации и дескремблирующее устройство для параллельной кадровой синхронизации, которые могут обеспечить скремблирование и дескремблирование, соответственно. Что касается скремблирующего устройства, блок управления в этом устройстве используется, чтобы считывать псевдослучайную последовательность из устройства хранения данных последовательно и получать контент, соответствующий параллельным данным в псевдослучайной последовательности; устройство хранения данных используется для хранения заранее заданной псевдослучайной последовательности и для ввода контента, соответствующего параллельным данным в псевдослучайной последовательности, в блок XOR; блок XOR используется, чтобы выполнять обработку XOR поочередно для параллельных данных, которые вводятся последовательно, с контентом, соответствующим параллельным данным в псевдослучайной последовательности, полученной из устройства хранения данных, и затем выводить скремблированные данные. Что касается соответствующего дескремблирующего устройства, блок управления в этом устройстве используется, чтобы считывать псевдослучайную последовательность из устройства хранения данных последовательно и получать контент, соответствующий дескремблированным данным в псевдослучайной последовательности; блок XOR используется, чтобы выполнять обработку XOR поочередно для скремблированных данных, которые вводятся последовательно, с контентом, соответствующим скремблированным данным в псевдослучайной последовательности, полученной из устройства хранения данных, и затем выводить параллельные данные, полученные после дескремблирования.

Данное изобретение позволяет реализовать скремблирование и дескремблирование параллельной кадровой синхронизации, соответственно, и обеспечить скремблирование/дескремблирование параллельной кадровой синхронизации с любой битовой разрядностью. Данное изобретение применимо к параллельным данным с различными битовыми разрядностями, имеет универсальность и благоприятно для продвижения; при этом сложность вычислений уменьшается, а эффективность работы и частота обработки скремблирующего устройства и дескремблирующего устройства повышаются. По сравнению с существующей параллельной схемой скремблирования/дескремблирования, данное изобретение легко реализуемо и характеризуется небольшими задержками, обусловленными комбинационной логикой и обработкой; изобретение в большей степени применимо для параллельного скремблирования/дескремблирования с большой битовой разрядностью и высокой скоростью.

Краткое описание чертежей

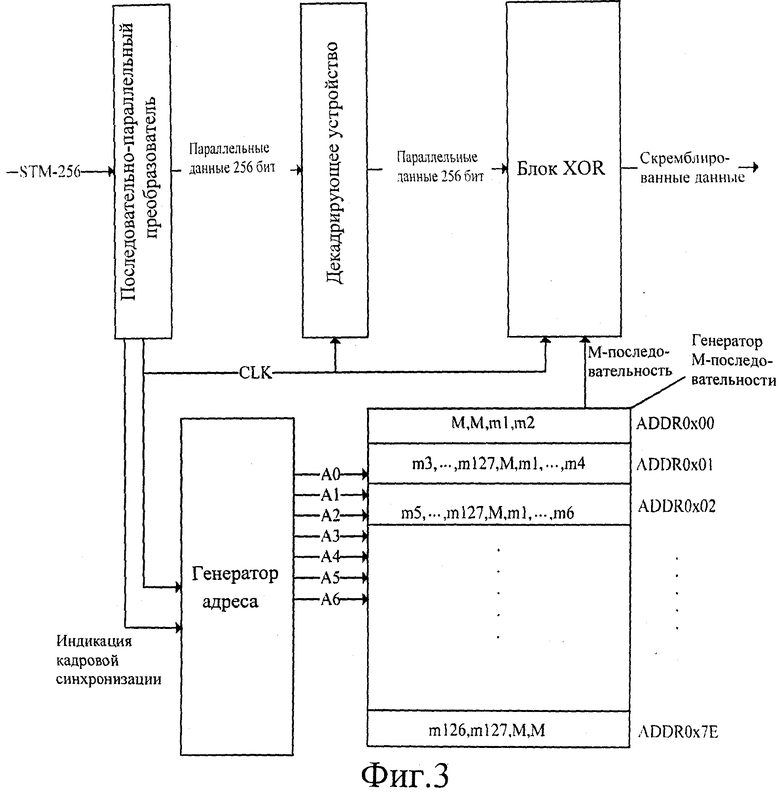

Фиг.1 иллюстрирует структуру скремблирующего устройства/дескремблирующего устройства для параллельной кадровой синхронизации согласно данному изобретению;

фиг.2 иллюстрирует структуру примера скремблирующего устройства/дескремблирующего устройства для параллельной кадровой синхронизации согласно данному изобретению;

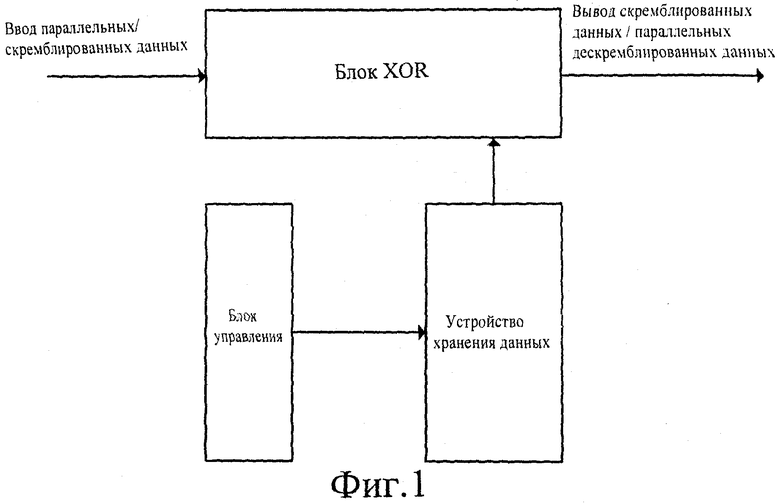

фиг.3 иллюстрирует структуру примера параллельного скремблирующего устройства/дескремблирующего устройства с 256 битами применительно к сигналу STM-256.

Предпочтительные варианты осуществления изобретения

Основная концепция данного изобретения состоит в следующем: когда устройство используется в качестве скремблирующего устройства, после того как параллельные данные вводятся в скремблирующее устройство, блок управления считывает контент, соответствующий параллельным данным в псевдослучайной последовательности, из устройства хранения данных; и затем они подвергаются операции XOR в блоке XOR, чтобы получить скремблированные данные. Когда устройство используется в качестве дескремблирующего устройства, входные данные являются скремблированными данными, и блок управления считывает контент, соответствующий параллельным данным в псевдослучайной последовательности, из устройства хранения данных; и затем контент и скремблированные данные подвергаются операции XOR в блоке XOR, чтобы получить дескремблированные данные. Нужно заметить, что контент, соответствующий параллельным данным в псевдослучайной последовательности, считываемой из устройства хранения данных, когда устройство используется в качестве скремблирующего устройства, и контент, соответствующий скремблированным данным в псевдослучайной последовательности, считываемой из устройства хранения данных, когда устройство используется в качестве дескремблирующего устройства, является одним и тем же.

Примеры реализации данной технической схемы будут далее описаны более подробно со ссылками на чертежи.

Когда данное изобретение используется или в качестве скремблирующего устройства, или в качестве дескремблирующего устройства, устройство состоит из трех функциональных модулей: блока XOR, блока управления и устройства хранения данных. Независимо от того, используется ли устройство в качестве скремблирующего устройства или дескремблирующего устройства, заранее заданная псевдослучайная последовательность, хранимая в устройстве хранения данных, является одинаковой; и данные, считываемые последовательно из устройства хранения данных под управлением блока управления, являются одинаковыми. Таким образом, когда обработка XOR выполняется в блоке XOR, часть контента псевдослучайной последовательности, которая используется, является одной и той же. Различие состоит в том, что когда устройство используется в качестве скремблирующего устройства, данные, вводимые в блок XOR, являются параллельными данными, а выходные данные после обработки XOR являются скремблированными данными; а когда устройство используется как дескремблирующее устройство, данные, вводимые в блок XOR, являются скремблированными данными, а выходные данные после обработки XOR являются дескремблированными потоками параллельных данных. Только таким образом дескремблирующее устройство согласно данному изобретению может выполнять дескремблирование скремблированных данных, сформированных и выведенных скремблирующим устройством, таким образом восстанавливая после обработки дескремблирования потоки параллельных данных, которые были первоначально введены в скремблирующее устройство. Поскольку данное изобретение используется или в качестве скремблирующего устройства, или в качестве дескремблирующего устройства, и каждое такое устройство состоит из трех функциональных модулей, блока XOR, блока управления и устройства хранения данных, на фиг.1 иллюстрируется системная архитектура обоих устройств, чтобы упростить описание, а конкретная реализация каждого блока при использовании данного изобретения в различных устройствах будет описана соответственно.

Как показано на фиг.1, скремблирующее устройство для параллельной кадровой синхронизации включает блок управления, устройство хранения данных и блок XOR. Блок управления используется, чтобы считывать псевдослучайную последовательность из устройства хранения данных последовательно и получать контент, соответствующий параллельным данным в псевдослучайной последовательности; устройство хранения данных используется для хранения заранее заданной псевдослучайной последовательности и для ввода контента, соответствующего параллельным данным в псевдослучайной последовательности, в блок XOR; блок XOR используется, чтобы выполнять обработку XOR поочередно для параллельных данных, которые вводятся последовательно, с контентом, соответствующим параллельным данным в псевдослучайной последовательности, полученной из устройства хранения данных, и затем выводить скремблированные данные.

Здесь в ситуации, когда битовая разрядность параллельных данных равна Q, контент, соответствующий параллельным данным в псевдослучайной последовательности, представляет собой Q битов контента, соответствующего параллельным данным в псевдослучайной последовательности; Длина псевдослучайной последовательности равна T×Q, и состоит из Q битов М-последовательностей, где Т является периодом цикла повторения М-последовательностей. Что касается Q, значение Q связано со скоростью параллельных данных и скоростью обработки чипа, например, это может быть 256 битов; значение Т определяется характеристическим уравнением М-последовательности, и когда самый высокий порядок характеристического уравнения М-последовательности равен r, T=2r-1. Нужно отметить, что значения Q и Т, упоминаемые ниже, имеют такой же смысл и, таким образом, не будут повторно описываться.

Как можно видеть, в данном изобретении предварительно рассчитанная псевдослучайная последовательность заранее сохранена в устройстве хранения данных, чтобы непосредственно использоваться, когда выполняется обработка XOR; в то время как в известных устройствах псевдослучайная последовательность не вычисляется или сохраняется заранее, а формируется в реальном времени. Поэтому данное изобретение может уменьшить сложность вычисления, и, соответственно, устройство, выполненное согласно данному изобретению, выполняет простую обработку и характеризуется высокой эффективностью обработки, и, таким образом, изобретение применимо к устройству с большей разрядной шириной параллельных данных и более высокой скоростью; кроме того, разрядная ширина параллельных данных и характеристическое уравнение М-последовательности не задаются; таким образом, данное изобретение имеет лучшую универсальность и применимо к различным типам протоколов связи.

Упомянутый выше блок управления также используется, чтобы по кругу, согласно периоду Т, под управлением кадрового сигнала синхронизации получать поочередно Q битов М-последовательностей, соответствующих параллельным данным в псевдослучайной последовательности.

Упомянутый выше блок XOR также используется, чтобы выполнять обработку XOR поочередно для параллельных данных, которые вводятся последовательно, с Q битами М-последовательностей, соответствующих параллельным данным в псевдослучайной последовательности, пока обход T×Q битов М-последовательностей не завершается, и затем выводить скремблированные данные.

Конкретно, блок управления является генератором адреса, а устройство хранения данных является генератором М-последовательности.

Дескремблирующее устройство для параллельной кадровой синхронизации включает устройство хранения данных, блок управления, и блок XOR. Блок управления используется, чтобы считывать псевдослучайную последовательность из устройства хранения данных последовательно и получать контент, соответствующий скремблированным данным в псевдослучайной последовательности; устройство хранения данных используется для хранения заранее заданной псевдослучайной последовательности и для ввода контента, соответствующего скремблированным данным в псевдослучайной последовательности, в блок XOR; блок XOR используется, чтобы выполнять обработку XOR поочередно для скремблированных данных, которые вводятся последовательно, с контентом, соответствующим скремблированным данным в псевдослучайной последовательности, полученной из устройства хранения данных, и затем выводить параллельные данные, полученные после дескремблирования.

Нужно заметить, что контент, соответствующий параллельным данным в псевдослучайной последовательности, считываемой из устройства хранения данных, когда устройство используется в качестве скремблирующего устройства, и контент, соответствующий скремблированным данным в псевдослучайной последовательности, считываемой из устройства хранения данных, когда устройство используется в качестве дескремблирующего устройства, является одним и тем же. Только таким образом дескремблирующее устройство согласно данному изобретению может выполнить дескремблирование скремблированных данных, сформированных и выведенных скремблирующим устройством, таким образом восстанавливая потоки параллельных данных, которые первоначально введены в скремблирующее устройство, после обработки дескремблирования.

При этом в ситуации, когда битовая разрядность скремблированных данных равна Q, контент, соответствующий скремблированным данным в псевдослучайной последовательности, представляет собой Q битов контента, соответствующего скремблированным данным, в псевдослучайной последовательности. Длина псевдослучайной последовательности равна T×Q, и она состоит из Q битов М-последовательностей, где Т является периодом цикла повторения М-последовательностей.

Блок управления также используется, чтобы по кругу, согласно Т, под управлением кадрового сигнала синхронизации, получать поочередно Q битов М-последовательностей, соответствующих скремблированным данным в псевдослучайной последовательности.

Упомянутый блок XOR также используется, чтобы выполнять обработку XOR поочередно для параллельных данных, которые вводятся последовательно, с Q битами М-последовательностей, соответствующих параллельным данным в псевдослучайной последовательности, пока обход T×Q битов М-последовательностей не завершается.

Конкретно, блок управления является генератором адреса, а устройство хранения данных является генератором М-последовательности.

Вышеупомянутые генератор адреса и генератор М-последовательности для случая, когда данное изобретение используется в качестве скремблирующего устройства или дескремблирующего устройства, показаны на фиг.2.

Таким образом, данное изобретение включает следующее:

Принцип технической схемы, принятой в данном изобретении, следующий: М-последовательность является периодической последовательностью, период повторения которой для скремблера с самым высоким порядком r равен 2r-1, то есть T=2r-1. Рассматривая в качестве примера скремблирование/дескремблирование в системе SDH/SONET, характеристический полином для скремблирование представляет собой х7+х6+1, то есть используется псевдослучайная последовательность с периодом 27-1 бита, а именно, 127 битов. Сущность скремблирования кадровой синхронизации состоит в том, что согласно порядку передачи битов данных, каждый бит данных подвергается операции XOR с битом, выведенным генератором М-последовательности, и затем подается в линию связи. Согласно соответствующему порядку, в схеме дескремблирования скремблированные биты данных подвергаются операции XOR с битами, выведенными таким же генератором М-последовательности, чтобы получить исходные потоки битов данных. В каждой точке кадровой синхронизации линейному сдвиговому регистру М-последовательности будет присвоено начальное значение, которое обычно является значением "все 1".

Предположим, что разрядная ширина входных параллельных данных D равна Q, период повторения М-последовательности равен Т, и каждая полная М-последовательность является М [0, Т-1]. Тогда должна быть одна последовательность R, длина которой T×Q, и контент которой является Q М-последовательностями в комбинации, то есть:

R[0,TQ-1]={M[0,T-1]0, М[0,Т-1]1 M[0,T-1]2, М[0,Т-1]3…M[0,T-1]Q-1}

Относительно параллельного скремблирования битов разрядностью Q, Q битов данных, которые вводятся последовательно, подвергаются операции XOR с соответствующими Q битами контента последовательности R поочередно, то есть D0^R[0,Q-1], D1^R[Q,2Q-1], D2^R[2Q,3Q-1], …, DT-1^R[(T-1)Q, TQ-1], пока весь контент R-последовательности не будет пройден один раз, и в этот момент один большой период скремблирования завершается. Последующая обработка скремблирования повторяет описанный выше процесс, пока работа по скремблированию текущего кадра не будет завершена. Процесс дескремблирования в точности повторяет описанный выше процесс скремблирования.

Скремблирующее/дескремблирующее устройство для параллельной кадровой синхронизации, разработанное в данном изобретении, реализуется на основе описанного выше теоретического принципа, как показано на фиг.1. Устройство состоит из трех блоков, а именно, блока управления, устройства хранения данных и блока XOR, как показано на фиг.1. Когда требуется скремблирование кадровой синхронизации, после того как параллельные данные вводятся в скремблирующее устройство, блок управления берет часть контента соответствующей М-последовательности из устройства хранения данных; и затем они подвергаются операции XOR в блоке XOR, чтобы получить скремблированные данные. Когда устройство используется в качестве дескремблирующего устройства, входные данные являются скремблированными данными, и та же самая часть М-последовательности извлекается блоком управления из устройства хранения данных; и подвергается операции XOR со скремблированными данными в блоке XOR, чтобы получить дескремблированные параллельные данные. Скремблирующее/дескремблирующее устройство для параллельной кадровой синхронизации согласно данному изобретению не ограничивает разрядность входных параллельных данных и характеристическое уравнение М-последовательности, и для более высокой разрядности и более длинной последовательности скремблирования увеличиваются только емкость и сложность блока управления и устройства хранения данных. Данное изобретение позволяет реализовать функции скремблирования и дескремблирования на относительно низкой скорости и таким образом применимо к системе передачи SDH/SONET и другим системам связи, использующим схему скремблирования кадровой синхронизации.

На фиг.1 блок управления является генератором адреса, а устройство хранения данных является генератором М-последовательности. Как показано на фиг.2, предполагается, что разрядность параллельных данных равна q, и самый высокий порядок характеристического уравнения М равен r. Число допустимых адресных строк, выводимых генератором адреса, равно r, и диапазон управляемых адресов равен 1-2r-1. Согласно сигналу кадровой синхронизации выходным адресом управляют так, чтобы он был адресом 1, и затем, согласно входной тактовой синхронизации, к адресу добавляется 1 в каждый допустимый момент данных до достижения самого верхнего адреса 27-1, после которого следует возврат снова к адресу 1 и очередное прохождение диапазона адресов. После того как скремблирование/ дескремблирование одного кадра завершается, следует ожидание сигнала кадровой синхронизации нового кадра, и адрес перенаправляется к начальному адресу 1, чтобы запустить обработку накопления адреса для нового кадра. Генератор М-последовательности обычно реализуется памятью RAM или ROM, и допустимое пространство данных является q×2r-1 битами. Согласно порядку битов, сгенерированных псевдослучайной последовательностью, М-последовательности заполняются поочередно, начиная с бита М1 до бита M2r-1, и всего заполняется q М-последовательностей с длиной 2r-1. Диапазон, соответствующий каждому адресу, выводимому контроллером, составляет q битов, и размер, соответствующий 2r-1 адресным пространствам, составляет точно 2r-1×q, что соответствует q полным М-последовательностям с длинами 2r-1. Согласно адресу, выведенному генератором адреса, генератор М-последовательности извлекает действительный контент М-последовательности согласно индексному адресу для выполнения операции XOR с входными параллельными данными/скремблированными данными, таким образом получая действительные скремблированные данные/восстановленные параллельные данные после дескремблирования.

Примеры

Описание будет сделано на примере устройства параллельного скремблирования кадровой синхронизации для сигнала SDH STM-256 с разрядностью 256 битов со ссылкой на фиг.3, но все схемы применимы к устройствам параллельного скремблирования кадровой синхронизации с другими разрядностями.

Система работает с тактовой частотой 155,52 МГц, и скремблирующая функция реализуется при параллельной ширине 256 битов. Генератор М-последовательности образован памятью ROM. Так как характеристический полиномиал скремблирования SDH х7+x6+1, и используется псевдослучайная последовательность с периодом 27-1 бита, то есть 127 битов, его емкость составляет (27-1×256) битов, и 27-1 являются глубиной пространства хранения; а ширина пространства хранения составляет 256, и в таком пространстве может быть сохранен контент 256 псевдослучайных последовательностей по 127 битов каждая. Нужно отметить, что М на фиг.3 указывает целую псевдослучайную последовательность из 127 битов, а m1, m2… указывают контент битовых позиций, соответствующих псевдослучайным последовательностям.

На фиг.3 преобразователь последовательного кода в параллельный реализует восстановление синхронизации, синхронный захват и последовательно-параллельное преобразование, и выводит параллельные данные с шириной слова 256 битов и сигнал тактовой синхронизации (CLK). Декадрирующее устройство генерирует сигнал индикации кадровой синхронизации, выровненный с первым словом из 256 битов в структуре кадра STM-256, и параллельные данные из 256 битов после кадровой синхронизации посредством обнаружения байтов кадрирования А1А2 в сигнале обнаружения. Генератор адреса вычисляет адреса строки и столбца в структуре кадра SDH и получает табличный адрес ROM скремблирования согласно адресам строки и столбца. Когда происходит индикация кадровой синхронизации, адреса строки и столбца направляются к начальной позиции структуры кадра, и к адресу столбца каждый раз добавляется 1 под управлением индикации синхронизации. Когда адрес столбца ≥270×256/8-1=8639, адрес столбца направляется к первому столбцу структуры кадра, и тем временем к адресу строки добавляется 1. Когда адрес строки ≥8 и адрес столбца S8639, адреса строки и столбца перенаправляются к начальной позиции структуры кадра. С другой стороны, когда происходит индикация кадровой синхронизации, табличный адрес ROM адресуется на 0, и так как 9×N байтов в первой строке заголовка секции STM-N не скремблированы, когда адрес строки равен 0, и адрес столбца ≥9×256/8-1=287, табличный адрес начинает проходить всю ROM периодически от адресов ADDR0×00 до ADDR0×7E, и тем временем выводится скремблированный кадр данных STM-256, полученный после выполнения операции XOR на контенте М-последовательности, сохраненном по соответствующему адресу ROM, и параллельные данные из 256 битов, пока адрес строки не будет ≥8 и адрес столбца не будет ≥8639, и адрес поисковой таблицы перенаправляется на адрес 0. Таким образом, процесс скремблирования целого кадра завершается. Процесс дескремблирования аналогичен вышеописанному скремблированию.

Вышеупомянутое описание является только предпочтительным примером осуществления данного изобретения и не предназначается для ограничения объема данного изобретения.

Изобретение относится к технике цифровой связи и может быть использовано в сетях синхронной цифровой иерархии/синхронных оптических сетях. Скремблирующее устройство для параллельной кадровой синхронизации включает блок управления, используемый, для последовательного считывания псевдослучайной последовательности из устройства хранения данных и получения контента, соответствующего параллельным данным в этой псевдослучайной последовательности, устройство хранения данных, сконфигурированное для хранения псевдослучайной последовательности, которая является заранее заданной, и введения контента, соответствующего параллельным данным в псевдослучайной последовательности, в блок XOR, который выполняет обработку XOR поочередно для параллельных данных, которые вводятся последовательно, с контентом, соответствующим параллельным данным в псевдослучайной последовательности, и затем выводит скремблированные данные. В случае, когда битовая разрядность параллельных данных равна Q, контент, соответствующий параллельным данным в псевдослучайной последовательности, представляет собой Q битов контента, а длина псевдослучайной последовательности равна T×Q, и она состоит из Q М-последовательностей псевдослучайного кода, где Т является периодом цикла повторения М-последовательностей. Технический результат - уменьшение сложности вычислений. 2 н. и 6 з.п. ф-лы, 3 ил.

1. Скремблирующее устройство для параллельной кадровой синхронизации, включающее блок управления, устройство хранения данных и блок XOR (исключающее ИЛИ), при этом

блок управления конфигурирован так, чтобы последовательно считывать псевдослучайную последовательность из устройства хранения данных и получать контент, соответствующий параллельным данным в этой псевдослучайной последовательности;

устройство хранения данных конфигурировано так, чтобы хранить псевдослучайную последовательность, которая является заранее заданной, и вводить контент, соответствующий параллельным данным в псевдослучайной последовательности, в блок XOR;

блок XOR конфигурирован так, чтобы выполнять обработку XOR поочередно для параллельных данных, которые вводятся последовательно, с контентом, соответствующим параллельным данным в псевдослучайной последовательности, полученной из устройства хранения данных, и затем выводить скремблированные данные;

причем в ситуации, когда битовая разрядность параллельных данных равна Q, контент, соответствующий параллельным данным в псевдослучайной последовательности, представляет собой Q битов контента, соответствующего параллельным данным в псевдослучайной последовательности; и

длина псевдослучайной последовательности равна T×Q и она состоит из Q М-последовательностей псевдослучайного кода, где Т является периодом цикла повторения М-последовательностей.

2. Скремблирующее устройство по п.1, в котором блок управления также конфигурирован так, чтобы по кругу согласно Т под управлением кадрового сигнала синхронизации получать поочередно Q битов М-последовательностей, соответствующих параллельным данным в псевдослучайной последовательности.

3. Скремблирующее устройство по п.1, в котором блок XOR также конфигурирован так, чтобы выполнять обработку XOR поочередно для параллельных данных, которые вводятся последовательно, с Q битами М-последовательностей, соответствующих параллельным данным в псевдослучайной последовательности, пока обход T×Q битов М-последовательностей не завершается.

4. Скремблирующее устройство по п.2 или 3, в котором блок управления является генератором адреса; а устройство хранения данных является генератором М-последовательности.

5. Дескремблирующее устройство для параллельной кадровой синхронизации, включающее устройство хранения данных, блок управления и блок XOR; при этом

блок управления конфигурирован так, чтобы считывать псевдослучайную последовательность из устройства хранения данных последовательно и получать контент, соответствующий скремблированным данным в псевдослучайной последовательности;

устройство хранения данных конфигурировано так, чтобы хранить псевдослучайную последовательность, которая является заранее заданной, и вводить контент, соответствующий скремблированным данным в псевдослучайной последовательности, в блок XOR;

блок XOR конфигурирован так, чтобы выполнять обработку XOR поочередно для скремблированных данных, которые вводятся последовательно, с контентом, соответствующим скремблированным данным в псевдослучайной последовательности, полученной из устройства хранения данных, и затем

выводить параллельные данные, полученные после дескремблирования;

причем в ситуации, когда битовая разрядность скремблированных данных равна Q, контент, соответствующий скремблированным данным в псевдослучайной последовательности, представляет собой Q битов контента, соответствующего скремблированным данным в псевдослучайной последовательности; и

длина псевдослучайной последовательности равна T×Q и она состоит из Q М-последовательностей псевдослучайного кода, где Т является периодом цикла повторения М-последовательностей.

6. Дескремблирующее устройство по п.5, в котором блок управления также конфигурирован так, чтобы по кругу согласно Т под управлением кадрового сигнала синхронизации получать поочередно Q битов М-последовательностей, соответствующих скремблированным данным в псевдослучайной последовательности.

7. Дескремблирующее устройство по п.5, в котором блок XOR также конфигурирован так, чтобы выполнять обработку XOR поочередно для скремблированных данных, которые вводятся последовательно, с Q битами М-последовательностей, соответствующих скремблированным данным в псевдослучайной последовательности, пока обход T×Q битов М-последовательностей не завершается.

8. Дескремблирующее устройство по п.6 или 7, в котором блок управления является генератором адреса, а устройство хранения данных является генератором М-последовательности.

| US 20030072449 A1, 17.04.2003 | |||

| KR 2003059508 А, 10.03.2003 | |||

| КАДРОВАЯ СИНХРОНИЗАЦИЯ И ИДЕНТИФИКАЦИЯ СКРЕМБЛИРУЮЩЕГО КОДА В СИСТЕМАХ БЕСПРОВОДНОЙ СВЯЗИ И СПОСОБЫ ДЛЯ ЭТОГО | 2004 |

|

RU2352076C2 |

| WO 1999029078 A3, 10.06.1999. | |||

Авторы

Даты

2014-01-27—Публикация

2010-06-10—Подача