Предлагаемое изобретение относится к области вычислительной техники, автоматики и может использоваться в различных системах автоматического управления, передачи информации и т.п.

В различных вычислительных и управляющих системах широко используются мажоритарные логические элементы (МЛЭ), реализованные на основе эмиттерно-связанной логики [1-9], работающие по законам булевой алгебры и имеющие по выходу два логических состояния «0» и «1», характеризующихся низким и высоким потенциалами.

В работах [10-12], а также монографиях соавтора настоящей заявки [14-15] показано, что булева алгебра является частным случаем более общей линейной алгебры, практическая реализация которой в структуре вычислительных и логических устройств автоматики нового поколения требует создания специальной элементной базы, реализуемой на основе логики с многозначным внутренним представлением сигналов, в которой эквивалентом стандартного логического сигнала является квант тока. Заявляемое устройство МЛЭ относится к этому типу логических элементов.

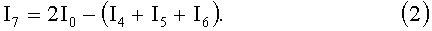

Ближайшим прототипом заявляемого устройства является мажоритарный логический элемент, представленный в патенте US 4.617.475, fig.2. Он содержит первый 1, второй 2 и третий 3 коммутаторы квантов тока I0 с объединенными токовыми выходами 4, 5, 6, управляемые соответствующими источниками входных логических сигналов 7, 8, 9, выходной транзистор 10, коллектор которого является токовым выходом 11 устройства, согласованным с первой 12 шиной источника питания, а эмиттер связан со второй 13 шиной источника питания через опорный источник кванта тока 14, вспомогательный источник опорного тока 15.

Существенный недостаток известного мажоритарного логического элемента состоит в том, что он, используя потенциальные двоичные сигналы, обладает усложненной структурой связей, нелинейностью рабочих режимов элементов и критичностью параметров элементов его структуры, а также параметров входных сигналов, что в конечном итоге приводит к снижению его быстродействия.

Основная задача предлагаемого изобретения состоит в создании мажоритарного логического элемента, в котором внутреннее преобразование информации производится в многозначной форме токовых сигналов, определяемой состоянием входных потенциальных двоичных сигналов. В конечном итоге это позволяет повысить быстродействие и создать элементную базу вычислительных устройств, работающих на принципах многозначной линейной алгебры - как более общей теории математической логики, для которой известная булева логика является ее частным случаем.

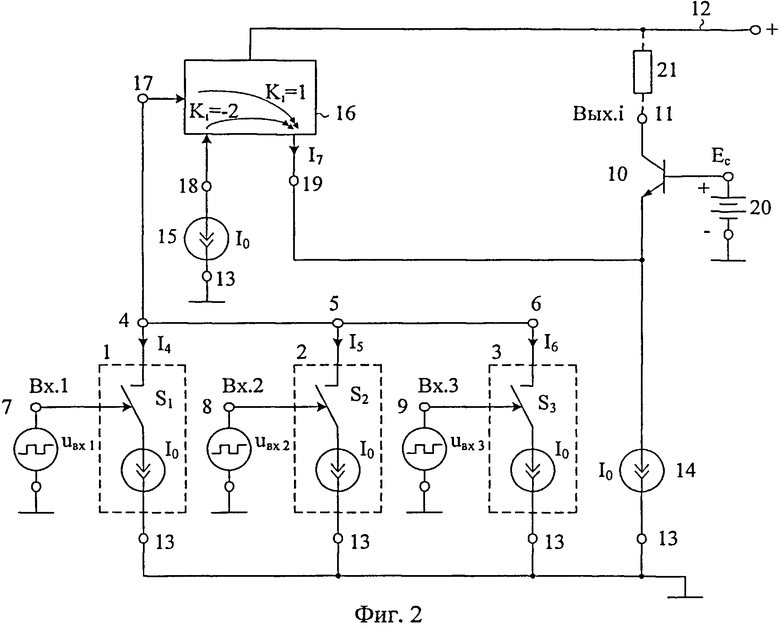

Поставленная задача решается тем, что в мажоритарном элементе с многозначным внутренним представлением сигналов (фиг.1), содержащем первый 1, второй 2 и третий 3 коммутаторы квантов тока I0 с объединенными токовыми выходами 4, 5, 6, управляемые соответствующими источниками входных логических сигналов 7, 8, 9, выходной транзистор 10, коллектор которого является токовым выходом 11 устройства, согласованным с первой 12 шиной источника питания, а эмиттер связан со второй 13 шиной источника питания через опорный источник кванта тока 14, вспомогательный источник опорного тока 15, предусмотрены новые элементы и связи - в схему введено дополнительное токовое зеркало 16, согласованное с первой 12 шиной источника питания, неинвертирующий токовый вход которого 17 соединен с объединенными токовыми выходами 4, 5, 6 первого 1, второго 2 и третьего 3 коммутаторов квантов тока I0, между инвертирующим токовым входом 18 дополнительного токового зеркала 16 и второй 13 шиной источника питания включен вспомогательный источник опорного тока 15, а токовый выход 19 дополнительного токового зеркала 16 соединен с эмиттером выходного транзистора 10, причем база выходного транзистора 10 связана с источником опорного напряжения 20.

Схема мажоритарного логического элемента-прототипа показана на чертеже фиг.1. На чертеже фиг.2 представлена схема заявляемого устройства в соответствии с формулой изобретения.

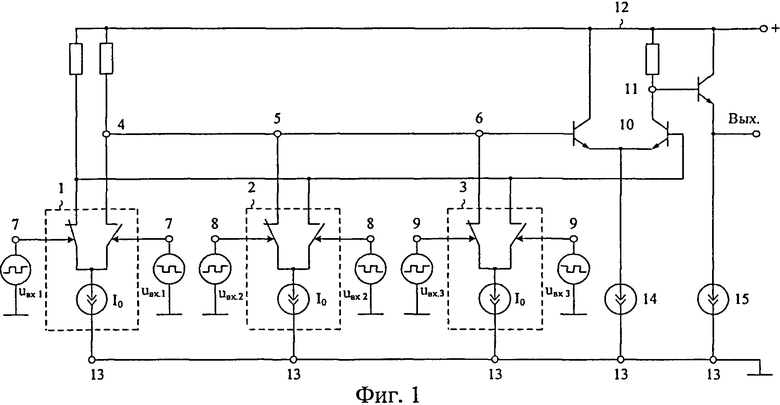

На чертеже фиг.3 приведена одна из возможных схем дополнительного токового зеркала 16.

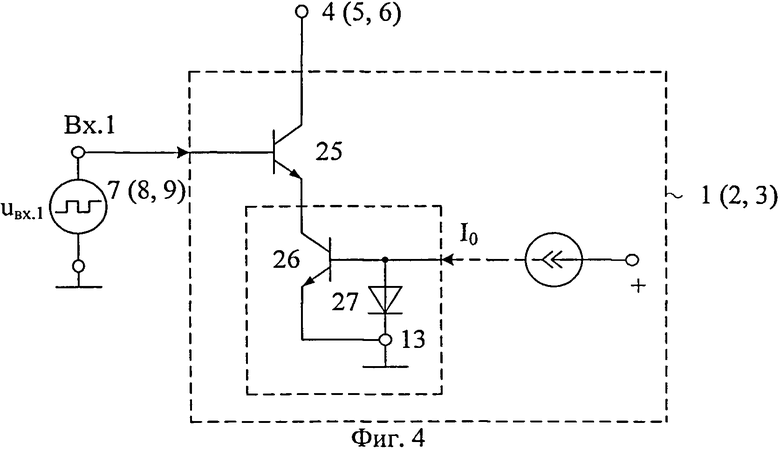

На чертеже фиг.4 приведена первая возможная схема первого 1, второго 2 и третьего 3 входных коммутаторов кванта тока 10, реализованных по каскодной схеме на элементах 25-27.

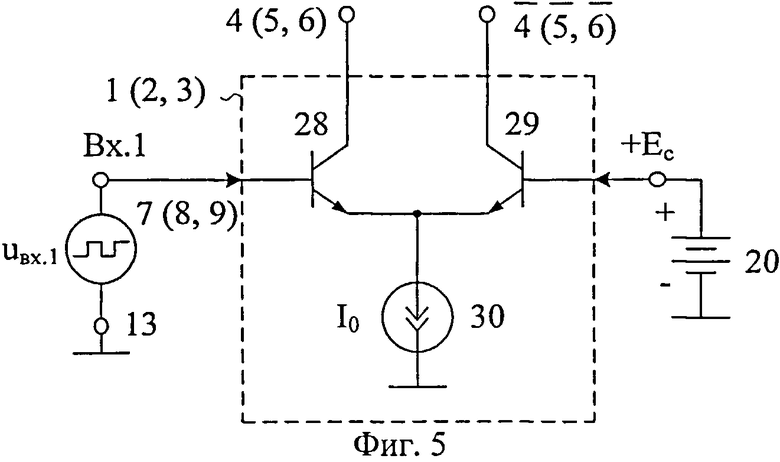

На чертеже фиг.5 приведены входные коммутаторы 1, 2, 3 квантов тока 10, реализованные на основе дифференциальных каскадов на элементах 28, 29, 30.

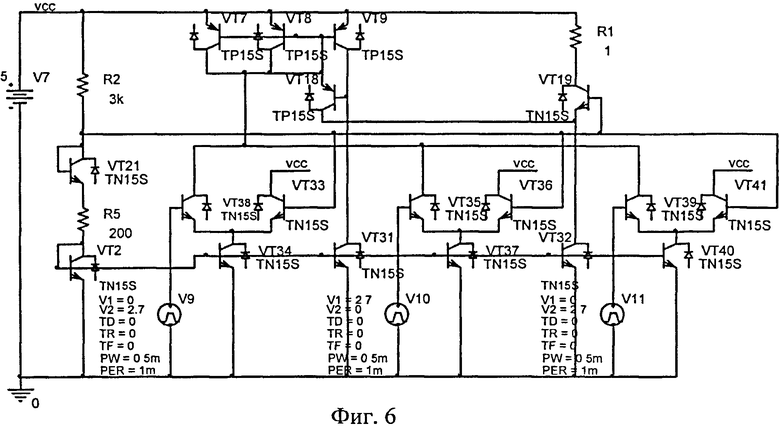

На чертеже фиг.6 представлена схема заявляемого мажоритарного элемента фиг.2 в среде Pspise на моделях интегральных транзисторов ФГУП НЛП «Пульсар».

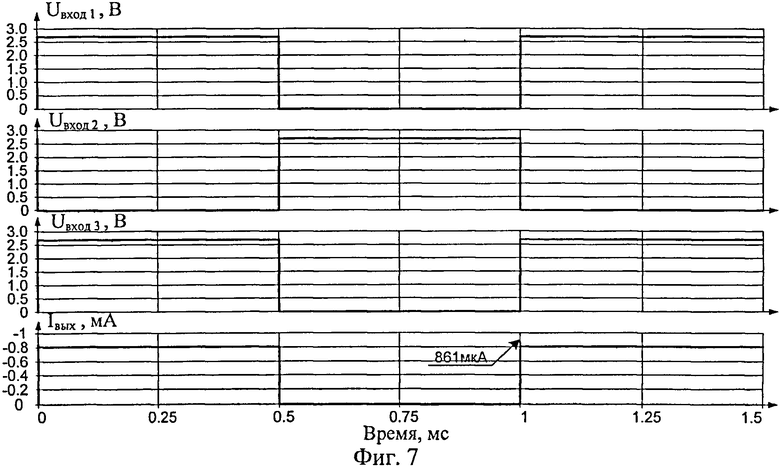

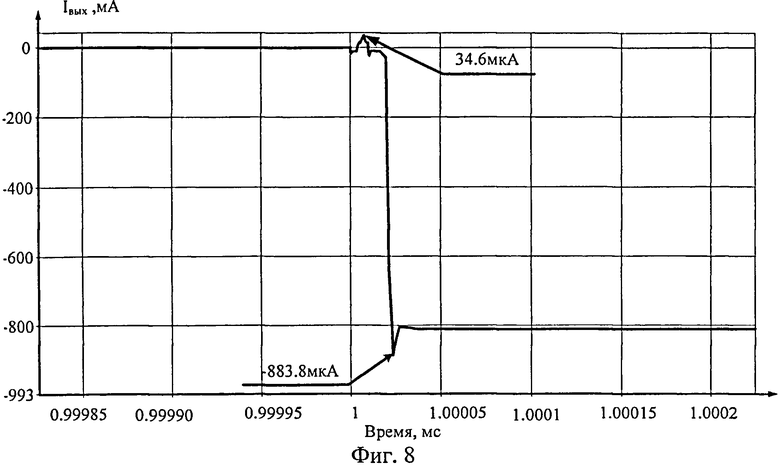

На чертеже фиг.7 показаны временные диаграммы токов и напряжений в схеме фиг.6, а на чертеже фиг.8 представлена временная зависимость выходного тока МЛЭ в увеличенном масштабе.

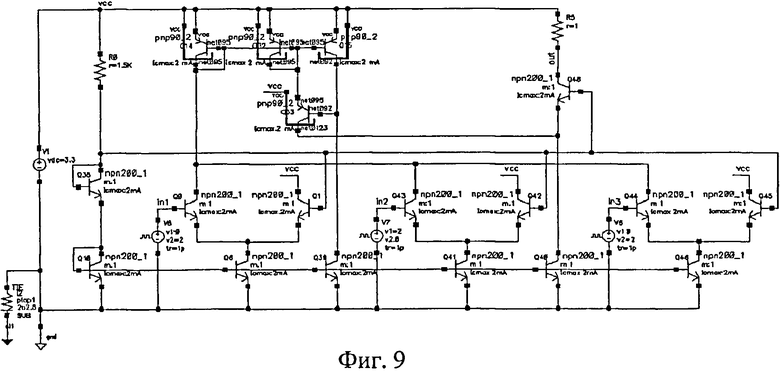

На чертеже фиг.9 представлена схема мажоритарного элемента фиг.2 в среде Cadence на моделях SiGe интегральных транзисторов.

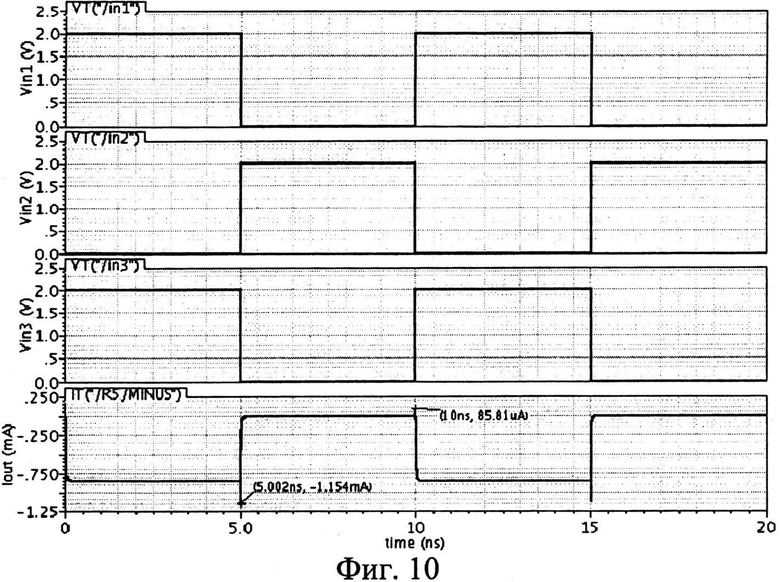

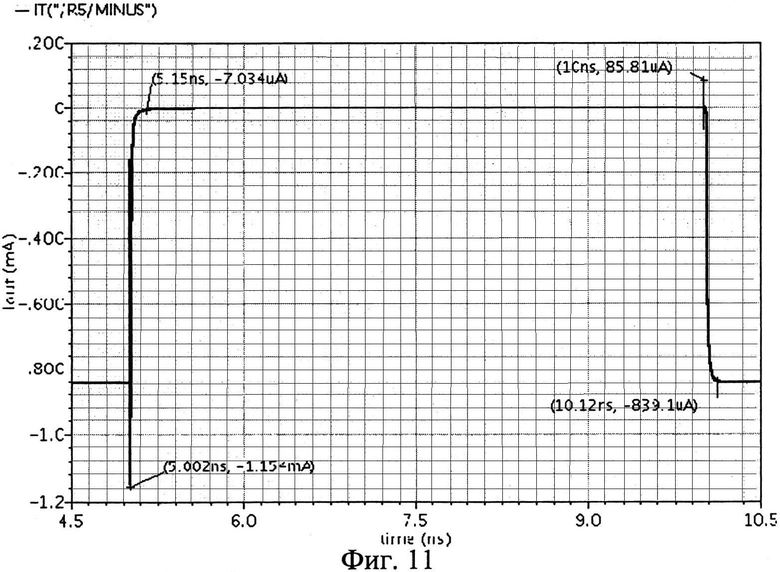

На чертеже фиг.10 показана осциллограмма входных напряжений 7, 8, 9 и выходного тока МЛЭ фиг.9, а на чертеже фиг.11 - осциллограмма выходного тока МЛЭ фиг.9 в увеличенном масштабе.

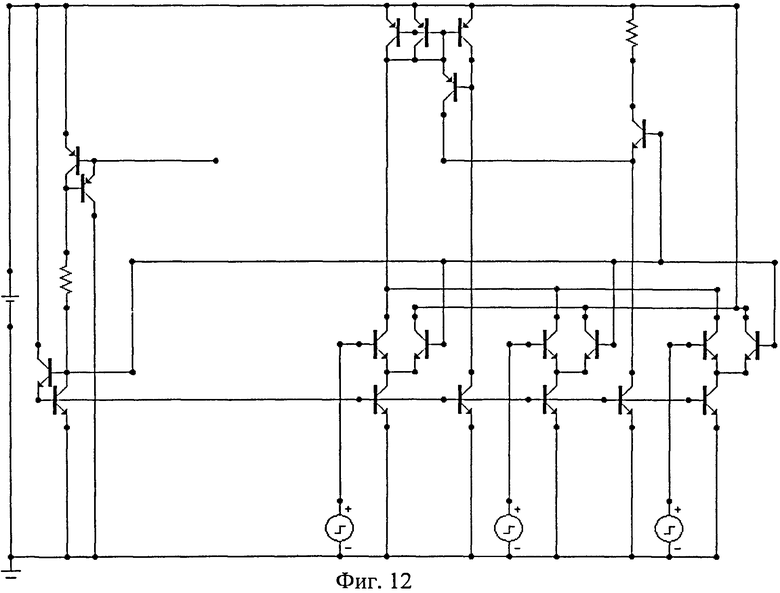

На чертеже фиг.12 представлена схема мажоритарного элемента фиг.2 в среде Micro-Cap на моделях дискретных транзисторов, а на чертеже фиг.13 показаны временные диаграммы мажоритарного элемента фиг.12 для потенциальных и токовых сигналов.

Мажоритарный элемент с многозначным внутренним представлением сигналов фиг.2 содержит первый 1, второй 2 и третий 3 коммутаторы квантов тока I0 с объединенными токовыми выходами 4, 5, 6, управляемые соответствующими источниками входных логических сигналов 7, 8, 9, выходной транзистор 10, коллектор которого является токовым выходом 11 устройства, согласованным с первой 12 шиной источника питания, а эмиттер связан со второй 13 шиной источника питания через опорный источник кванта тока 14, вспомогательный источник опорного тока 15. В схему введено дополнительное токовое зеркало 16, согласованное с первой 12 шиной источника питания, неинвертирующий токовый вход которого 17 соединен с объединенными токовыми выходами 4, 5, 6 первого 1, второго 2 и третьего 3 коммутаторов квантов тока I0, между инвертирующим токовым входом 18 дополнительного токового зеркала 16 и второй 13 шиной источника питания включен вспомогательный источник опорного тока 15, а токовый выход 19 дополнительного токового зеркала 16 соединен с эмиттером выходного транзистора 10, причем база выходного транзистора 10 связана с источником опорного напряжения 20.

Дополнительное токовое зеркало 16 (фиг.3), имеющее два противофазных токовых входа 17 и 18, реализовано на транзисторах 22-24, причем коэффициент передачи по току со входа 18 равен Ki=-1, а со входа 17-Ki=+1.

Входные коммутаторы квантов тока I0 1, 2, 3 могут быть реализованы по каскодной схеме фиг.4 (элементы 25, 26, 27) или на основе дифференциального каскада фиг.5 (элементы 28, 29, 30).

Рассмотрим работу предлагаемой схемы МЛЭ фиг.2.

Синтез схемы мажоритарного элемента на примере трехвходового элемента производится в соответствии с его логической функцией, которая представляется в линейной алгебре предикатом

где k - значность логики,

x1, x2, x3 - входные сигналы.

Реализация предиката производится посредством дополнительного токового зеркала 16 (фиг.3), выполняющего вычитание сигнала на входе 17 из сигнала на входе 18. На вход 18 подается удвоенное значение кванта тока от источника тока 15, а на вход 17 - сумма квантов выходных токов I4, I5, I6 с выходов коммутаторов 1, 2, 3 соответственно. На выходе 19 дополнительного токового зеркала 16 формируется сигнал разности:

Величина этого сигнала в зависимости от сочетаний вычитаемых сигналов может иметь значение 2, 1, 0 или -1. Из этого сигнала вычитается квант тока I0 источника тока 14. Если при этом I7>I0, то выходной транзистор 10 заперт и выходной ток мажоритарного элемента равен «0», что соответствует логическому нулю, если I7<I0 (т.е. I7=0), то выходной транзистор 10 открыт и выходной ток мажоритарного элемента равен I0. Как видно приведенного описания, реализация логической функции мажоритарного элемента здесь производится формированием алгебраической суммы квантов тока и выделением определенных значений этой суммы токов. Все элементы приведенной схемы работают в активном режиме, предполагающем отсутствие насыщения в процессе переключений, что повышает общее быстродействие схемы. Кроме того, использование многозначного внутреннего представления сигналов повышает информативность линий связи, что уменьшает их количество. Использование стабильных значений квантов тока, а также определение выходного сигнала разностью этих токов обеспечивает малую зависимость функционирования схемы от внешних дестабилизирующих факторов (девиация питающего напряжения, радиационное и температурное воздействия, синфазная помеха и др.).

Другие варианты предлагаемых схем МЛЭ работают аналогично.

Отличием мажоритарного логического элемента по схемам фиг.6- 9 является реализация входных коммутаторов квантов тока 1, 2, 3 (токовых ключей S1, S2 и S3) в виде дифференциальных каскадов. Вариант такой реализации коммутаторов кванта тока I0 приведен на чертеже фиг.5. Здесь дифференциальный каскад производит коммутацию кванта тока I0. При этом источник тока 30 при любом состоянии входного логического сигнала не выходит из активного режима, что повышает быстродействие схемы.

Отличием мажоритарного логического элемента по схеме фиг.12 является реализация его входных коммутаторов квантов тока I0 в виде каскодной структуры фиг.4

Показанные на чертежах фиг.7, фиг.8, фиг.10, фиг.11, фиг.13 результаты моделирования заявляемого МЛЭ при его реализации на качественно разных технологических процессах подтверждают указанные свойства предлагаемых схем. Следует отметить, что кратковременные импульсы на выходе МЛЭ, возникающие в момент переключения входных сигналов (фиг.13), характерные и для других известных логических элементов, определяются различными временами переключения входных коммутаторов квантов тока 1, 2, 3 и могут быть устранены в реальных схемах средствами технологии (фиг.7, фиг.10).

Таким образом, рассмотренные схемотехнические решения мажоритарного логического элемента характеризуются многозначным внутренним и двузначным токовым представлением сигналов и могут быть положены в основу перспективных вычислительных и управляющих устройств, использующих многозначную линейную алгебру, частным случаем которой является булева алгебра.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US 4.423.339.

2. Патентная заявка US 2010/005373.

3. Патент US 5.084.878.

4. Патент US 5.907.671.

5. Патент RU 2393528.

6. Патент US 4.789.795.

7. Патент US 8.069.403.

8. Патент US 6.253.348.

9. Патент US 7.236.005.

10. Боголюбов И.Н., Овсиевич Б.Л., Розенблюм Л.Я. Пороговая и мажоритарная логика // Технич. кибернетика // Информационный листок, 1964. №2 (29).

11. Чернов Н.И. Основы теории логического синтеза цифровых структур над полем вещественных чисел // Монография. - Таганрог: ТРТУ, 2001. - 147 с.

12. Чернов Н.И. Линейный синтез цифровых структур АСОИУ» // Учебное пособие Таганрог. - ТРТУ, 2004 г., 118 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ "ИСКЛЮЧАЮЩЕЕ ИЛИ" С МНОГОЗНАЧНЫМ ВНУТРЕННИМ ПРЕДСТАВЛЕНИЕМ СИГНАЛОВ | 2012 |

|

RU2506695C1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ "И" С МНОГОЗНАЧНЫМ ВНУТРЕННИМ ПРЕДСТАВЛЕНИЕМ СИГНАЛОВ | 2012 |

|

RU2509412C1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ "2-И" С МНОГОЗНАЧНЫМ ВНУТРЕННИМ ПРЕДСТАВЛЕНИЕМ СИГНАЛОВ | 2012 |

|

RU2513717C1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ "2-И" С МНОГОЗНАЧНЫМ ВНУТРЕННИМ ПРЕДСТАВЛЕНИЕМ СИГНАЛОВ | 2012 |

|

RU2513478C1 |

| ТОКОВЫЙ ПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ "РАВНОЗНАЧНОСТЬ" | 2018 |

|

RU2712412C1 |

| ТОКОВЫЙ ПОРОГОВЫЙ ПАРАЛЛЕЛЬНЫЙ ТРОИЧНЫЙ КОМПАРАТОР | 2020 |

|

RU2723672C1 |

| ТОКОВЫЙ ПОРОГОВЫЙ ЭЛЕМЕНТ "СУММАТОР ПО МОДУЛЮ ТРИ" | 2020 |

|

RU2725165C1 |

| МНОГОЗНАЧНЫЙ СУММАТОР ПО МОДУЛЮ k | 2014 |

|

RU2546078C1 |

| ДВОИЧНЫЙ ТОКОВЫЙ ПОРОГОВЫЙ RS-ТРИГГЕР | 2018 |

|

RU2695979C1 |

| ТОКОВЫЙ ПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ "НЕРАВНОЗНАЧНОСТЬ" | 2018 |

|

RU2692573C1 |

Изобретение относится к области вычислительной техники и автоматики. Техническим результатом является повышение быстродействия мажоритарного элемента. Мажоритарный элемент с многозначным внутренним представлением сигналов содержит первый (1), второй (2) и третий (3) коммутаторы квантов тока I0 с объединенными токовыми выходами (4), (5), (6), управляемые соответствующими источниками входных логических сигналов (7), (8), (9), выходной транзистор (10), коллектор которого является токовым выходом (11) устройства, согласованным с первой (12) шиной источника питания, а эмиттер связан со второй (13) шиной источника питания через опорный источник кванта тока (14), вспомогательный источник опорного тока (15). В схему введено дополнительное токовое зеркало (16), согласованное с первой (12) шиной источника питания, неинвертирующий токовый вход которого (17) соединен с объединенными токовыми выходами (4), (5), (6) первого (1), второго (2) и третьего (3) коммутаторов квантов тока I0, между инвертирующим токовым входом (18) дополнительного токового зеркала (16) и второй (13) шиной источника питания включен вспомогательный источник опорного тока (15), а токовый выход (19) дополнительного токового зеркала (16) соединен с эмиттером выходного транзистора (10), причем база выходного транзистора (10) связана с источником опорного напряжения (20). 13 ил.

Мажоритарный элемент с многозначным внутренним представлением сигналов, содержащий первый (1), второй (2) и третий (3) коммутаторы квантов тока I0 с объединенными токовыми выходами (4), (5), (6), управляемые соответствующими источниками входных логических сигналов (7), (8), (9), выходной транзистор (10), коллектор которого является токовым выходом (11) устройства, согласованным с первой (12) шиной источника питания, а эмиттер связан со второй (13) шиной источника питания через опорный источник кванта тока (14), вспомогательный источник опорного тока (15), отличающийся тем, что в схему введено дополнительное токовое зеркало (16), согласованное с первой (12) шиной источника питания, неинвертирующий токовый вход которого (17) соединен с объединенными токовыми выходами (4), (5), (6) первого (1), второго (2) и третьего (3) коммутаторов квантов тока I0, между инвертирующим токовым входом (18) дополнительного токового зеркала (16) и второй (13) шиной источника питания включен вспомогательный источник опорного тока (15), а токовый выход (19) дополнительного токового зеркала (16) соединен с эмиттером выходного транзистора (10), причем база выходного транзистора (10) связана с источником опорного напряжения (20).

| US 4617475 A, 14.10.1986 | |||

| US 6130559 A, 10.10.2000 | |||

| US 4423339 A, 27.12.1983 | |||

| Согласующее устройство | 1985 |

|

SU1262719A1 |

| Мажоритарный логический элемент | 1973 |

|

SU683025A1 |

Авторы

Даты

2014-02-10—Публикация

2012-09-10—Подача