Изобретение относится к области вычислительной техники, автоматики, связи и может использоваться в различных цифровых структурах и системах автоматического управления, передачи цифровой информации. Техническим результатом является повышение быстродействия систем обработки информации и создание элементной базы вычислительных устройств, работающих на принципах многозначной линейной алгебры. Такой результат достигается за счет создания двоичного токового порогового RS-триггера с прямыми и инверсными входами, в котором внутреннее преобразование информации производится в токовой форме сигналов на пороговых логических элементах. Устройство содержит четыре токовых зеркала, четыре источника опорного тока, четыре источника напряжения смещения, восемь транзисторов.

В различных цифровых и аналого-цифровых вычислительных и управляющих устройствах широко используются классические RS-триггеры [1-35], входными и выходными логическими сигналами которых являются заданные уровни напряжений (высокий - соответствующий логической единице «1», низкий - логическому нулю «0»). На базе данных функциональных узлов сегодня реализуется 95-98% компьютеров различного назначения. Однако традиционные средства вычислительной техники, основой которых является булева алгебра, достигли сегодня предельных возможностей по быстродействию и способности обеспечить надежную работу в условиях дестабилизирующих факторов.

В работе [36], а также монографиях соавтора настоящей заявки [37, 38] показано, что булева алгебра является частным случаем более общей линейной алгебры, практическая реализация которой в структуре вычислительных и логических устройств автоматики нового поколения требует создания специальной элементной базы, реализуемой на основе логики с многозначным внутренним представлением сигналов, в которой эквивалентом стандартного логического сигнала является квант тока. Заявляемое устройство относится к этому типу логических элементов.

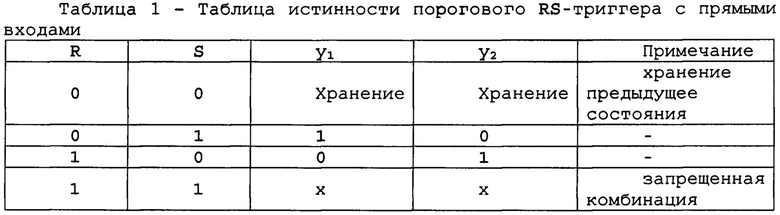

Ближайшим прототипом заявляемого устройства является патент RU 2604682 («RS-триггер», МПК Н03K 3/037, Н03K 19/00, 2016 г. ). Он содержит (фиг. 1) первый 1 (R) и второй 2 (S) логические входы устройства, первый 3 и второй 4 выходы устройства, первый 5 и второй 6 входные транзисторы, базы которых подключены к первому 7 источнику напряжения смещения, третий 8 и четвертый 9 входные транзисторы другого типа проводимости с объединенными базами, которые подключены ко второму 10 источнику напряжения смещения, коллекторы третьего 8 и четвертого 9 входных транзисторов подключены к первой 11 шине источника питания, эмиттеры первого 5 и третьего 8 входных транзисторов объединены, первое 12 и второе 13 токовые зеркала, согласованные с первой 11 шиной источника питания, выход первого 12 токового зеркала связан со второй 14 шиной источника питания через первый 15 источник опорного тока, второй 16 источник опорного тока включен между второй 14 шиной источника питания и объединенными эмиттерами первого 5 и третьего 8 входных транзисторов, эмиттеры второго 6 и четвертого 9 входных транзисторов объединены и подключены к выходу первого 12 токового зеркала.

Существенный недостаток известного устройства состоит в том, что он не реализует работу с пороговыми представлениями логических функций, а устойчивое состояние кольца положительной обратной связи обеспечивается увеличением коэффициентов передачи токовых зеркал (в данном случае выбраны коэффициенты передачи равные 2). Кроме того, известная схема имеет погрешности преобразования сигналов, происходящие на каждой операции, эти погрешности неизбежно суммируются в выходном сигнале и могут приводить к заметным общим отклонениям от уровней опорных сигналов. Это не позволяет создать на его основе полный базис средств вычислительной техники, функционирующих на принципах преобразования токовых сигналов.

Основная задача предлагаемого изобретения состоит в создании порогового RS-триггера, в котором внутреннее преобразование информации производится в многозначной токовой форме сигналов с использованием пороговых логических элементов. В конечном итоге это позволяет повысить быстродействие систем обработки информации и создать элементную базу вычислительных устройств, работающих на принципах линейной алгебры [36-38].

Поставленная задача достигается тем, что RS-триггере, содержащем первый 1 (R) и второй 2 (S) логические входы устройства, первый 3 и второй 4 выходы устройства, первый 5 и второй 6 входные транзисторы, базы которых подключены к первому 7 источнику напряжения смещения, третий 8 и четвертый 9 входные транзисторы другого типа проводимости с объединенными базами, которые подключены ко второму 10 источнику напряжения смещения, коллекторы третьего 8 и четвертого 9 входных транзисторов подключены к первой 11 шине источника питания, эмиттеры первого 5 и третьего 8 входных транзисторов объединены, первое 12 и второе 13 токовые зеркала, согласованные с первой 11 шиной источника питания, выход первого 12 токового зеркала связан со второй 14 шиной источника питания через первый 15 источник опорного тока, второй 16 источник опорного тока включен между второй 14 шиной источника питания и объединенными эмиттерами первого 5 и третьего 8 входных транзисторов, эмиттеры второго 6 и четвертого 9 входных транзисторов объединены и подключены к выходу первого 12 токового зеркала, предусмотрены новые элементы и связи - в схему введены первый 17, второй 18, третий 19 и четвертый 20 дополнительные транзисторы, первый 21 и второй 22 дополнительные источники напряжения смещения, первый 23 и второй 24 дополнительные источники опорного тока, первое 25 и второе 26 дополнительные токовые зеркала, причем коллекторы первого 5 и второго 6 входных транзисторов подключены ко второй 14 шине источника питания, первый 1 (R) логический вход устройства подключен к объединенным эмиттерам первого 5 и третьего 8 входных транзисторов, второй 2 (S) логический вход устройства подключен к выходу первого 12 токового зеркала, база первого 17 дополнительного транзистора подключена к объединенным эмиттерам первого 5 и третьего 8 входных транзисторов, база второго 18 дополнительного транзистора соединена с первым 21 дополнительным источником напряжения смещения, объединенные эмиттеры первого 17 и второго 18 дополнительных транзисторов подключены ко второй 14 шине источника питания через первый 23 дополнительный источник опорного тока, коллектор первого 17 дополнительного транзистора подключен ко входу первого 25 дополнительного токового зеркала, которое согласовано с первой 11 шиной источника питания, коллектор второго 18 дополнительного транзистора подключен ко входу первого 12 токового зеркала, выход первого 25 дополнительного токового зеркала связан с первым 3 выходом устройства, база третьего 19 дополнительного транзистора подключена к объединенным эмиттерам второго 6 и четвертого 9 входных транзисторов, база четвертого 20 дополнительного транзистора согласована со вторым 22 дополнительным источником напряжения смещения, объединенные эмиттеры третьего 19 и четвертого 20 дополнительных транзисторов подключены ко второй 14 шине источника питания через второй 24 дополнительный источник опорного тока, коллектор третьего 19 дополнительного транзистора подключен ко входу второго 2 6 дополнительного токового зеркала, которое согласовано с первой 11 шиной источника питания, коллектор четвертого 20 дополнительного транзистора подключен ко входу второго 13 токового зеркала, выход второго (13) токового зеркала подключен к первому (1) входу устройства, выход второго 26 дополнительного токового зеркала согласован со вторым 4 выходом устройства.

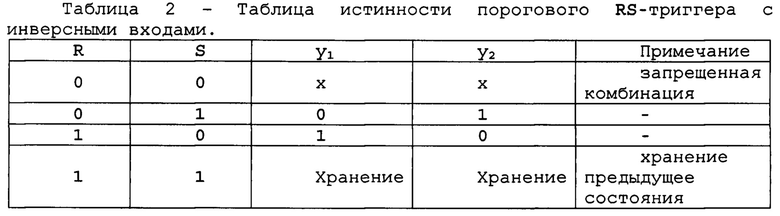

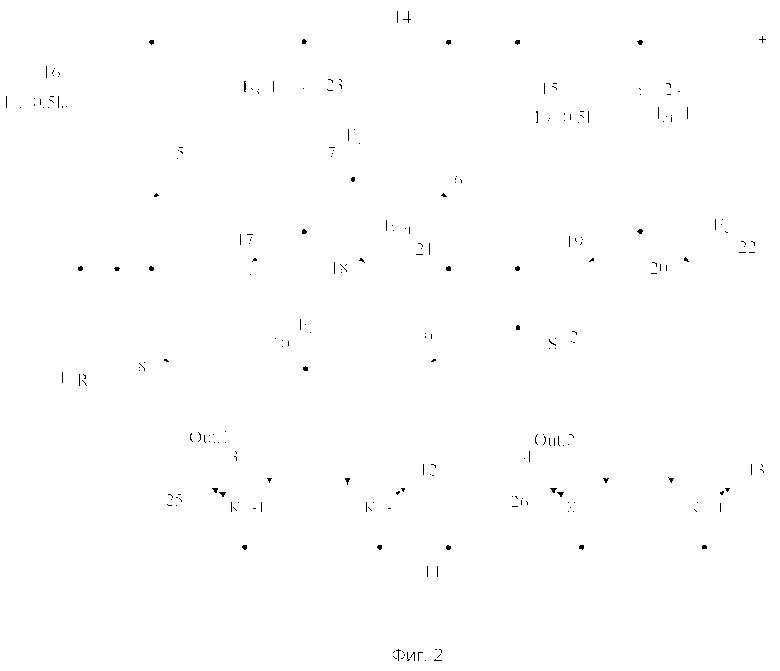

На чертеже фиг. 1 показана схема прототипа, а на чертеже фиг. 2 схема заявляемого двоичного токового порогового RS-триггера с прямыми входами при реализации на биполярных транзисторах в соответствии с п. 1 формулы изобретения.

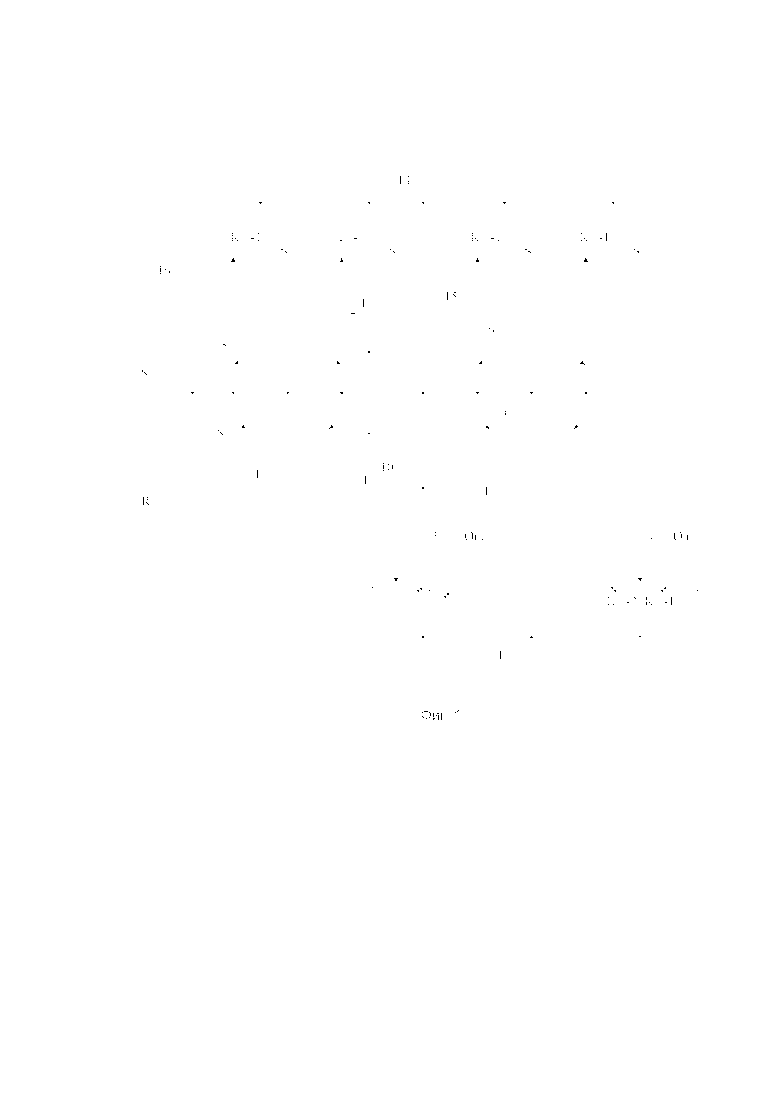

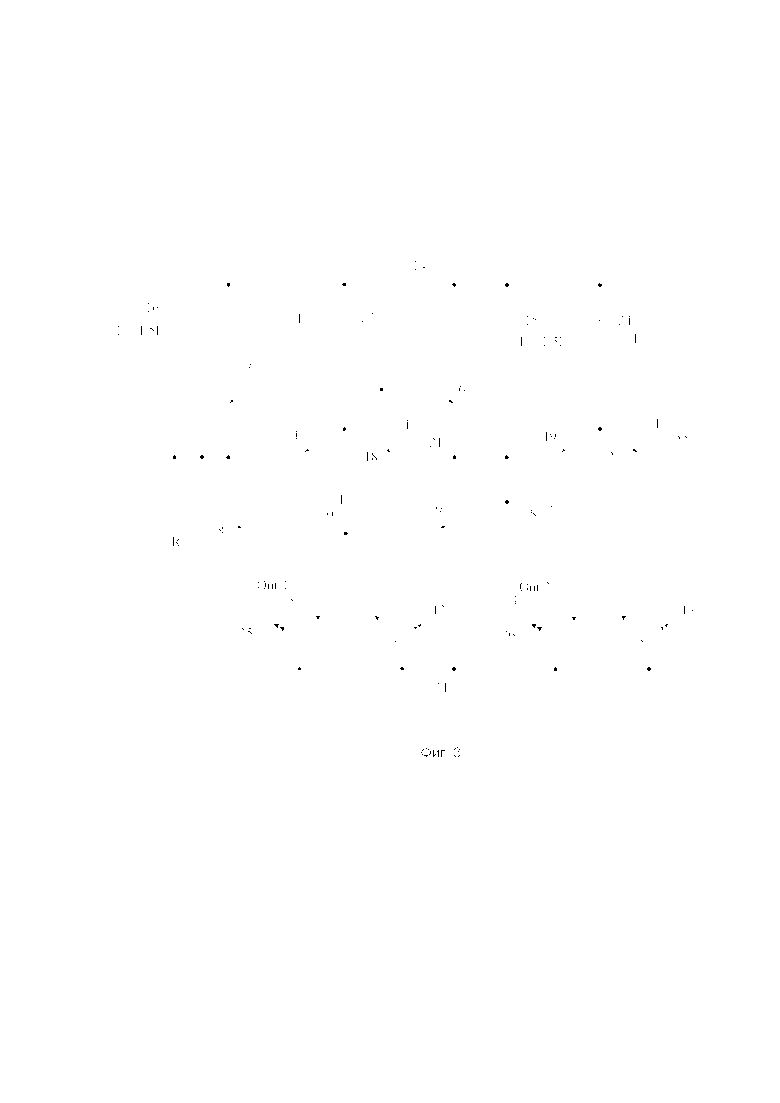

На чертеже фиг. 3 изображена схема заявляемого устройства с инверсными входами при реализации на биполярных транзисторах в соответствии с п. 2 формулы изобретения.

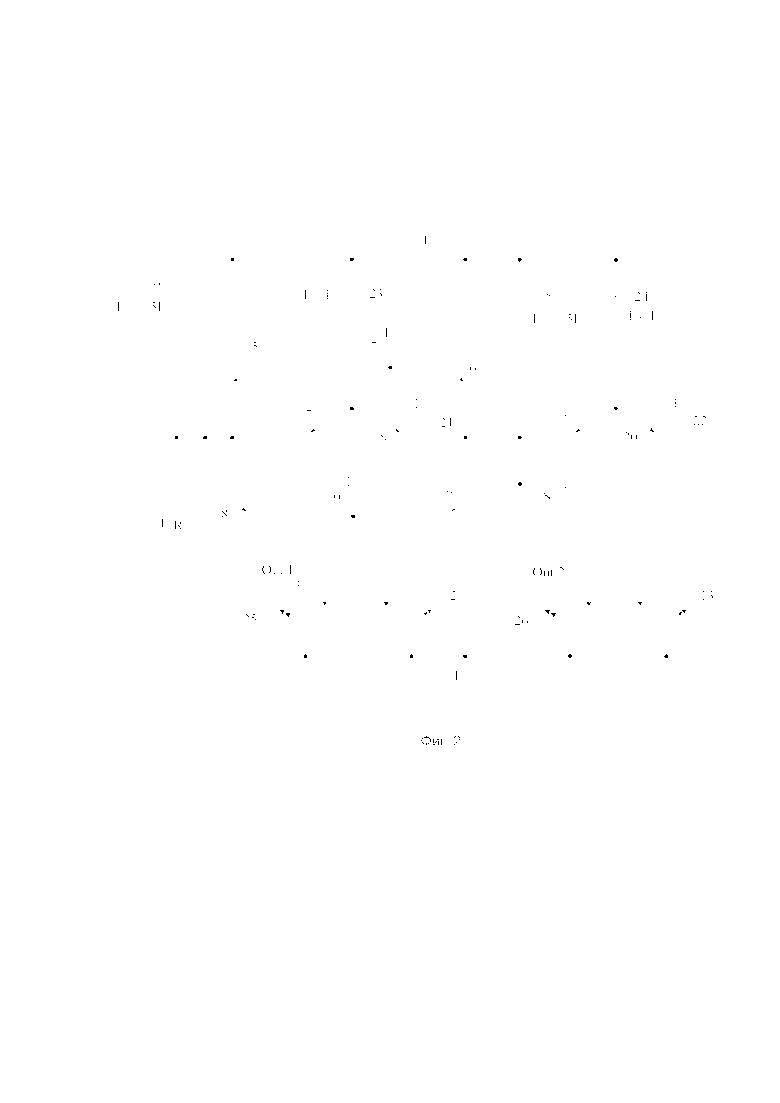

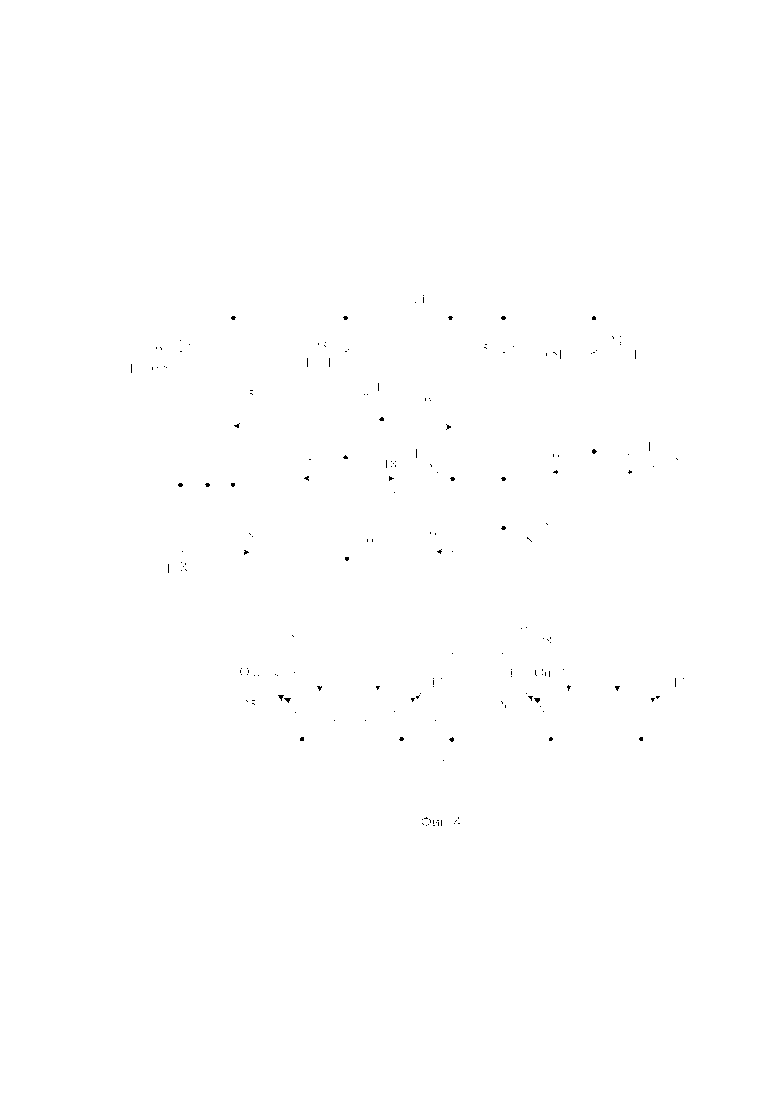

На чертеже фиг. 4 представлена схема двоичного токового порогового RS-триггера с прямыми входами при реализации на полевых транзисторах в соответствии с п. 3 формулы изобретения.

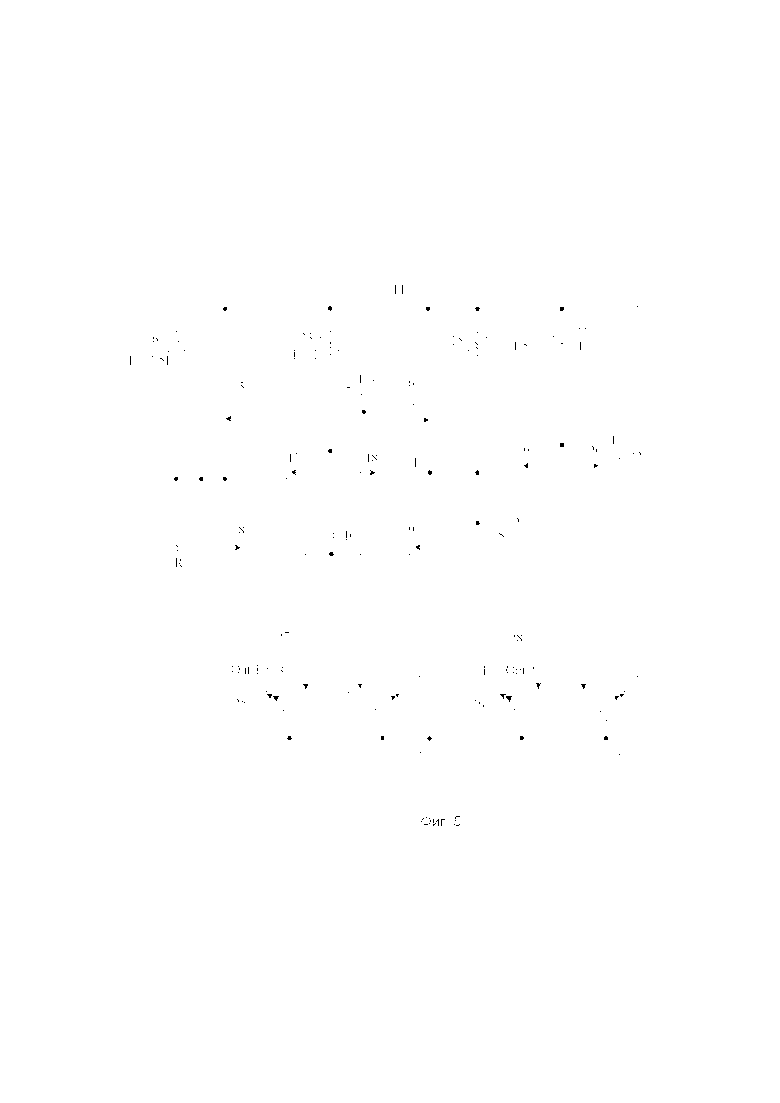

На чертеже фиг. 5 изображена схема заявляемого устройства с инверсными входами при реализации на полевых транзисторах в соответствии с п. 4 формулы изобретения.

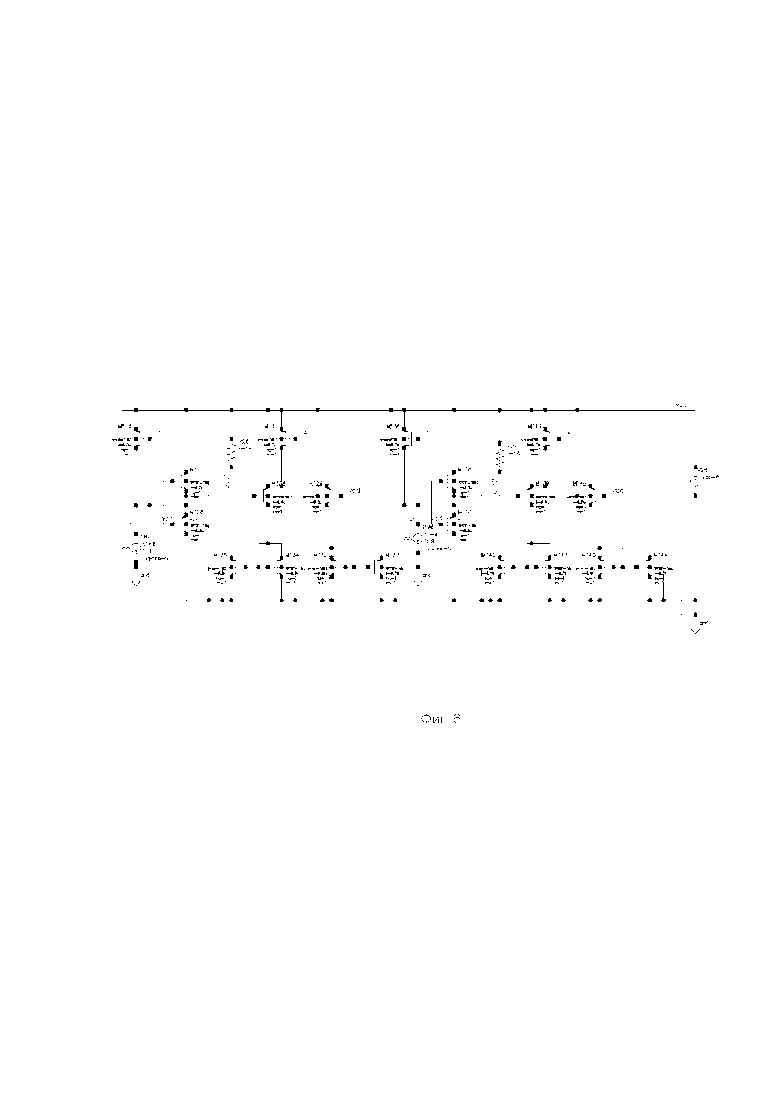

На чертеже фиг. 6 приведена схема двоичного токового порогового RS-триггера с прямыми входами фиг. 4 в среде компьютерного моделирования Cadence на моделях полевых транзисторов ХВ06.

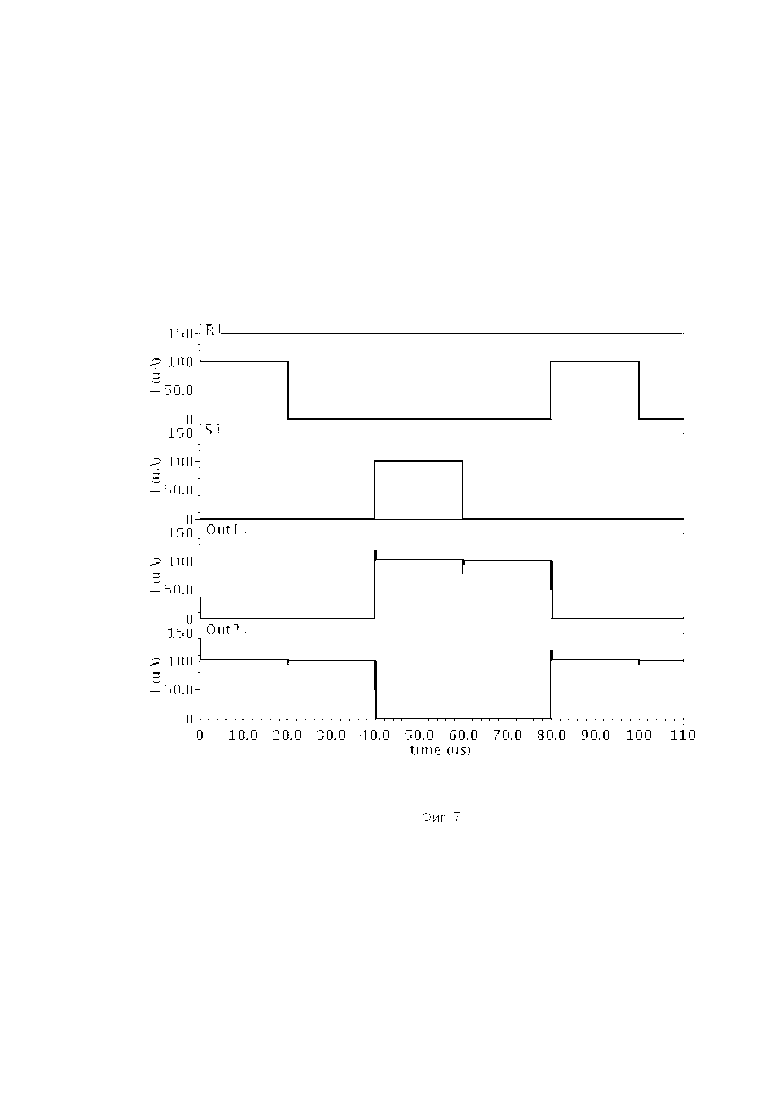

На чертеже фиг. 7 показаны осциллограммы входных и выходных сигналов двоичного токового порогового RS-триггера с прямыми входами фиг. 6.

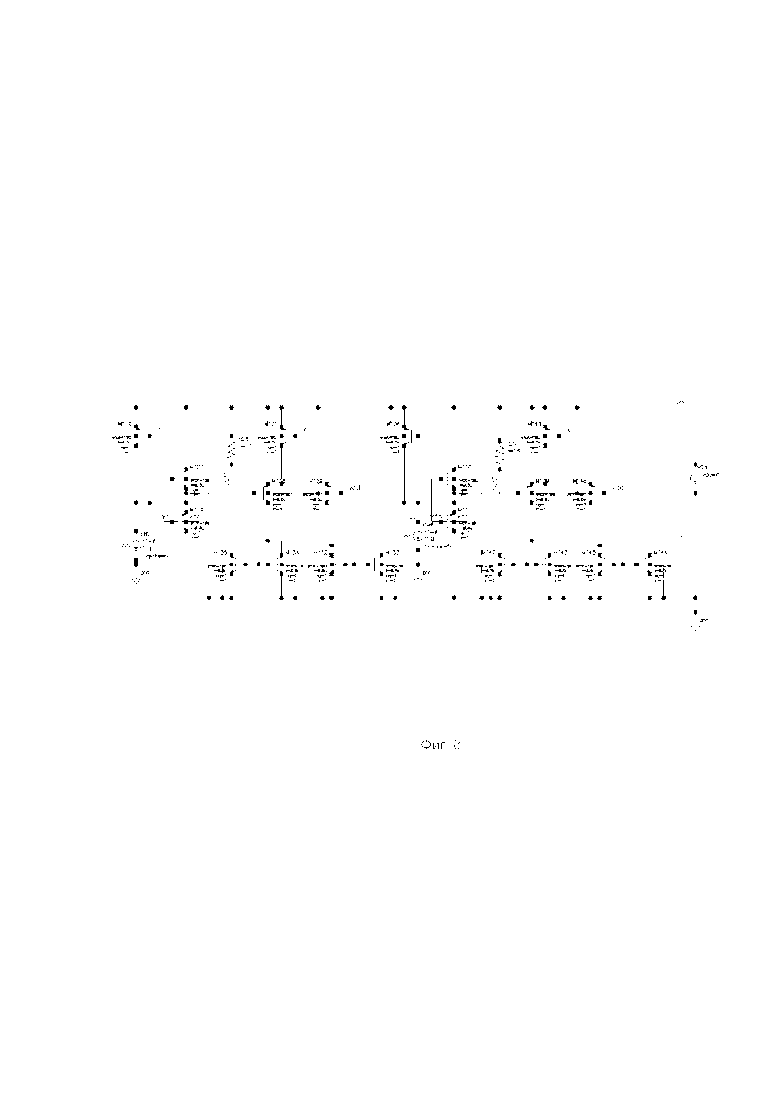

На чертеже фиг. 8 представлена схема двоичного токового порогового RS-триггера с инверсными входами фиг. 5 в среде компьютерного моделирования Cadence на моделях полевых транзисторов ХВ06.

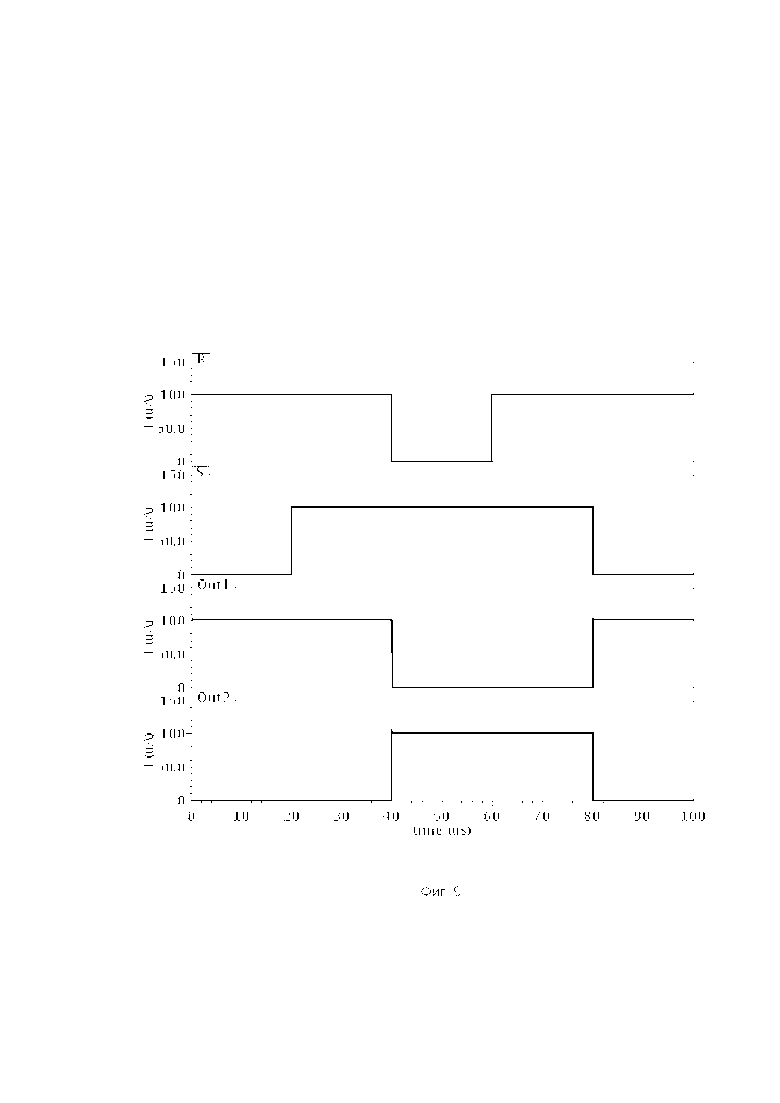

На чертеже фиг. 9 приведены осциллограммы входных и выходных сигналов двоичного токового порогового RS-триггера с инверсными входами фиг. 8.

Двоичный токовый пороговый RS-триггер (фиг. 2) содержит первый 1 (R) и второй 2 (S) логические входы устройства, первый 3 и второй 4 выходы устройства, первый 5 и второй 6 входные транзисторы, базы которых подключены к первому 7 источнику напряжения смещения, третий 8 и четвертый 9 входные транзисторы другого типа проводимости с объединенными базами, которые подключены ко второму 10 источнику напряжения смещения, коллекторы третьего 8 и четвертого 9 входных транзисторов подключены к первой 11 шине источника питания, эмиттеры первого 5 и третьего 8 входных транзисторов объединены, первое 12 и второе 13 токовые зеркала, согласованные с первой 11 шиной источника питания, выход первого 12 токового зеркала связан со второй 14 шиной источника питания через первый 15 источник опорного тока, второй 16 источник опорного тока включен между второй 14 шиной источника питания и объединенными эмиттерами первого 5 и третьего 8 входных транзисторов, эмиттеры второго 6 и четвертого 9 входных транзисторов объединены и подключены к выходу первого 12 токового зеркала. В схему введены первый 17, второй 18, третий 19 и четвертый 20 дополнительные транзисторы, первый 21 и второй 22 дополнительные источники напряжения смещения, первый 23 и второй 24 дополнительные источники опорного тока, первое 25 и второе 26 дополнительные токовые зеркала, причем коллекторы первого 5 и второго 6 входных транзисторов подключены ко второй 14 шине источника питания, первый 1 (R) логический вход устройства подключен к объединенным эмиттерам первого 5 и третьего 8 входных транзисторов, второй 2 (S) логический вход устройства подключен к выходу первого 12 токового зеркала, база первого 17 дополнительного транзистора подключена к объединенным эмиттерам первого 5 и третьего 8 входных транзисторов, база второго 18 дополнительного транзистора соединена с первым 21 дополнительным источником напряжения смещения, объединенные эмиттеры первого 17 и второго 18 дополнительных транзисторов подключены ко второй 14 шине источника питания через первый 23 дополнительный источник опорного тока, коллектор первого 17 дополнительного транзистора подключен ко входу первого 25 дополнительного токового зеркала, которое согласовано с первой 11 шиной источника питания, коллектор второго 18 дополнительного транзистора подключен ко входу первого 12 токового зеркала, выход первого 25 дополнительного токового зеркала связан с первым 3 выходом устройства, база третьего 19 дополнительного транзистора подключена к объединенным эмиттерам второго 6 и четвертого 9 входных транзисторов, база четвертого 20 дополнительного транзистора согласована со вторым 22 дополнительным источником напряжения смещения, объединенные эмиттеры третьего 19 и четвертого 20 дополнительных транзисторов подключены ко второй 14 шине источника питания через второй 24 дополнительный источник опорного тока, коллектор третьего 19 дополнительного транзистора подключен ко входу второго 26 дополнительного токового зеркала, которое согласовано с первой 11 шиной источника питания, коллектор четвертого 20 дополнительного транзистора подключен ко входу второго 13 токового зеркала, выход второго 26 дополнительного токового зеркала согласован со вторым 4 выходом устройства.

На чертеже фиг.3, в соответствии с п. 2 формулы изобретения, значения токов первого 15 и второго 16 источников тока близки к значениям 1,5I0, где I0 - квант тока.

На чертеже фиг. 4, в соответствии с п. 3 формулы изобретения, в качестве первого 5, второго 6, третьего 8 и четвертого 9 входных транзисторов, а также первого 17, второго 18, третьего 19 и четвертого 20 дополнительных транзисторов используются полевые транзисторы, причем исток каждого из полевых транзисторов соответствует эмиттеру, затвор - базе, а сток - коллектору биполярного транзистора [39].

На чертеже фиг. 5, в соответствии с п. 4 формулы изобретения, в качестве первого 5, второго 6, третьего 8 и четвертого 9 входных транзисторов, а также первого 17, второго 18, третьего 19 и четвертого 20 дополнительных транзисторов используются полевые транзисторы, причем исток каждого из полевых транзисторов соответствует эмиттеру, затвор - базе, а сток - коллектору биполярного транзистора [39].

Рассмотрим работу двоичного токового порогового RS-триггера, представленного на чертеже фиг. 2. Принцип его работы аналогичен принципу работы RS-триггера-прототипа (фиг. 1).

Для схемотехнической реализации логических элементов используются токовые зеркала и дифференциальные каскады (ДК), реализующие пороговые функции. Для двоичных переменных логический ноль представляется отсутствием некоторого заданного кванта тока I0, а единица - наличием кванта тока I0. При этом знак кванта определяется его направлением (втекающим, вытекающим). При токовом сигнальном представлении логических переменных направление тока не влияет на значение переменной, а зависит только от знака слагаемых в операциях алгебраического суммирования, реализующих выражения линейной алгебры [37-38]. Объединение таких логических элементов в более сложные структуры требует согласования не только уровней квантов тока I0, но и направлений входных и выходных токовых логических сигналов.

Традиционные сигналы установки заявляемого триггера в единичное (R) или нулевое (S) состояния поступают в виде квантов вытекающего тока на первый 1 (R) и второй 2 (S) логические входы устройства соответственно (фиг. 2). Режим хранения - R=S=0, для установки в одно из состояний подается сигнал «1» на соответствующий вход, R=S=1 - запрещенная комбинация (Таблица 1).

Входная переменная «R» в виде кванта втекающего тока поступает на первый 1 (R) логический вход устройства и далее на объединенные эмиттеры первого 5 и третьего 8 входных транзисторов, а также на базу первого 17 дополнительного транзистора, где из него вычитается 0,5 кванта вытекающего тока второго 16 источника опорного тока. Режимы работы первого 5, второго 6, третьего 8 и четвертого 9 входных транзисторов задаются значениями напряжений первого 7 и второго 10 источников напряжения смещения и обеспечивают предотвращение насыщения транзисторов первого 23 дополнительного источника опорного тока. Первый 17 и второй 18 дополнительные транзисторы образуют дифференциальный каскад (ДК), переключение коллекторных токов этих транзисторов определяется сигналом, поступающим на базу первого 17 дополнительного транзистора. ДК в данном случае выполняет функции порогового элемента, выполняя сравнение переменной «R» с пороговым уровнем 0,5. Выбор такого порогового уровня обеспечивает независимость результатов преобразования сигналов от погрешностей преобразования в пределах 0,5 кванта тока I0. Разностный сигнал, поступая на эмиттеры первого 5 и третьего 8 входных транзисторов формирует соответствующее знаку этой разности входное напряжение ДК на базе первого 17 дополнительного транзистора. Сигнал с коллектора первого 17 дополнительного транзистора в виде сигнала вытекающего тока подается на первое 25 дополнительное токового зеркала, где преобразуется в равный ему сигнал втекающего тока и подается на первый 3 выход устройства. Сигнал с коллектора второго 18 дополнительного транзистора в виде сигнала вытекающего тока подается на первое 12 токовое зеркало, где преобразуется в равный ему сигнал втекающего тока и подается на объединенные эмиттеры второго 6 и четвертого 9 входных транзисторов, а также на базу третьего 19 дополнительного транзистора, где из него вычитается 0,5 кванта вытекающего тока первого 15 источника опорного тока. Входная переменная «S» в виде кванта втекающего тока поступает на второй 2 (S) логический вход устройства и далее на объединенные эмиттеры второго 6 и четвертого 9 входных транзисторов. Третий 19 и четвертый 20 дополнительные транзисторы образуют дифференциальный каскад (ДК), переключение коллекторных токов этих транзисторов определяется сигналом, поступающим на базу третьего 19 дополнительного транзистора. ДК в данном случае выполняет функции порогового элемента, выполняя сравнение переменной «S» с пороговым уровнем 0,5. Выбор такого порогового уровня обеспечивает независимость результатов преобразования сигналов от погрешностей преобразования в пределах 0,5 кванта тока I0. Разностный сигнал, поступая на эмиттеры второго 6 и четвертого 9 входных транзисторов формирует соответствующее знаку этой разности входное напряжение ДК на базе третьего 19 дополнительного транзистора. Сигнал с коллектора третьего 19 дополнительного транзистора в виде сигнала вытекающего тока подается на второе 26 дополнительное токовое зеркало, где преобразуется в равный ему сигнал втекающего тока и подается на второй 4 выход устройства. Сигнал с коллектора четвертого 20 дополнительного транзистора в виде сигнала вытекающего тока подается на второе 13 токовое зеркало, где преобразуется в равный ему сигнал втекающего тока и подается на первый 1 вход устройства, образуя 100% положительную обратную связь. Переключение ДК, выполняющих функции пороговых элементов, и, следовательно, переключение триггера в новое состояние происходит в моменты, когда соответствующий входной сигнал «R» для ДК на первом 17 и втором 18 дополнительных транзисторах или «S» для ДК на третьем 19 и четвертом 20 дополнительных транзисторах принимает значение 1 (I0).

Устройство (фиг. 3) работает аналогично. Для перехода ко второй классической структуре с инверсными входами достаточно опорные токи первого 15 и второго 16 источников тока 0,5I0 заменить на токи 1,5I0. Такое изменение опорных токов приводит к следующему изменению алгоритма работы триггера: устойчивому состоянию триггера в режиме хранения соответствуют сигналы R=S=1 (I0), а переключение ДК и, следовательно триггера, происходит при переключении одного из входных сигналов в состояние 0 (Таблица 2).

Реализация логической функции порогового RS-триггера здесь производится формированием алгебраической суммы квантов тока и выделением определенных значений этой суммы токов. Все элементы приведенных схем фиг. 2 - фиг. 5 работают в активном режиме, предполагающем отсутствие насыщения в процессе переключений, что повышает общее быстродействие RS-триггера. Кроме того, использование многозначного внутреннего представления сигналов повышает информативность линий связи в сложных системах на кристалле, что уменьшает их количество. Использование стабильных значений квантов тока, а также определение выходного сигнала разностью этих токов обеспечивает малую зависимость функционирования схемы от внешних дестабилизирующих факторов (девиация питающего напряжения, радиационное и температурное воздействия, синфазная помеха и др.).

В схемах на фиг. 4 и фиг. 5 двухполюсники 27 и 28 служат для обнаружения наличия кванта тока в выходной цепи в процессе экспериментальных исследований.

Показанные на фиг. 7 и фиг. 9 результаты моделирования подтверждают указанные свойства заявляемой схемы RS-триггера.

Таким образом, рассмотренное схемотехническое решение RS-триггера на пороговых логических элементах характеризуется многозначным состоянием внутренних сигналов и сигналов на его токовых входах и выходах, что может быть положено в основу вычислительных и управляющих устройств, использующих токовое представление информационных сигналов.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент RU 2604682, фиг. 8, 2016 г.

2. Патент US 2011/0121877, fig. 9, 2011 г.

3. Патент ЕР 06011821, fig. 2, 2007 г.

4. Патент US 5.994.936, fig. 3, 1999 г.

5. Патент US 5.327.020, fig. 1, 1994 г.

6. Патент US 6.362.674, fig. 4А, 2002 г.

7. Патент US 6.535.024, 2003 г.

8. Патент US 7.098.652, fig. 1, fig. 10, 2006 г.

9. Патент US 4.441.075, fig. l, 1984 г.

10. Авторское свидетельство СССР 1390790, 1988 г.

11. Авторское свидетельство СССР 1193798, 1985 г.

12. Авторское свидетельство СССР 1370732, 1988 г.

13. Патент US 5.065.052, fig. 3, fig. 10, 1991 г.

14. Патент US 7.697.319, fig. 2, 2010 г.

15. Патент US 8.232.825, fig. 9, 2012 г.

16. Патент US 8.115.522, fig. 2, 2012 г.

17. Патент US 7.626.433, 2009 г.

18. Патент US 7.236.029, fig. 3, 2007 г.

19. Патент US 6.268.752, fig. 4, 2001 г.

20. Патент US 6.486.720, 2002 г.

21. Патентная заявка US 2002/0003443 fig. 4, 2002 г.

22. Патент US 6.714.060, 2004 г.

23. Патент US 5.025.174, 1991 г.

24. Патент US 5.945.858, 1999 г.

25. Патент US 5.892.382, fig. 2, 1999 г.

26. Патент US 5.844.437, fig. 2, 1998 г.

27. Патент US 5.220.212, 1993 г.

28. Патент US 5.815.019, fig. l, 1998 г.

29. Патент US 5.541.544, fig. l, 1996 г.

30. Патент US 5.001.361, fig. 3, 1991 г.

31. Патент US 5.969.556, fig. l, 1999 г.

32. Патент US 4.156.819, fig. 2, 1979 г.

33. Патент US 4.779.009, fig. 4, 1988 г.

34. Патент US 4.309.625, fig. 4, 1982 г.

35. Патент US 3.305.728, 1967 г.

36. Малюгин В.Д. Реализация булевых функций арифметическими полиномами // Автоматика и телемеханика, 1982. №4. С. 84-93.

37. Чернов Н.И. Основы теории логического синтеза цифровых структур над полем вещественных чисел // Монография. - Таганрог: ТРТУ, 2001. - 147 с.

38. Чернов Н.И. Линейный синтез цифровых структур АСОИУ» // Учебное пособие Таганрог.- ТРТУ, 2004 г., 118 с.

39. Хоровиц П., Хилл У. Искусство схемотехники: Пер. с англ. - Изд. 2-е. - М.: Издательство БИНОМ 2014. - с. 126.

| название | год | авторы | номер документа |

|---|---|---|---|

| RS-ТРИГГЕР | 2015 |

|

RU2604682C1 |

| RS-ТРИГГЕР | 2015 |

|

RU2615069C1 |

| ТОКОВЫЙ ПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ПРЯМОГО ЦИКЛИЧЕСКОГО СДВИГА | 2018 |

|

RU2693639C1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ СРАВНЕНИЯ k-ЗНАЧНОЙ ПЕРЕМЕННОЙ С ПОРОГОВЫМ ЗНАЧЕНИЕМ | 2014 |

|

RU2546085C1 |

| ТОКОВЫЙ ПОРОГОВЫЙ ЭЛЕМЕНТ "СУММАТОР ПО МОДУЛЮ ТРИ" | 2020 |

|

RU2725165C1 |

| ТОКОВЫЙ ПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ "НЕРАВНОЗНАЧНОСТЬ" | 2018 |

|

RU2701108C1 |

| ТОКОВЫЙ ПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ "НЕРАВНОЗНАЧНОСТЬ" | 2018 |

|

RU2692573C1 |

| ТОКОВЫЙ ПОРОГОВЫЙ ЭЛЕМЕНТ «ВЫЧИТАТЕЛЬ ПО МОДУЛЮ ТРИ» | 2022 |

|

RU2786945C1 |

| МНОГОЗНАЧНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ОБРАТНОГО ЦИКЛИЧЕСКОГО СДВИГА | 2014 |

|

RU2553071C1 |

| RS-ТРИГГЕР С МНОГОЗНАЧНЫМ ВНУТРЕННИМ ПРЕДСТАВЛЕНИЕМ СИГНАЛОВ | 2012 |

|

RU2514789C1 |

Изобретение относится к области радиотехники и аналоговой микроэлектроники и может быть использовано в быстродействующих аналоговых и аналого-цифровых интерфейсах для обработки сигналов датчиков. Технический результат: повышение быстродействия систем обработки информации и создание элементной базы вычислительных устройств. Такой результат достигается за счет создания двоичного токового порогового RS-триггера с прямыми и инверсными входами, в схему которого введены первый (17), второй (18), третий (19) и четвертый (20) дополнительные транзисторы, первый (21) и второй (22) дополнительные источники напряжения смещения, первое (25) и второе (26) дополнительные токовые зеркала, коллектор первого (17) дополнительного транзистора подключен ко входу первого (25) дополнительного токового зеркала, коллектор второго (18) дополнительного транзистора подключен ко входу первого (12) токового зеркала, коллектор третьего (19) дополнительного транзистора подключен ко входу второго (2 6) дополнительного токового зеркала, коллектор четвертого (20) дополнительного транзистора подключен ко входу второго (13) токового зеркала. 9 ил., 2 табл.

Двоичный токовый пороговый RS-триггер, содержащий первый (1) (R) и второй (2) (S) логические входы устройства, первый (3) и второй (4) выходы устройства, первый (5) и второй (6) входные транзисторы, базы которых подключены к первому (7) источнику напряжения смещения, третий (8) и четвертый (9) входные транзисторы другого типа проводимости с объединенными базами, которые подключены ко второму (10) источнику напряжения смещения, коллекторы третьего (8) и четвертого (9) входных транзисторов подключены к первой (11) шине источника питания, эмиттеры первого (5) и третьего (8) входных транзисторов объединены, первое (12) и второе (13) токовые зеркала, согласованные с первой (11) шиной источника питания, выход первого (12) токового зеркала связан со второй (14) шиной источника питания через первый (15) источник опорного тока, второй (16) источник опорного тока включен между второй (14) шиной источника питания и объединенными эмиттерами первого (5) и третьего (8) входных транзисторов, эмиттеры второго (6) и четвертого (9) входных транзисторов объединены и подключены к выходу первого (12) токового зеркала отличающийся тем, что в схему введены первый (17), второй (18), третий (19) и четвертый (20) дополнительные транзисторы, первый (21) и второй (22) дополнительные источники напряжения смещения, первый (23) и второй (24) дополнительные источники опорного тока, первое (25) и второе (2 6) дополнительные токовые зеркала, причем коллекторы первого (5) и второго (б) входных транзисторов подключены ко второй (14) шине источника питания, первый (1) (R) логический вход устройства подключен к объединенным эмиттерам первого (5) и третьего (8) входных транзисторов, второй (2) (S) логический вход устройства подключен к выходу первого (12) токового зеркала, база первого (17) дополнительного транзистора подключена к объединенным эмиттерам первого (5) и третьего (8) входных транзисторов, база второго (18) дополнительного транзистора соединена с первым (21) дополнительным источником напряжения смещения, объединенные эмиттеры первого (17) и второго (18) дополнительных транзисторов подключены ко второй (14) шине источника питания через первый (23) дополнительный источник опорного тока, коллектор первого (17) дополнительного транзистора подключен ко входу первого (25) дополнительного токового зеркала, которое согласовано с первой (11) шиной источника питания, коллектор второго (18) дополнительного транзистора подключен ко входу первого (12) токового зеркала, выход первого (25) дополнительного токового зеркала связан с первым (3) выходом устройства, база третьего (19) дополнительного транзистора подключена к объединенным эмиттерам второго (6) и четвертого (9) входных транзисторов, база четвертого (20) дополнительного транзистора согласована со вторым (22) дополнительным источником напряжения смещения, объединенные эмиттеры третьего (19) и четвертого (20) дополнительных транзисторов подключены ко второй (14) шине источника питания через второй (24) дополнительный источник опорного тока, коллектор третьего (19) дополнительного транзистора подключен ко входу второго (26) дополнительного токового зеркала, которое согласовано с первой (11) шиной источника питания, коллектор четвертого (20) дополнительного транзистора подключен ко входу второго (13) токового зеркала, выход второго (13) токового зеркала подключен к первому (1) входу устройства, выход второго (26) дополнительного токового зеркала согласован со вторым (4) выходом устройства.

| RS-ТРИГГЕР | 2015 |

|

RU2604682C1 |

| RS-ТРИГГЕР | 2015 |

|

RU2615069C1 |

| RS-ТРИГГЕР С МНОГОЗНАЧНЫМ ВНУТРЕННИМ ПРЕДСТАВЛЕНИЕМ СИГНАЛОВ | 2012 |

|

RU2514789C1 |

| Способ приготовления лака | 1924 |

|

SU2011A1 |

Авторы

Даты

2019-07-29—Публикация

2018-12-21—Подача