Область техники, к которой относится изобретение

Настоящее изобретение, в общем, относится к декодированию и, в частности, к системе и способу декодирования, выполняемому для кодированных блоков элементов текстуры.

Уровень техники

При попытке увеличивать производительность для графических процессоров (GPU), одно решение состоит в том, чтобы применять различные технологии для того, чтобы уменьшать потребление пропускной способности запоминающего устройства. Уменьшение пропускной способности также становится все более важным, поскольку темп роста рабочих характеристик по вычислительной мощности существенно превышает темп роста рабочих характеристик по пропускной способности и времени задержки для оперативного запоминающего устройства (RAM).

Сжатие текстуры является одним популярным способом уменьшения требований по пропускной способности. Посредством сохранения текстур в сжатой форме в запоминающем устройстве и передачи блоков сжатых данных по шине пропускная способность текстуры существенно уменьшается.

Сегодня, наиболее распространенными системами сжатия текстуры являются DXTC[1] для систем на базе Windows и Xbox и ETC[2] для мобильных телефонов. Обе этих системы разделяют изображение, обозначенное как текстура, на блоки элементов текстуры (текселов) в 4×4 тексела, и данные красного, зеленого, синего цвета (RGB) текселов затем сжимаются с (8+8+8)×16=384 битов до 64 битов. Таким образом, каждому текселному блоку предоставляется идентичное число битов. Это важно, поскольку растризатор, используемый при распаковке, возможно, должен осуществлять доступ к любой части текстуры и должен иметь возможность легко вычислять адрес ячейки памяти требуемого текселного блока. Другими словами, кодек с фиксированной скоростью, т.е. кодек, в котором каждый текселный блок занимает идентичный объем пространства для хранения, является очень желательным и является нормой для алгоритмов сжатия текстуры сегодня.

Разработка ETC-декодера привела к так называемому ETC2-декодеру [3], имеющему дополнительную функциональность для обработки так называемого T-режима, H-режима и PLANAR-режима. T- и H-режим выполнены с возможностью обрабатывать текселные блоки с неравномерным распределением цвета и цветов, размещаемых в двух группах соответственно. Аппаратные схемы ETC-декодера могут быть многократно использованы в значительной степени, чтобы охватывать дополнительные T- и H-режимы. PLANAR-режим тем не менее существенно отличается от ETC и T- и H-режимов и выполнен с возможностью обрабатывать текселные блоки с плавными цветовыми переходами. Сложные аппаратные схемы для PLANAR-режима должны подразумевать, что сложность ETC2-декодера должна значительно увеличиваться по сравнению с ETC-декодером.

Таким образом, существует потребность в предоставлении эффективной реализации PLANAR-режима, и в частности, такой реализации, которая может предоставляться в качестве аппаратной реализации с использованием экономически эффективной схемы. Такая экономически эффективная схема является, в частности, желательной, если PLANAR-режим должен быть использован вместе с ETC-декодером и T- и H-режимами, чтобы формировать ETC2-декодер.

Аналогичная проблема, в общем, присутствует в данной области техники, т.е. существует общая потребность в технологии, которая может применяться к системе декодирования с целью уменьшения сложности реализации.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

Общая цель состоит в том, чтобы предоставлять эффективное декодирование кодированных текселных блоков.

Конкретная цель состоит в том, чтобы предоставлять структуру декодирования, которая может быть эффективно реализована в аппаратных средствах.

Эти и другие цели удовлетворяются посредством вариантов осуществления, как раскрыто в данном документе.

Кратко, вариант осуществления относится к системе декодирования для формирования декодированного пиксела на основе, по меньшей мере, одного кодированного текселного блока. Система декодирования содержит

Система декодирования также содержит модуль выбора значений, соединенный с

Тщательный выбор посредством модуля выбора значений обеспечивает такую конструкцию декодеров, что, по меньшей мере, некоторые из

Вариант осуществления задает способ формирования пиксела посредством декодирования, по меньшей мере, одного кодированного текселного блока. Способ содержит избирательный вывод

Варианты осуществления предоставляют эффективную реализацию структуры пикселного декодирования посредством уменьшения сложности, требуемой, по меньшей мере, для некоторых параллельных декодеров. Полная сложность структуры декодирования тем самым уменьшается по сравнению с наличием

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Изобретение вместе с дополнительными целями и преимуществами может лучше всего пониматься посредством обращения к последующему описанию, рассматриваемому вместе с прилагаемыми чертежами, на которых:

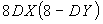

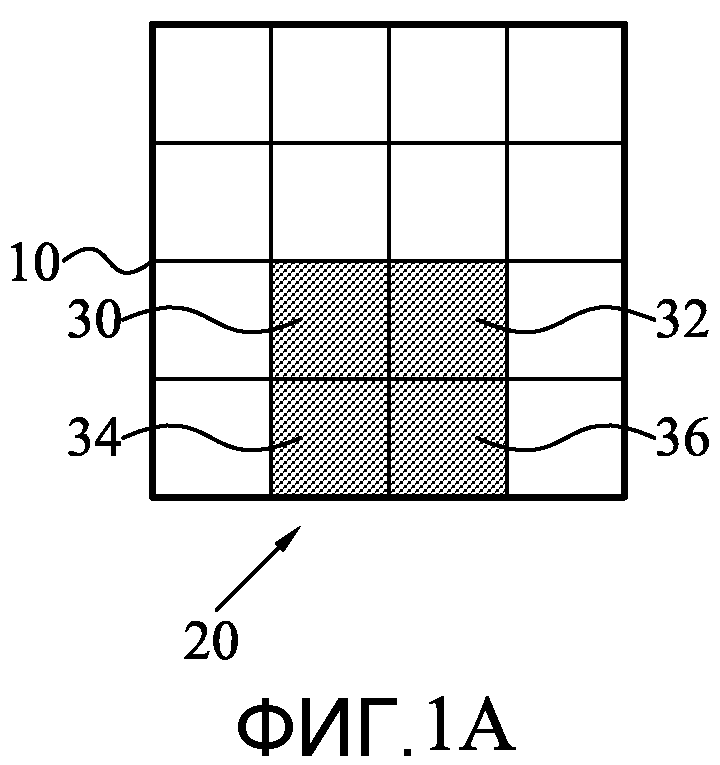

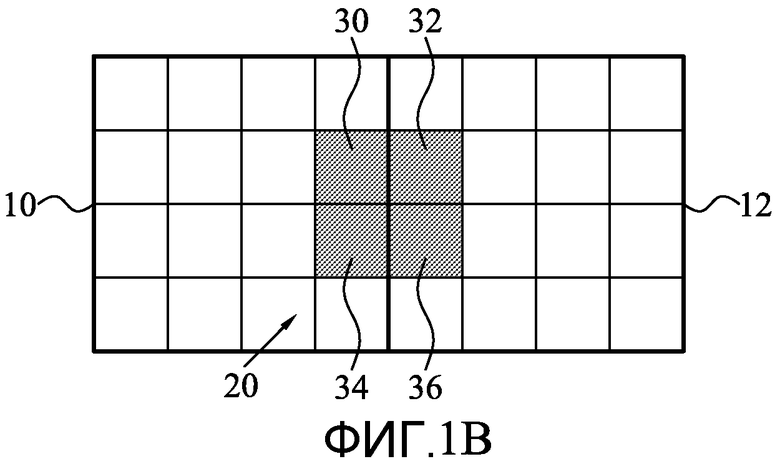

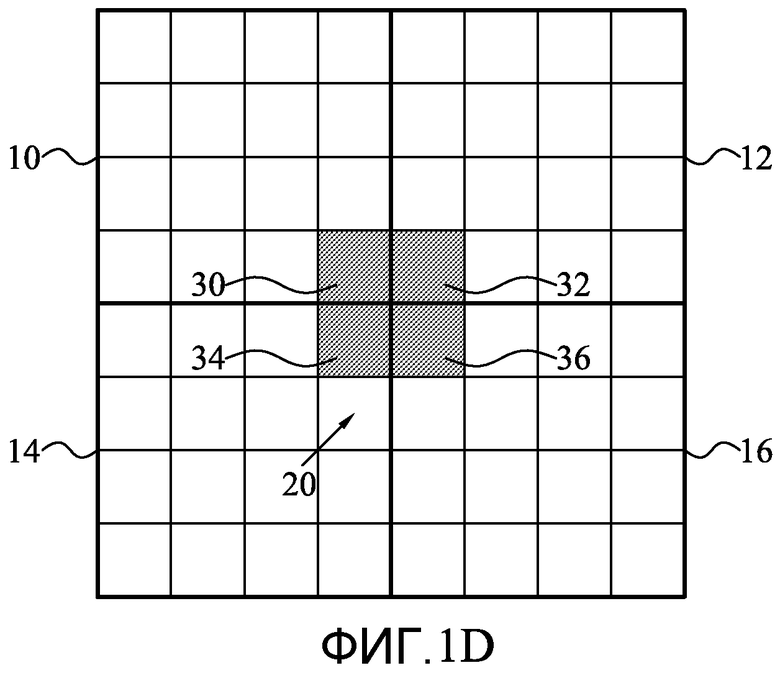

Фиг. 1A-1D иллюстрируют различные позиции билинейного исправления относительно границ текселных блоков;

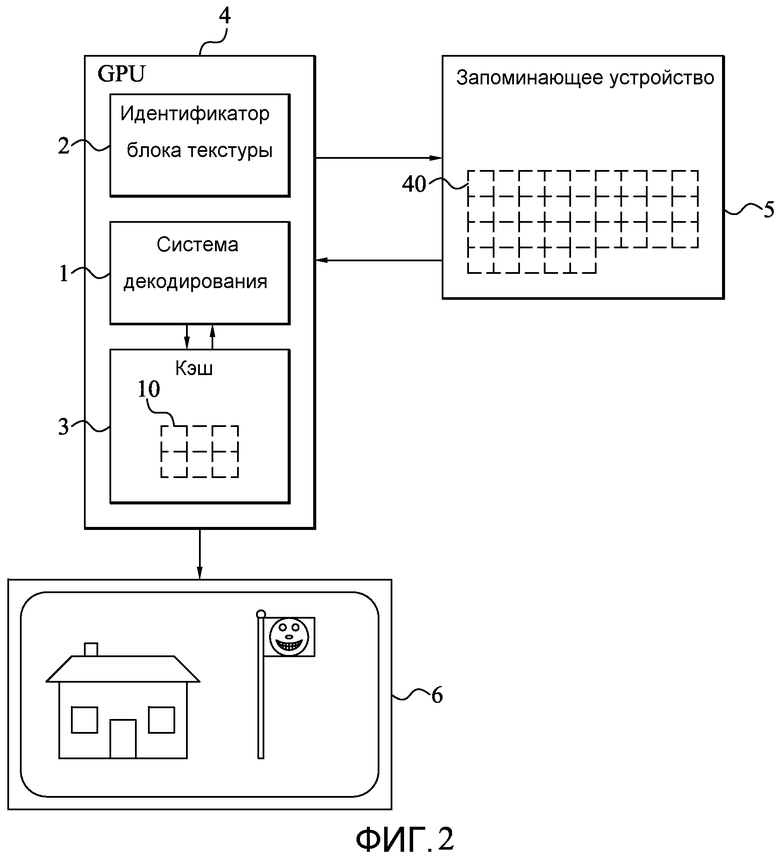

Фиг. 2 является схематичным видом компоновки декодирования, содержащей систему декодирования согласно варианту осуществления;

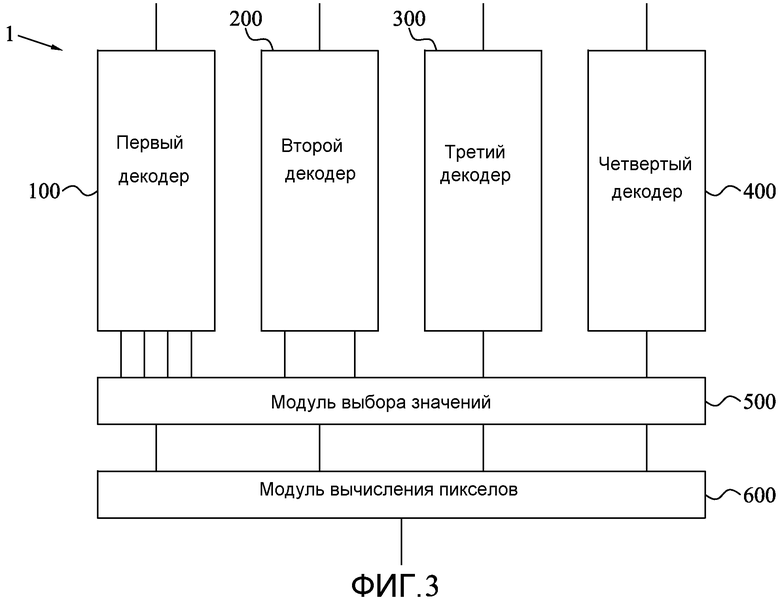

Фиг. 3 является иллюстрацией системы декодирования согласно варианту осуществления;

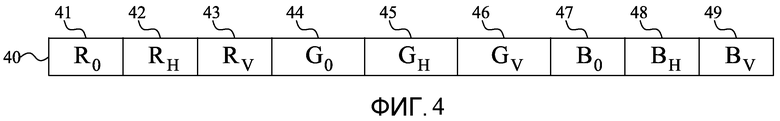

Фиг. 4 схематично иллюстрирует кодированный текселный блок согласно варианту осуществления;

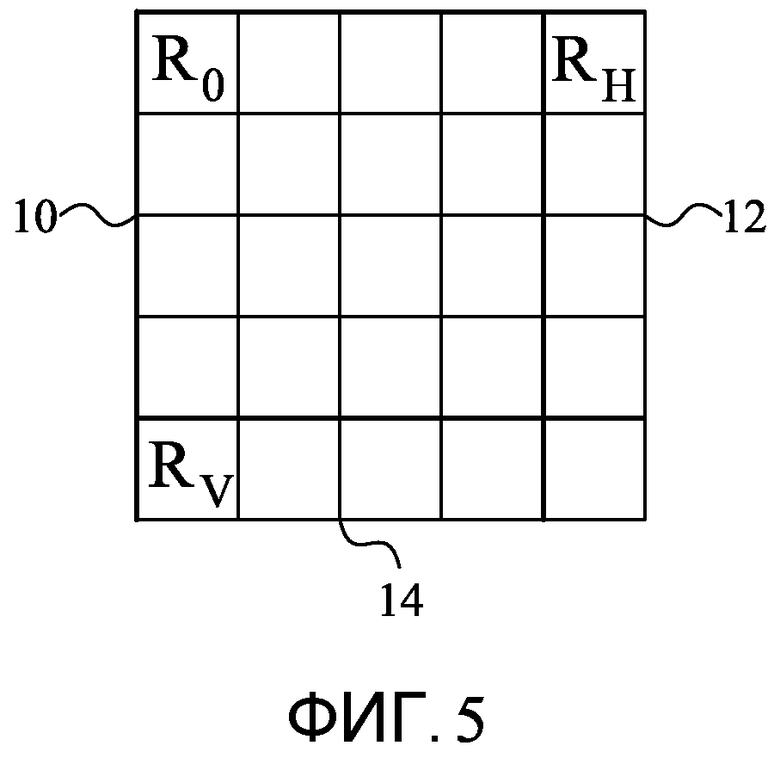

Фиг. 5 иллюстрирует принцип использования планарной аппроксимации значений свойств текселов в текселном блоке;

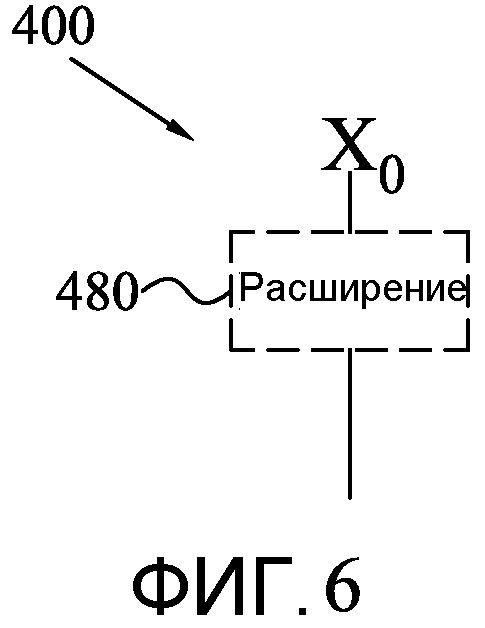

Фиг. 6 является примером аппаратной реализации четвертого декодера на фиг. 3;

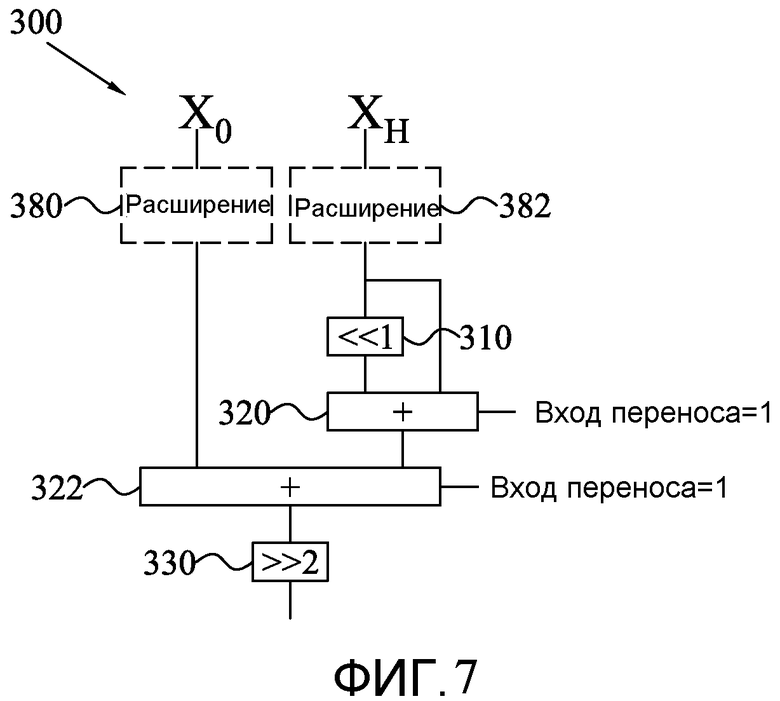

Фиг. 7 является примером аппаратной реализации третьего декодера на фиг. 3;

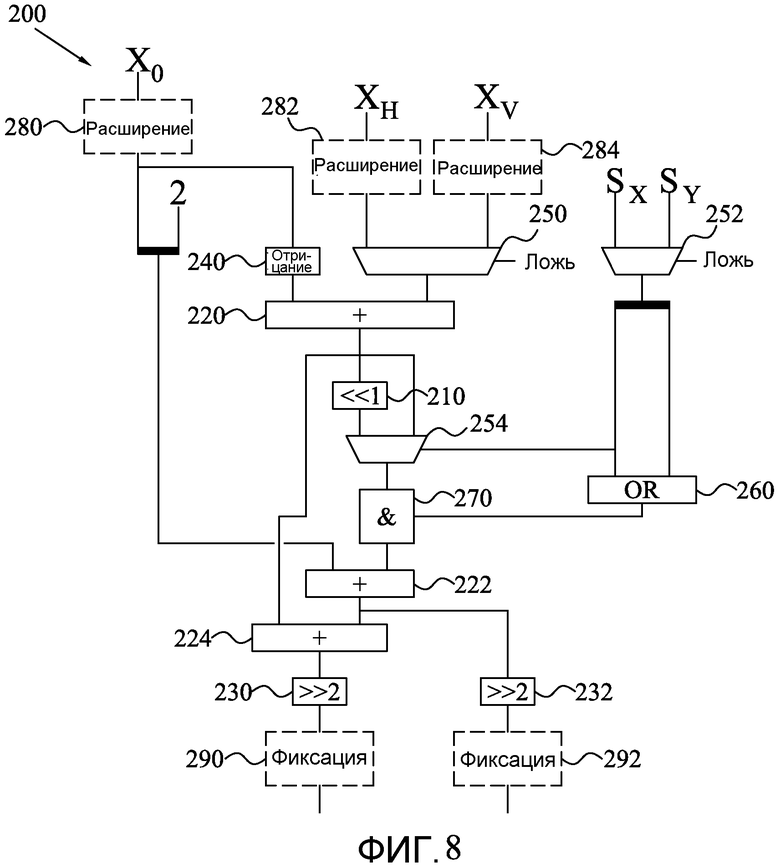

Фиг. 8 является примером аппаратной реализации второго декодера на фиг. 3;

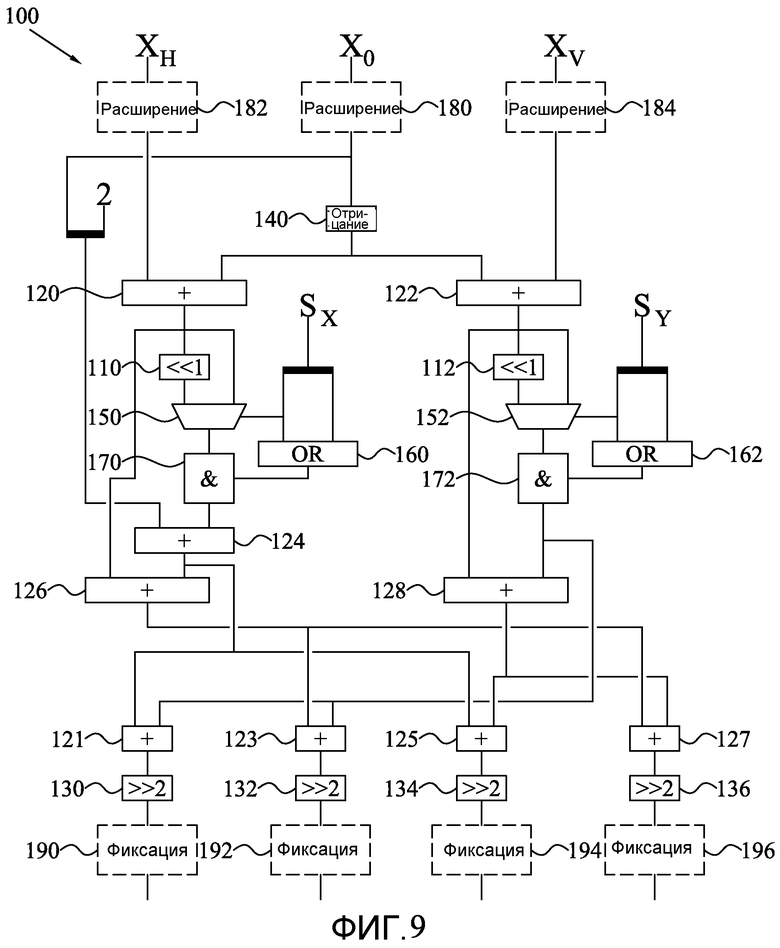

Фиг. 9 является примером аппаратной реализации первого декодера на фиг. 3;

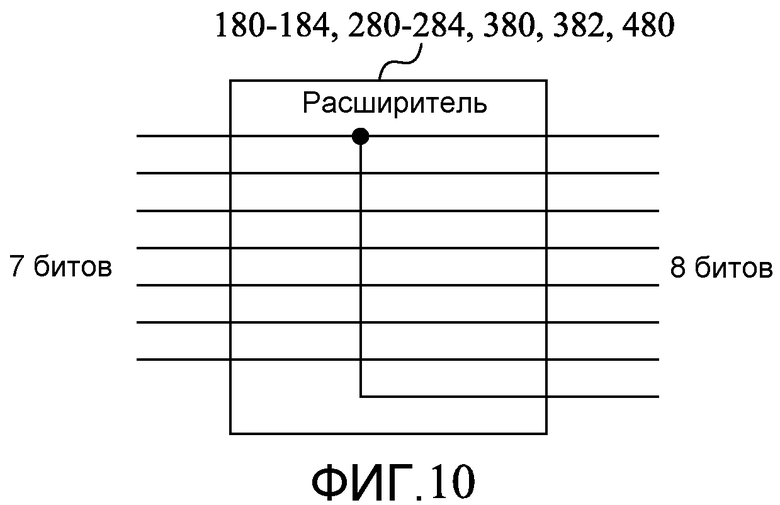

Фиг. 10 является примером аппаратной реализации битового расширителя "с семи до восьми битов";

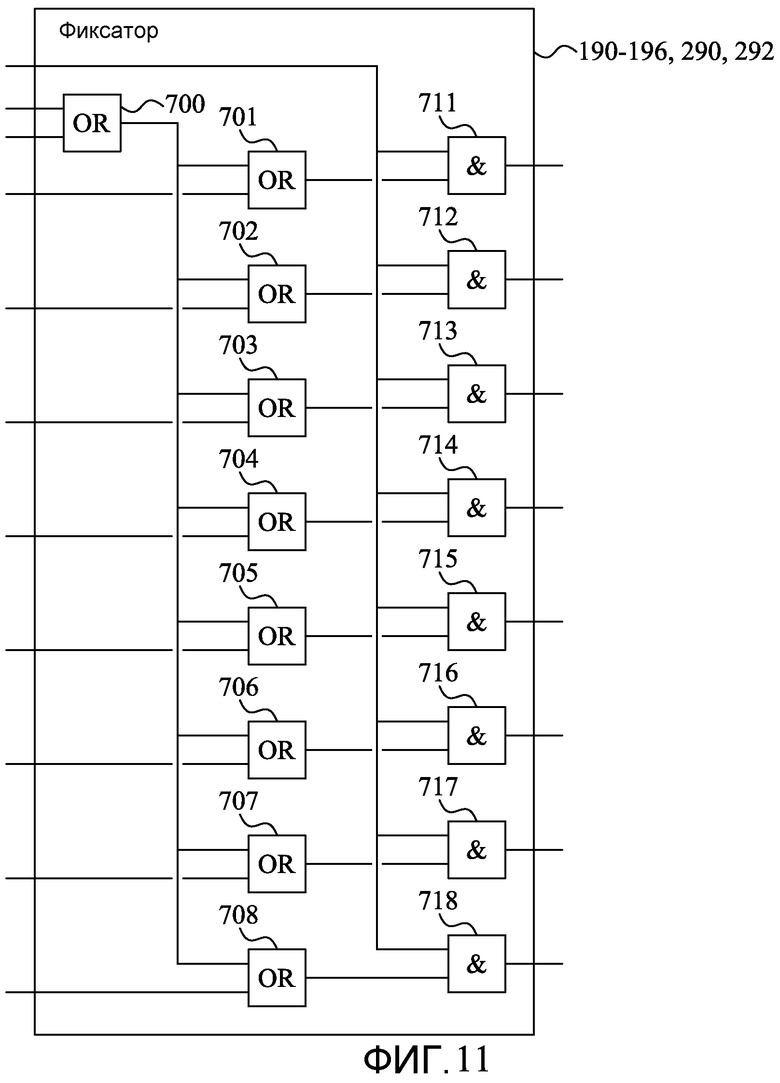

Фиг. 11 является аппаратной реализацией фиксатора;

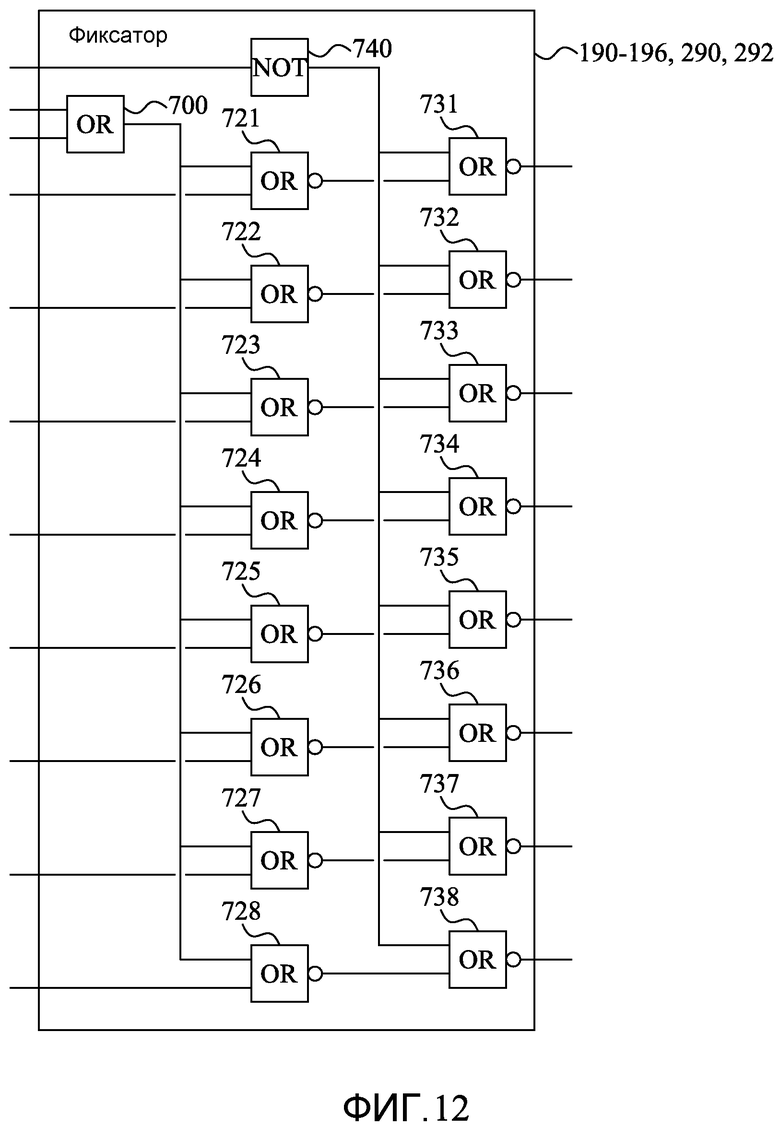

Фиг. 12 является другой аппаратной реализацией фиксатора;

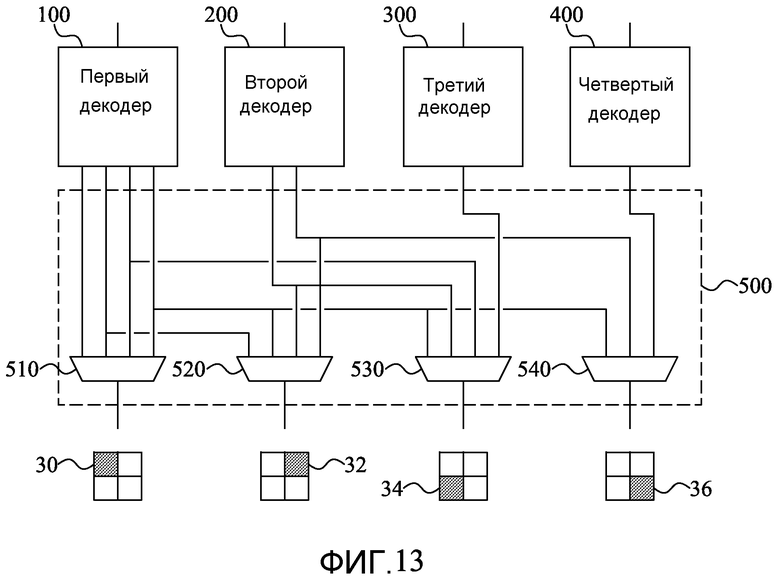

Фиг. 13 является примером аппаратной реализации модуля выбора значений по фиг. 3; и

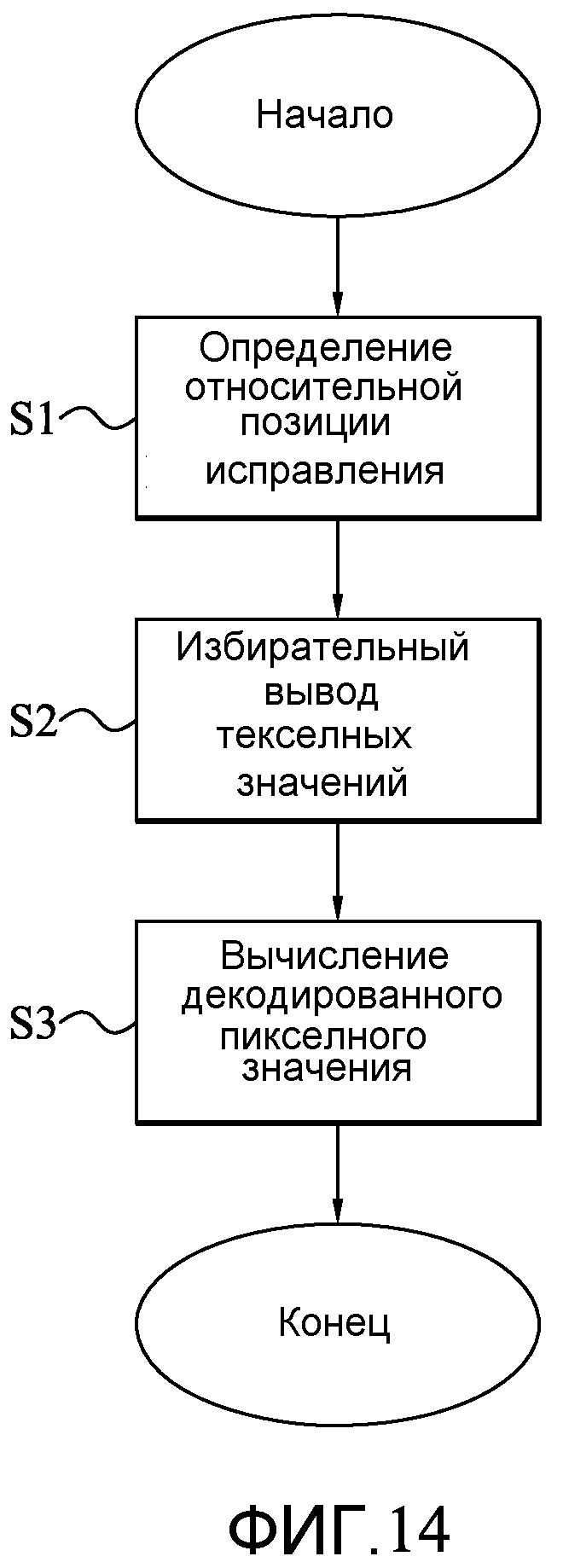

Фиг. 14 является блок-схемой последовательности операций, иллюстрирующей способ декодирования согласно варианту осуществления.

ПОДРОБНОЕ ОПИСАНИЕ ИЗОБРЕТЕНИЯ

На всех чертежах идентичные ссылки с номерами используются для аналогичных или соответствующих элементов.

Варианты осуществления, в общем, относятся к декодированию или распаковке кодированных или сжатых блоков элементов текстуры (текселов) для формирования декодированных пикселных значений.

Декодирование хорошо подходит для использования с трехмерной графикой, такой как игры, трехмерные карты и сцены, трехмерные сообщения, к примеру, анимированные сообщения, экранные заставки, человекомашинные интерфейсы (MMI) и т.д., но не ограничено этим. Таким образом, варианты осуществления также могут использоваться для декодирования других типов изображений или графики, например, одномерных, двумерных или трехмерных изображений.

Процесс рендеринга трехмерной графики типично содержит три подстадии. Вкратце, первая стадия, прикладная стадия, создает несколько треугольников. Углы этих треугольников трансформируются, проецируются и освещаются на второй стадии, геометрической стадии. На третьей стадии, стадии растеризации, изображения, часто называемые текстурами, могут быть "наложены" на треугольники, повышая реализм подготовленного посредством рендеринга изображения. Третья стадия также выполняет сортировку с помощью Z-буфера.

Тем не менее рендеринг текстур и, в частности, трехмерных изображений и графики является вычислительно затратной задачей в отношении пропускной способности запоминающего устройства и вычислительной мощности, требуемой для графических систем. Например, текстуры являются затратными как в отношении запоминающего устройства (текстуры должны помещаться в быстрое однокристальное запоминающее устройства), так и в отношении пропускной способности запоминающего устройства, доступ к текстуре может осуществляться несколько раз, чтобы отрисовывать один пиксел. Также несколько текстур иногда могут требоваться для того, чтобы отрисовывать пиксел.

Чтобы уменьшать требования по пропускной способности и вычислительной мощности, типично используется способ или система кодирования текстур. Такая система кодирования должна приводить к более эффективному использованию дорогого однокристального запоминающего устройства и меньшей пропускной способности запоминающего устройства в ходе рендеринга, и таким образом, к меньшему энергопотреблению и/или более быстрому рендерингу. Это снижение требований к пропускной способности и мощности обработки особенно важно для тонких клиентов, таких как мобильные устройства и телефоны, с небольшим объемом памяти, маленькой пропускной способностью памяти и ограниченной мощностью (например, питаемых от аккумуляторов).

В данной области техники текстуры разделяются на так называемые текселные блоки, содержащие определенное число текселов. Такой текселный блок типично является прямоугольным или квадратным, к примеру, размера MR×MC текселов, где MR, MC являются положительными целыми числами с таким условием, что и MR и MC не являются одновременно единицами. Предпочтительно, MR=2mR и MC=2mC, где mR, mC являются положительными целыми числами. В типичной реализации, MR=MC, и такими предпочтительными вариантами осуществления блоков могут являться 4×4 тексела.

В данной области техники пиксел или элемент изображения иногда используется для того, чтобы обозначать элемент текстуры. В последующем описании, тексел тем не менее используется для того, чтобы обозначать элемент текстуры, и пиксел используется для того, чтобы обозначать элемент изображения, сформированный из таких текселов в связи с растеризацией.

Тексел ассоциирован с текселным значением, а пиксел ассоциирован с пикселным значением. Текселные и пикселные значения могут преимущественно быть значениями цвета. Значение цвета может быть представлено в различных цветных форматах, к примеру, красный, зеленый, синий (RGB) цвет или в качестве сигнала яркости и сигнала цветности. Кроме того, текселное значение может представлять другие свойства тексела, к примеру, нормаль или значение Z. В последующем описании, текселное значение неограниченно указывается в качестве примера значения цвета.

Типичный растризатор не осуществляет доступ к текстуре по одному текселу за раз. Вместо этого используется небольшое окружение текселов, к примеру, 2×2 текселов. Например, во время билинейной фильтрации, считываются четыре таких соседних тексела, чтобы формировать билинейно фильтрованное значение, т.е. пикселное значение. В данной области техники, такая группа соседних текселов, совместно обработанных с тем, чтобы формировать пикселное значение, типично обозначается как исправление. Следовательно, группа 2×2 текселов, используемая в билинейной фильтрации, обозначается как билинейное исправление. Этот принцип может быть дополнительно расширен, например, до трехлинейной фильтрации. Трехлинейная фильтрация использует два билинейных исправления из двух различных множественных отображений.

Проблема с обработкой исправлений текселов состоит в том, что текселы в исправлении могут охватывать несколько текселных блоков. Это схематично иллюстрируется на фиг. 1A-1D. Фиг. 1A иллюстрирует случай, в котором билинейное исправление 20 четырех текселов 30-36 находится в одном текселном блоке 10. Фиг. 1B и 1C иллюстрируют другой случай, когда билинейное исправление 20 охватывает два пикселных блока 10, 12, 14, присутствующих либо рядом (фиг. 1B), либо поверх друг друга (фиг. 1C). Экстремальный случай проиллюстрирован на фиг. 1D с одним текселом 30-36 билинейного исправления 20 в соответствующем текселном блоке 10-16.

Традиционный способ разрешать эту проблему состоит в том, чтобы использовать четыре идентичных декодера, каждый из которых декодирует предварительно определенный тексел в билинейном исправлении. Например, в случае фиг. 1A, кодированный текселный блок, представляющий текселный блок 10, вводится в четырех декодерах. Первый декодер выводит тексел (1, 2) 30, тексел (2, 2) получается из второго декодера, при этом третий и четвертый декодер формируют тексел (1, 3) и (2, 3) 36 билинейного исправления соответственно. Допускается система координат, в которой начало координат находится в левом верхнем текселе текселного блока 10. На фиг. 1D кодированный текселный блок текселного блока 10 вводится в первый декодер, чтобы формировать тексел (3, 3) 10, кодированный текселный блок текселного блока 12 обрабатывается посредством второго декодера, чтобы получать тексел (0, 3) 32. Тексел (3, 0) 34 получается из третьего декодера на основе кодированного текселного блока для текселного блока 14, и четвертый декодер выводит тексел (0, 0) 36 из кодированного текселного блока текселного блока 16.

Таким образом, следовательно, можно формировать билинейное исправление 2×2 каждый тактовый цикл независимо от того, какая конфигурация (фиг. 1A-1D) предоставляется. Высокопроизводительные аппаратные средства растеризации формируют два таких билинейных исправления в расчете на тактовый цикл, чтобы предоставлять трехлинейную фильтрацию. Тем не менее в таком случае восемь идентичных декодеров требуются согласно технологиям предшествующего уровня техники.

Принцип совместной обработки текселов в параллельных декодерах тем не менее резко увеличивает сложность системы декодирования, что является проблемой для тонких клиентов. Например, добавление вышеупомянутого PLANAR-режима в систему ETC-декодирования приводит к увеличению сложности, заданной как число сумматоров, с 6 сумматоров до 21 сумматора [3] в расчете на декодер. Таким образом, PLANAR использует в 3,5 раза больше сумматоров, чем ETC, и сложность системы декодирования, имеющей четыре ETC-декодера и четыре PLANAR-декодера, увеличивается в 3,5 раза.

Варианты осуществления, как раскрыто в данном документе, уменьшают сложность системы декодирования посредством отказа от использования идентичных параллельных декодеров. Наоборот, различная схема декодера может использоваться для декодеров, если декодеры выполнены с возможностью обрабатывать различное число текселов и различные текселные позиции в исправлении.

В общем варианте осуществления, система декодирования содержит

Каждый декодер 100, 200, 300, 400 дополнительно сконфигурирован с возможностью декодирования кодированных текселных блоков для формирования, по меньшей мере, одного текселного значения. Система 1 декодирования также содержит модуль 500 выбора значений, соединенный с

Общий вариант осуществления достигает уменьшения сложности декодеров 100, 200, 300, 400 посредством такого ограничения некоторых декодеров, что они имеют возможность обрабатывать текселы только в определенных текселных позициях в текселном блоке. Как следствие, схема этих декодеров 100, 200, 300, 400 может быть значительно уменьшена по сравнению со случаем предшествующего уровня техники без таких ограничений на декодеры.

В предпочтительном варианте осуществления, первый декодер 100 из

Если половина из

В предпочтительном варианте осуществления при

В случае, проиллюстрированном на фиг. 1D, все, предпочтительно четыре, декодера 100, 200, 300, 400 выводят текселные значения, которые выбираются посредством модуля 500 выбора значений. Таким образом, модуль 500 выбора значений в таком случае выполнен с возможностью избирательно выводить первое текселное значение из первого декодера 100, второе текселное значение из второго декодера 200, третье текселное значение из третьего декодера 300 и, в завершение, четвертое текселное значение из четвертого декодера 400. В этом случае каждый из четырех текселов 30-36 размещается в соответствующем текселном блоке 10-16.

Фиг. 2 схематично иллюстрирует структуру реализации с системой 1 декодирования согласно варианту осуществления. Структура содержит запоминающее устройство 5, типично RAM, имеющее местоположения в памяти, содержащие кодированные текселные блоки 40. Графический процессор (GPU) 4 соединяется с запоминающим устройством 5 через шину запоминающего устройства. GPU 4 включает в себя идентификатор 2 текселного блока для идентификации текселного блока, кодированный блок 40 которого должен извлекаться из запоминающего устройства 5. Идентификатор 2 текселного блока по существу вычисляет адрес кодированного текселного блока 40 в запоминающем устройстве 5 и отправляет запрос на доступ к памяти по шине в запоминающее устройство 5. Кодированный текселный блок 40, присутствующий в местоположении в памяти, назначенном или выделенном для текселного блока, считывается из запоминающего устройства 5 и передается по шине в систему 1 декодирования или в кэш 3 GPU 4.

Система 1 декодирования содержит или соединяется, по меньшей мере, с одним кэшем 3, имеющим местоположения или области в кэше для сохранения кодированных текселных блоков или декодированных текселных значений. В альтернативном варианте осуществления, GPU 4 может содержать систему кэшей 3, к примеру кэш текстур и кэш цветового буфера. GPU 4 типично соединяется с экраном 6 отображения, на котором отображается декодированное изображение.

GPU 4 и его включенные модули 1, 2, 3 могут предоставляться в одном или более кристаллов, таких как видеокарта, видеокарта или материнская плата. Структура реализации по фиг. 2 может быть реализована в любом процессоре текстур или изображений или устройстве, в том числе, например, в компьютере, игровой приставке, портативном устройстве, таком как мобильный телефон или устройство обработки мультимедиа.

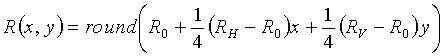

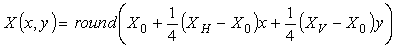

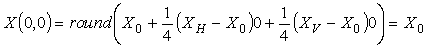

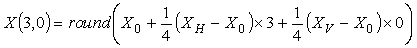

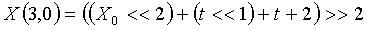

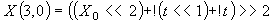

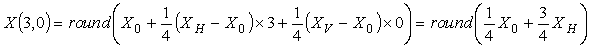

Далее, варианты осуществления системы декодирования описываются подробнее в связи с различными примерами реализации. Эти примеры дополнительно выполнены с возможностью подходить для того, чтобы обрабатывать текселные блоки, кодированные согласно PLANAR, описанному в [3, 4]. Кратко, PLANAR выполнен с возможностью обрабатывать текселные блоки с плавно варьирующимися сигналами цветности. PLANAR аппроксимирует цветовые компоненты (красный, зеленый, синий) в текселном блоке с помощью планарной аппроксимации. Чтобы указывать плоскость, достаточно указывать цвета в трех местоположениях в текселном блоке. Фиг. 5 иллюстрирует этот принцип с тремя компонентами R0, RH и RV красного цвета в определенных позициях относительно текселного блока 10. При таком размещении трех компонентов красного цвета, компонент красного цвета может быть вычислен в любом месте в текселном блоке 10 с использованием следующего уравнения:

Компоненты синего и зеленого цвета вычисляются идентично компоненту красного цвета. Кодированный текселный блок 40, как проиллюстрировано на фиг. 4, следовательно, содержит три цветовых кодовых слова 41-49 в расчете на цветовой компонент, т.е. X0, XH и XV, где X - это R для компонента красного цвета, G для компонента зеленого цвета и B для компонента синего цвета. В предпочтительной реализации, шесть битов предпочтительно расходуются на каждое из кодовых слов 41-43 красного цвета и кодовых слов 47-49 синего цвета и семь битов для каждого из кодовых слов 44-46 зеленого цвета, поскольку человеческий глаз является более чувствительным к компоненту зеленого цвета по сравнению с компонентами красного и синего цвета. Полный размер кодированного текселного блока составляет 57 битов, что точно соответствует 57-битовому режиму ETC2 [3]. Если PLANAR используется автономно, а не как специальный режим ETC, кодированный текселный блок 40 преимущественно расходует семь битов для всех кроме одного из цветовых кодовых слов 41-47, к примеру, G0, который вместо этого составляет восемь битов. Полный размер в таком случае составляет 64 бита.

В PLANAR-реализации, первый декодер 100 по фиг. 3 может декодировать любое билинейное исправление 2×2, которое имеет все четыре тексела в текселном блоке, см. фиг. 1A. Второй декодер 200 является менее совершенным и формирует текселные значения для текселов в первой строке или в первом столбце текселного блока, см. тексел 32, 36 на фиг. 1B и текселы 34, 36 на фиг. 1C. Второй декодер 200, следовательно, предпочтительно выводит два текселных значения сразу, исправление 2×1 или исправление 1×2. Третий декодер 300 декодирует кодированный текселный блок, чтобы формировать одно текселное значение, предпочтительно верхнее правое текселное значение в координате (3, 0), см. тексел 34 на фиг. 1D. Четвертый декодер 400 также предпочтительно выводит одно текселное значение тексела начала координат (0, 0), см. тексел 36 на фиг. 1D.

Это означает то, что если все текселы 30-36 билинейного исправления 20 находятся внутри границы текселного блока 10, как показано на фиг. 1A, вывод из первого декодера 100 выбирается посредством модуля 500 выбора значений. Если два тексела 30, 34 (30, 32) находятся в одном текселном блоке 10 и два 32, 36 (34, 36) находятся в соседнем текселном блоке 12 (14), как показано на фиг. 1B и 1C, текселные значения левых 30, 34 или верхних 30, 32 двух текселов получаются из первого декодера 100, а текселные значения из двух правых 32, 36 или нижних 34, 36 текселов поступают из второго декодера 200. В завершение, если все четыре тексела 30-36 находятся в различных текселных блоках 10-16, как показано на фиг. 1D, модуль 500 выбора значений выбирает текселное значение для левого верхнего тексела 30 из первого декодера 100, текселное значение для верхнего правого тексела 32 из второго декодера 200, текселное значение для нижнего правого тексела 34 из третьего декодера 300 и текселное значение для нижнего левого тексела 36 из четвертого декодера 400. Таким образом, все четыре тексела 30-36 билинейного исправления 20 могут быть получены в одном тактовом цикле с таким преимуществом, что второй-четвертый декодеры 200, 300, 400 могут быть реализованы с использованием очень небольшого числа аппаратных средств.

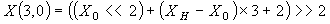

Из уравнения

Следовательно, четвертый декодер 400 может быть реализован вообще без логических вентилей.

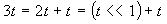

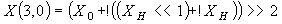

Третий декодер 300 должен, согласно пояснению выше, предпочтительно обрабатывать текселы в позиции (3, 0):

Умножение на три может быть заменено на прибавление числа к сдвинутой версии себя:

В каждом сумматоре существует возможность прибавления 1 посредством задания входа переноса=1 вместо 0. Следовательно, прибавление 2 может заменяться посредством изменения двух сумматоров таким образом. В нижеприведенном уравнении "+!" используется для того, чтобы указывать сумматор, имеющий вход переноса, заданный равным единице:

Операторы сдвига могут быть реализованы посредством соединения ветвей по-другому. Единственными оставшимися операциями, требуемыми для того, чтобы вычислять

Фиг. 7 иллюстрирует вариант осуществления схемы третьего декодера 300. Третий декодер 300 содержит оператор 310 сдвига влево для сдвига второго цветового кодового слова XH на одну позицию бита влево, чтобы получать сдвинутую влево битовую последовательность. Оператор 310 сдвига влево соединяется с первым сумматором 320, имеющим вход переноса, заданный равным единице. Этот первый сумматор 320 суммирует сдвинутую влево битовую последовательность со вторым цветовым кодовым словом XH. Результирующий вывод суммируется с первым цветовым кодовым словом X0 во втором сумматоре 322, имеющем вход переноса, заданный равным единице, и соединенном с первым сумматором 320. В завершение, второй сумматор 322 соединяется с оператором 330 сдвига вправо, выполненным с возможностью сдвигать битовую последовательность, соответствующую выводу второго сумматора 322, на две позиции бита вправо, чтобы формировать окончательный результат третьего декодера 300, т.е. текселное значение

В необязательном, но предпочтительном варианте осуществления первое цветовое кодовое слово X0 и второе цветовое кодовое слово XH предпочтительно сначала расширяются или разворачиваются с шести или семи битов до восьми битов. Как следствие, первый расширитель 380 предпочтительно размещается соединенным со вторым сумматором 322 и выполнен с возможностью расширять первое цветовое кодовое слово X0 в предварительно заданный размер в битах, предпочтительно восемь битов. Второй расширитель 382 предпочтительно размещается соединенным с оператором 310 сдвига влево и первым сумматором 320 и выполнен с возможностью расширять или разворачивать второе цветовое кодовое слово XH в предварительно заданный размер в битах, т.е. предпочтительно восемь битов.

Расширитель может быть реализован очень легко посредством простой компоновки, так что k старших битов l-битовой последовательности (k<l) копируются в k младших битов, чтобы получать l+k-битовую последовательность. Фиг. 10 является схематичной иллюстрацией реализации первого и второго расширителей 380, 382, подходящих для компонента зеленого цвета. Как видно на чертеже, старший бит входной 7-битовой последовательности копируется в позицию младшего бита, чтобы получать выходную 8-битовую последовательность. Для компонентов красного и синего цвета два старших бита копируются в две позиции младших битов, чтобы переходить от 6-битовой последовательности к 8-битовой последовательности.

При вышеуказанном размере в битах для кодированного текселного блока, т.е. шесть битов в расчете на цветовое кодовое слово для компонентов красного и синего цвета и семь битов в расчете на цветовое кодовое слово для компонента зеленого цвета и использовании двух расширителей, аппаратные схемы третьего декодера 300 могут быть реализованы всего с помощью 250,8 логических вентилей, если каждый сумматор имеет затраты в 4,4 логических вентиля в расчете на бит:

R/G/B: 1 9-битовый сумматор→9×4,4=39,6 логических вентилей

1 10-битовый сумматор→10×4,4=44 логических вентиля

Всего: 3×83,6=250,8 логических вентилей

Фиксаторы не требуются для третьего декодера 300 согласно предпочтительной реализации первого и второго декодеров, которая дополнительно поясняется в данном документе.

Фиг. 8 иллюстрирует вариант осуществления аппаратной реализации второго декодера 200. Второй декодер 200 содержит первый мультиплексор 250, выполненный с возможностью выводить одно из второго цветового кодового слова XH и третьего цветового кодового слова XV. Выбор цветового кодового слова зависит от того, размещается половина из четырех текселов в первой строке или первом столбце внутри границы текселного блока, кодированный текселный блок которого вводится во второй декодер 200. Если два пиксела размещаются в первой строке, второе цветовое кодовое слово XH выводится из первого мультиплексора 250, в противном случае, выводится третье цветовое кодовое слово XV. Оператор 240 отрицания выполнен с возможностью отрицать первое цветовое кодовое слово X0. Первый сумматор 220 соединяется с первым мультиплексором 250 и оператором 240 отрицания и суммирует вывод из этих модулей 240, 250, чтобы формировать разность XH-X0 или XV-X0. В альтернативной реализации, оператор 240 отрицания заменяется посредством оператора "НЕ", при этом первый сумматор 220 является сумматором с входом переноса, заданным равным единице. Использование оператора "НЕ" вместе с сумматором с входом переноса, заданным равным единице, в общем, предпочитается по сравнению с оператором отрицания с обычным сумматором с точки зрения аппаратной сложности.

Оператор 210 сдвига влево соединяется с первым сумматором 220 и выполнен с возможностью сдвигать битовую последовательность, соответствующую выводу сумматора, на одну позицию бита влево.

Второй мультиплексор 252 выполнен с возможностью выводить одну из координаты строки и координаты столбца тексела. Этот тексел является первым текселом из двух текселов, присутствующих в текселном блоке, кодированный текселный блок которого вводится во второй декодер 200. На чертеже SX обозначает координату столбца, а SY обозначает координату строки этого тексела. Если два тексела размещаются в первой строке, координата SX столбца выводится из второго мультиплексора 252, в противном случае координата SY строки.

Третий мультиплексор 254 соединяется с оператором 210 сдвига влево и первым сумматором 220. Третий мультиплексор 254 выбирает между 2×(XH/V-X0)=2d, т.е. выводом из оператора 210 сдвига влево, и (XH/V-X0)=d, т.е. выводом первого сумматора 220. Выбор осуществляется на основе значения старшего бита координаты строки или столбца, выводимой из второго мультиплексора 252.

Оператор 360 "ИЛИ" соединяется со вторым мультиплексором 352 и выполнен с возможностью осуществлять операцию "ИЛИ" для старшего бита и младшего бита координаты строки или столбца из второго мультиплексора 352. Оператор 360 "ИЛИ" и третий мультиплексор 254 дополнительно соединяются с оператором 270 "И". Этот оператор 270 "И" выполняет операцию "И" вывода мультиплексора побитового с одним битом из оператора 260 "ИЛИ". При этом результатом является то, что сохраняется вывод мультиплексора, если выводом "ИЛИ" является 1bin, и вывод из оператора 270 "И" равен нулю, если выводом "ИЛИ" является 0bin. Следовательно, выводом из оператора 270 "И" является 2d, d или 0.

Второй сумматор 222 соединяется с оператором 270 "И" и выполнен с возможностью суммировать вывод оператора 270 "И" и битовой последовательности, имеющей 10bin в качестве двух младших битов, которым предшествует первое цветовое кодовое слово X0. Эта битовая последовательность соответствует f=4×X0+2, что может быть реализовано посредством сдвига битовой последовательности первого цветового кодового слова X0 на две позиции бита влево и вставки 2=10bin в качестве последних двух битов, которые в противном случае равны нулю после сдвига. Выводом из второго сумматора 222, следовательно, является 2d+f, d+f или f.

Третий сумматор 224 соединяется с первым сумматором 220 и вторым сумматором 222 и выполнен с возможностью суммировать выводы из этих сумматоров 220, 222. Этот третий сумматор 224, следовательно, дает результат 3d+f, 2d+f или d+f. Первый оператор 230 сдвига вправо соединяется с третьим сумматором 224 и выполнен с возможностью сдвигать битовую последовательность из третьего сумматора 224 на две позиции бита вправо, чтобы получать текселное значение нижнего или правого тексела из двух текселов в первом столбце или первой строке в билинейном исправлении. Второй оператор 232 сдвига вправо соединяется со вторым сумматором 222 и сдвигает вывод сумматора на две позиции бита вправо, чтобы формировать текселное значение верхнего из левого тексела из двух текселов в первом столбце или первой строке.

Входные цветовые кодовые слова X0, XH, XV предпочтительно расширяются с шести или семи битов до восьми битов, аналогично третьему декодеру на фиг. 7. Как следствие, необязательные, но предпочтительные расширители 280, 282, 284 предпочтительно размещаются во входных терминалах, чтобы тем самым иметь первый расширитель 280, выполненный с возможностью расширять первое цветовое кодовое слово X0 до прибавления 10bin в качестве двух младших битов, чтобы формировать, в этом случае, 10-битовую последовательность. Первый расширитель 280 также соединяется с оператором 240 отрицания. Второй 282 и третий 284 расширитель соединяется с первым мультиплексором 250 и расширяет второе XH и третье XV цветовые кодовые слова соответственно.

В необязательной реализации, операторы 230, 232 сдвига вправо предпочтительно соединяются с соответствующим фиксатором или оператором 290, 292 фиксации. Эти фиксаторы 290, 292 выполнены с возможностью фиксировать вывод из операторов 230, 232 сдвига вправо между минимальным текселным значением и максимальным текселным значением. Таким образом, фиксаторы 290, 292 удостоверяются, что выходная битовая последовательность из второго декодера 200 находится в интервале допустимых значений. Пример такого интервала допустимых значений - это от 0 до 255, если выходные последовательности из второго декодера 200 должны иметь 8 битов.

Фиг. 11 иллюстрирует пример аппаратной реализации фиксатора 190-196, 290, 292, к примеру, используемого во втором декодере по фиг. 8 или первом декодере по фиг. 9. Этот вариант осуществления фиксатора выполнен с возможностью фиксировать 11-битовую последовательность, потенциально представляющую значение в интервале [-1024, 1023], до 8-битовой последовательности, представляющей значение в интервале [0, 255]. Фиксатор 190-196, 290, 292 содержит восемь операторов 701-708 "ИЛИ", каждый из которых принимает один из восьми младших битов входной битовой последовательности. Другие соответствующие вводы в операторы 701-708 "ИЛИ" соединяются с выводом другого оператора "ИЛИ" 700. Этот оператор "ИЛИ" 700 принимает два старших бита входной битовой последовательности. Выводы восьми операторов 701-708 "ИЛИ" соединяются с соответствующим оператором 711-718 "И". Другой соответствующий ввод операторов 711-718 "И" принимает знаковый бит входной битовой последовательности.

Альтернативный вариант осуществления реализации для фиксатора 190-196, 290, 292 проиллюстрирован на фиг. 12. В этом варианте осуществления, восемь операторов "ИЛИ" заменяются посредством восьми операторов 721-724 "ИЛИ-НЕ". Соответственно восемь операторов "И" по фиг. 11 также заменяются посредством восьми операторов 731-738 "ИЛИ-НЕ". Помимо этого, оператор 740 "НЕ" соединяется между восемью операторами 731-738 "ИЛИ-НЕ" и вводом для знакового бита входной битовой последовательности.

Затраты на реализацию аппаратного варианта осуществления, проиллюстрированного на фиг. 12, составляют:

16 "ИЛИ-НЕ"→16×1=16 логических вентилей

1 "ИЛИ"→1×1,5=1,5 логических вентиля

1 "НЕ"→1×0,5=0,5 логических вентиля

Всего: 16+1,5+0,5=18 логических вентилей

Число логических вентилей для примера реализации второго декодера 200 на фиг. 8, исключая фиксаторы, составляет:

R/G/B: 1 8-битовый сумматор→8×4,4=35,2 логических вентилей

1 11-битовый сумматор→11×4,4=48,4 логических вентилей

1 12-битовый сумматор→12×4,4=52,8 логических вентиля

1 8-битовый мультиплексор→8×2,2=17,6 логических вентилей

1 10-битовый мультиплексор→10×2,2=22 логических вентиля

1 2-битовый мультиплексор→2×2,2=4,4 логических вентиля

1 1-битовое "ИЛИ"→1×1,5=1,5 логических вентиля

1 10-битовое "И"→10×1,5=15 логических вентилей

1 8-битовое "НЕ"→8×0,5=4 логических вентилей

Всего: 3×200,9=602,7 логических вентиля

В завершение, фиг. 9 является примером аппаратной реализации первого декодера 100. Первый декодер 100 содержит оператор 140 отрицания, выполненный с возможностью отрицать первое цветовое кодовое слово X0. Первый сумматор 120 соединяется с оператором 140 отрицания и суммирует первое цветовое кодовое слово с отрицанием со вторым цветовым кодовым словом XH, чтобы получать g=XH-X0. Второй сумматор 122 также соединяется с оператором 140 отрицания и суммирует первое цветовое кодовое слово с отрицанием с третьим цветовым кодовым словом XV, чтобы получать h=XV-X0. В альтернативной реализации, оператор 140 отрицания заменяется посредством оператора "НЕ". В таком случае первый сумматор 120 и второй сумматор 122 имеют вход переноса, заданный равным единице.

Первый оператор 110 сдвига влево соединяется с первым сумматором 120 и сдвигает вывод сумматора на одну позицию бита влево, чтобы получать сдвинутую влево битовую последовательность, соответствующую 2g. Второй оператор 112 сдвига влево соединяется со вторым сумматором 122 и сдвигает вывод сумматора на одну позицию бита влево, чтобы получать битовую последовательность 2h. Первый мультиплексор 150 соединяется с первым оператором 110 сдвига влево и первым сумматором 120 и выполнен с возможностью выбирать между g и 2g на основе старшего бита координаты SX столбца. Второй мультиплексор 152 соответственно соединяется со вторым оператором 112 сдвига влево и вторым сумматором 122 и выбирает между h и 2h на основе старшего бита координаты SY строки. Координаты столбцов и строк являются координатами левого верхнего тексела в билинейном исправлении 2×2, т.е. тексела 30 на фиг. 1A-1D.

Первый оператор 160 "ИЛИ" выполняет операцию "ИЛИ" для старшего бита и младшего бита координаты SX столбца. Второй оператор 162 "ИЛИ" выполняет операцию "ИЛИ" для старшего бита и младшего бита координаты SY строки. Первый оператор 160 "ИЛИ" и первый мультиплексор 150 соединяются с первым оператором 170 "И", который выполняет побитовую операцию "И" для вывода мультиплексора с одним битом из первого оператора 160 "ИЛИ". Выводом из первого оператора 170 "И", следовательно, является 2g, g или 0. Второй оператор 172 "И" соединяется со вторым мультиплексором 152 и вторым оператором 162 "ИЛИ". Второй оператор 172 "И" выполняет побитовую операцию "И" для вывода мультиплексора с битом из второго оператора 162 "ИЛИ", чтобы получать вывод 2h, h или 0.

Третий сумматор 124 соединяется с первым оператором 124 "И" и суммирует вывод сумматора с битовой последовательностью, имеющей 10bin в качестве двух младших битов, которым предшествует первое цветовое кодовое слово. Эта битовая последовательность соответствует, как описано выше, f=4X0+2. Выводом сумматора, следовательно, является 2g+f, g+f или f. Четвертый сумматор 126 соединяется с первым сумматором 120 и третьим сумматором 124 и выполнен с возможностью суммировать выводы из этих сумматоров 120, 124, чтобы получать 3g+f, 2g+f или g+f. Пятый сумматор 128 соединяется со вторым сумматором 122 и вторым оператором 172 "И" и суммирует выводы из этих двух модулей 122, 172, чтобы получать 3h, 2h или h.

Шестой сумматор 121 соединяется с третьим сумматором 124 и вторым оператором 172 "И" и выполнен с возможностью суммировать выводы из этих модулей 124, 172. Первый оператор 130 сдвига вправо соединяется с шестым сумматором 121 и выполнен с возможностью сдвигать битовую последовательность вывода сумматора на две позиции бита вправо, чтобы получать текселное значение тексела 30 на фиг. 1A.

Седьмой сумматор 123 соединяется с четвертым сумматором 126 и вторым оператором 172 "И" и выполнен с возможностью суммировать выводы из этих модулей 126, 172. Второй оператор 132 сдвига вправо соединяется с седьмым сумматором 123 и выполнен с возможностью сдвигать битовую последовательность вывода сумматора на две позиции бита вправо, чтобы получать текселное значение тексела 32 на фиг. 1A.

Восьмой сумматор 125 соединяется с третьим сумматором 124 и пятым сумматором 128 и выполнен с возможностью суммировать выводы из этих сумматоров 124, 128. Третий оператор 134 сдвига вправо соединяется с восьмым сумматором 125 и выполнен с возможностью сдвигать битовую последовательность вывода сумматора на две позиции бита вправо, чтобы получать текселное значение тексела 34 на фиг. 1A.

Девятый сумматор 127 соединяется с четвертым сумматором 126 и пятым сумматором 128 и выполнен с возможностью суммировать выводы из этих сумматоров 126, 128. Четвертый оператор 136 сдвига вправо соединяется с четвертым сумматором 127 и выполнен с возможностью сдвигать битовую последовательность вывода сумматора на две позиции бита вправо, чтобы получать текселное значение тексела 36 на фиг. 1A.

В необязательной, но предпочтительной реализации входные цветовые кодовые слова X0 XH, XV сначала расширяются или разворачиваются с шести или семи битов до восьми битов. Как следствие, первый битовый расширитель 180 предпочтительно размещается соединенным с оператором 140 отрицания и дополнительно выполнен с возможностью расширять или разворачивать первое цветовое кодовое слово X0 в предварительно заданную битовую последовательность, предпочтительно восемь битов, до того как 10bin прибавляется в качестве младших битов, чтобы получать 10-битовую последовательность. Второй расширитель 182 соответственно размещается соединенным с первым сумматором 120 и выполнен с возможностью расширять второе цветовое кодовое слово XH. В завершение, третий расширитель 184 соединяется со вторым сумматором 122 и выполнен с возможностью расширять третье цветовое кодовое слово XV.

В необязательной реализации, каждый оператор 130-136 сдвига вправо предпочтительно соединяется с соответствующим фиксатором или оператором 190-196 фиксации. Эти фиксаторы 190-196 выполнены с возможностью фиксировать вывод из операторов 130-136 сдвига вправо между минимальным текселным значением и максимальным текселным значением. Таким образом, фиксаторы 190-196 удостоверяются, что выходная битовая последовательность из первого декодера 100 находится в интервале допустимых значений. Пример такого интервала допустимых значений - это от 0 до 255, если выходные последовательности из первого декодера 100 должны иметь 8 битов.

Число логических вентилей для примера реализации по фиг. 8 исключая необязательные фиксаторы 190-196, составляет:

R/G/B: 2 8-битовых сумматора→16×4,4=70,4 логических вентилей

1 10-битовый сумматор→10×4,4=44 логических вентиля

1 11-битовый сумматор→11×4,4=48,4 логических вентилей

5 12-битовых сумматоров→60×4,4=264 логических вентиля

2 10-битовых мультиплексора→20×2,2=44 логических вентиля

2 1-битовых "ИЛИ"→2×1,5=3 логических вентиля

2 10-битовых "И"→20×1,5=30 логических вентилей

1 8-битовое "НЕ"→8×0,5=4 логических вентиля

Всего: 3×507,8=1523,4 логических вентиля

Четыре декодера системы декодирования, следовательно, могут быть реализованы только с помощью 0+250,8+602,7+1523,4=2376,9 логических вентилей, исключая фиксаторы.

Традиционная реализация с четырьмя идентичными декодерами, предлагаемая в предшествующем уровне техники [3], очень походит на первый декодер на фиг. 9. Единственная разница состоит в том, что только один тексел требуется в выводе вместо четырех, как показано на чертеже. Следовательно, четыре сумматора 121, 123, 125, 127 в таком случае заменяются посредством двух четырёхсторонних мультиплексоров, после которых идет сумматор. Это приводит к затратам в 6 сумматоров, 4 мультиплексора и два оператора "И" в расчете на цветовой канал. Это означает то, что с четырьмя декодерами и тремя различными цветовыми компонентами затраты на аппаратные средства или сложность согласно предшествующему уровню техники составляют:

6×3×4=72 сумматора

4×3×4=48 мультиплексоров

2×3×4=24 оператора "И"

Это должно сравниваться с раскрытыми вариантами осуществления реализаций по фиг. 6-8, требующими:

(9+3+2+0)×3=42 сумматора

(2+3+0+0)×3=15 мультиплексоров

(2+1+0+0)×3=9 операторов "И"

Число сумматоров, следовательно, сокращено с 72 до 42, или на 42%. Мультиплексоры сокращены еще в большей степени в относительном выражении, с 48 до 15, или на 69%.

Фиг. 13 иллюстрирует вариант осуществления аппаратной реализации модуля 500 выбора значений. В этом варианте осуществления модуль 500 выбора значений содержит четыре мультиплексора 510, каждый из которых выводит текселное значение тексела 30-36 билинейного исправления. Первый мультиплексор 510 соединяется с четырьмя выводами первого декодера 100 и выбирает одну из четырех битовых последовательностей в качестве текселного значения первого тексела 30 в билинейном исправлении. Второй мультиплексор 520 соединяется со вторым и четвертым выводом первого декодера 100 и двумя выводами второго декодера 200. Этот второй мультиплексор 520 выводит текселное значение второго тексела 32 в билинейном исправлении. Третий мультиплексор 530 соединяется с третьим и четвертым выводами первого декодера 100, первым выводом второго декодера 200 и одним выводом третьего декодера 300. Третий мультиплексор 530 выводит текселное значение для третьего тексела 34 в билинейном исправлении. В завершение, четвертый мультиплексор 540 соединяется с четвертым выводом первого декодера 100, вторым выводом второго декодера 200 и одним выводом четвертого декодера 400. Четвертый мультиплексор 540 выбирает и выводит текселное значение четвертого тексела 36 в билинейном исправлении.

Позиция билинейного исправления относительно границы текселного блока предписывает то, какие битовые последовательности выводятся из мультиплексоров 510-540. Таким образом, в случае, проиллюстрированном на фиг. 1A, битовые последовательности из четырех выводов первого декодера 100 выбираются посредством мультиплексоров 510-540. Подробнее, первый мультиплексор 510 выводит битовую последовательность из первого вывода первого декодера 100, второй мультиплексор 520 выводит битовую последовательность из второго вывода, при этом третий 530 и четвертый 540 мультиплексоры выводят битовые последовательности из третьего и четвертого выводов декодера соответственно. Билинейное исправление с такой компоновкой, как проиллюстрировано на фиг. 1B, подразумевает, что первый мультиплексор 510 выбирает битовую последовательность второго вывода первого декодера 100. Второй мультиплексор 520 выбирает битовую последовательность первого вывода второго декодера 200. Третий декодер 300 выбирает битовую последовательность четвертого вывода из первого декодера 100, и четвертый декодер 400 выбирает битовую последовательность из второго вывода второго декодера 200. Принцип затем может применяться аналогичным образом к двум другим позициям исправлений, как проиллюстрировано на фиг. 1C и 1D.

Затраты с точки зрения числа логических вентилей на реализацию варианта осуществления модуля 500 выбора значений, как проиллюстрировано на фиг. 13, составляют:

3 8-битовых 4-сторонних мультиплексора→24×6,6=158,4 логических вентилей

1 8-битовый 3-сторонний мультиплексор→8×4,4=35,2 логических вентилей

Всего: 158,4+35,2=193,6 логических вентиля

Совокупные затраты для декодеров и модуля выбора значений, включающих в себя фиксаторы, составляют 2376,9+6×18+193,6=2678,5 логических вентилей.

Если фиксаторы первого и второго декодеров, как проиллюстрировано на фиг. 8 и 9, опущены и вместо этого заменены посредством четырех фиксаторов, каждый из которых соединен с одним из мультиплексоров 510-540 модуля 500 выбора значений, затраты на реализацию модуля 500 выбора значений увеличиваются, поскольку требуется три 11-битовых 4-сторонних мультиплексора и один 11-битовый 3-сторонний мультиплексор, приводя к затратам в 266,2 логических вентилей вместо 193,6 логических вентилей.

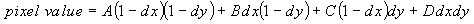

Модуль вычисления пикселов системы декодирования может быть реализован в аппаратных средствах согласно технологиям, известным в данной области техники. Подробнее, допустим, что четыре текселных значения, в случае билинейной фильтрации, из модуля выбора значений обозначаются как A, B, C и D. Модуль вычисления пикселов затем вычисляет пикселное значение как:

где dx является расстоянием вдоль оси X между средней точкой тексела A и точкой выборки для пиксела, а dy является соответствующим расстоянием вдоль оси Y между средней точкой тексела A и точкой выборки для пиксела.

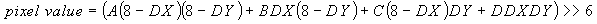

Вышеописанное уравнение выполняется параллельно для компонентов красного, зеленого и синего цвета. Аппаратная реализация затем может быть задана на основе уравнения. Например, допустим, что позиция точки выборки может выражаться тремя двоично-десятичными разрядами, например, позиция dx может допускать следующие значения [0,000, 0,125, 0,250, 0,375, 0,500, 0,625, 0,750, 0,875]. В таком случае, позиция может быть задана в восьмерках, так что вышеприведенные значения могут быть представлены посредством [0, 1, 2, 3, 4, 5, 6, 7]. Уравнение выше в таком случае может быть перезаписано следующим образом:

где DX=8×dx и DY=8×dy; DX, DY являются целыми числами между 0 и 7.

При анализе второго члена

Вывод из оператора умножения затем должен быть умножен на текселное значение B, предпочтительно число между 0 и 255. Это умножение может обрабатываться посредством оператора умножения, который берет два 8-битовых ввода и выводит 16-битовую битовую последовательность. Тем не менее только требуется четырнадцать младших битов из оператора умножения, поскольку наибольшее возможное число составляет 56×255<214.

Соответствующая реализация затем выполняется для других членов в уравнении, и выводы из соответствующих конечных операторов умножения суммируются и сдвигаются на шесть шагов вправо, чтобы получать конечное 8-битовое пикселное значение.

Вышеописанные примеры реализации должны рассматриваться просто в качестве предпочтительных, но неограничивающих вариантов осуществления того, как модули системы декодирования могут быть реализованы в аппаратных средствах. Их различные разновидности являются возможными и находится в пределах объема изобретения. Тем не менее важный признак состоит в том, что схема включения декодеров отличается с увеличением сложности, и каждый декодер выполнен с возможностью обрабатывать и выводить текселное значение(я) одного или более текселов в предварительно заданных позициях в исправлении.

Фиг. 14 является блок-схемой последовательности операций, иллюстрирующей способ формирования декодированного пиксела посредством декодирования, по меньшей мере, одного кодированного текселного блока. Способ начинается на этапе S1, на котором определяется позиция, по меньшей мере,

Этап S2 предпочтительно заключает в себе избирательный вывод всех

В предпочтительном варианте осуществления,

Вышеописанные варианты осуществления следует рассматривать как несколько иллюстративных примеров настоящего изобретения. Специалисты в данной области техники должны понимать, что различные модификации, комбинации и изменения могут быть выполнены в вариантах осуществления без отступления от объема настоящего изобретения. В частности, решения по различным частям в различных вариантах осуществления могут быть комбинированы в другие конфигурации, если технически осуществимо. Объем настоящего изобретения тем не менее задается посредством прилагаемой формулы изобретения.

ПРОТИВОПОСТАВЛЕННЫЕ МАТЕРИАЛЫ

[1] Патент (США) № 5956431.

[2] Ström and Möller, "iPACKMAN: High-Quality, Low-Complexity Texture Compression for Mobile Phones", Graphics Hardware, 2005, ACM Press, стр. 63-70

[3] Ström and Pettersson, "ETC2: Texture Compression using Invalid Combinations", Graphics Hardware, 2007, ACM Press, стр. 49-54

[4] Международная заявка номер WO 2006/126949

Изобретение относится к системе и способу декодирования, выполняемому для кодированных блоков элементов текстуры. Техническим результатом является повышение эффективности декодирования кодированных текселных блоков. Система (1) декодирования содержит N различных декодеров (100, 200, 300, 400), каждый из которых имеет уникальную схему, которая отличается от схем других N-1 декодеров. Декодеры (100, 200, 300, 400) формируют, по меньшей мере, одно текселное значение на основе входного кодированного текселного блока (40). Модуль (500) выбора значений выполнен с возможностью избирательно выводить, по меньшей мере, N текселных значений, по меньшей мере, из одного из декодеров (100, 200, 300, 400) на основе позиции, по меньшей мере, N текселов (30-36) относительно границы текселного блока (10), содержащего, по меньшей мере, один, по меньшей мере, из N текселов (30-36). Модуль (600) вычисления пикселов вычисляет пикселное значение декодированного пиксела на основе, по меньшей мере, N выбранных текселных значений из модуля (500) выбора значений. 2 н. и 15 з.п. ф-лы. 17 ил.

1. Система (1) декодирования для формирования декодированного пиксела на основе, по меньшей мере, одного кодированного текселного блока (40), причем упомянутая система (1) декодирования содержит:

-  различных декодеров (100, 200, 300, 400), каждый из которых имеет схему, имеющую уровень сложности, который отличается от уровня сложности схемы других

различных декодеров (100, 200, 300, 400), каждый из которых имеет схему, имеющую уровень сложности, который отличается от уровня сложности схемы других  декодеров, и выполнен с возможностью декодировать кодированный текселный блок (40), чтобы формировать, по меньшей мере, одно соответствующее текселное значение;

декодеров, и выполнен с возможностью декодировать кодированный текселный блок (40), чтобы формировать, по меньшей мере, одно соответствующее текселное значение;

- модуль (500) выбора значений, соединенный с упомянутыми  декодеров (100, 200, 300, 400) и выполненный с возможностью избирательно выводить, по меньшей мере,

декодеров (100, 200, 300, 400) и выполненный с возможностью избирательно выводить, по меньшей мере,  текселных значений, по меньшей мере, из одного из упомянутых

текселных значений, по меньшей мере, из одного из упомянутых  декодеров (100, 200, 300, 400) на основе позиций, по меньшей мере,

декодеров (100, 200, 300, 400) на основе позиций, по меньшей мере,  текселов (30-36), ассоциированных с упомянутыми, по меньшей мере,

текселов (30-36), ассоциированных с упомянутыми, по меньшей мере,  текселных значений относительно границы текселного блока (10), содержащего, по меньшей мере, один из упомянутых, по меньшей мере,

текселных значений относительно границы текселного блока (10), содержащего, по меньшей мере, один из упомянутых, по меньшей мере,  текселов (30-36); и

текселов (30-36); и

- модуль (600) вычисления пикселов, выполненный с возможностью вычислять декодированное пикселное значение упомянутого декодированного пиксела на основе упомянутых, по меньшей мере,  текселных значений, избирательно выводимых посредством упомянутого модуля (500) выбора значений.

текселных значений, избирательно выводимых посредством упомянутого модуля (500) выбора значений.

2. Система декодирования по п.1, в которой упомянутый модуль (500) выбора значений выполнен с возможностью избирательно выводить  текселных значений из первого декодера (100) из упомянутых

текселных значений из первого декодера (100) из упомянутых  декодеров (100, 200, 300, 400), если

декодеров (100, 200, 300, 400), если  текселов (30-36), ассоциированных с упомянутыми

текселов (30-36), ассоциированных с упомянутыми  текселных значений, размещаются внутри упомянутой границы текселного блока (10).

текселных значений, размещаются внутри упомянутой границы текселного блока (10).

3. Система декодирования по п.1, в которой упомянутый модуль (500) выбора значений выполнен с возможностью избирательно выводить половину из  текселных значений из первого декодера (100) из упомянутых

текселных значений из первого декодера (100) из упомянутых  декодеров (100, 200, 300, 400) и оставшуюся половину из упомянутых

декодеров (100, 200, 300, 400) и оставшуюся половину из упомянутых  текселных значений из второго декодера (200) из упомянутых

текселных значений из второго декодера (200) из упомянутых  декодеров (100, 200, 300, 400), если половина из

декодеров (100, 200, 300, 400), если половина из  текселов (30-36), ассоциированных с упомянутыми

текселов (30-36), ассоциированных с упомянутыми  текселных значений, размещается внутри упомянутой границы упомянутого текселного блока (10) и половина из упомянутых

текселных значений, размещается внутри упомянутой границы упомянутого текселного блока (10) и половина из упомянутых  текселов (30-36) является позициями внутри границы соседнего текселного блока (12, 14).

текселов (30-36) является позициями внутри границы соседнего текселного блока (12, 14).

4. Система декодирования по п.1, в которой  равно четырем, и упомянутый модуль (500) выбора значений выполнен с возможностью избирательно выводить первое текселное значение из упомянутых четырех текселных значений из первого декодера (100) из упомянутых четырех декодеров (100, 200, 300, 400), второе текселное значение из упомянутых четырех текселных значений из второго декодера (200) из упомянутых четырех декодеров (100, 200, 300, 400), третье текселное значение из упомянутых четырех текселных значений из третьего декодера (300) из упомянутых четырех декодеров (100, 200, 300, 400) и четвертое текселное значение из упомянутых четырех текселных значений из четвертого декодера (400) из упомянутых четырех декодеров (100, 200, 300, 400), если один из упомянутых четырех текселов (30-36) размещается внутри упомянутой границы упомянутого текселного блока (10) и каждый из оставшихся трех текселов размещается внутри границы соответствующего соседнего текселного блока (12, 14, 16).

равно четырем, и упомянутый модуль (500) выбора значений выполнен с возможностью избирательно выводить первое текселное значение из упомянутых четырех текселных значений из первого декодера (100) из упомянутых четырех декодеров (100, 200, 300, 400), второе текселное значение из упомянутых четырех текселных значений из второго декодера (200) из упомянутых четырех декодеров (100, 200, 300, 400), третье текселное значение из упомянутых четырех текселных значений из третьего декодера (300) из упомянутых четырех декодеров (100, 200, 300, 400) и четвертое текселное значение из упомянутых четырех текселных значений из четвертого декодера (400) из упомянутых четырех декодеров (100, 200, 300, 400), если один из упомянутых четырех текселов (30-36) размещается внутри упомянутой границы упомянутого текселного блока (10) и каждый из оставшихся трех текселов размещается внутри границы соответствующего соседнего текселного блока (12, 14, 16).

5. Система декодирования по п.1, в которой  равно четырем, и

равно четырем, и

- первый декодер (100) из упомянутых четырех декодеров (100, 200, 300, 400) имеет первую схему и выполнен с возможностью декодировать кодированный текселный блок (40), чтобы формировать четыре текселных значения;

- второй декодер (200) из упомянутых четырех декодеров (100, 200, 300, 400) имеет вторую схему и выполнен с возможностью декодировать кодированный текселный блок (40), чтобы формировать два текселных значения;

- третий декодер (300) из упомянутых четырех декодеров (100, 200, 300, 400) имеет третью схему и выполнен с возможностью декодировать кодированный текселный блок (40), чтобы формировать одно текселное значение; и

- четвертый декодер (400) из упомянутых четырех декодеров (100, 200, 300, 400) имеет четвертую схему и выполнен с возможностью декодировать кодированный текселный блок (40), чтобы формировать одно текселное значение.

6. Система декодирования по п.1, в которой упомянутый кодированный текселный блок (40) содержит первое цветовое кодовое слово (41, 44, 47), второе цветовое кодовое слово (42, 45, 48) и третье цветовое кодовое слово (43, 46, 49).

7. Система декодирования по п.6, в которой упомянутый четвертый декодер (400) содержит, по меньшей мере, одну ветвь, чтобы выводить упомянутое первое цветовое кодовое слово (41, 44, 47).

8. Система декодирования по п.6, в которой упомянутый третий декодер (300) содержит:

- оператор (310) сдвига влево, выполненный с возможностью сдвигать битовую последовательность, соответствующую упомянутому второму цветовому кодовому слову (42, 45, 48), на одну позицию бита влево, чтобы формировать сдвинутую влево битовую последовательность;

- первый сумматор (320), имеющий вход переноса, заданный равным единице, и соединенный с упомянутым оператором (310) сдвига влево и выполненный с возможностью суммировать упомянутое второе цветовое кодовое слово (42, 45, 48) и упомянутую сдвинутую влево битовую последовательность;

- второй сумматор (322), имеющий вход переноса, заданный равным единице, и соединенный с упомянутым первым сумматором (320) и выполненный с возможностью суммировать вывод упомянутого первого сумматора (320) и упомянутого первого цветового кодового слова (41, 44, 47); и

- оператор (330) сдвига вправо, соединенный с упомянутым вторым сумматором (322) и выполненный с возможностью сдвигать битовую последовательность, соответствующую выводу упомянутого второго сумматора (322), на две позиции бита вправо, чтобы формировать сдвинутую вправо последовательность.

9. Система декодирования по п.6, в которой упомянутый второй декодер (200) содержит:

- первый мультиплексор (250), выполненный с возможностью выводить одно из упомянутого второго цветового кодового слова (42, 45, 48) и упомянутого третьего цветового кодового слова (43, 46, 49) на основе того, размещается половина из четырех текселов (30-36) в строке или столбце внутри упомянутой границы упомянутого текселного блока (10);

- оператор (240) отрицания, выполненный с возможностью отрицать упомянутое первое цветовое кодовое слово (41, 44, 47);

- первый сумматор (220), соединенный с упомянутым первым мультиплексором (250) и упомянутым оператором (240) отрицания и выполненный с возможностью суммировать вывод упомянутого первого мультиплексора (250) и упомянутого первого цветового кодового слова с отрицанием;

- оператор (210) сдвига влево, соединенный с упомянутым первым сумматором (220) и выполненный с возможностью сдвигать битовую последовательность, соответствующую выводу упомянутого первого сумматора (220), на одну позицию бита влево, чтобы формировать сдвинутую влево битовую последовательность;

- второй мультиплексор (252), выполненный с возможностью выводить одну из координаты строки и координаты столбца тексела (32, 24) на основе того, размещается упомянутая половина из четырех текселов (30-36) в строке или столбце внутри упомянутой границы упомянутого текселного блока (10);

- третий мультиплексор (254), соединенный с упомянутым оператором (210) сдвига влево и упомянутым первым сумматором (220) и выполненный с возможностью выводить одно из упомянутого вывода упомянутого первого сумматора (220) и упомянутой сдвинутой влево битовой последовательности на основе старшего бита вывода упомянутого второго мультиплексора (252);

- оператор (260) "ИЛИ", соединенный с упомянутым вторым мультиплексором (252) и выполненный с возможностью принимать упомянутый старший бит упомянутого вывода упомянутого второго мультиплексора (252) и младший бит упомянутого вывода упомянутого второго мультиплексора;

- оператор (270) "И", соединенный с упомянутым третьим мультиплексором (254) и упомянутым оператором (260) "ИЛИ" и выполненный с возможностью принимать вывод упомянутого третьего мультиплексора (254) и вывод упомянутого оператора (260) "ИЛИ";

- второй сумматор (222), соединенный с упомянутым оператором (270) "И" и выполненный с возможностью суммировать вывод упомянутого оператора (270) "И" и битовой последовательности, имеющей 10bin в качестве двух младших битов, которым предшествует упомянутое первое цветовое кодовое слово (41, 44, 47);

- третий сумматор (224), соединенный с упомянутым первым сумматором (220) и упомянутым вторым сумматором (222) и выполненный с возможностью суммировать упомянутый вывод упомянутого первого сумматора (220) и вывод упомянутого второго сумматора (222);

- первый оператор (230) сдвига вправо, соединенный с упомянутым третьим сумматором (224) и выполненный с возможностью сдвигать битовую последовательность, соответствующую выводу упомянутого третьего сумматора (224), на две позиции бита вправо, чтобы формировать первую сдвинутую вправо последовательность;

- второй оператор (232) сдвига вправо, соединенный с упомянутым вторым сумматором (222) и выполненный с возможностью сдвигать битовую последовательность, соответствующую упомянутому выводу упомянутого второго сумматора (222), на две позиции бита вправо, чтобы формировать вторую сдвинутую вправо последовательность.

10. Система декодирования по п.6, в которой упомянутый второй декодер (200) содержит:

- первый мультиплексор (250), выполненный с возможностью выводить одно из упомянутого второго цветового кодового слова (42, 45, 48) и упомянутого третьего цветового кодового слова (43, 46, 49) на основе того, размещается половина из четырех текселов (30-36) в строке или столбце внутри упомянутой границы упомянутого текселного блока (10);

- оператор "НЕ", выполненный с возможностью отрицать упомянутое первое цветовое кодовое слово (41, 44, 47);

- первый сумматор (220), имеющий перенос, заданный равным единице, соединенный с упомянутым первым мультиплексором (250) и упомянутым оператором "НЕ" и выполненный с возможностью суммировать вывод упомянутого первого мультиплексора (250) и упомянутого первого цветового кодового слова с отрицанием;

- оператор (210) сдвига влево, соединенный с упомянутым первым сумматором (220) и выполненный с возможностью сдвигать битовую последовательность, соответствующую выводу упомянутого первого сумматора (220), на одну позицию бита влево, чтобы формировать сдвинутую влево битовую последовательность;

- второй мультиплексор (252), выполненный с возможностью выводить одну из координаты строки и координаты столбца тексела (32, 24) на основе того, размещается упомянутая половина из четырех текселов (30-36) в строке или столбце внутри упомянутой границы упомянутого текселного блока (10);

- третий мультиплексор (254), соединенный с упомянутым оператором (210) сдвига влево и упомянутым первым сумматором (220) и выполненный с возможностью выводить одно из упомянутого вывода упомянутого первого сумматора (220) и упомянутой сдвинутой влево битовой последовательности на основе старшего бита вывода упомянутого второго мультиплексора (252);

- оператор (260) "ИЛИ", соединенный с упомянутым вторым мультиплексором (252) и выполненный с возможностью принимать упомянутый старший бит упомянутого вывода упомянутого второго мультиплексора (252) и младший бит упомянутого вывода упомянутого второго мультиплексора;

- оператор (270) "И", соединенный с упомянутым третьим мультиплексором (254) и упомянутым оператором (260) "ИЛИ" и выполненный с возможностью принимать вывод упомянутого третьего мультиплексора (254) и вывод упомянутого оператора (260) "ИЛИ";

- второй сумматор (222), соединенный с упомянутым оператором (270) "И" и выполненный с возможностью суммировать вывод упомянутого оператора (270) "И" и битовой последовательности, имеющей 10bin в качестве двух младших битов, которым предшествует упомянутое первое цветовое кодовое слово (41, 44, 47);

- третий сумматор (224), соединенный с упомянутым первым сумматором (220) и упомянутым вторым сумматором (222) и выполненный с возможностью суммировать упомянутый вывод упомянутого первого сумматора (220) и вывод упомянутого второго сумматора (222);

- первый оператор (230) сдвига вправо, соединенный с упомянутым третьим сумматором (224) и выполненный с возможностью сдвигать битовую последовательность, соответствующую выводу упомянутого третьего сумматора (224), на две позиции бита вправо, чтобы формировать первую сдвинутую вправо последовательность;

- второй оператор (232) сдвига вправо, соединенный с упомянутым вторым сумматором (222) и выполненный с возможностью сдвигать битовую последовательность, соответствующую упомянутому выводу упомянутого второго сумматора (222), на две позиции бита вправо, чтобы формировать вторую сдвинутую вправо последовательность.

11. Система декодирования по п.6, в которой упомянутый первый декодер (100) содержит:

- оператор (140) отрицания, выполненный с возможностью отрицать упомянутое первое цветовое кодовое слово (41, 44, 47);

- первый сумматор (120), соединенный с упомянутым оператором (140) отрицания и выполненный с возможностью суммировать упомянутое второе цветовое кодовое слово (42, 45, 48) и упомянутое первое цветовое кодовое слово с отрицанием;

- второй сумматор (122), соединенный с упомянутым оператором (140) отрицания и выполненный с возможностью суммировать упомянутое третье цветовое кодовое слово (43, 46, 49) и упомянутое первое цветовое кодовое слово с отрицанием;

- первый оператор (110) сдвига влево, соединенный с упомянутым первым сумматором (120) и выполненный с возможностью сдвигать битовую последовательность, соответствующую выводу упомянутого первого сумматора (120), на одну позицию бита влево, чтобы формировать первую сдвинутую влево битовую последовательность;

- второй оператор (112) сдвига влево, соединенный с упомянутым вторым сумматором (122) и выполненный с возможностью сдвигать битовую последовательность, соответствующую выводу упомянутого второго сумматора (122), на одну позицию бита влево, чтобы формировать вторую сдвинутую влево битовую последовательность;

- первый мультиплексор (150), соединенный с упомянутым первым сумматором (120) и упомянутым первым оператором (110) сдвига влево и выполненный с возможностью выводить одно из упомянутого вывода упомянутого первого сумматора (120) и упомянутой первой сдвинутой влево битовой последовательности на основе старшего бита координаты столбца тексела (30);

- второй мультиплексор (152), соединенный с упомянутым вторым сумматором (122) и упомянутым вторым оператором (112) сдвига влево и выполненный с возможностью выводить одно из упомянутого вывода упомянутого второго сумматора (122) и упомянутой второй сдвинутой влево битовой последовательности на основе старшего бита координаты строки упомянутого тексела (30);

- первый оператор (160) "ИЛИ", выполненный с возможностью принимать упомянутый старший бит упомянутой координаты столбца и упомянутый младший бит упомянутой координаты столбца;

- второй оператор (162) "ИЛИ", выполненный с возможностью принимать упомянутый старший бит упомянутой координаты строки и упомянутый младший бит упомянутой координаты строки;

- первый оператор (170) "И", соединенный с упомянутым первым мультиплексором (150) и упомянутым первым оператором (160) "ИЛИ" и выполненный с возможностью принимать вывод упомянутого первого мультиплексора (150) и вывод упомянутого первого оператора (160) "ИЛИ";

- второй оператор (172) "И", соединенный с упомянутым вторым мультиплексором (152) и упомянутым вторым оператором (162) "ИЛИ" и выполненный с возможностью принимать вывод упомянутого второго мультиплексора (152) и вывод упомянутого второго оператора (162) "ИЛИ";

- третий сумматор (124), соединенный с упомянутым первым оператором (170) "И" и выполненный с возможностью суммировать вывод упомянутого первого оператора (170) "И" и битовой последовательности, имеющей 10bin в качестве двух младших битов, которым предшествует упомянутое первое цветовое кодовое слово (41, 44, 47);

- четвертый сумматор (126), соединенный с упомянутым первым сумматором (120) и упомянутым третьим сумматором (124) и выполненный с возможностью суммировать упомянутый вывод упомянутого первого сумматора (120) и вывод упомянутого третьего сумматора (124);

- пятый сумматор (128), соединенный с упомянутым вторым сумматором (122) и упомянутым вторым оператором (172) "И" и выполненный с возможностью суммировать упомянутый вывод упомянутого второго сумматора (122) и вывод упомянутого второго оператора (172) "И";

- шестой сумматор (121), соединенный с упомянутым третьим сумматором (124) и упомянутым вторым оператором (172) "И" и выполненный с возможностью суммировать упомянутый вывод упомянутого третьего сумматора (124) и упомянутый вывод упомянутого второго оператора (172) "И";

- седьмой сумматор (123), соединенный с упомянутым четвертым сумматором (126) и упомянутым вторым оператором (172) "И" и выполненный с возможностью суммировать упомянутый вывод упомянутого четвертого сумматора (126) и упомянутый вывод упомянутого второго оператора (172) "И";

- восьмой сумматор (125), соединенный с упомянутым третьим сумматором (124) и упомянутым пятым сумматором (128) и выполненный с возможностью суммировать упомянутый вывод упомянутого третьего сумматора (124) и вывод упомянутого пятого сумматора (128);

- девятый сумматор (127), соединенный с упомянутым четвертым сумматором (126) и упомянутым пятым сумматором (128) и выполненный с возможностью суммировать упомянутый вывод упомянутого четвертого сумматора (126) и упомянутый вывод упомянутого пятого сумматора (128);

- первый оператор (130) сдвига вправо, соединенный с упомянутым шестым сумматором (121) и выполненный с возможностью сдвигать битовую последовательность, соответствующую выводу упомянутого шестого сумматора (121), на две позиции бита вправо, чтобы формировать первую сдвинутую вправо последовательность;

- второй оператор (132) сдвига вправо, соединенный с упомянутым седьмым сумматором (123) и выполненный с возможностью сдвигать битовую последовательность, соответствующую выводу упомянутого седьмого сумматора (123), на две позиции бита вправо, чтобы формировать вторую сдвинутую вправо последовательность;

- третий оператор (134) сдвига вправо, соединенный с упомянутым восьмым сумматором (125) и выполненный с возможностью сдвигать битовую последовательность, соответствующую выводу упомянутого восьмого сумматора (125), на две позиции бита вправо, чтобы формировать третью сдвинутую вправо последовательность; и

- четвертый оператор (136) сдвига вправо, соединенный с упомянутым девятым сумматором (127) и выполненный с возможностью сдвигать битовую последовательность, соответствующую выводу упомянутого девятого сумматора (127), на две позиции бита вправо, чтобы формировать четвертую сдвинутую вправо последовательность.

12. Система декодирования по п.6, в которой упомянутый первый декодер (100) содержит:

- оператор "НЕ", выполненный с возможностью отрицать упомянутое первое цветовое кодовое слово (41, 44, 47);

- первый сумматор (120), имеющий вход переноса, заданный равным единице, соединенный с упомянутым оператором "НЕ" и выполненный с возможностью суммировать упомянутое второе цветовое кодовое слово (42, 45, 48) и упомянутое первое цветовое кодовое слово с отрицанием;

- второй сумматор (122), имеющий вход переноса, заданный равным единице, соединенный с упомянутым оператором "НЕ" и выполненный с возможностью суммировать упомянутое третье цветовое кодовое слово (43, 46, 49) и упомянутое первое цветовое кодовое слово с отрицанием;

- первый оператор (110) сдвига влево, соединенный с упомянутым первым сумматором (120) и выполненный с возможностью сдвигать битовую последовательность, соответствующую выводу упомянутого первого сумматора (120), на одну позицию бита влево, чтобы формировать первую сдвинутую влево битовую последовательность;

- второй оператор (112) сдвига влево, соединенный с упомянутым вторым сумматором (122) и выполненный с возможностью сдвигать битовую последовательность, соответствующую выводу упомянутого второго сумматора (122), на одну позицию бита влево, чтобы формировать вторую сдвинутую влево битовую последовательность;

- первый мультиплексор (150), соединенный с упомянутым первым сумматором (120) и упомянутым первым оператором (110) сдвига влево и выполненный с возможностью выводить одно из упомянутого вывода упомянутого первого сумматора (120) и упомянутой первой сдвинутой влево битовой последовательности на основе старшего бита координаты столбца тексела (30);

- второй мультиплексор (152), соединенный с упомянутым вторым сумматором (122) и упомянутым вторым оператором (112) сдвига влево и выполненный с возможностью выводить одно из упомянутого вывода упомянутого второго сумматора (122) и упомянутой второй сдвинутой влево битовой последовательности на основе старшего бита координаты строки упомянутого тексела (30);

- первый оператор (160) "ИЛИ", выполненный с возможностью принимать упомянутый старший бит упомянутой координаты столбца и упомянутый младший бит упомянутой координаты столбца;

- второй оператор (162) "ИЛИ", выполненный с возможностью принимать упомянутый старший бит упомянутой координаты строки и упомянутый младший бит упомянутой координаты строки;

- первый оператор (170) "И", соединенный с упомянутым первым мультиплексором (150) и упомянутым первым оператором (160) "ИЛИ" и выполненный с возможностью принимать вывод упомянутого первого мультиплексора (150) и вывод упомянутого первого оператора (160) "ИЛИ";

- второй оператор (172) "И", соединенный с упомянутым вторым мультиплексором (152) и упомянутым вторым оператором (162) "ИЛИ" и выполненный с возможностью принимать вывод упомянутого второго мультиплексора (152) и вывод упомянутого второго оператора (162) "ИЛИ";

- третий сумматор (124), соединенный с упомянутым первым оператором (170) "И" и выполненный с возможностью суммировать вывод упомянутого первого оператора (170) "И" и битовой последовательности, имеющей 10bin в качестве двух младших битов, которым предшествует упомянутое первое цветовое кодовое слово (41, 44, 47);

- четвертый сумматор (126), соединенный с упомянутым первым сумматором (120) и упомянутым третьим сумматором (124) и выполненный с возможностью суммировать упомянутый вывод упомянутого первого сумматора (120) и вывод упомянутого третьего сумматора (124);

- пятый сумматор (128), соединенный с упомянутым вторым сумматором (122) и упомянутым вторым оператором (172) "И" и выполненный с возможностью суммировать упомянутый вывод упомянутого второго сумматора (122) и вывод упомянутого второго оператора (172) "И";

- шестой сумматор (121), соединенный с упомянутым третьим сумматором (124) и упомянутым вторым оператором (172) "И" и выполненный с возможностью суммировать упомянутый вывод упомянутого третьего сумматора (124) и упомянутый вывод упомянутого второго оператора (172) "И";

- седьмой сумматор (123), соединенный с упомянутым четвертым сумматором (126) и упомянутым вторым оператором (172) "И" и выполненный с возможностью суммировать упомянутый вывод упомянутого четвертого сумматора (126) и упомянутый вывод упомянутого второго оператора (172) "И";

- восьмой сумматор (125), соединенный с упомянутым третьим сумматором (124) и упомянутым пятым сумматором (128) и выполненный с возможностью суммировать упомянутый вывод упомянутого третьего сумматора (124) и вывод упомянутого пятого сумматора (128);

- девятый сумматор (127), соединенный с упомянутым четвертым сумматором (126) и упомянутым пятым сумматором (128) и выполненный с возможностью суммировать упомянутый вывод упомянутого четвертого сумматора (126) и упомянутый вывод упомянутого пятого сумматора (128);

- первый оператор (130) сдвига вправо, соединенный с упомянутым шестым сумматором (121) и выполненный с возможностью сдвигать битовую последовательность, соответствующую выводу упомянутого шестого сумматора (121), на две позиции бита вправо, чтобы формировать первую сдвинутую вправо последовательность;

- второй оператор (132) сдвига вправо, соединенный с упомянутым седьмым сумматором (123) и выполненный с возможностью сдвигать битовую последовательность, соответствующую выводу упомянутого седьмого сумматора (123), на две позиции бита вправо, чтобы формировать вторую сдвинутую вправо последовательность;

- третий оператор (134) сдвига вправо, соединенный с упомянутым восьмым сумматором (125) и выполненный с возможностью сдвигать битовую последовательность, соответствующую выводу упомянутого восьмого сумматора (125), на две позиции бита вправо, чтобы формировать третью сдвинутую вправо последовательность; и

- четвертый оператор (136) сдвига вправо, соединенный с упомянутым девятым сумматором (127) и выполненный с возможностью сдвигать битовую последовательность, соответствующую выводу упомянутого девятого сумматора (127), на две позиции бита вправо, чтобы формировать четвертую сдвинутую вправо последовательность.

13. Система декодирования по п.6, в которой упомянутый модуль (500) выбора значений содержит:

- первый мультиплексор (510), соединенный с упомянутым первым декодером (100) и выполненный с возможностью выводить первое текселное значение;

- второй мультиплексор (520), соединенный с упомянутым первым декодером (100) и упомянутым вторым декодером (200) и выполненный с возможностью выводить второе текселное значение;

- третий мультиплексор (530), соединенный с упомянутым первым декодером (100), упомянутым вторым декодером (200) и упомянутым третьим декодером (300) и выполненный с возможностью выводить третье текселное значение; и

- четвертый мультиплексор (540), соединенный с упомянутым первым декодером (100), упомянутым вторым декодером (200) и упомянутым четвертым декодером (400) и выполненный с возможностью выводить четвертое текселное значение.

14. Способ формирования декодированного пиксела посредством декодирования, по меньшей мере, одного кодированного текселного блока (40), причем упомянутый способ содержит этапы, на которых: