Изобретение относится к автоматике и вычислительной технике. Целью изобретения является разработка устройства для моделирования процесса принятия решения в условиях неопределенности, обеспечивающего расширение функциональных возможностей.

Наиболее близким по технической сущности является устройство [1], содержащее генератор тактовых импульсов (ГТИ) 1, выход которого подсоединен к первому входу первого элемента И 2, выход которого подсоединен к входу счетчика 3, первый регистр 4, выход которого подсоединен к первому входу первой схемы сравнения 5, выход которой подсоединен к первому входу второго элемента И 17, группу вторых регистров 6j (j=1,…,n), матрицу из m*n третьих 7ij регистров, третьих элементов И 9ij (i=1,…,m, j=1,…,n), группу из m триггеров 10i (i=1,…,m).

Недостатком данного устройства является невозможность моделирования процесса принятия решения в условиях неопределенности [1].

Задача изобретения - создать устройство, обеспечивающее моделирование процесса принятия решения в условиях неопределенности с возможностью ранжирования вариантов принятия решения.

Сущность изобретения состоит в том, что в известное устройство, содержащее генератор тактовых импульсов (ГТИ) 1, выход которого подсоединен к первому входу первого элемента И 2, выход которого подсоединен к входу счетчика 3, первый регистр 4, выход которого подсоединен к первому входу первой схемы сравнения 5, выход которой подсоединен к первому входу второго элемента И 17, группу вторых регистров 6j (1=j,…,n), матрицу из m*n третьих 7ij регистров, третьих элементов И 9ij (i=1,…,m, j=1,…,n), группу из m триггеров 10i (i=1,…,m), введены сумматоры 11i (i=1,…,m), первый элемент задержки 12, второй элемент задержки 13, третий элемент задержки 14, блок выбора максимального кода (БВМК) 15, матрицу из m*n блоков умножения 8ij и стековую память 16, первый вход которой подсоединен к первому выходу БВМК 15, второй выход которого подсоединен к входам триггеров 10i (i=1,…,m), выходы каждого из которых подсоединены к первым входам элементов И 9ij (i=1…,m, j=1,…,n), вторые входы которых подсоединены к выходам одноименных блоков умножения 8ij (i=1,…,m, j=1,…,n), первые входы которых подсоединены к выходам вторых регистров 6j (j=1,…,n), вторые входы - к выходам одноименных третьих регистров 7ij (i=1,…,m, j=1,…,n), а третьи входы - к выходу первого элемента И 2, вход первого элемента задержки 12 подсоединен к выходу первого элемента И 2, а выход - к входу второго элемента задержки 13 и к первым входам сумматоров 11j (i=1,…,m), вторые входы которых подсоединены к выходам одноименных элементов И 9ij (i=1,…,m, j=1,…,n), а выходы - к одноименным первым входам БВМК 15, выход второго элемента задержки 13 подсоединен ко второму входу БВМК 15 и к входу третьего элемента задержки 14, выход которого подсоединен ко второму входу стековой памяти 16 и ко второму входу элемента И 17, выход схемы сравнения 5 подсоединен к инверсному входу элемента И 2, а второй вход - к выходу счетчика 3.

Проведенный поиск в известной научно-технической литературе не выявил наличие подобных технических решений.

Новизна предлагаемого устройства заключается в том, что новое техническое устройство отличается от прототипа тем, что дополнительно в него введены сумматоры 11i (i=1,…,m), первый элемент задержки 12, второй элементы задержки 13, третий элемент задержки 14, блок выбора максимального кода (БВМК) 15, матрицу из m*n блоков умножения 8ij и стековую память 16, первый вход которой подсоединен к первому выходу БВМК 15, второй выход которого подсоединен к входам триггеров 10 (i=1,…,m), выходы каждого из которых подсоединены к первым входам элементов И 9ij (i=1,…,m, j=1,…,n), вторые входы которых подсоединены к выходам одноименных блоков умножения 8ij (i=1,…,m, j=1,…,n), первые входы которых подсоединены к выходам вторых регистров 6j (j=1,…,n), вторые входы - к выходам одноименных третьих регистров 7ij (i=1,…,m, j=1,…,n), а третьи входы - к выходу первого элемента И 2, вход первого элемента задержки 12 подсоединен к выходу первого элемента И 2, а выход - к входу второго элемента задержки 13 и к первым входам сумматоров 11i (i=1,…,m), вторые входы которых подсоединены к выходам одноименных элементов И 9ij (i=1,…,m, j=1,…,n), а выходы - к одноименным первым входам БВМК 15, выход второго элемента задержки 13 подсоединен ко второму входу БВМК 15 и к входу третьего элемента задержки 14, выход которого подсоединен ко второму входу стековой памяти 16 и ко второму входу элемента И 17, выход схемы сравнения 5 подсоединен к инверсному входу элемента И 2, а второй вход - к выходу счетчика 3.

Изобретательский уровень достигается тем, что ввод соответствующих элементов в известный прототип вместе со связями позволяет решить новую техническую задачу, решение которой в известных технических решениях и в литературе в настоящее время не отражено.

Предлагаемое устройство позволяет быстро решить задачу моделирования процесса принятия решения в условиях неопределенности.

Сущность изобретения поясняется чертежом, на котором приведена структурная схема заявленного устройства.

Устройство для моделирования процесса принятия решения (см. чертеж) содержит: генератор тактовых импульсов (ГТИ) 1, элемент И 2, счетчик 3, регистр 4, схему сравнения 5, группу из n регистров 6j (j=1,…,n), группу из m*n регистров 7ij (i=1,…,m, j=1,…,n), группу из m*n блоков умножения 8ij (i=1,…,m, j=1,…,n), группу из m*n элементов И 9ij (i=1,…,m, j=1,…,n), группу из m триггеров 10i(i=1,…,m), группу из m сумматоров 111 (i=1,…,m), элементы задержки 12, 13, 14, блок выбора максимального кода 15 [2], стековую память 16, элемент И 17, выходы устройства 18 и 20, вход устройства 19.

Стековая память 16 может быть выполнена как последовательность m сдвигающих регистров.

Устройство работает следующим образом.

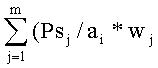

Предполагается, что имеется m допустимых стратегий (управляющих воздействий A={ai} (i=1, 2,…m) на систему). При этом вероятность наступления исхода Sj из множества исходов S={sj}, (j=1, 2,…n) в результате применения стратегии ai задается распределением вероятностей на множестве возможных исходов Psj/aj. Кроме того, каждому исходу Sj приписывается некоторая субъективная ценность исхода Wj ∈ W, W={wj}, (j=1, 2,…,n). Устройство позволяет в результате просмотра всех альтернативных и возможных вариантов выбрать наилучшую альтернативу аi ∈ А (i=1, 2,…m), для которой выполняется максимум целевой функции

В исходном состоянии (см. чертеж):

- все регистры стека 16, сумматоры 11i (i=1,…,m), счетчик 3 находятся в нулевом состоянии;

- на регистре 4 записан код числа m (число вариантов);

- на регистрах 7ij хранятся коды значений Рij j-го критерия по i -му варианту (i=11,…,m, j=1,…,n);

- триггеры 10j (i=1,…,m) установлены в единичное состояние, поэтому на их выходах будет единичный сигнал;

- на регистрах 6j хранятся коды коэффициентов важности j-го критерия (j=1,…,n) (установочные входы на чертеже из-за его громоздкости не показаны);

- на инверсный вход элемента И 2 поступает нулевой сигнал с выхода схемы сравнения 5.

Устройство для моделирования процесса принятия решения функционирует следующим образом (см. чертеж). На вход 19 устройства поступает пусковой сигнал, который подается на управляющий вход элемента И 2, после чего счетные импульсы с выхода генератора 1 через открытый элемент И 2 поступают на счетный вход счетчика 3, на вход элемента задержки 12 и на управляющие входы блоков умножения 8ij (i=1,…,m, j=1,…,n). Содержимое счетчика 3 далее поступает на вход схемы сравнения 5.

На входы блоков умножения 8ij (i=1,…,m, j=1,…,n) поступают коды с выходов регистров 7ij (значения Рij j-го критерия по i-му варианту) и коды с выходов регистров 6j (коэффициенты важности j-го критерия (j=1,…,n)). Результаты умножения с выходов блоков 8ij (i=1,…,m, j=1,…,n) через открытые элементы И 9ij (i=1,…,m, j=1,…,n) поступают на одноименные входы сумматоров 11j (i=1,…,m).

На управляющие входы сумматоров 11i (i=1,…,m) поступает единичный сигнал с выхода элемента И 2, задержанный элементом задержки 12 на время надежного срабатывания блока умножения 8ij и элемента И 9ij (i=1,…,m, j=1,…,n). Выходы сумматоров 11i (i=1,…,m) подсоединены к одноименным входам блока выбора максимального кода 15, на управляющий вход которого поступает единичный сигнал, задержанный элементом задержки 13 на время надежного срабатывания сумматоров 11i (i=1,…,m).

Значение максимального кода с выхода блока выбора максимального кода 15 поступает на информационный вход блока стековой памяти 16, а через время надежного срабатывания блока выбора максимального кода 15 на управляющий вход стековой памяти 16 поступает задержанный сигнал элементом задержки 14, после чего происходит сдвиг данных в стековой памяти 16 на одну позицию.

Одновременно после срабатывания блока выбора максимального кода 15 на другом его выходе появляется код с одной единицей, соответствующей максимальному коду, по которому осуществляется сброс одноименного триггера 10i (i=1,…,m) в нулевое состояние. В результате далее коды с выходов блоков умножения 8ij через элементы И 9ij в i-й строке матрицы будут поступать на входы блока выбора максимального кода 15 нулевыми.

Аналогичным образом происходит работа устройства после прихода очередных импульсов с выхода генератора 1 вплоть до прихода m-го импульса, после чего на счетчике 3 зафиксируется код числа m, в результате чего сработает схема сравнения 5, на ее выходе появится единичный сигнал, который подается на инверсный вход элемента И 2, запрещающий подачу тактовых импульсов с выхода генератора 1. Кроме того, единичный сигнал с выхода схемы сравнения 5 подается на второй вход элемента И 17, на выходе которого появляется сигнал 20 окончания работы устройства.

Результатом работы устройства являются коды с выхода 18 блока 16 после появления сигнала окончания работы устройства 20 с выхода элемента И 17. Таким образом, описанное устройство позволяет моделировать процесс принятия решения при наличии многих вариантов и некоторого количества критериев значимости, выбирать из них максимальный и ранжировать их.

Литература.

1. Патент 2335016. Устройство для моделирования системы защиты вычислительной сети. Опубликовано: 27.09.2008.

2. Авторское свидетельство 1128249. Устройство для выделения экстремального кода. Опубликовано: 08.08.1984.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ СИСТЕМЫ ЗАЩИТЫ ВЫЧИСЛИТЕЛЬНОЙ СЕТИ | 2007 |

|

RU2335016C1 |

| Устройство для технико-экономической оценки выполнения научно-исследовательских и опытно-конструкторских работ | 2015 |

|

RU2613022C1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ СИСТЕМЫ ЗАЩИТЫ ВЫЧИСЛИТЕЛЬНОЙ СЕТИ | 2005 |

|

RU2292081C1 |

| Устройство для моделирования графика работы сотрудников учреждения | 2022 |

|

RU2788323C1 |

| Устройство для решения задачи о назначениях | 2016 |

|

RU2613523C1 |

| Устройство для решения задачи о рюкзаке | 2015 |

|

RU2613854C1 |

| ОПТИЧЕСКИЙ КОНЪЮНКТОР НЕПРЕРЫВНЫХ МНОЖЕСТВ | 2009 |

|

RU2419128C2 |

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ЗАДАЧИ О НАЗНАЧЕНИЯХ | 2010 |

|

RU2439687C1 |

| Устройство для формирования потенциала инновационного проекта | 2017 |

|

RU2669071C1 |

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ЗАДАЧИ О РЮКЗАКЕ | 2014 |

|

RU2542661C1 |

Изобретение относится к устройствам принятия решения в условиях неопределенности. Техническим результатом является расширение функциональных возможностей устройства за счет обеспечения возможности ранжирования вариантов принятия решения. Устройство содержит сумматоры 11i (i=1,…,m), первый элемент задержки 12, второй элемент задержки 13, третий элемент задержки 14, блок выбора максимального кода (БВМК) 15, матрицу из m*n блоков умножения 8ij, стековую память 16, входные триггеры 10i, (i=1,…,m), элемент И 9ij (i=1,…,m, j=1,…,n), блоки умножения 8ij (i=1,…,m, j=1,…,n), вторые регистры 6j (j=1,…,n), третьи регистры 7ij (i=1,…,m, j=1,…,n), первый элемент И 2, элемент задержки 12, второй элемент задержки 13, сумматоры 11i (i=1,…,m), элементы И 9ij (i=1,…,m, j=1,…,n), стековую память 16, элемент И 17, схему сравнения 5. 1 ил.

Устройство для моделирования процесса принятия решения, содержащее генератор тактовых импульсов (ГТИ) 1, выход которого подсоединен к первому входу первого элемента И 2, выход которого подсоединен к входу счетчика 3, первый регистр 4, выход которого подсоединен к первому входу первой схемы сравнения 5, выход которой подсоединен к первому входу второго элемента И 17, группу вторых регистров 6j (j=1,…,n), матрицу из m*n третьих 7ij регистров, третьих элементов И 9ij (i=1,…,m, j=1,…,n), группу из m триггеров 10i (i=1,…,m), отличающееся тем, что в него дополнительно включены сумматоры 11i (i=1,…,m), первый элемент задержки 12, второй элемент задержки 13, третий элемент задержки 14, блок выбора максимального кода (БВМК) 15, матрица из m*n блоков умножения 8ij и стековая память 16, первый вход которой подсоединен к первому выходу БВМК 15, второй выход которого подсоединен к входам триггеров 10i (i=1,…,m), выходы каждого из которых подсоединены к первым входам элементов И 9ij (i=1,…,m, j=1,…,n), вторые входы которых подсоединены к выходам одноименных блоков умножения 8ij (i=1,…,m, j=1,…,n), первые входы которых подсоединены к выходам вторых регистров 6j (j=1,…,n), вторые входы - к выходам одноименных третьих регистров 7ij (i=1,…,m, j=1,…,n), а третьи входы - к выходу первого элемента И 2, вход первого элемента задержки 12 подсоединен к выходу первого элемента И 2, а выход - к входу второго элемента задержки 13 и к первым входам сумматоров 11i (i=1,…,m), вторые входы которых подсоединены к выходам одноименных элементов И 9ij (i=1,…,m, j=1,…,n), а выходы - к одноименным первым входам БВМК 15, выход второго элемента задержки 13 подсоединен ко второму входу БВМК 15 и к входу третьего элемента задержки 14, выход которого подсоединен ко второму входу стековой памяти 16 и ко второму входу элемента И 17, выход схемы сравнения 5 подсоединен к инверсному входу элемента И 2, а второй вход - к выходу счетчика 3.

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ПРОЦЕССА ПРИНЯТИЯ РЕШЕНИЯ В УСЛОВИЯХ НЕОПРЕДЕЛЕННОСТИ | 2011 |

|

RU2468423C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ АВТОНОМНЫМ РОБОТОМ | 2008 |

|

RU2424105C2 |

| Устройство для выбора оптимальных решений | 1989 |

|

SU1640716A1 |

| CN 101833709 A, 15.09.2010 | |||

| EP 1517281 A2, 23.03.2005 | |||

| US 7103124 B1, 05.09.2006 | |||

| US 20040015376 A1, 22.01.2004 | |||

Авторы

Даты

2014-12-10—Публикация

2013-03-29—Подача