Фиг.1

Изобретение относится к автоматике и контрольно-измерительной.технике и может быть использовано в автоматизированных системах управления различными технологическими процессами как средство измерения, регистрации и позиционного регулирования температуры, давления и других физических величин, преобразованных в электрические.

Цель изобретения - повышение надежности устройства по регистрации, управлению и аварийной защите технологических процессов.

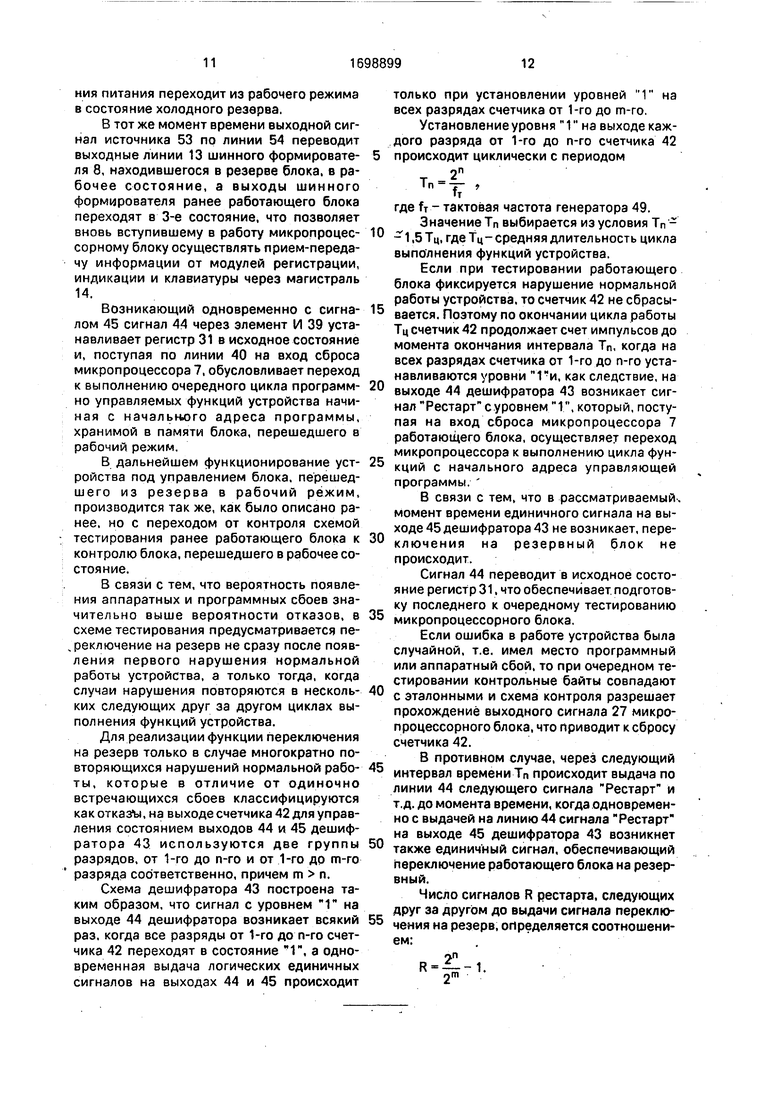

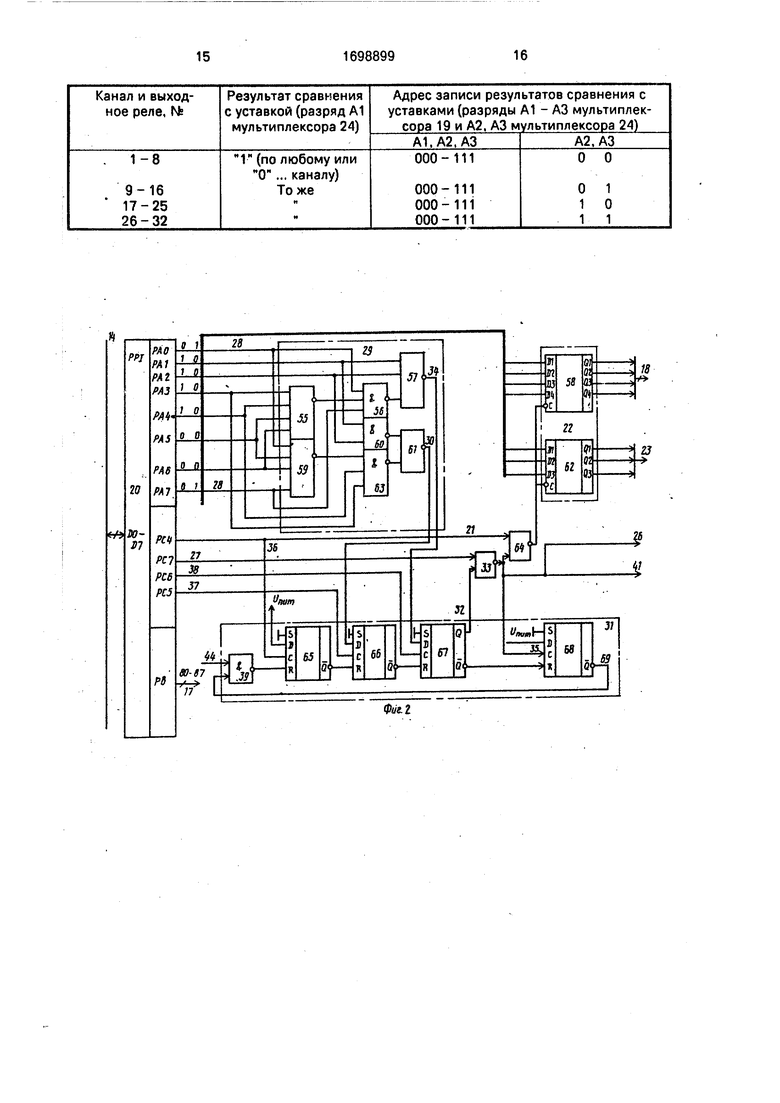

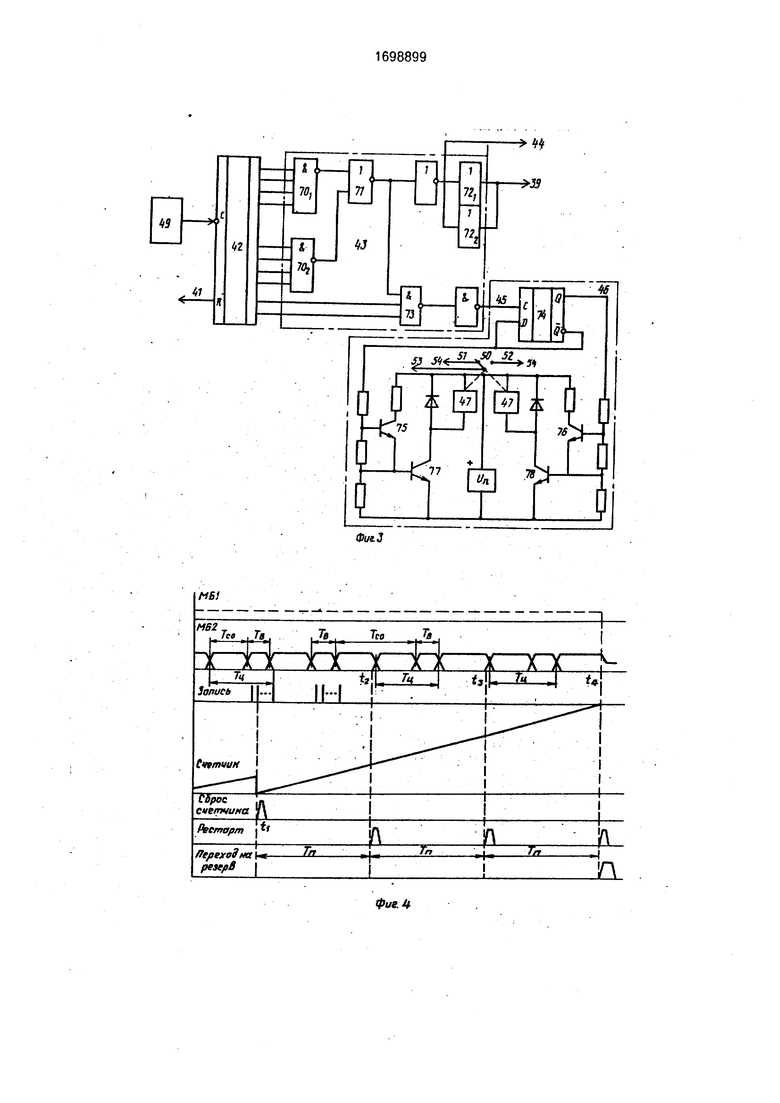

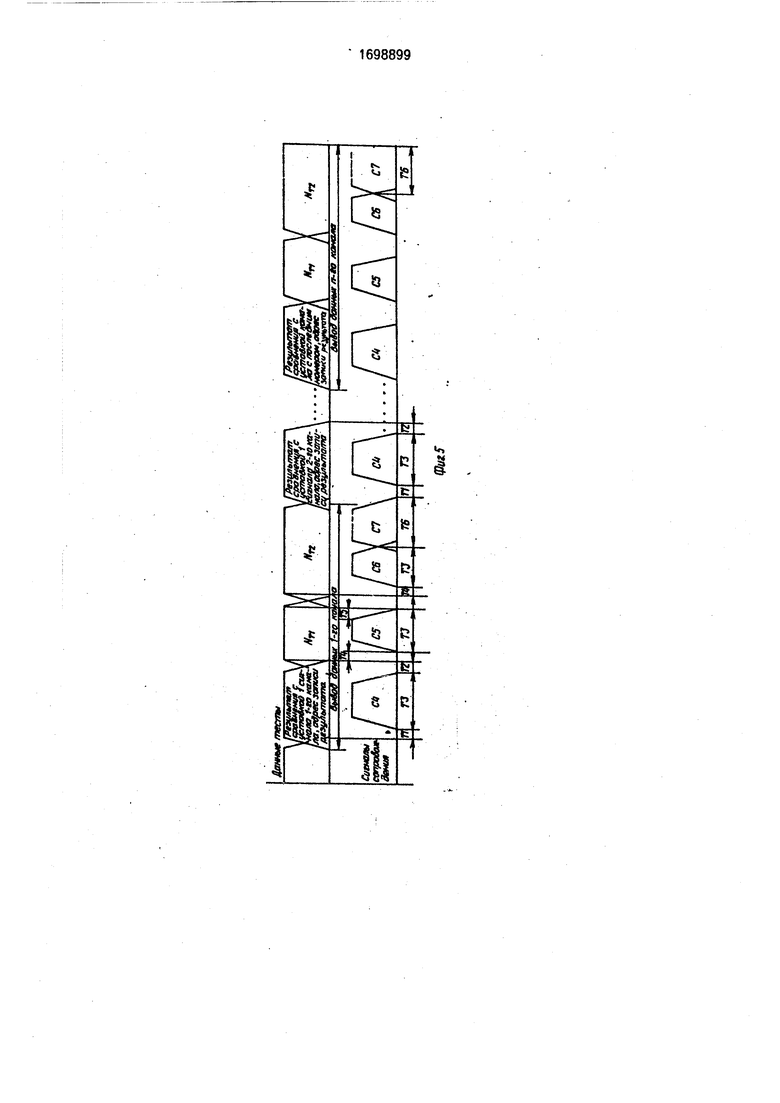

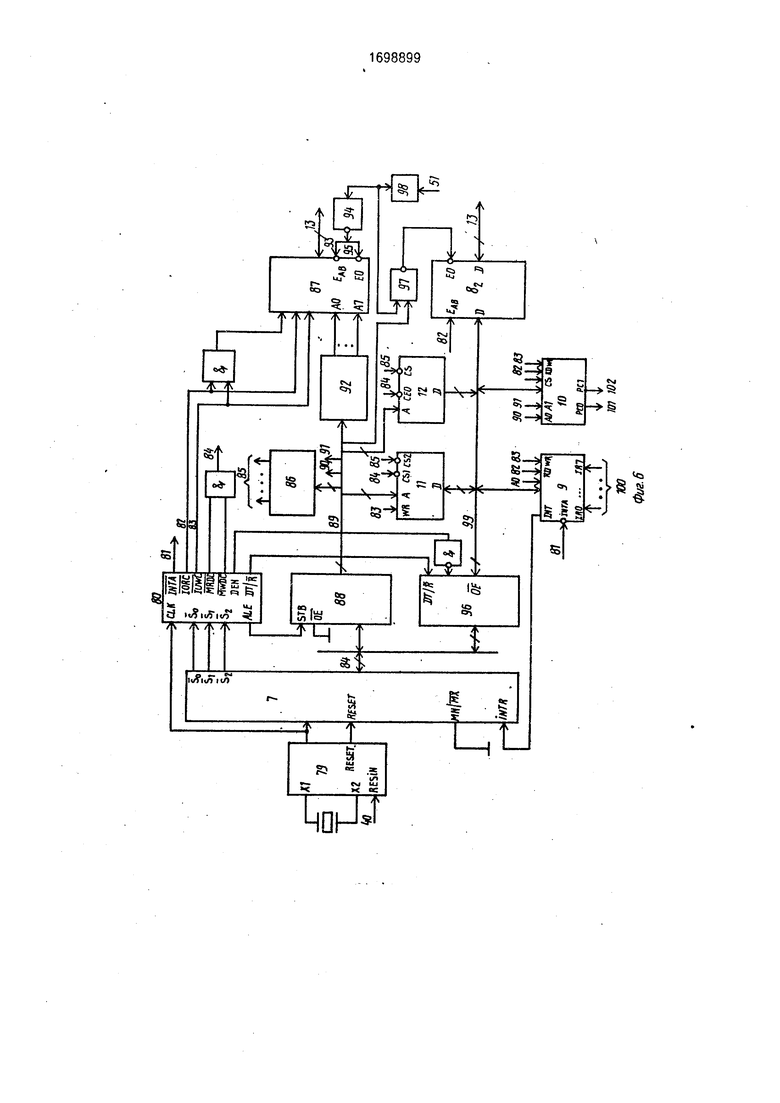

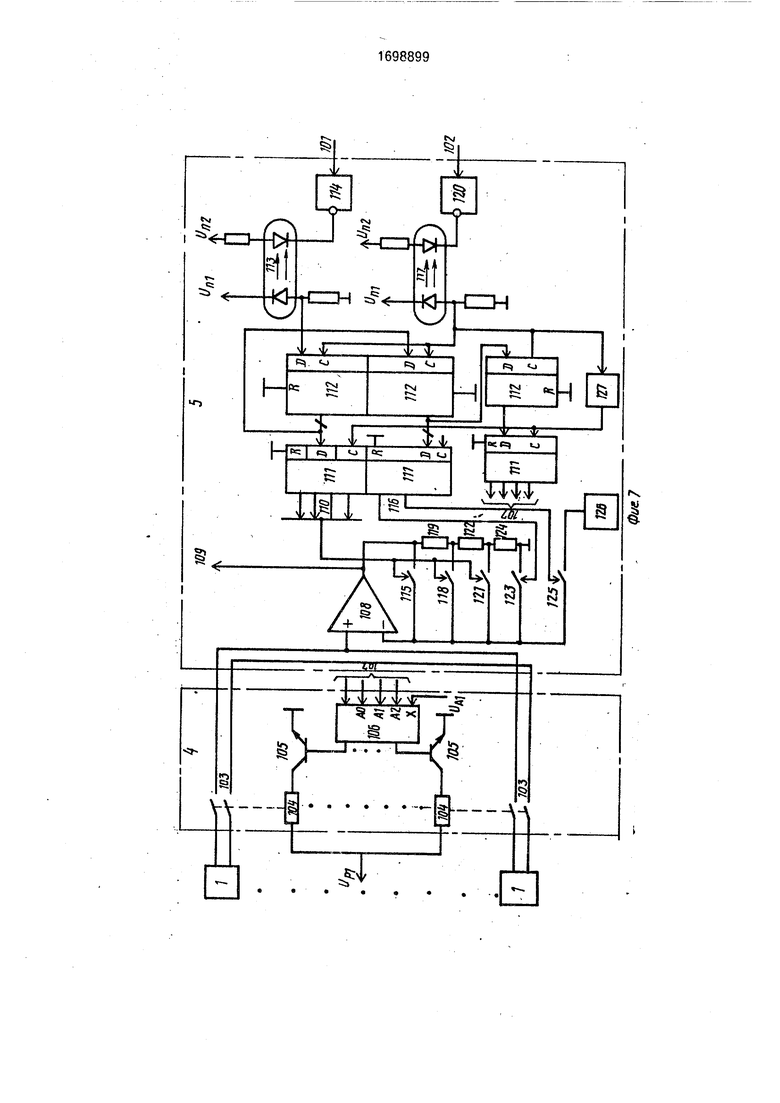

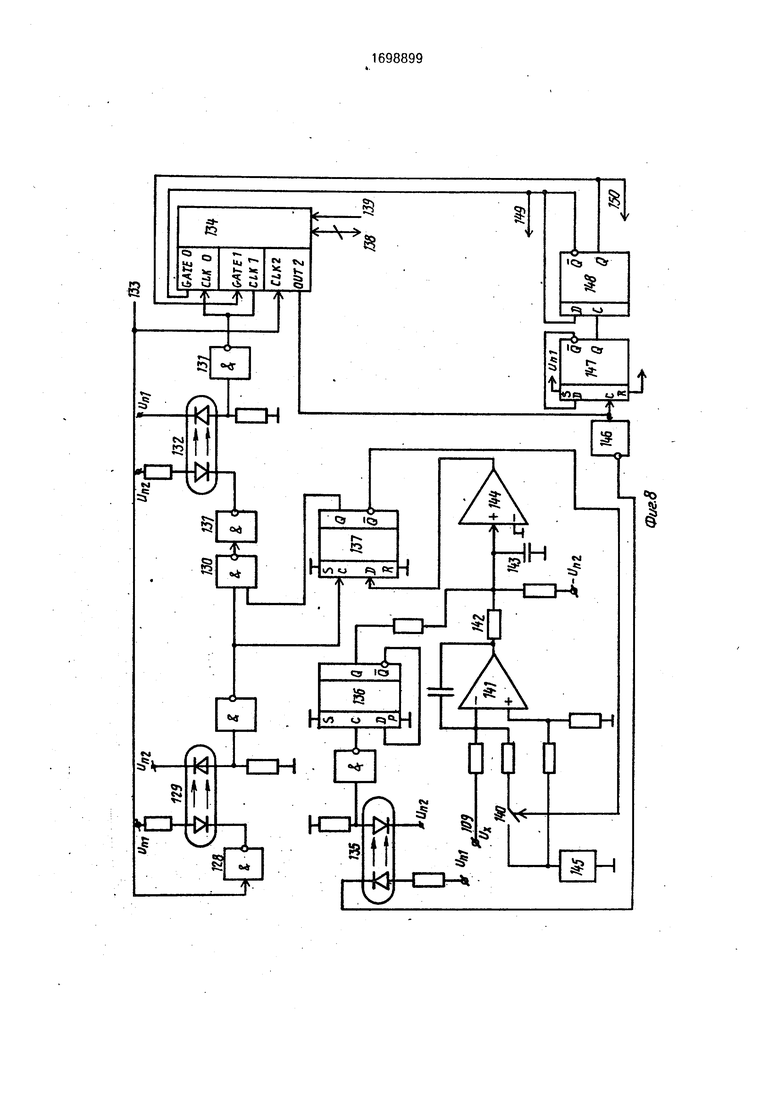

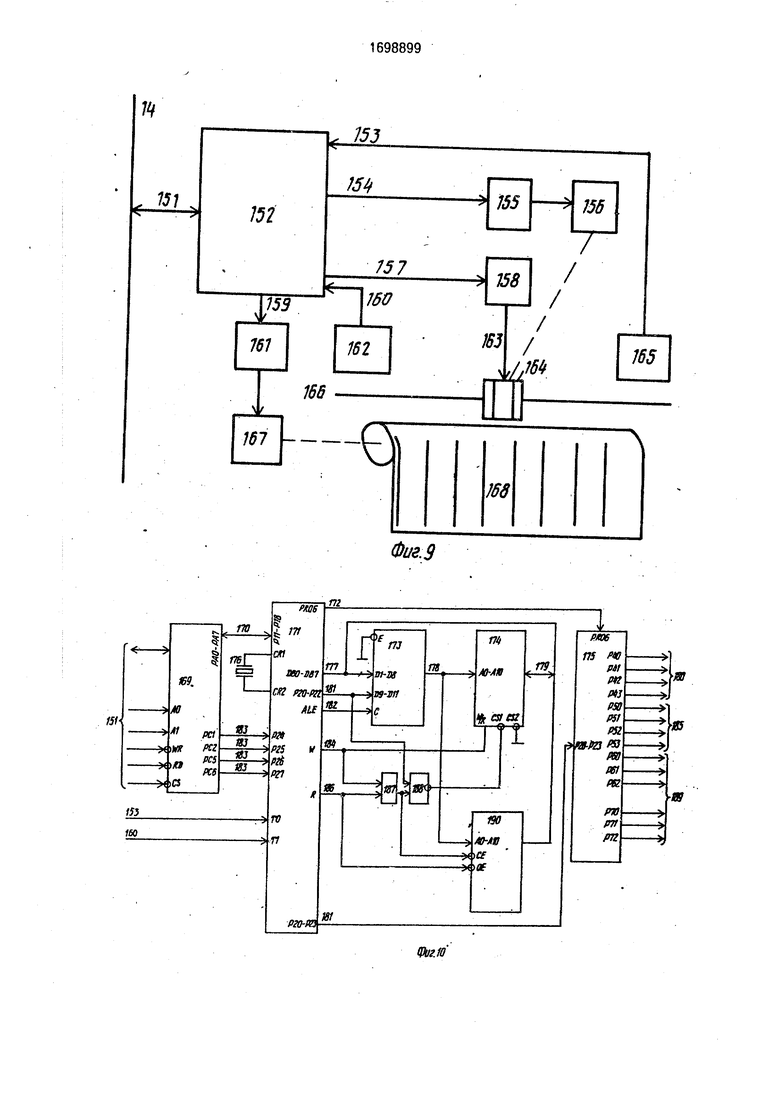

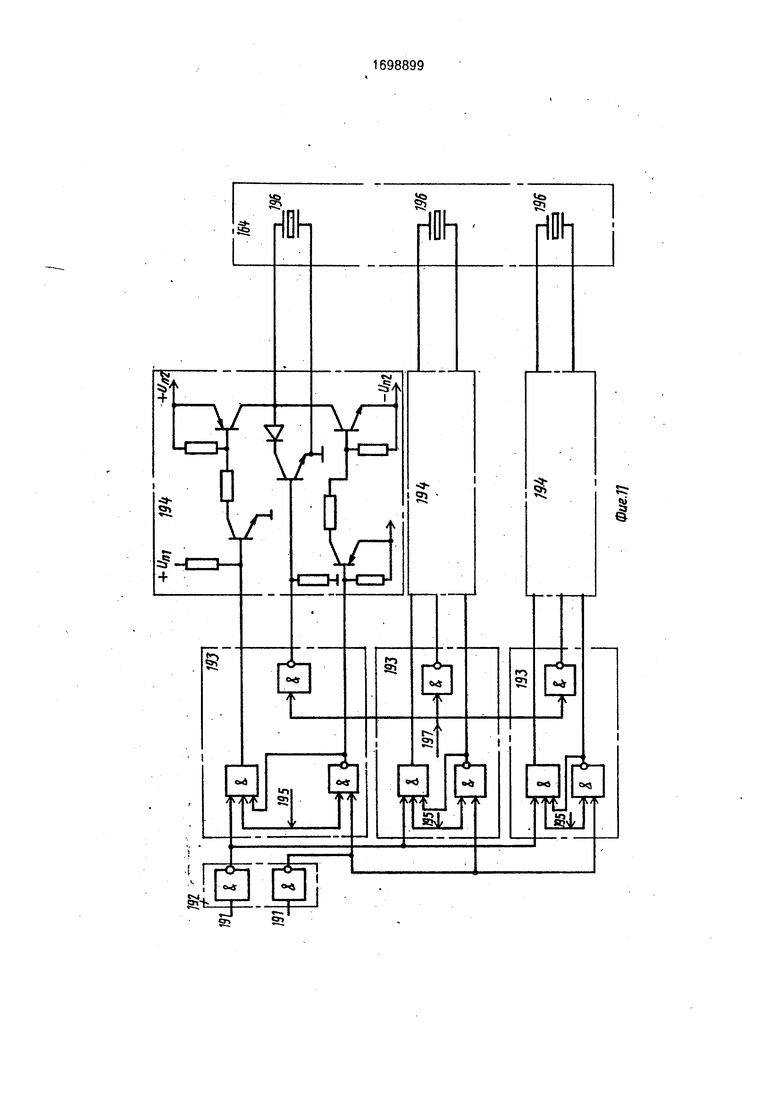

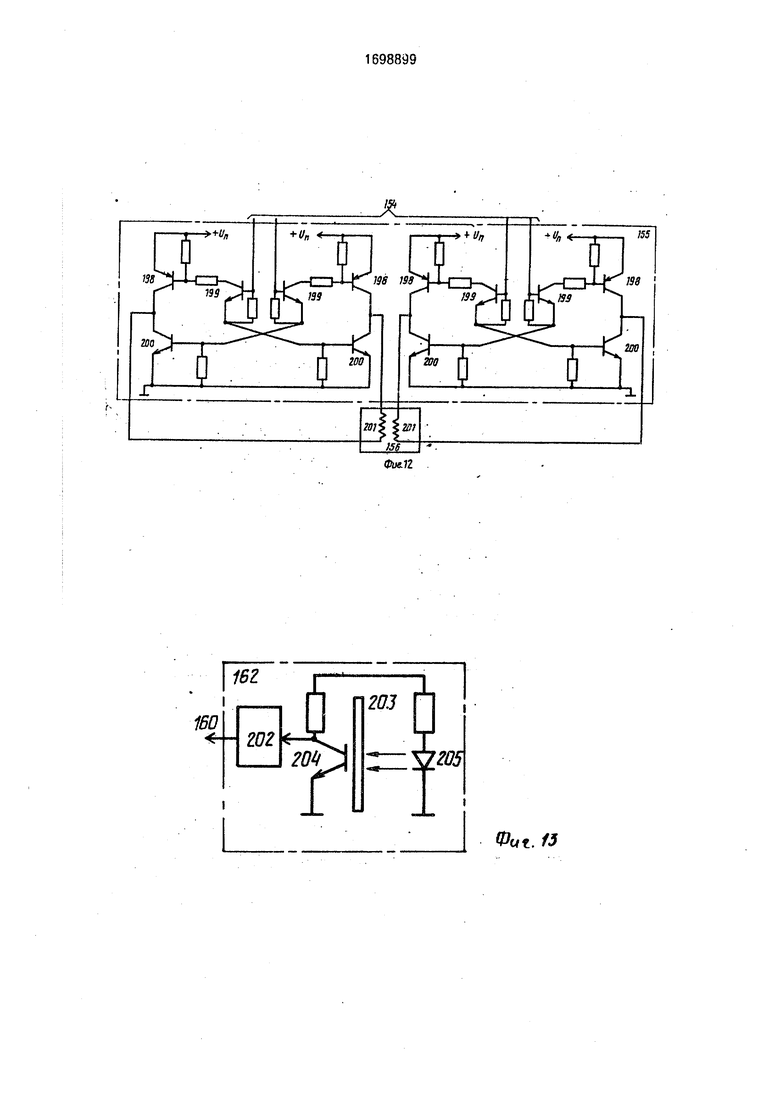

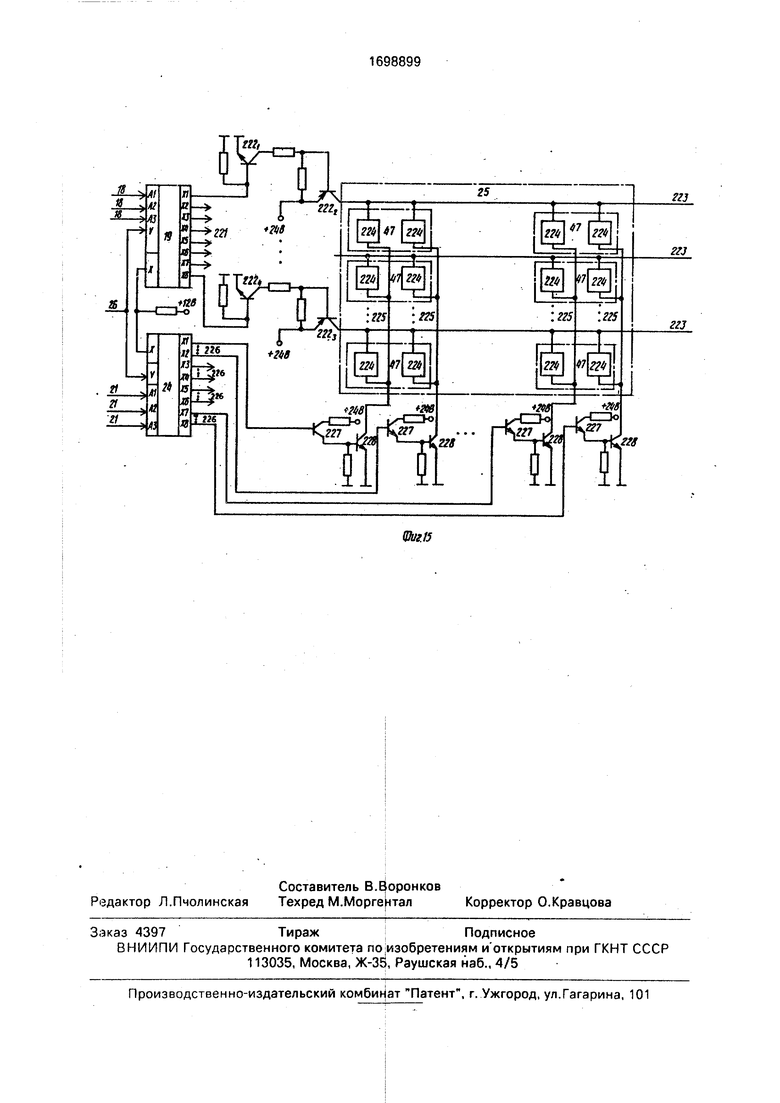

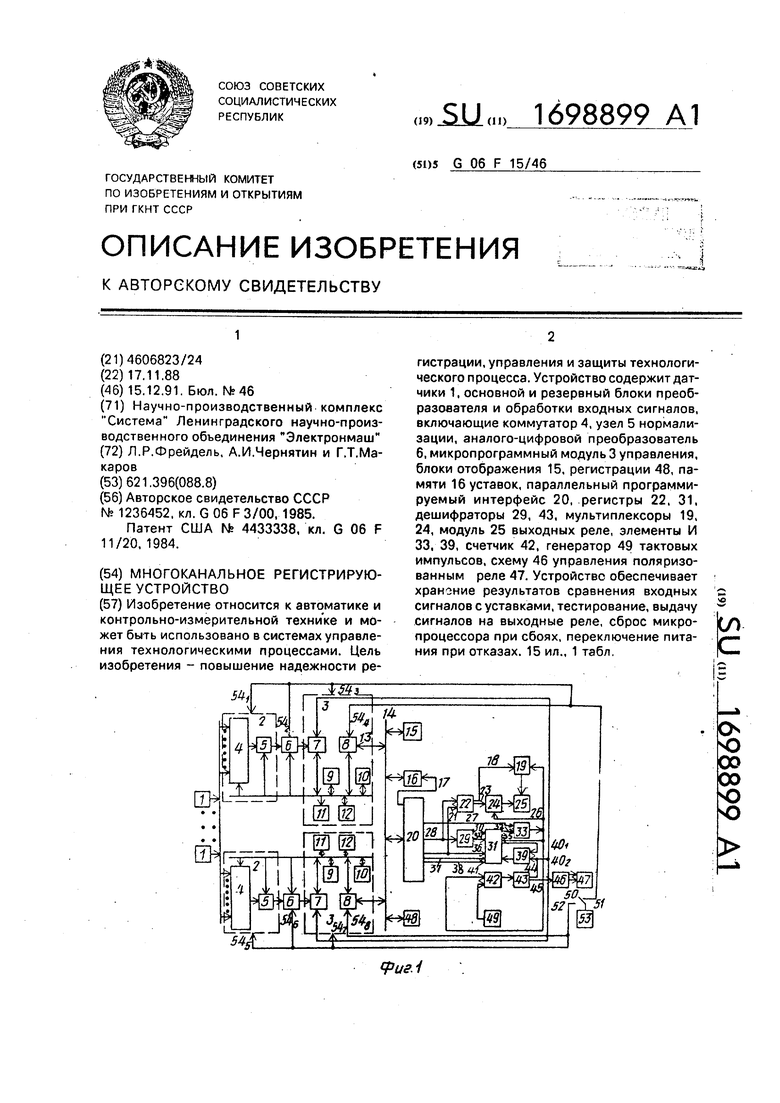

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - схема тестирования; на фиг. 3 - схема формирования сигналов Рестарт и переключения на резерв; на фиг. 4 - временные диаграммы работы устройства; на фиг. 5 - временные диаграммы выдачи результатов сравнения с уставками и контрольных байтов; на фиг. 6 - функционэльна схема микропроцессорного модуля управления; на фиг. 7 - схема аналоговой части прибора; на фиг. 8 - схема аналого-цифрового преобразователя; на фиг. 9 - структурная схема блока регистрации; на фиг. 10 - функциональная схема управления регистрацией; на фиг. 11 - схема управления узлом записи; на фиг. 12 и 13 - схемы управления шаговыми двигателями; на фиг. 14 - функциональная схема клавиатуры и индикации; на фиг. 15 - схема управления выходными реле.

Устройство содержит идентичные основной и резервный блоки преобразования и обработки входных аналоговых сигналов -от датчиков 1. Каждый из указанных блоков состоит из последовательно включенных аналогового модуля 2 и микропроцессорного модуля 3 управления. Аналоговый модуль 2 содержит последовательно соединенные коммутатор 4 и узел 5 нормализации, а также аналого-цифровой преобразователь 6. Модуль 3 образуют микропроцессор 7, шинный формирователь 8, контроллер 9 прерываний, интерфейс 10, узлы оперативной 11 и постоянной 12 памяти. Шины 13 адреса, данных исправления основного и резервного блоков соединены соответственно друг с другом и образуют общую магистраль 14, к которой подключены блок 15 отображения и блок 16 памяти уставок с входом 17.

На фиг. 1-15 обозначены: адресный вход 18 первого мультиплексора 19, параллельный программируемый интерфейс 20, управляющий вход 21 первого регистра 22, адресный вход 23 второго мультиплексора 24, модуль 25 выходных реле, управляющие входы 26 мультиплексоров, выходы 27 и 28 интерфейса 20, первый дешифратор 29 с

первым выходом 30, второй регистр 31 с выходом 32, первый элемент И 33, второй выход 34 первого дешифратора, управляющие входы 35-38 регистра 31, второй элемент И 39, соединительные шины 40 с микропроцессорами, вход сброса 41 счетчика 42, второй дешифратор 43 с выходами 44, 45, схема 46 управления поляризованным реле 47, блок 48 регистрации, генератор 49

тактовых импульсов, подвижный 50 и неподвижные 51 и 52 контакты поляризованного реле, источник 53 питания, входы 54 питания ряда узлов, элементы ИЛИ-НЕ 55, И-НЕ 56 и ИЛИ-НЕ 57, триггер 58, элементы ИЛИНЕ 59 и И-НЕ 61.триггер 62, элементы И-НЕ 63 и 64, триггеры 65-68, выход 69 триггера 68, элементы И-НЕ 70, ИЛИ-НЕ 71 и 72 и И-НЕ 73, триггер 74, транзисторы 75-78, блок 79 запуска микропроцессора, системный контроллер 80 с выходами 81-83, шина 84 данных, выходы 85 дешифратора 86, формирователь 87, внутренний регистр 88, внутренняя шина 89 адреса, входы 90 и 91 интерфейса 10, внутренний дешифратор 92, выход 93 элемента И 94 и его вход 95, внутренний шинный формирователь 96, элемент И 97, преобразователь 98 уровня, внутренняя ши-. на 99 данных, выходы 100 запросов, выходы 101 и 102 интерфейса 10, контакты 103 реле

104, транзисторы 105, распределитель 106 входных сигналов 107 коммутатора, усилитель 108 с выходом 109, выходы 110 триггеров 111 и 112, оптрон 113, элемент И 114, ключ 115, выходы 116 триггера 111, оптрон

117, ключ 118, регистр 119, элемент И 120, ключ 121, резистор 122, ключ 123, резистор 124, ключ 125, эталонный источник 126, од- новибратор 127. элемент И 128, оптрон 129, элементы И 130, 131, оптрон 132, вход 133

элемента И 128Чтаймер 134. оптрон 135, триггеры 136,137, входы 138 и 139 таймера, ключ 140, интегратор 141, резистор 142, конденсатор 143,компаратор 144,опорный источник 145, элемент И 146, триггеры 147

и 148 с выходами 149 и 150, входы-выходы 151, контроллер 152 блока регистра с дополнительными входом 153 и выходом 154, коммутатор 155 шагового двигателя 156 позиционирования, вход 157 схемы 158 управления блока регистрации, вход 159 и выход 160 коммутатора 161 шагового двигателя и датчика 162 положения, вход 163 узла 164 записи, второй датчик 165 положения, ось 166 узла записи, шаговый двигатель 167 лентопротяжного механизма, носитель 168, интерфейс 169 блока регистрации с шиной, 170, микроЭВМ 171 с выходом 172, регистр 173, оперативная память 174, расширитель 175, кварц 176, соединительные шины 177-179, выходы 180 расширигеля, выходы 181 и 182 микроЭВМ, шины 183, выходы микроЭВМ 184 и расширителя 185, выход 186 микроЭВМ, элементы И 187 и 188, выходы 189 расширителя, постоянная память 190, входы 191 элементов И 192 узла записи, логические схемы 193, транзисторные усилители 194 напряжения, входы 195 элементов И логических схем, пьезоэлемен- ты 196, входы 197 элементов И, транзисторы 198-200, обмотки 201 шагового двигателя, триггер Шмитта 202, элементы светодисда и транзистор 203-205, источник 206, ключи 207, входы 208 индикатора 209, источник 210 переменного напряжения, программируемый контроллер 211, дешиф- ратор212, вход 213 контроллера, дешифратор 214, входы 215 контроллера, клавиатура 216, выход 217 контроллера, клавиши 218, входы 219 контроллера, дешифратор 220, выходы 221 мультиплексора 19, транзисто- ры 222, выходы 223, реле 224 и связи 225 модуля 25, выходы 226 мультиплексора 24 и транзисторы 227 и 228.

Кодовые комбинации на шинах 18 и 21 при записи результатов сравнения с устав- ками в матрицу выходных реле для устройства с 32 измерительными каналами представлены в таблице,

Устройство работает следующим образом.

После заключения устройства в сеть питания в зависимости от исходного положения подвижного контакта поляризованного реле47 один из микропроцессорных блоков устройства переходит в рабочий режим, вто- рой в состояние холодного резерва.

Если до включения устройства в сеть были замкнуты контакты 50 и 51 реле 47, то микропроцессорный блок в верхней части на фиг. 1 по линиям 54 подключается к источнику питания 53 и переходит поэтому в рабочее состояние, а блок в нижней части на фиг. 1 остается отключенным от источника питания 53 и оказывается в состоянии холодного резерва.

Свойство поляризованного реле сохранять состояние контактов после отключения питания обеспечивает перевод в рабочий режим при очередном включении устройства в сеть именно того блока, который был в рабочем режиме до предшествующего отключения устройства от сети питания.

Одновременно с подключением источ- ника 53 питания к выводам питания одного из микропроцессорных блоков, напряже- ние источника 53 по линии 54 в виде сигнала с уровнем 1 подается на управляющий вход шинного формирователя 8, относящегося к перешедшему в рабочий режим блоку, в то время как на управляющем входе

шинного формирователя резервного блока устанавливается сигнал с уровнем О, благодаря чему выходные шины 13 рабочего блока подключаются к общей магистрали 14, а выходные шины 13 резервного блока переходят в третье состояние, отключая этот блок от магистрали 14.

Питание шинных формирователей 8 осуществляется от отдельного источника питания (не показан) независимо от положения контактов реле 47.

Сразу после включения устройства в сеть питания, кроме описанных процессов, с помощью схемы начальной установки (не показана) выдается единичный импульс на вход сброса счетчика 42, который переводит все выходные разряды счетчика в состояние О, а на выходах 44 и 40 дешифратора 43 возникают единичные импульсы, поступающие на входы сброса микропроцессоров 7.

После появления-импульса на входе сброса микропроцессора блока, находящегося в рабочем режиме, начинается циклическое выполнение функций устройства под управлением программы, записанной в узле 12 начиная с начального адреса, и одновременно с этим счетчик 42 начинает счет импульсов tr, поступающих на его счетный вход с выхода генератора 49 тактовых импульсов.

В каждом цикле выполнения функций устройства последовательно во времени производятся следующие программно-управляемые операции:

-последовательное подключение датчиков 1 с помощью коммутатора 4 к входу узла 5 нормализации с программно изменяемым коэффициентом усиления;

-последовательное преобразование усиленных сигналов датчиков 1 всех измерительных каналов в цифровые эквиваленты с помощью аналого-цифрового преобразователя 6;

-линеаризация сигналов нелинейных датчиков;

-самодиагностические операции; проверка аналоговой части блоков 11 и 12 и др.;

-выдачу данных в блоки 48 регистрации, отображения, индикации и клавиатуры 15;

-сравнение цифровых значений входных сигналов с установленными предельными значениями (уставками) в каждом измерительном канале;

-выдачу дискретных результатов сравнения с уставками и контрольных байтов соответственно в регистр 22 и на входы дешифратора 29 схемы тестирования.

Управление перечисленными операциями сбора, нормализации, аналого-цифрового преобразования данных, обработки данных (цифровая фильтрация, линеаризация, коррекция смещения нулевого уровня и коэффициента передачи аналоговой части), сравнения входных сигналов с уставками, самодиагностики, регистрации и цифровой индикации данных производится по известным процедурам, входящим в фонд программного обеспечения измерительной техники.

Программно-управляемый вывод контрольных байтов и результатов сравнения с уставками в схему тестирования производится в конце каждого цикла работы устройства через параллельный интерфейс 20.

До начала вывода указанных данных через интерфейс 20 под управлением программы формируются контрольные байты NTL Мт2.

Байт Nn образуется путем логического сложения двух байтов NTI и Mm (MrS - цифровой эквивалент входного эталонного сигнала постоянного напряжения U3T, Nm - результат выполнения самодиагностической программы проверки правильности функционирования узлов коммутации, нормализации и др.).

При нормальном функционировании устройства дожно выполняться условие:

Мп Мэт1 N3T + N3T,

где N3r - номинальное цифровое значение эталонного сигнала;

N3T - результат выполнения программы самодиагностики при отсутствии нарушений в работе контролируемых узлов.

Для представленных на фиг. 2, 3 -схем реализации узлов устройства NST 011110002, N3T 000000002 и, соответственно, МЭт1 011110002.

Байт NT2 формируется по результатам сравнения NTI с хранящимися в узле 12 зна- чениями эталонных уставок Мэт.уст.1 и МЭтуст2. Если выполняется условие N3T уст.1 NTI N3T уст.2. то в старшие и младшие разряды байта Ni2 записываются 1, в противном случае - О (во всех остальных разрядах постоянно записаны уровни О).

При нормальном функционировании устройства должно выполняться условие:

NT2 N3T.2.

где N3T.2 100000012.

Вывод байтов результатов сравнения с уставками и контрольных байтов производится через интерфейс 20 в режиме О следующим образом.

Сначала производится вывод из микропроцессорного блока в порт А интерфейса 20 полученного ранее 8-разрядного слова (байта), где в одном из разрядов записан дискретный результат (1 или О) сравнения входного сигнала 1-го канала с уставкой, относящейся к этому каналу, а остальные разряды содержат адрес канала 1 для последующей записи указанного дискретного результата в соответствующее реле матрицы модуля 25.

До записи в матрицу реле байты результата сравнения предварительно записываются по шине 28 в регистр 22 путем выдачи,

0 сразу же после вывода байта результата сравнения с уставками, сигнала сопровождения с уровнем Г через разряд С4 порта С на управляющий вход 21 регистра 22, в котором записанная информация хранится

5 до передачи ее в матрицу выходных реле.

Сигнал сопровождения с выхода разряда С4 поступает также на управляющий вход 37 регистра 31, подготавливая последний к приему контрольных байтов NTI, Ni2.

0 После записи байта результата сравнения в регистр 22 производится поочередный вывод в разряды 28 порта А контрольных байтов NTI, Ni2.

Сравнение NTI, Мт2 с эталонными зна5 чениями МЭт.1, МЭт.2, соответственно производится с помощью дешифратора 29 и регистра 31.

Контрольный байт NTI с выходов 28 (АО- А7) порта А интерфейса 20 поступает на

0 входы дешифратора 29.

Схема дешифратора 29 построена таким образом, что на его выходах 30 и 34 сигналы с уровнем 1 возникают только тогда, когда на вход дешифратора поступа5 ют коды, совпадающие во всех разрядах с NST.I и N3T.2 соответственно.

При равенстве NTI NST i на выходе 30 дешифратора возникает сигнал 1, записываемый затем в регистр 31 по переднему

0 фронту сигнала сопровождения, поступающего на вход 37 управления регистра 31.

Сигнал сопровождения выдается микропроцессорным блоком путем установки уровня 1 на выходе разряда С5 интерфей5 са 20 сразу после установления байта NTI на выходах 28 порта А.

После записи результата сравнения 1Мц с Ыэт.1 в регистр 31 аналогично осуществляется вывод второго контрольного байта Мт2

0 и сравнение его с эталонным значением N3T.2. Запись результата сравнения Мт2 с Мэт.2. определяемого уровнем сигнала 34 на выходе дешифратора 29, в регистр 31 производится передним фронтом единичного

5 сигнала сопровождения, поступающего с выхода разряда Сб на управляющий вход 38 регистра.31. В случае совпадения кодов NTL Мт2 с эталонными кодами МЭт.1 и N3r.2 на выходах 30 и 34 дешифратора 29 соответст- венно возникает сигнал с уровнем 1, разрешающий запись результатов сравнения с устапками 1-го канала из регистра 22 в матрицу выходньж реле модуля 25.

Для записи результата сравнения в матрицу выходных реле модуля 25 микропроцессор в течение 30 мс выставляет единичный импульсный сигнал на выходе 27 разряда С7 интерфейса 20. Одновременное поступление сигналов с уровнем 1 по линиям 32 и 27 на входы элемента И 33, приводит к возникновению единичного импульса на выходе элемента 33, который, поступая на управляющие входы мультиплексоров 19 и 24 обеспечивает передачу результата сравнения с уставками, хранящегося в регистре 22, через мультиплексоры 19 и 24 в матрицу реле модуля 25 по адресу 1-го канала.

Сигнал с выхода элемента 33 поступает также на управляющий вход 35 регистра 31 и на вход сброса 41 счетчика 42. что приводит к сбросу регистра 31 в исходное состояние через элемент И 39 и сбросу в исходное состояние счетчика 42, который после прохождения импульса сброса, вновь начинает счет импульсов, поступающих на его вход с генератора 49.

После записи результатов сравнения с уставками 1-го канала и тестирования работы процессорной части путем сравнения контрольных байтов с эталонными, аналогично производится тестирование и запись результатов сравнения с уставками 2-го канала, затем 3-го и т.д. до последнего по номеру канала, т.е. до окончания записи результатов сравнения с уставками сигналов всех подключенных к прибору датчиков.

Временные диаграммы процессов вывода результатов сравнения с уставками и контрольных байтов представлены на фиг.5.

После записи всех результатов сравнения с уставками начинается новый следующий цикл выполнения Функций устройства.

В случае кратковременного самовосстанавливаемого нарушения (сбоя) нормальной работы устройства, например, в результате воздействия разного рода помех на масштабирующий усилитель, или преобразователь 6, преобразование эталонного сигнала в контрольный байт NTI производится с ошибкой, в результате чего содержимое NTI уже не не совпадает с содержимым эталонного байта NST.I.

Различного рода аппаратные и программные сбои, возникающие при подготовке к передаче контрольных байтов NTI и Мт2. искажают их содержимое, что также приводит к несовпадению Мп и Ni2 с NST.I и N3r.2 соответственно.

Отказы, возникающие при выполнении процедур математической обработки данных (цифровая фильтрация, линеаризация, коррекция нулевого уровня и коэффициента передачи аналого-цифровой части и др.) в связи с воздействием помех на память или в связи с ошибками оператора при распределении и идентификации датчиков по измерительным каналам, выявляются и

индицируются на цифровом индикаторе устройства программой самодиагностики, которая формирует результат диагностирования в виде байта Nm, теперь уже отличного от его значения N3i 000000002, выдаваемого при нормальной работе.

В результате логического суммирования байта Nm с NTI образуется байт NTL отличающийся от МЭт.1.

Несовпадение хотя бы одного из контрольных байтов Nn или NT2 с соответствующим эталонным кодом или появление ошибки при выдаче сигналов сопровождения С4-С7 приводит к тому, что на одном или обоих выходах 30 и 34 дешифратора 29

при выводе контрольных байтов остаются сигналы с уровнем О, в результате чего на выходе 32 регистра 31 также остается О, и импульс записи результатов тестирования, выдаваемый из интерфейса 20 по линии 27,

не проходит через закрытый элемент И 33 на входы управления мультиплексоров 19 и 24 и не поступает на вход сброса счетчика 42.

Поэтому в случае сбоя или отказа микропроцессорного блока результат сравнения с уставками в выходные реле модуля 25 не записывается, что предотвращает возможность выдачи ложных управляющих сигналов на внешние устройства, а счетчик 42

не сбрасыватся и продолжает счет импульсов,поступающих с выхода генератора 49.

Как только на выходах счетчика появляется заданноее число NЈ, происходит пре- образование этого числа дешифратором 43

в сигналы с уровнем выходах 44 и 45 дешифратора, причем длительность действия этих сигналов определяется периодом тактовой частоты генератора 49.

Появление сигнала 15, поступающего

на вход схемы 46 вызывает срабатывание поляризованного реле 47, средний контакт 50 которого размыкается с контактом 51 и замыкается с контактом 52, в результате чего напряжение питания источника 53 отключается от находившегося в рабочем со стоянии микропроцессорного блока и

подключается к блоку, бывшему в резерве,

который переходит в рабочий режим, тогда

как отказавший блок в результате отключения питания переходит из рабочего режима в состояние холодного резерва.

В тот же момент времени выходной сигнал источника 53 по линии 54 переводит выходные линии 13 шинного формировате- ля 8, находившегося в резерве блока, в рабочее состояние, а выходы шинного формирователя ранее работающего блока переходят в 3-е состояние, что позволяет вновь вступившему в работу микропроцес- сорному блоку осуществлять прием-передачу информации от модулей регистрации, индикации и клавиатуры через магистраль 14.

Возникающий одновременно с сигна- лом 45 сигнал 44 через элемент И 39 устанавливает регистр 31 в исходное состояние и, поступая по линии 40 на вход сброса микропроцессора 7, обусловливает переход к выполнению очередного цикла программ- но управляемых функций устройства начиная с начального адреса программы, хранимой в памяти блока, перешедшего в рабочий режим.

В дальнейшем функционирование уст- ройства под управлением блока, перешедшего из резерва в рабочий режим, производится так же, как было описано ранее, но с переходом от контроля схемой тестирования ранее работающего блока к контролю блока, перешедшего в рабочее состояние.

В связи с тем, что вероятность появления аппаратных и программных сбоев значительно выше вероятности отказов, в схеме тестирования предусматривается пе- . реключение на резерв не сразу после появления первого нарушения нормальной работы устройства, а только тогда, когда случаи нарушения повторяются в несколь- ких следующих друг за другом циклах выполнения функций устройства.

Для реализации функции переключения на резерв только в случае многократно повторяющихся нарушений нормальной рабо- ты, которые в отличие от одиночно встречающихся сбоев классифицируются как отказ ы, на выходе счетчика 42 для управления состоянием выходов 44 и 45 дешифратора 43 используются две группы разрядов, от 1-го до n-го и от 1-го до т-го разряда соответственно, причем m п.

Схема дешифратора 43 построена таким образом, что сигнал с уровнем 1 на выходе 44 дешифратора возникает всякий раз, когда все разряды от 1-го до n-го счетчика 42 переходят в состояние Г, а одновременная выдача логических единичных сигналов на выходах 44 и 45 происходит

только при установлении уровней 1 на всех разрядах счетчика от 1-го до т-го.

Установление уровня 1 на выходе каждого разряда от 1-го до n-го счетчика 42 происходит циклически с периодом

Т п -т- ч Тт

где fT - тактовая частота генератора 49.

Значение Тп выбирается из условия Тп- 1,5Тц, где Тц-средняя длительность цикла выполнения функций устройства.

Если при тестировании работающего блока фиксируется нарушение нормальной работы устройства, то счетчик 42 не сбрасывается. Поэтому по окончании цикла работы Тц счетчик 42 продолжает счет импульсов до момента окончания интервала Тп, когда на всех разрядах счетчика от 1-го до n-го устанавливаются уровни Ти, как следствие, на выходе 44 дешифратора 43 возникает сигнал Рестарт с уровнем 1, который, поступая на вход сброса микропроцессора 7 работающего блока, осуществляет переход микропроцессора к выполнению цикла функций с начального адреса управляющей программы.

В связи с тем, что в рассматриваемый, момент времени единичного сигнала на выходе 45 дешифратора 43 не возникает, пере- ключения на резервный блок не происходит.

Сигнал 44 переводит в исходное состояние регистр 31, что обеспечивает подготовку последнего к очередному тестированию микропроцессорного блока.

Если ошибка в работе устройства была случайной, т.е. имел место программный или аппаратный сбой, то при очередном тестировании контрольные байты совпадают с эталонными и схема контроля разрешает прохождение выходного сигнала 27 микропроцессорного блока, что приводит к сбросу счетчика 42.

В противном случае, через следующий интервал времени Тп происходит выдача по линии 44 следующего сигнала Рестарт и т.д. до момента времени, когда одновременно с выдачей на линию 44 сигнала Рестарт на выходе 45 дешифратора 43 возникнет также единичный сигнал, обеспечивающий переключение работающего блока на резервный.

Число сигналов R рестарта, следующих друг за другом до выдачи сигнала переключения на резерв, определяется соотношением:

2

R

,т

-1.

Например, при п 8, m 10, R 3, т.е. в этом случае подряд следуют 3 сигнала Рестарт, а сигнал переключения на резерв возникает одновременно с 4-м по счету сигналом Рестарт, который теперь уже обеспечивает переход к выполнению управляющей программы начального адреса вновь вступающего в работу микропроцессорного блока.

После переключения на резерв счетчик 42 продолжает счет импульсов до сброса при прохождении тестирования или до собственного переполнения, после которого происходит переход счетчика в исходное состояние и продолжение счета импульсов.

Временные диаграммы последовательности выполнения основных функций устройства, последовательность выдачи сигналов Рестарт и переключения на резерв представлены на фиг. 4.

Формула изобретен.и я Многоканальное регистрирующее устройство, содержащее группу датчиков, параллельный программируемый интерфейс, модуль выходных реле, блок памяти уставок, источник питания, блоки регистрации и отображения и основной и резервный блоки преобразования и обработки вторых аналоговых сигналов, каждый из которых включает коммутатор, узел нормализации, аналого-цифровой преобразователь и микропроцессорный модуль управления, содержащий микропроцессор, шинный формирователь, контроллер прерываний, интерфейс и узлы постоянной и оперативной памяти, выходами соединенные через шины адреса, данных и управления с управляющими входами коммутатора, узла нормализации и аналого-цифрового преобразователя, а выходами и входами - соответственно с управляющими входами и выходами микропроцессора, входами и выходами контроллера прерываний и интерфейса и первыми входами и выходами шинного формирователя, информационные входы каждого коммутатора связаны с выходами датчиков группы, а его выход - с информационным входом соответствующего узла нормализации, выход которого подключен к информационному входу соответствующего аналого-цифрового преобразователя, выход которого связан с информационным входом микропроцессора своего микропроцессорного модуля управления, вторые входы и выходы каждого шинного формирователя посредством общей магистрали соединены соответственное выходами и входами блоков регистрации и отображения, выходами и первыми входами блока памяти уставок и первыми выходами и входами параллельного программируемого интерфейса, вторые выходы которого подключены к вторым входам блока памяти уставок, отличающ е е с я тем, что, с целью повышения надежности устройства по регистрации, управлению и аварийной защите технологических процессов, в него введены два мульиплексора, два регистра, два дешифратора,,два элемента И. генератор тактовых импульсов, счетчик, поляризованное реле и схема управления поляризованным реле, выходы которой соединены с управляющими входами поляризованного реле, подвижный контакт которого связан с выходом источника питания, а неподвижные контакты подключены к входам питания узла нормализации аналого-цифрового преобразователя, шинного формирователя и

микропроцессорного модуля управления соответственно основного и резервного блоков преобразования и обработки входных аналоговых сигналов, выходы параллельного программируемого интерфейса с третьего по седьмой соединены с первым входом первого элемента И. информационным и управляющим входами первого регистра, первым и вторым входами разрешения записи, входом подготовки к приему информации

второго регистра и входом первого дешифратора, выходы которого связаны с информационными входами второго регистра, первый вход сброса которого подключен к выходу второго элемента И, а первый и второй выходы - к первому входу второго элемента И и второму входу первого элемента И, выход которого соединен с управляющими входами двух мультиплексоров, с входом сброса второго регистра и входом сброса

счетчика, счетный вход которого связан с выходом генератора тактовых импульсов, а выход - с входом второго дешифратора, первый выход которого подключен к входу схемы управления поляризованным реле, а

второй выход - к второму входу второго элемента И и входам сброса мультипроцессоров, выходы первого регистра соединены с адресными входами двух мультиплексоров, выходы которых связаны с входами модуля

выходных реле.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки микропроцессорной системы | 1987 |

|

SU1453408A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1741137A1 |

| МНОГОФУНКЦИОНАЛЬНОЕ ОТЛАДОЧНОЕ УСТРОЙСТВО ДЛЯ МИКРОПРОЦЕССОРНЫХ СИСТЕМ | 2016 |

|

RU2634197C1 |

| Устройство прерываний микропроцессорной системы | 1988 |

|

SU1621030A1 |

| МИКРОПРОЦЕССОР ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2042182C1 |

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1474650A2 |

| УСТРОЙСТВО КОНТРОЛЯ ПРОЧНОСТИ КРЫЛА ВОЗДУШНОГО СУДНА | 2011 |

|

RU2469289C1 |

| Многоканальное устройство для регистрации информации | 1984 |

|

SU1236452A1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Устройство для контроля микропроцессора | 1989 |

|

SU1693610A2 |

Изобретение относится к автоматике и контрольно-измерительной техни ке и может быть использовано в системах управления технологическими процессами. Цель изобретения - повышение надежности регистрации, управления и защиты технологического процесса. Устройство содержит датчики 1, основной и резервный блоки преобразователя и обработки входных сигналов, включающие коммутатор 4, узел 5 нормализации, аналого-цифровой преобразователь 6, микропрограммный модуль 3 управления, блоки отображения 15, регистрации 48, памяти 16 уставок, параллельный программируемый интерфейс 20, регистры 22, 31, дешифраторы 29, 43, мультиплексоры 19, 24, модуль 25 выходных реле, элементы И 33. 39, счетчик 42, генератор 49 тактовых импульсов, схему 46 управления поляризованным реле 47. Устройство обеспечивает хранение результатов сравнения входных сигналов с уставками, тестирование, выдачу сигналов на выходные реле, сброс микропроцессора при сбоях, переключение питания при отказах. 15 ил., 1 табл. сл с

НБ1

TJopj

103

и,

Ш

т

-iw

Упг

101

по

юг

О)

из со со со со

125$

Ј

W-4ZH

сгь-w4F

§

«xi

С 1СЭ

В

ь«

§

Я

tt

-шн

I

j

во

I

|

CZH.

шн

ь

Фи&З

«

§

g

riDh

Фиг. 13

ги,

| Многоканальное устройство для регистрации информации | 1984 |

|

SU1236452A1 |

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

| Патент США № 4433338 | |||

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-12-15—Публикация

1988-11-17—Подача