Настоящее изобретение относится к приемнику в узле шинной сети (шинном узле), прежде всего EIB-сети, подключаемому к шинной линии, которая предоставляет в распоряжение приемника образованный из битовых импульсов сигнал.

Шинные сети служат для того, чтобы связывать друг с другом в сеть способные к коммуникации приборы. Для этого эти приборы содержат шинный узел с передатчиком, приемником и, при необходимости, источник питания, который питает внутреннюю схему и возможно, при наличии, прикладные схемы.

Шинные узлы, которые должны использоваться в EIB-сети (European Installation Bus), должны удовлетворять строгим требованиям, которые установлены в «Konnex Handbuch, Version 2.0». На основании этих требований происходит сертификация готовых приборов. При этом для обеспечения различных свойств предписаны определенные испытания.

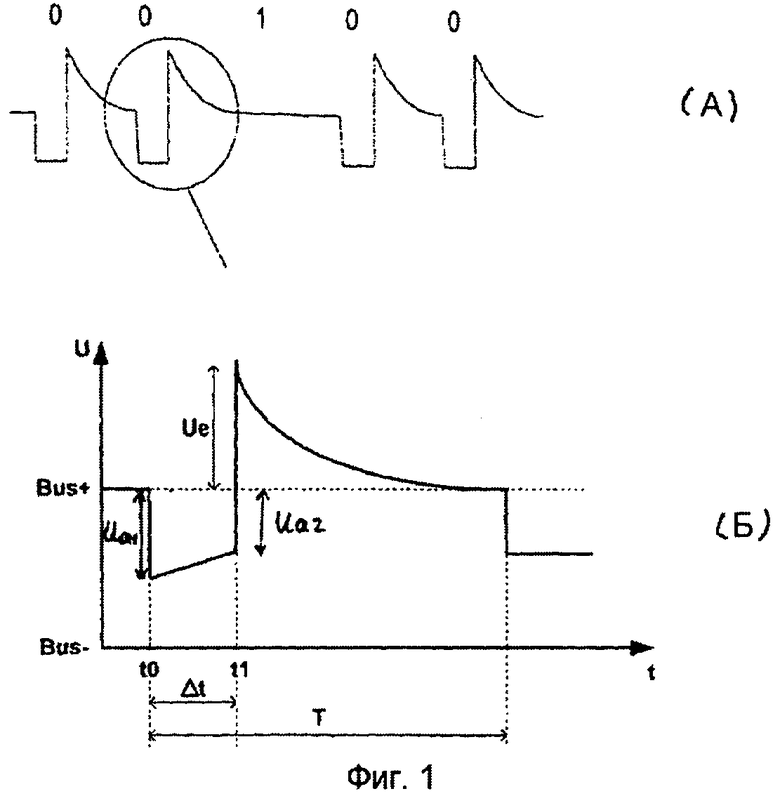

На фиг.1 на фрагменте (А) показана битовая последовательность из приведенной в качестве примера EIB-телеграммы, которая генерируется согласно последовательности импульсов передаваемого сигнала, на фрагменте (Б) показаны детали отдельного битового импульса. Bus+ является номинальным напряжением шины, Bus- представляет собой общий потенциал для дальнейшего рассмотрения, то есть потенциал массы. EIB-сигнал отдельного передаваемого импульса определяется от номинального напряжения Bus+ шины ограниченным во времени и синхронизируемым по длительности Δt с передаваемым сигналом, обозначенным через Ua1 и Ua2 падением напряжения, в общем называемым активным импульсом. С целью минимизации энергии при отправлении сообщения затем происходит определенное превышение напряжения Ue выше номинального напряжения Bus+ шины, которое начинает так называемый уравнивающий импульс. При взаимодействии с дроссельным модулем как преобразователем напряжения деталей шинной сети, который при этом одновременно представляет собой накопитель энергии, после каждого активного сигнала (передаваемого импульса) происходит обратная подача энергии на шинную линию. После этого выравнивающий импульс затухает как экспоненциальная функция, пока после истечения битового периода Т не появится следующий бит телеграммы. Тогда уравнивающий импульс должен полностью затухнуть, чтобы были обеспечены определенные условия напряжения для следующего бита. «Konnex Handbuch, Version 2.0» определяет, например, также границы допусков, которые должны соблюдать значения напряжения в различных условиях.

В зависимости от конфигурации шины, длины проводов, числа подключенных к шине приборов и эффективной величины постоянного напряжения шины, сигнал напряжения передатчика затухает и при определенных обстоятельствах приходит к приемнику с очень малой амплитудой. Однако полезный сигнал должен иметь заметное отношение сигнал/помеха для помех паразитной связи, а также шумов шинной линии. Кроме того, из сигнала должны отфильтровываться накладывающиеся высокочастотные составляющие паразитной связи.

С другой стороны, приемник не должен перегружаться, так как перегрузка может привести к такой деформации сигнала, что он уже не будет опознан как полезный сигнал. Высокие уровни сигнала возникают, например, когда на шинной линии расположены близко друг к другу два прибора, при этом один передает, а другой принимает, при малом числе приборов на шинной линии и дополнительно высоком постоянном напряжении шины. Поэтому, чтобы предотвратить перегрузку, сигналы не должны превышать верхнего порогового значения границ рабочих допусков.

Тем самым также определен динамический диапазон напряжения приемника. При этом для приемника в EIB-сети имеют силу величины из нижеприведенной таблицы. Приведены значения напряжения, при которых приемник должен передавать или запирать сигнал напряжения для оценки устройством управления, чем устанавливается нижнее пороговое значение для границ рабочих допусков.

В « Konnex Handbuch, Version 2.0, Volume 8: KNX System Conformance Testing, Part 2: Medium Dependant Layers Test, Chapter 2: TPI Physical and Link Layer,. Test 5.2 - Sensitivity» описан способ измерения, с помощью которого могут быть проверены требуемые свойства приемника. При этом должны быть достигнуты значения напряжения, приведенные в таблице, чтобы была возможной сертификация испытанного EIB-приемника.

Приемник с дифференциальным усилителем, который имеет первый вход и второй вход и по меньшей мере один выход, при этом к первому входу приложено опорное напряжение, а ко второму входу приложено несущее сигнал напряжение, которое рассчитано так, что сигнал на выходе появляется лишь тогда, когда абсолютное значение напряжения на втором входе больше, чем абсолютное значение опорного напряжения на первом входе, известен из US 5,689,199. Описанный там, построенный по биполярной технологии дифференциальный усилитель действует как компаратор с гистерезисом, который может быть сформирован за счет того, что сигнал напряжения пропорционально выходному сигналу источника тока подается обратно на потенциальный вход дифференциального усилителя, предпочтительно на вход дифференциального усилителя, к которому приложено опорное напряжение. Предпочтительно, дифференциальный усилитель может быть выполнен в виде схемы токового зеркала.

Для таких схем обратной связи известно, например из ЕР 0736975, использовать большие номиналы сопротивления для того, чтобы предотвратить, что схема имеет нежелательно малое сопротивление. Описанная в качестве уровня техники в ЕР 0736975 А1 схема использует сопротивление обратной связи в 1 МОм.

Задачей изобретения является разработка вышеописанного приемника так, что он является оптимизированным в отношении чувствительности, динамики и помехозащищенности. Также он должен быть выполнен устойчивым к перегрузке, при этом одновременно должно быть возможным приведение выходного уровня в соответствие с допустимым входным напряжением подключенного управляющего устройства, например микропроцессора.

Эта задача решена посредством приемника по п.1 формулы изобретения. Предпочтительные варианты осуществления являются предметом зависимых пунктов. Вариант применения предлагаемого в изобретении приемника приведен в п. 6 формулы изобретения.

Предлагаемый в изобретении приемник подключен к источнику напряжения, выдающему несущее сигнал напряжение, из которого отводится опорное напряжение. Так обеспечивается, что несущее сигнал напряжение всегда находится в определенном отношении к опорному напряжению, при этом последнее следует выбирать в зависимости от глубины сигнала (Ua1, Ua2, см. фиг. 1).

Кроме того, в соответствии с изобретением для обеспечения стабильности в поведении схемы приемника предусмотрено сопротивление обратной связи, которое соединяет выход с первым входом. Тем самым схеме придаются выгодные свойства триггера Шмитта.

Технические результаты, достигаемые при осуществлении изобретения, заключаются, в частности, в уменьшении относительных колебаний напряжения на входах дифференциального усилителя, обеспечиваемом получением опорного напряжения и несущего сигнал напряжения от одного источника напряжения, а также в уменьшении сопротивления обратной связи, потребного для создания гистерезиса, стабилизирующего режим работы дифференциального усилителя, без ухудшения чувствительности и динамических характеристик последнего.

Изобретение придает дифференциальному усилителю функцию компаратора, которая устраняет зависимость, например, от напряжения база-эмиттер транзистора, которая используется в уровне техники для того, чтобы соблюдать нижнее пороговое значение для границ рабочих допусков.

Предпочтительно, дифференциальный усилитель состоит, по меньшей мере, из первого транзистора и второго транзистора в схеме с общим эмиттером с общим сопротивлением эмиттера, при этом база первого транзистора образует второй вход, а база второго транзистора - первый вход дифференциального усилителя. При этом выполнении первый вход можно было бы рассматривать в качестве положительного входа компаратора, к которому приложено опорное напряжение. Второй вход можно было бы рассматривать как отрицательный вход компаратора, к которому приложен приходящий сигнал. Таким образом, опорное напряжение задает нижнее пороговое значение для границ рабочих допусков согласно таблице.

Далее, предпочтительно, предусмотрено, что коллектор первого транзистора образует выход.

Согласно одному предпочтительному варианту осуществления изобретения дифференциальный усилитель имеет токовое зеркало, вход которого соединен с коллектором второго транзистора, и выход которого соединен с коллектором первого транзистора. С помощью этой меры создается противодействие перегрузке, так как здесь определяется пороговое значение для верхней границы рабочих допусков, которые не должны превышаться по схемотехническим причинам.

Наконец, объектом изобретения является применение приемника по одному из пп. 1-5 формулы в специализированной интегральной схеме (ASIC - Application Specific Integrated Circuit), которая может включать в себя также дополнительные элементы схемы, например передатчик, источник напряжения, сетевой блок питания и тому подобное.

Ниже изобретение будет более подробно описано с использованием прилагаемых чертежей.

Фиг. 1: на фрагменте (А) показана битовая последовательность из приведенной в качестве примера EIB-телеграммы, а на фрагменте (Б) - детали битового импульса из битовой последовательности.

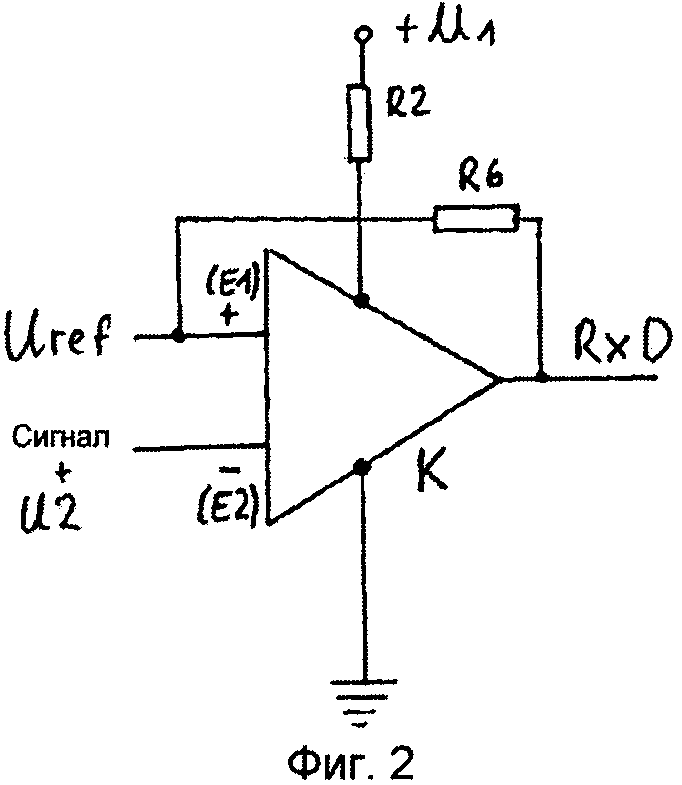

Фиг. 2: показана эквивалентная схема приемника согласно настоящему изобретению.

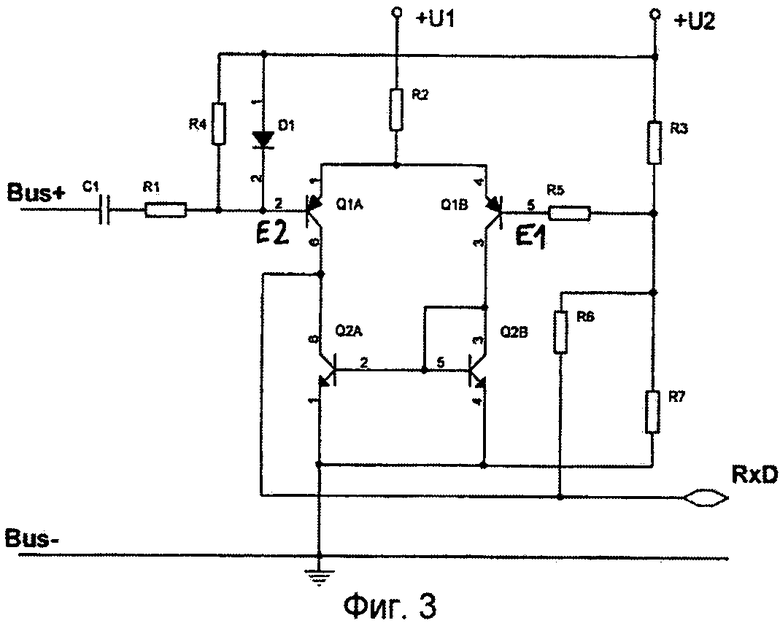

Фиг. 3: пример осуществления приемника согласно настоящему изобретению в дискретном выполнении.

В нижеследующем описании и на чертежах описаны многочисленные определенные подробности. Однако понятно, что формы осуществления настоящего изобретения могут применяться на практике без этих определенных подробностей. Для того чтобы не усложнять понимание изобретения, хорошо известные схемы, структуры и способы в других случаях опущены. Понятно, что в представленных вариантах осуществления могут быть предприняты многочисленные модификации и изменения без выхода за рамки изобретения. Поэтому представленные примеры осуществления должны рассматриваться как описательные, а не как ограничительные. Прежде всего, понятно, что, хотя пример осуществления выполнен с биполярными транзисторами, могут быть использованы другие технологии, так что схема, например, могла бы быть реализована с полевыми транзисторами.

На фиг. 2 показана эквивалентная схема для приемника согласно настоящему изобретению, с помощью которой будет разъяснена функциональность компаратора. Компаратор К питается напряжением U1, которое установлено более высоким, чем все другие имеющиеся в схеме напряжения. К первому входу компаратора К, который соответствует первому входу Е1 дифференциального усилителя, приложено опорное напряжение Uref, которое образует нижнее пороговое значение для границ рабочих допусков. Это опорное напряжение Uref, как еще будет описано в связи с фиг. 3, отводится из, предпочтительно, стабилизированного напряжения питания U2. Это напряжение U2 несет также сигнал, который отфильтровывается из шинной линии, прежде всего Bus+, и прикладывается вместе с сигналом к отрицательному входу компаратора К, который соответствует второму входу Е2 дифференциального усилителя. Компаратор К сравнивает напряжения на своем положительном и отрицательном входе и соответственно выдает на своем выходе RxD выходной сигнал. Сопротивление R6 обратной связи, которое соединяет выход RxD компаратора с его положительным входом, стабилизирует характеристику компаратора.

На фиг. 3 показан вариант выполнения приемника согласно настоящему изобретению в дискретном выполнении. При этом по существу идентичные транзисторы Q1A и Q1B, которые с общим сопротивлением R2 эмиттера включены в схему с общим эмиттером, образуют собственно дифференциальный усилитель, который дополнен токовым зеркалом, образованным из транзисторов Q2A и Q2B. U1 является первым напряжением питания, которое питает дифференциальный усилитель с функцией компаратора, при этом сопротивление R2 служит для установки тока эмиттера. U2 является вторым напряжением питания, которое является стабилизированным и служит для точной установки требуемых пороговых значений для границ рабочих допусков. Путем задания напряжения U2 на базе транзистора Q1A или транзистора Q1B напряжение эмиттера, которое также является напряжением питания компаратора, регулируется на величину, дополнительную к напряжению участка база-эмиттер. База транзистора Q1A образует второй вход Е2 дифференциального усилителя, база транзистора Q1B - первый вход Е1 дифференциального усилителя.

На выходе RxD обработанный полезный сигнал передается устройству управления, например микропроцессору. Так как напряжение питания, как описано выше, снижено, то и сигнал приведен в соответствие с допустимым входным напряжением устройства управления.

Ко второму входу Е2 напряжение U2 приложено напрямую через сопротивление R4. К этому второму входу Е2 приложен также шинный сигнал, который посредством конденсатора С1, который обеспечивает развязку по постоянному напряжению, извлекается из напряжения Bus+ шины. Тем самым напряжение U2 служит в качестве несущего сигнал напряжения. Диод D1 предусмотрен для защиты второго входа Е2 от перенапряжения. Дополнительно, сопротивление R1 с входными емкостями транзистора Q1A и диода D1 образует фильтр для высокочастотных компонентов в приходящем сигнале.

Первый вход E1 через сопротивление R5 подключен к делителю напряжения, состоящему из сопротивлений R3 и R7, с которого снимается опорное напряжение Uref. Делитель напряжения R3, R7 рассчитан так, что это напряжения лежит немного ниже напряжения U2.

Сопротивление R6 подключено в качестве сопротивления образной связи между выходом RxD и первым входом Е1. Этим устанавливается легкий гистерезис, который обеспечивает стабильность поведения приемника.

Благодаря функциональности дифференциального усилителя транзистор Q1 в спокойном состоянии закрыт, транзистор Q2 - открыт. Выход RxD является низким.

Если теперь битовый сигнал имеет уровень внутри обоих пороговых значений для границ рабочих допусков согласно таблице, сигнал с входа Bus+ через конденсатор С1 и сопротивление R1 передается на вход Е2. Так как сигнал имеет отрицательную полярность, напряжение U2 снижается и превышает по абсолютной величине опорное напряжение Uref на входе Е1. Теперь транзистор Q1A открывается, транзистор Q2A закрывается. Выход RxD на время длительности битового сигнала является высоким.

Шинный сигнал с уровнем ниже нижнего порогового значения для границ рабочих допусков не вызывает никакого переключения в дифференциальном усилителе, так как он по абсолютной величине не превышает опорное напряжение Uref.

Шинный сигнал выше верхнего порогового значения для границ рабочих допусков не приводит к перегрузке, так как постоянный ток базы для транзистора Q2A из опорной ветви Q1B и Q2B препятствует увеличению тока в ветви Q1A и Q2A. Благодаря этому приходящий сигнал не искажается.

При оптимальном определении параметров сопротивлений R1, R4, делителя напряжения R3, R7 и сопротивления R6 обратной связи может быть достигнуто поведение приемника в отношении требуемой чувствительности, динамики и помехозащищенности.

Раскрытые в вышеприведенном описании, на чертежах, а также в пунктах формулы изобретения признаки изобретения могут как по отдельности, так и в любой комбинации быть существенными для осуществления изобретения.

Приемник в шинном узле шинной сети, прежде всего EIB-сети. Достигаемый технический результат - оптимизация в отношении чувствительности, динамики и помехозащищенности. Приемник в узле шинной сети подключен к шинной линии (Bus+, Bus-) для приема передаваемого по ней сигнала, состоящего из битовых импульсов, содержит дифференциальный усилитель, который имеет первый вход для опорного напряжения (Е1) и второй вход (Е2) для несущего сигнал напряжения, при этом сигнал на выходе появляется лишь тогда, когда абсолютное значение напряжения на втором входе больше, чем абсолютное значение опорного напряжения на первом входе, а между выходом и первым входом дифференциального усилителя включено сопротивление обратной связи. 2 н. и 4 з.п. ф-лы, 3 ил., 1 табл.

1. Приемник в узле шинной сети, подключаемый к шинной линии (Bus+, Bus-) для приема передаваемого по ней сигнала, состоящего из битовых импульсов, содержащий дифференциальный усилитель, имеющий первый вход (Е1) для опорного напряжения (Uref), второй вход (Е2) для несущего сигнал напряжения и по меньшей мере один выход (R×D), причем дифференциальный усилитель выполнен так, что сигнал на выходе (R×D) появляется лишь тогда, когда абсолютное значение напряжения на втором входе (Е2) больше, чем абсолютное значение опорного напряжения (Uref) на первом входе (Е1), отличающийся тем, что он подключен к источнику (+U2) напряжения, выдающему несущее сигнал напряжение, из которого отводится опорное напряжение (Uref), при этом между выходом (R×D) и первым входом (Е1) дифференциального усилителя включено сопротивление (R6) обратной связи.

2. Приемник по п.1, отличающийся тем, что дифференциальный усилитель собран по меньшей мере из первого транзистора (Q1A) и второго транзистора (Q1B) по схеме с общим эмиттером с общим сопротивлением (R2) эмиттера, при этом база первого транзистора (Q1А) образует второй вход (Е2), а база второго транзистора (Q1B) - первый вход (Е1) дифференциального усилителя.

3. Приемник по п.2, отличающийся тем, что коллектор первого транзистора (Q1A) образует выход (R×D).

4. Приемник по п.2, отличающийся тем, что дифференциальный усилитель имеет токовое зеркало (Q2A, Q2B), вход которого соединен с коллектором второго транзистора (Q1B), а выход которого соединен с коллектором первого транзистора (Q1A).

5. Приемник по одному из пп.1-4, отличающийся тем, что он предназначен для применения в узле сети EIB.

6. Применение приемника по одному из пп.1-5 в специализированной интегральной схеме.

| US 5689199 A , 18.11.1997, |

Авторы

Даты

2015-03-10—Публикация

2010-02-05—Подача