Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях, компараторах, работающих в широком диапазоне изменения напряжения питания).

Известны схемы классических дифференциальных усилителей (ДУ), реализованных на основе токового зеркала, включенного в цепь нагрузки входного параллельно-балансного каскада [1-3]. Для установления их статического режима, как правило, применяются транзисторные источники опорного тока в общей эмиттерной цепи входного параллельно-балансного каскада. Известны также схемы ДУ с активными нагрузками, в которых применяется параллельное включение эмиттерно-базовых переходов нескольких входных транзисторов [4-6].

Однако вышеуказанные схемотехнические решения становятся малоэффективными в аналоговых микросхемах с низковольтным питанием. Во-первых, классические транзисторные источники опорного тока (ИОТ) на современных интегральных транзисторах при миллиамперных токах эмиттера имеют сравнительно невысокое выходное сопротивление (15-30 кОм). Во-вторых, применение классических ИОТ отрицательно сказывается на допустимом диапазоне изменения входного синфазного сигнала Uсинф.max, которые «съедают» 0,6÷0,7 В от Uсинф.max.

С другой стороны, замена ИОТ на токостабилизирующий резистор R0 в большинстве случаев неприемлемо, так как невысокие значения R0 существенно ухудшают подавление помехи по питанию.

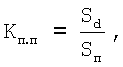

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель, описанный в патенте Японии JP 2003/110379, содержащий первый 1 и второй 2 входные транзисторы, объединенные базы которых связаны с первым 3 входом дифференциального усилителя, третий 4 и четвертый 5 входные транзисторы, объединенные базы которых связаны со вторым 6 входом дифференциального усилителя, токостабилизирующий двухполюсник 7, включенный между шиной источника питания 8 и объединенными эмиттерами первого 1, второго 2, третьего 4 и четвертого 5 входных транзисторов, первое 9 токовое зеркало, вход которого соединен с коллектором второго 2 входного транзистора, а выход подключен к коллектору четвертого 5 входного транзистора и выходу 10 дифференциального усилителя, второе 11 токовое зеркало, вход которого соединен с коллектором третьего 4 входного транзистора, а выход подключен к коллектору первого 1 входного транзистора.

Существенный недостаток известного ДУ состоит в том, что он имеет невысокий коэффициент подавления помехи по питанию.

Основная цель предлагаемого изобретения состоит в повышении коэффициента подавления помехи по питанию ДУ (Кпп). Причем высокие значения Кпп обеспечиваются при построении цепи стабилизации статического режима ДУ на основе сравнительно низкоомного резистора R0.

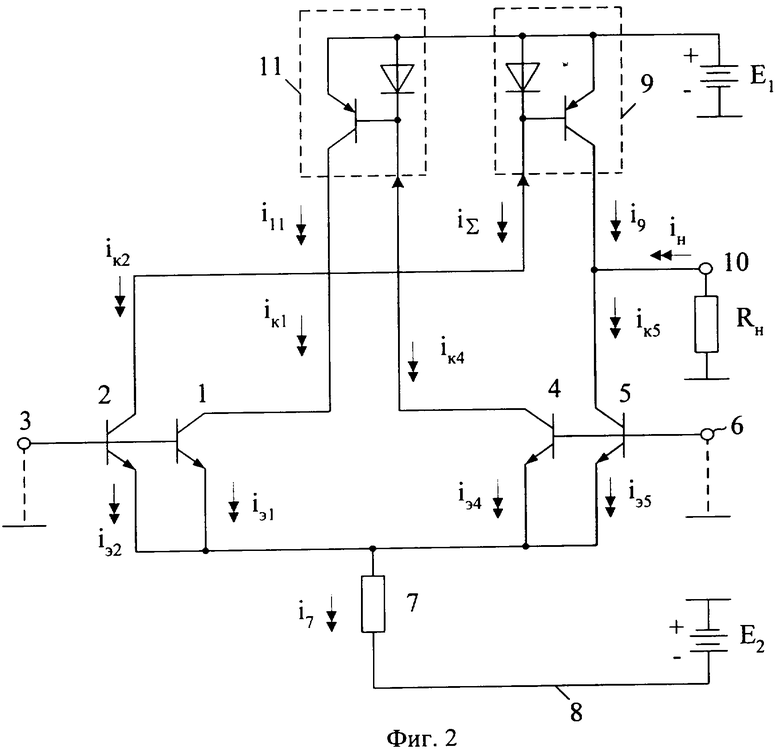

Поставленная цель достигается тем, что в дифференциальном усилителе фиг.1, содержащем первый 1 и второй 2 входные транзисторы, объединенные базы которых связаны с первым 3 входом дифференциального усилителя, третий 4 и четвертый 5 входные транзисторы, объединенные базы которых связаны со вторым 6 входом дифференциального усилителя, токостабилизирующий двухполюсник 7, включенный между шиной источника питания 8 и объединенными эмиттерами первого 1, второго 2, третьего 4 и четвертого 5 входных транзисторов, первое 9 токовое зеркало, вход которого соединен с коллектором второго 2 входного транзистора, а выход подключен к коллектору четвертого 5 входного транзистора и выходу 10 дифференциального усилителя, второе 11 токовое зеркало, вход которого соединен с коллектором третьего 4 входного транзистора, а выход подключен к коллектору первого 1 входного транзистора, предусмотрены новые элементы и связи - вход первого 9 токового зеркала соединен с выходом второго 11 токового зеркала.

Схема заявляемого устройства показана на фиг.2.

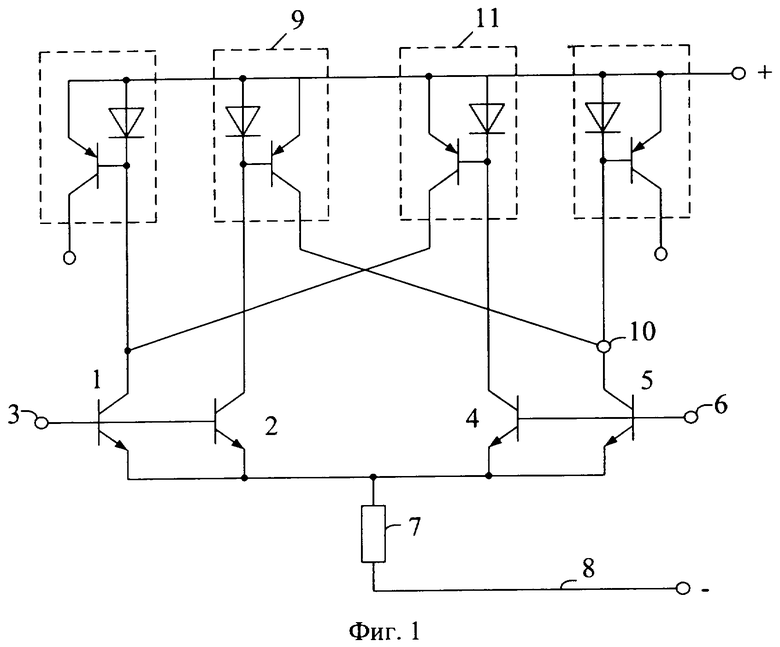

На фиг.3 показаны схемы заявляемого (верхний ряд) и известного (нижний ряд) ДУ в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

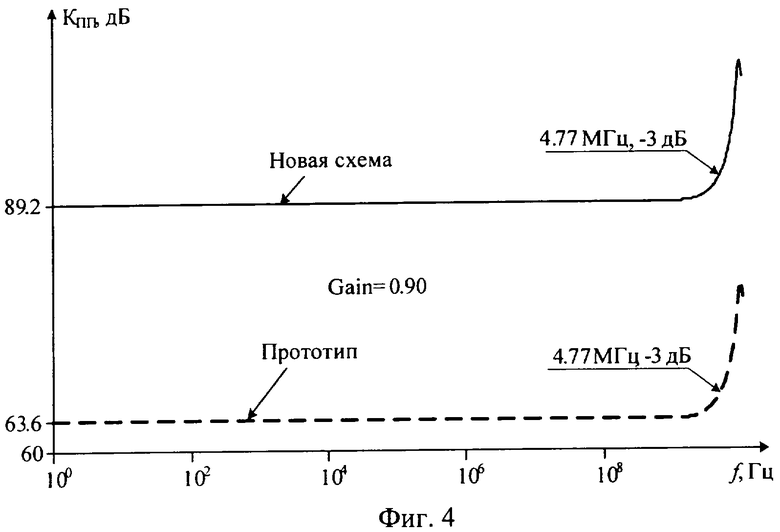

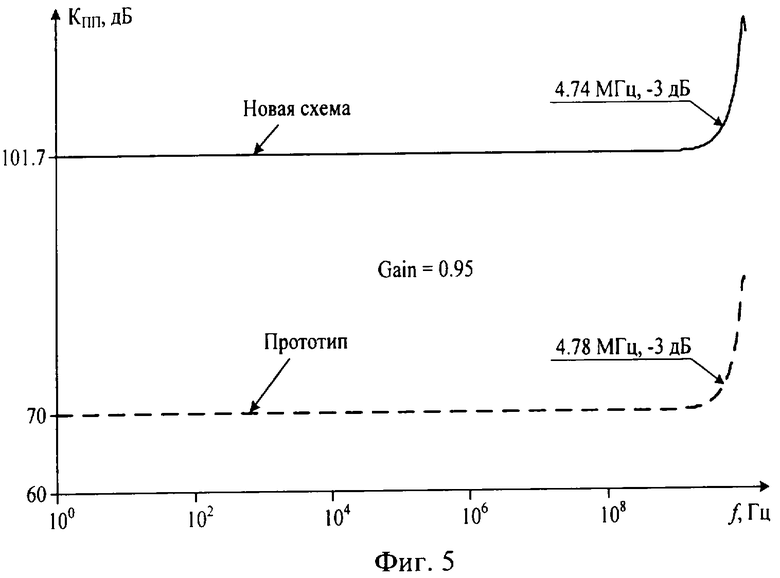

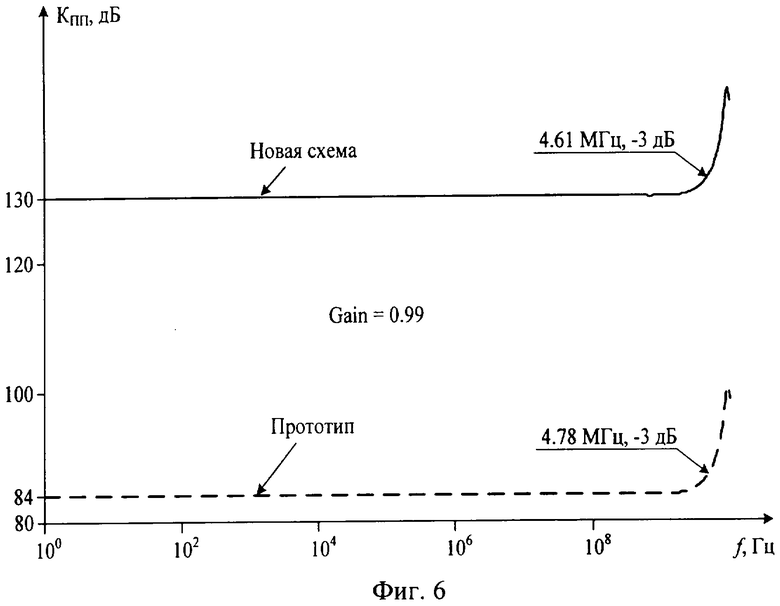

На фиг.4 - фиг.6 показана частотная зависимость коэффициента подавления помехи по питанию заявляемого (новая схема) и известного (прототип) ДУ при различных, но одинаковых значениях коэффициентов передачи по току токовых зеркал 11 и 9 (0,9; 0,95; 0,99).

Дифференциальный усилитель фиг.2 содержит первый 1 и второй 2 входные транзисторы, объединенные базы которых связаны с первым 3 входом дифференциального усилителя, третий 4 и четвертый 5 входные транзисторы, объединенные базы которых связаны со вторым 6 входом дифференциального усилителя, токостабилизирующий двухполюсник 7, включенный между шиной источника питания 8 и объединенными эмиттерами первого 1, второго 2, третьего 4 и четвертого 5 входных транзисторов, первое 9 токовое зеркало, вход которого соединен с коллектором второго 2 входного транзистора, а выход подключен к коллектору четвертого 5 входного транзистора и выходу 10 дифференциального усилителя, второе 11 токовое зеркало, вход которого соединен с коллектором третьего 4 входного транзистора, а выход подключен к коллектору первого 1 входного транзистора. Вход первого 9 токового зеркала соединен с выходом второго 11 токового зеркала.

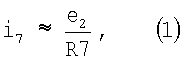

Рассмотрим работу заявляемого устройства фиг.2. Увеличение напряжения питания E2 на величину е2 приводит к увеличению тока через двухполюсник 7

где R7 - сопротивление двухполюсника 7.

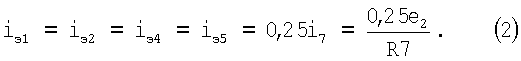

Ток i7 перераспределяется между эмиттерами транзисторов 1, 2, 3 и 4:

Поэтому коллекторные токи транзисторов 1, 2, 3; 4:

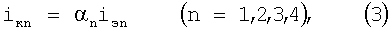

где αn≈1 - коэффициент усиления по току эмиттера n-го транзистора.

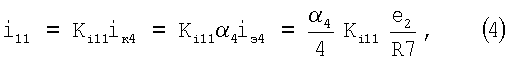

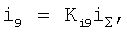

Выходные токи токовых зеркал 11 и 9 связаны с их входными токами через коэффициенты передачи по току Кi11≈1 и Кi9≈1

где iΣ=iк2+iк1-i11 - входной ток токового зеркала 9.

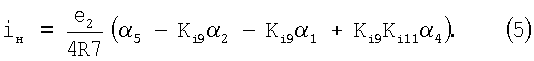

Таким образом, паразитный ток в нагрузке Rн, обусловленный изменением напряжения питания е2,

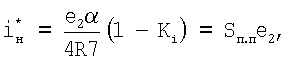

Если учесть, что элементы схемы имеют высокую идентичность (α5=α2=α1=α4≈α≈1, Кi9=Ki11=Ki≤1), то из последнего уравнения можно получить, что

где Sп.з - крутизна преобразования приращения напряжения питания е2 в паразитный ток нагрузки в заявляемом ДУ.

В усилителе-прототипе ток в нагрузке Rн, обусловленный изменением напряжения питания,

где Sп.п - крутизна преобразования приращения напряжения питания в ток нагрузки ДУ-прототипа.

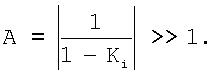

Таким образом, в предлагаемом усилителе существенно ослабляется влияние нестабильности напряжения питания е2 на паразитный ток в нагрузке. Причем крутизна преобразования е2 в iн в схеме фиг.2 в А раз меньше, чем в схеме фиг.1, где

Приращение тока iн, вызванное нестабильностью e2, можно преобразовать в соответствующее ему изменение ЭДС смещения нуля (есм) и соответствующий ему коэффициент подавления помехи по питанию (Кпп)

где Sd - крутизна преобразования дифференциального напряжения в выходной ток ДУ;

Sп - крутизна преобразования приращения напряжения питания в выходной ток ДУ.

Поэтому даже при одинаковых значениях крутизны Sd заявляемого и известного ДУ (Sd.з.=Sd.п) в схеме фиг.2 в А раз повышается коэффициент подавления помехи по питанию.

Полученные выше выводы подтверждаются результатами моделирования предлагаемой схемы в среде PSpice (фиг.4 - фиг.6). При коэффициентах передачи токовых зеркал 11 и 9 Gain=0,9 выигрыш по Кпп достигает 26 дБ. Если коэффициенты передачи токовых зеркал 11 и 9 имеют значение 0,95, то выигрыш по Кпп - 31,7 дБ. Если коэффициенты передачи по току токовых зеркал 11 и 9 принимают значения 0,99, то предлагаемое техническое решение увеличивает Кпп на 46 дБ, т.е. более чем в 100 раз.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Матавкин В.В. Быстродействующие операционные усилители [Текст] / В.В. Матавкин. - М.: Сов. Радио, 1989.

2. Операционные усилители с непосредственной связью каскадов [Текст] / В.И. Анисимов, М.В. Капитонов, Н.Н. Прокопенко, Ю.М. Соколов. - Л, 1979. - 148 с.

3. Полонников Д.Е. Операционные усилители: принципы построения, теория, схемотехника [Текст] / Д.Е. Полонников. - М., 1983. - 216 с.

4. Патент Японии JP 2003110379.

5. Патентная заявка США 2006/0215787.

6. Патент США № 5936465.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2010 |

|

RU2446555C2 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412530C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2432668C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2007 |

|

RU2331966C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С НИЗКОВОЛЬТНЫМ ПИТАНИЕМ | 2006 |

|

RU2319288C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2011 |

|

RU2441316C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2011 |

|

RU2449464C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412529C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С НИЗКОВОЛЬТНЫМ ПИТАНИЕМ | 2006 |

|

RU2310268C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ВХОДНЫМ СОПРОТИВЛЕНИЕМ | 2008 |

|

RU2368067C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ), компараторах). Технический результат заключается в повышении коэффициента подавления помехи по питанию. Дифференциальный усилитель (ДУ) содержит первый (1) и второй (2) входные транзисторы (Т), объединенные базы которых связаны с первым (3) входом ДУ, третий (4) и четвертый (5) входные Т, объединенные базы которых связаны со вторым (6) входом ДУ, токостабилизирующий двухполюсник (7), включенный между шиной источника питания (8) и объединенными эмиттерами Т (1, 2, 4 и 5), первое (9) токовое зеркало (ТЗ), вход которого соединен с коллектором второго Т (2), а выход подключен к коллектору четвертого Т (5) и выходу (10) ДУ, второе ТЗ (11), вход которого соединен с коллектором третьего Т (4), а выход подключен к коллектору первого Т (1). Вход первого ТЗ (9) соединен с выходом второго ТЗ (11). 6 ил.

Дифференциальный усилитель с повышенным ослаблением помехи по питанию, содержащий первый (1) и второй (2) входные транзисторы, объединенные базы которых связаны с первым входом (3) дифференциального усилителя, третий (4) и четвертый (5) входные транзисторы, объединенные базы которых связаны со вторым входом (6) дифференциального усилителя, токостабилизирующий двухполюсник (7), включенный между шиной источника питания (8) и объединенными эмиттерами первого (1), второго (2), третьего (4) и четвертого (5) входных транзисторов, первое токовое зеркало (9), вход которого соединен с коллектором второго входного транзистора (2), а выход подключен к коллектору четвертого входного транзистора (5) и выходу (10) дифференциального усилителя, второе токовое зеркало (11), вход которого соединен с коллектором третьего входного транзистора (4), а выход подключен к коллектору первого входного транзистора (1), отличающийся тем, что вход первого токового зеркала (9) соединен с выходом второго токового зеркала (11).

| Способ и приспособление для нагревания хлебопекарных камер | 1923 |

|

SU2003A1 |

| Дифференциальный усилитель | 1983 |

|

SU1166271A1 |

| Преобразователь напряжения в ток | 1987 |

|

SU1524161A2 |

| US 4595883, 17.06.1986 | |||

| US 5936465 А, 10.08.1999. | |||

Авторы

Даты

2008-08-20—Публикация

2007-05-16—Подача