Предлагаемое устройство относится к области измерительной техники и может быть использовано для измерения величин амплитуд и частот гармонических составляющих в исследуемых сигналах. В частности, предлагаемое устройство может быть использовано для формирования спектров при распознавании речи, формирования спектров при диагностике по шумовой составляющей работающих объектов, а также для формирования спектров акустических шумов при надводной и подводной навигациях.

Известны устройства для анализа гармонических составляющих в сигналах, одно из которых содержит генератор тактовых импульсов, блок постоянной памяти, счетчики, формирователь импульсов, блок сдвига фазы, умножитель, интегратор, блок выделения абсолютной величины сигнала, амплитудный детектор [1], а второе содержит аналоговый фильтр нижних частот, аналого-цифровой преобразователь, два цифровых фильтра, два блока измерения частот, блоки вычитания, сумматор, умножитель, блок усреднения, блок синхронизации [2]. Общей особенностью этих устройств относительно низкая точность измерения величин амплитуд гармонических составляющих.

Наиболее близким по техническому решению к предлагаемому устройству является устройство для анализа сигналов в реальном масштабе времени [3], содержащее последовательно соединенные генератор тактовых импульсов с регулируемой частотой, счетчик формирования адреса, счетчик циклов, последовательно соединенные блок постоянной памяти, аналого-цифровой умножитель, аналоговый интегратор со сбросом, блок выделения абсолютной величины сигнала, входную шину, выходную шину, шину установки начальных условий, где входы блока постоянной памяти подключены к выходам счетчика формирования адреса, входная шина подключена к аналоговому входу аналого-цифрового умножителя, а шина установки начальных условий соединена с установочным входом счетчика формирования адреса, с установочным входом счетчика циклов, с входом сброса аналогового интегратора со сбросом, а также содержащее вторую группу узлов, состоящую из последовательно соединенного блока постоянной памяти, аналого-цифрового умножителя, аналогового интегратора со сбросом, блока выделения абсолютной величины сигнала, аналоговый сумматор, схему И, сигнальную шину завершения цикла вычислений, причем входы блока постоянной памяти подключены к выходам счетчика формирования адреса, аналоговый вход аналого-цифрового умножителя подключен к входной шине, а вход сброса аналогового интегратора со сбросом подключен к шине установки начальных условий, входы аналогового сумматора подключены к выходам блоков выделения абсолютной величины сигнала, выход аналогового сумматора подключен к выходной шине, входы схемы И подключены к выходам счетчика циклов, выход схемы И подключен к сигнальной шине завершения цикла вычислений при данной частоте.

Это устройство принято в качестве прототипа.

Недостатком прототипа является относительно низкая точность определения величин амплитуд гармонических составляющих в исследуемых сигналах, которая обусловлена ориентацией конструкции устройства и соответственно применением в устройстве только двух сканирующих синусоидальных сигналов.

Технический результат предлагаемого изобретения направлен на повышение точности определения величин амплитуд гармонических составляющих в исследуемых сигналах за счет применения большего количества сканирующих синусоидальных сигналов при выполнении спектрального анализа. Это достигается тем, что в известное устройство для анализа сигналов в реальном масштабе времени, содержащее последовательно соединенные генератор тактовых импульсов с регулируемой частотой, счетчик формирования адреса и счетчик циклов, две группы узлов, каждая из которых содержит последовательно соединенные блок постоянной памяти, аналого-цифровой умножитель, аналоговый интегратор со сбросом и блок выделения абсолютной величины сигнала, а также содержащее аналоговый сумматор, схему И, входную шину, выходную шину, шину установки начальных условий и шину завершения цикла вычислений, где входы блоков постоянной памяти подключены к выходам счетчика формирования адреса, выходы блоков выделения абсолютной величины сигнала подключены к входам аналогового сумматора, входы схемы И подключены к выходам счетчика циклов, выход схемы И подключен к шине завершения цикла вычислений, входная шина подключена к аналоговым входам аналого-цифровых умножителей, шина установки начальных условий подключена к установочным входам счетчика формирования адреса, к установочным входам счетчика циклов и к входам сброса аналоговых интеграторов со сбросом, дополнительно введено к-2 групп узлов, каждая из которых содержит последовательно соединенные блок постоянной памяти, аналого-цифровой умножитель, аналоговый интегратор со сбросом и блок выделения абсолютной величины сигнала, где к - общее количество сканирующих синусоидальных сигналов при выполнении спектрального анализа, а также введены дополнительный аналоговый сумматор и выходной аналоговый сумматор, где входы введенных в состав устройства блоков постоянной памяти соединены с выходами счетчика формирования адреса, аналоговые входы аналого-цифровых умножителей подключены к входной шине, выходы блоков выделения абсолютной величины сигнала подключены к входам дополнительного аналогового сумматора, выходы аналогового сумматора и дополнительного аналогового сумматора подключены к входам выходного аналогового сумматора, входы сброса аналоговых интеграторов со сбросом подключены к шине установки начальных условий, а выход выходного аналогового сумматора подключен к выходной шине. Это позволяет повысить точность определения величин амплитуд гармонических составляющих в исследуемых сигналах за счет применения при выполнении спектрального анализа большего количества сканирующих синусоидальных сигналов.

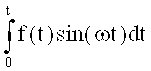

Вычисление величин амплитуд гармонических составляющих при данной величине циклической частоты в устройстве-прототипе выполняется в соответствии с формулой:

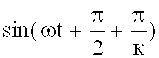

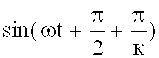

в которой f(τ) - исследуемый сигнал, sin(ωτ) и

В [3,4] показано, что относительная погрешность определения величин амплитуд в соответствии с формулой (1) может достигать величинь δ≈21%, что может быть неприемлемо для некоторых практических приложений.

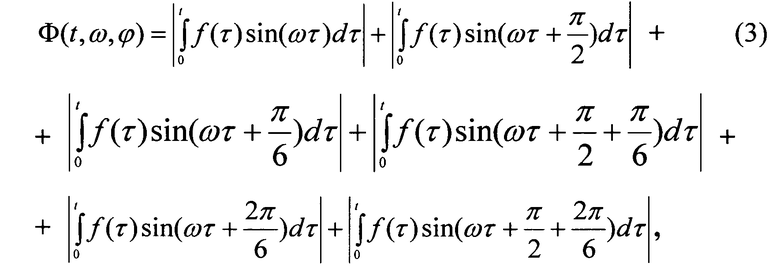

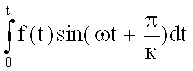

При введении двух, четырех и шести дополнительных сканирующих сигналов определение величин амплитуд синусоидальных составляющих в предлагаемом устройстве осуществляется по следующим формулам:

В этих формулах в первых строках содержится формула (1), т.е. формула, на основе которой осуществляется работа устройства-прототипа. Последующие строки в формулах (2)-(4) содержат записи вспомогательных сканирующих синусоидальных сигналов, которые сдвинуты по начальной фазе относительно исходных сканирующих синусоидальных сигналов в формуле (1) соответственно с величинами шага

Обоснование справедливости формул (2)-(4) и соответственно результаты проверки справедливости этих формул посредством моделирования приводятся в [4].

Структурная схема устройства изображена на фиг.1. Устройство для анализа сигналов в реальном масштабе времени содержит последовательно соединенные генератор тактовых импульсов 1 с регулируемой частотой, счетчик формирования адреса 2, счетчик циклов 3, два блока постоянной памяти 4 и 5, последовательно соединенные с каждым из блоков постоянной памяти 4 и 5 аналого-цифровые умножители 6, аналоговые интеграторы со сбросом 7, блоки выделения абсолютной величины сигнала 8, а также содержит аналоговый сумматор 9, схему И 10, входную шину 11, шину установки начальных условий 12, выходную шину 13, сигнальную шину 14 завершения вычислений при данной частоте, где входы блоков постоянной памяти 4 и 5 подключены к выходам счетчика формирования адреса 2, выходы блоков выделения абсолютной величины сигнала 8 подключены к входам аналогового сумматора 9, выходы счетчика циклов 3 подключены к входам схемы И 10, входная шина подключена к аналоговым входам аналого-цифровых умножителей 6, шина установки начальных условий 12 соединена с установочным входом счетчика формирования адреса 2, с установочным входом счетчика циклов 3, с входами сброса аналоговых интеграторов со сбросом 7, а к выходу схемы И 10 подключена сигнальная шина 14 завершения вычислений при данной частоте, а также согласно изобретению содержит введенные в устройство к-2 блоков постоянной памяти 15, где к - общее количество сканирующих синусоидальных сигналов в устройстве, последовательно соединенные с каждым из к-2 блоков постоянной памяти 15, аналого-цифровые умножители 16, аналоговые интеграторы со сбросом 17, блоки выделения абсолютной величины сигнала 18, а также дополнительный аналоговый сумматор 19 и выходной аналоговый сумматор 20, где входы блоков постоянной памяти 15 подключены к выходам счетчика формирования адреса 2, выходы блоков выделения абсолютной величины сигнала 18 подключены к входам дополнительного аналогового сумматора 19, а выходы аналогового сумматора 9 и дополнительного аналогового сумматора 19 подключены к входам выходного аналогового сумматора 20, входная шина 11 подключена к аналоговым входам аналого-цифровых умножителей 16, шина установки начальных условий 12 соединена с входами сброса аналоговых интеграторов со сбросом 17, а выходная шина 13 подключена к выходу выходного аналогового сумматора 20.

Генератор тактовых импульсов 1 с регулируемой частотой - генератор прямоугольных импульсов любой известной конструкции с частотой F, регулируемой в заданном диапазоне частот F1≤F≤F2. Счетчики 2 и 3 - счетчики прямого счета, имеющие n1 и n2 двоичных разрядов соответственно. Счетчик 2 предназначен для формирования последовательностей двоичных адресов с разрядностью ni в диапазоне значений от 00…0 до 11…1, а счетчик циклов 3 предназначен для подсчета количества сформированных последовательностей адресов в упомянутом диапазоне. Блоки постоянной памяти 4 и 5 предназначены для хранения в цифровом виде и соответственно для выдачи последовательностей значений основных сканирующих синусоидальных сигналов sin(ωt) и

Работает устройство следующим образом. На генераторе тактовых импульсов 1 с регулируемой частотой вручную или с помощью микроЭВМ устанавливается частота F, обеспечивающая генерацию сигналов sin(ωt) и

На аналоговых интеграторах со сбросом 17 формируются интегралы

Эффективность рассматриваемого устройства можно проиллюстрировать на следующих примерах. Моделирование непосредственно показало [4], что при использовании двух вспомогательных сканирующих синусоидальных сигналов, т.е. при использовании формулы (2) относительная погрешность определения величин амплитуд в исследуемых сигналах уменьшается до δ≈5%. При использовании четырех вспомогательных сканирующих синусоидальных сигналов, т.е. при использовании формулы (3) относительная погрешность определения величин амплитуд в исследуемых сигналах уменьшается до δ≈3%. При использовании шести вспомогательных сканирующих синусоидальных сигналов, т.е. при использовании формулы (4) относительная погрешность определения величин амплитуд в исследуемых сигналах уменьшается до δ≈2%, т.е. уменьшается приблизительно на порядок.

Источники информации

1. Авт.св. СССР №1812518.

2. Патент РФ №2018144.

3. Патент РФ №2404438.

4. Любомудров А.А., Башков А.А. Подход к повышению точности определения амплитуд синусоидальных составляющих в исследуемых сигналах при спектральном анализе. Труды научной сессии НИЯУ МИФИ-2010. В 6 томах. Том V. Информационно-телекоммуникационные системы. Проблемы информационной безопасности. М.: НИЯУ МИФИ, 2010.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ АНАЛИЗА СИГНАЛОВ В РЕАЛЬНОМ МАСШТАБЕ ВРЕМЕНИ | 2009 |

|

RU2404438C1 |

| Устройство для анализа сигналов в реальном масштабе времени | 1990 |

|

SU1812518A1 |

| СКАНИРУЮЩИЙ РАДИОМЕТР | 2012 |

|

RU2495443C1 |

| УНИВЕРСАЛЬНЫЙ ГЕНЕРАТОР СИГНАЛОВ ПРОИЗВОЛЬНОЙ ФОРМЫ | 1994 |

|

RU2060536C1 |

| ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ КОЭФФИЦИЕНТА ГАРМОНИКИ НАПРЯЖЕНИЯ | 1990 |

|

RU2030753C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ НИЗКОЧАСТОТНЫХ ДОПЛЕРОВСКИХ СИГНАЛОВ | 1985 |

|

SU1281125A1 |

| Аналого-цифровой анализатор сигналов | 2024 |

|

RU2826857C1 |

| УСТРОЙСТВО КОНТРОЛЯ МАТЕРИАЛОВ И ВЕЩЕСТВ | 2012 |

|

RU2529670C2 |

| Устройство для отображения векторных диаграмм на экране электронно-лучевой трубки | 1985 |

|

SU1316027A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ПСЕВДОСЛУЧАЙНОГО СИГНАЛА | 1989 |

|

SU1692272A1 |

Изобретение относится к измерительной технике и может быть использовано в измерительных системах для измерения амплитуд и частот гармонических составляющих в исследуемых сигналах. В устройство дополнительно включено к-2 дополнительных групп узлов, каждая из которых содержит последовательно соединенные блок постоянной памяти, аналого-цифровой умножитель, аналоговый интегратор со сбросом и блок выделения абсолютной величины сигнала, где k - общее количество сканирующих синусоидальных сигналов при выполнении спектрального анализа, а также введения дополнительного аналогового сумматора и выходного аналогового сумматора, где входы введенных в состав устройства блоков постоянной памяти соединены с выходами счетчика формирования адреса, аналоговые входы аналого-цифровых умножителей подключены к входной шине, выходы блоков выделения абсолютной величины сигнала подключены к входам дополнительного аналогового сумматора. Технический результат заключается в повышении точности измерения амплитуд гармонических составляющих. 1 ил.

Устройство для анализа сигналов в реальном масштабе времени, содержащее последовательно соединенные генератор тактовых импульсов с регулируемой частотой, счетчик формирования адреса, счетчик циклов, две группы узлов, каждая из которых содержит последовательно соединенные блок постоянной памяти, аналого-цифровой умножитель, аналоговый интегратор со сбросом и блок выделения абсолютной величины сигнала, а также содержащее аналоговый сумматор, схему И, входную шину, выходную шину, шину установки начальных условий и шину завершения цикла вычислений, где входы блоков постоянной памяти подключены к выходам счетчика формирования адреса, выходы блоков выделения абсолютной величины сигнала подключены к входам аналогового сумматора, входы схемы И подключены к выходам счетчика циклов, выход схемы И подключен к шине завершения цикла вычислений, входная шина подключена к аналоговым входам аналого-цифровых умножителей, шина установки начальных условий подключена к установочным входам счетчика формирования адреса, к установочным входам счетчика циклов и к входам сброса аналоговых интеграторов со сбросом, отличающееся тем, что в состав устройства введено дополнительно к-2 групп узлов, каждая из которых содержит последовательно соединенные блок постоянной памяти, аналого-цифровой умножитель, аналоговый интегратор со сбросом и блок выделения абсолютной величины сигнала, где к - общее количество сканирующих синусоидальных сигналов при выполнении спектрального анализа, а также введены дополнительный аналоговый сумматор и выходной аналоговый сумматор, где входы введенных в состав устройства блоков постоянной памяти соединены с выходами счетчика формирования адреса, аналоговые входы аналого-цифровых умножителей подключены к входной шине, выходы блоков выделения абсолютной величины сигнала подключены к входам дополнительного аналогового сумматора, выходы аналогового сумматора и дополнительного аналогового сумматора подключены к входам выходного аналогового сумматора, входы сброса аналоговых интеграторов со сбросом подключены к шине установки начальных условий, а выход выходного аналогового сумматора подключен к выходной шине.

| УСТРОЙСТВО ДЛЯ АНАЛИЗА СИГНАЛОВ В РЕАЛЬНОМ МАСШТАБЕ ВРЕМЕНИ | 2009 |

|

RU2404438C1 |

| Устройство для анализа сигналов в реальном масштабе времени | 1990 |

|

SU1812518A1 |

| Устройство для подачи порошкообразного материала при сварке | 1974 |

|

SU498121A1 |

| EP 1676222 A2, 05.07.2006 | |||

| US 2003187621 A1, 02.10.2003 | |||

Авторы

Даты

2015-05-10—Публикация

2013-12-30—Подача