Изобретение относится к области измерительной техники и может быть использовано для измерения величин амплитуд гармонических составляющих в исследуемых сигналах на заданных частотах.

Цель изобретения - повышение быстродействия.

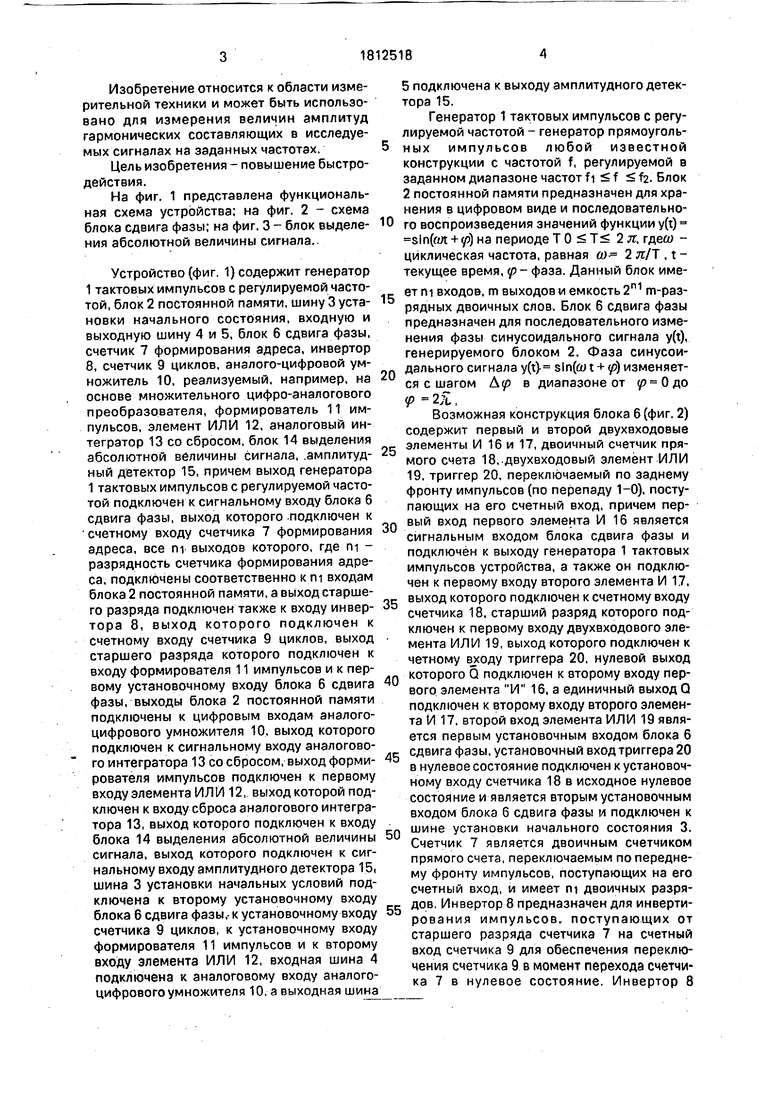

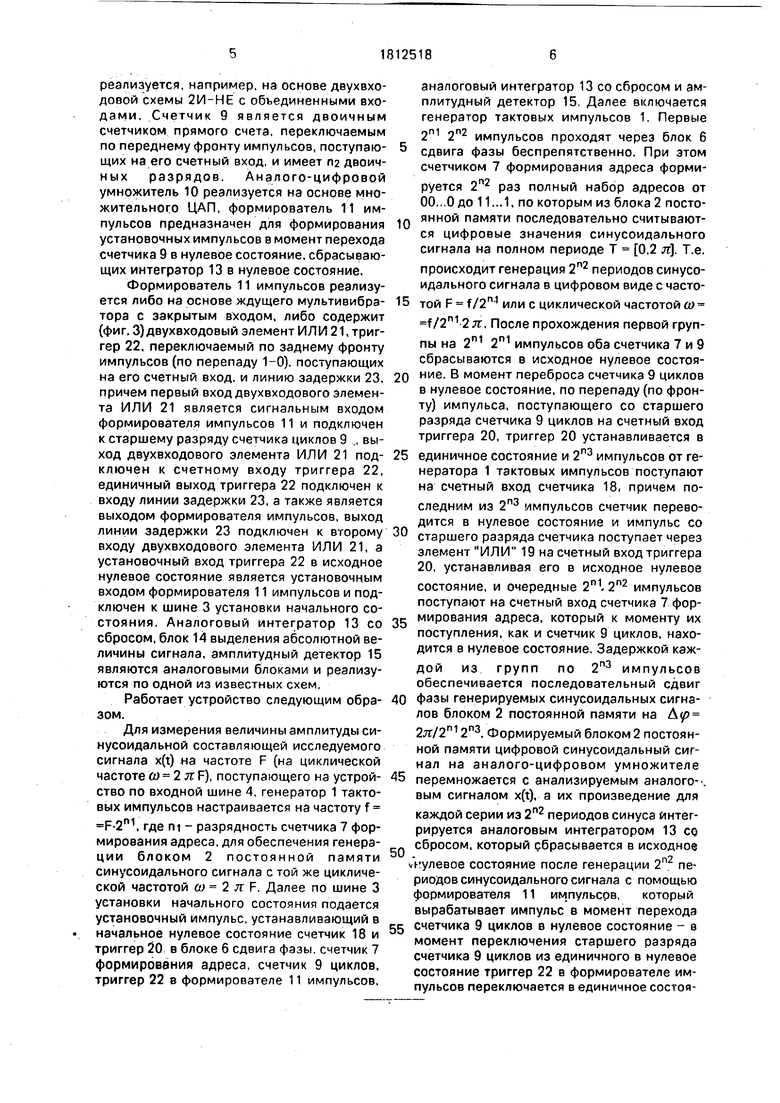

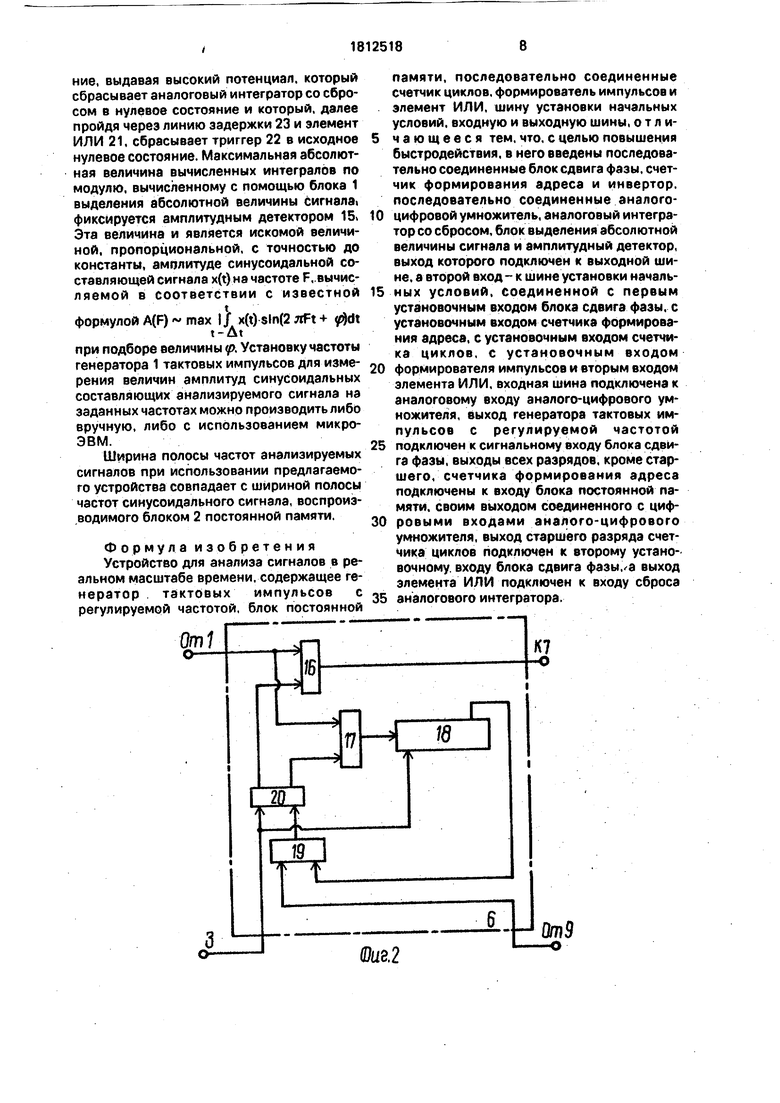

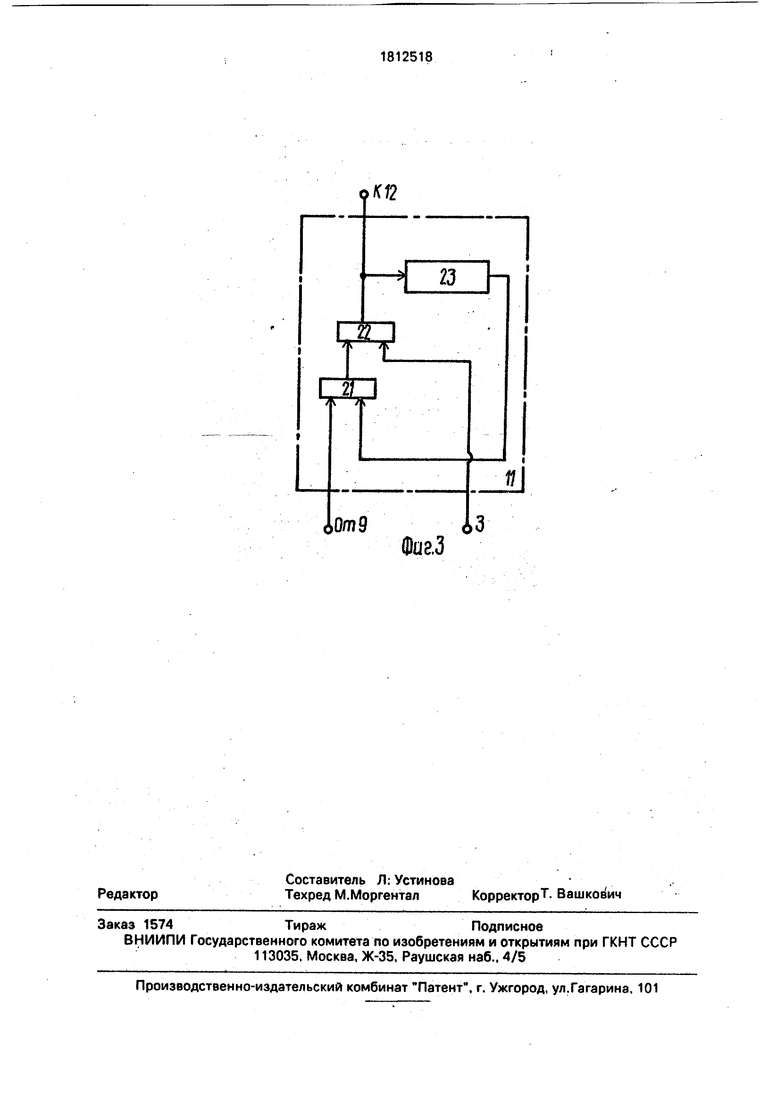

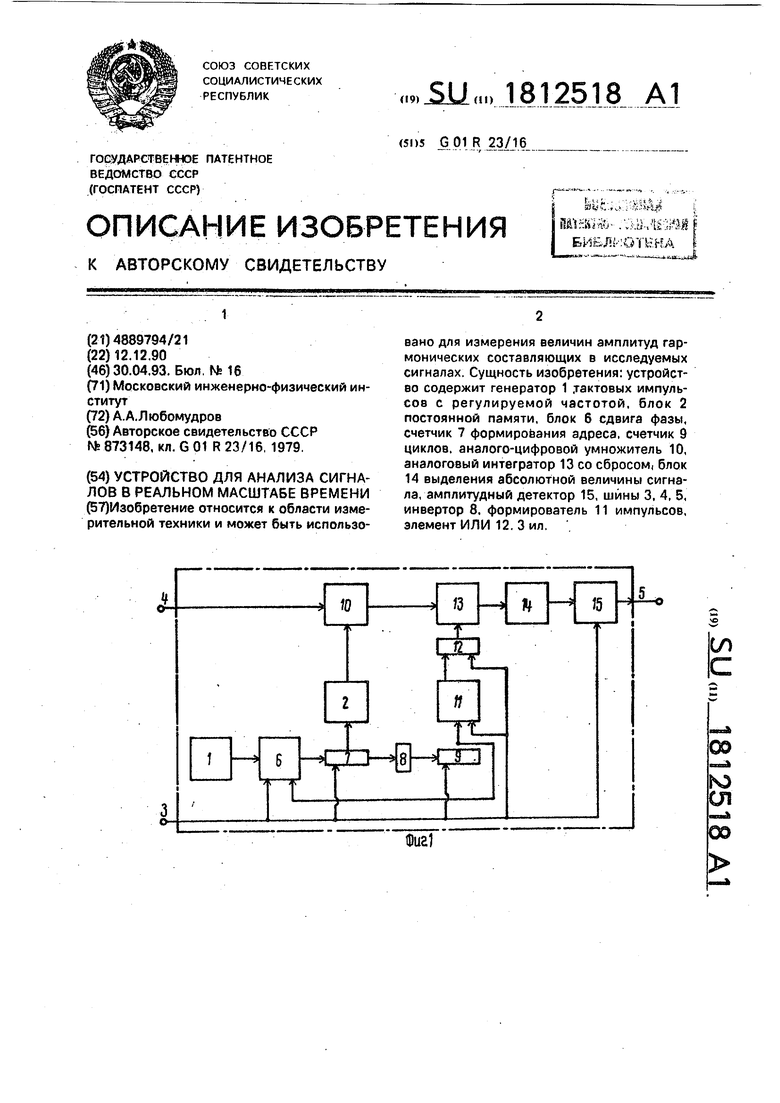

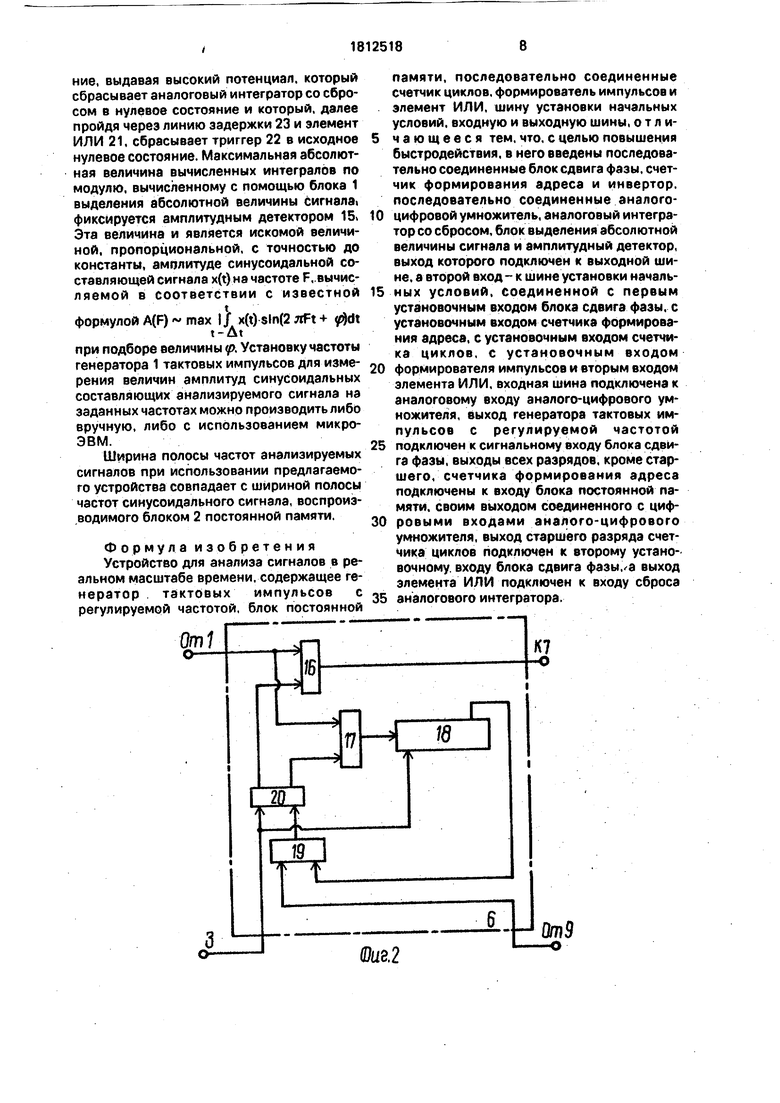

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 - схема блока сдвига фазы; на фиг. 3 - блок выделения абсолютной величины сигнала..

Устройство (фиг. 1) содержит генератор 1 тактовых импульсов с регулируемой частотой, блок 2 постоянной памяти, шину 3 установки начального состояния, входную и выходную шину 4 и 5, блок 6 сдвига фазы, счетчик 7 формирования адреса, инвертор 8, счетчик 9 циклов, аналого-цифровой умножитель 10, реализуемый, например, на основе множительного цифро-аналогового преобразователя, формирователь 11 импульсов, элемент ИЛИ 12, аналоговый интегратор 13 со сбросом, блок 14 выделения абсолютной величины сигнала, .амплитудный детектор 15, причем выход генератора 1 тактовых импульсов с регулируемой частотой подключен к сигнальному входу блока б сдвига фазы, выход которого подключен к счетному входу счетчика 7 формирования адреса, все пг выходов которого, где ги - разрядность счетчика формирования адреса, подключены соответственно кщ входам блока 2 постоянной памяти, а выход старшего разряда подключен также к входу инвертора 8, выход которого подключен к счетному входу счетчика 9 циклов, выход старшего разряда которого подключен к входу формирователя 11 импульсов и к первому установочному входу блока 6 сдвига фазы/выходы блока 2 постоянной памяти подключены к цифровым входам аналого- цифрового умножителя 10. выход которого подключен к сигнальному входу аналогового интегратора 13 со сбросом, выход формирователя импульсов подключен к первому входу элемента ИЛИ 12, выход которой подключен к входу сброса аналогового интегратора 13, выход которого подключен к входу блока 14 выделения абсолютной величины сигнала, выход которого подключен к сигнальному входу амплитудного детектора 15, шина 3 установки начальных условий подключена к второму установочному входу блока 6 сдвига фазы,- к установочному входу счетчика 9 циклов, к установочному входу формирователя 11 импульсов и к второму входу элемента ИЛИ 12, входная шина 4 подключена к аналоговому входу аналого- цифрового умножителя 10, а выходная шина

5 подключена к выходу амплитудного детектора 15.

Генератор 1 тактовых импульсов с регулируемой частотой - генератор прямоугольных импульсов любой известной конструкции с частотой f, регулируемой в заданном диапазоне частот f 1 S f f2. Блок 2 постоянной памяти предназначен для хранения в цифровом виде и последовательного воспроизведения значений функции y(t) sln(«t + /)} на периоде Т 0 TS 2 л; гдеш - циклическая частота, равная со- 2 тг/Т , t - текущее время, (р- фаза. Данный блок имеет щ входов, m выходов и емкость m-раз- рядных двоичных слов. Блок 6 сдвига фазы предназначен для последовательного изменения фазы синусоидального сигнала y(t), генерируемого блоком 2. Фаза синусоидальнего сигнала y(t} sln(fut + j) изменяется с шагом Ду в диапазоне от р 0 до р 2Ј,

Возможная конструкция блока 6 (фиг. 2) содержит первый и второй двухвходовые

элементы И 16 и 17, двоичный счетчик прямого счета 18,.двухвходовый элемент ИЛИ 19, триггер 20, переключаемый по заднему фронту импульсов (по перепаду 1-0), поступающих на его счетный вход, причем первый вход первого элемента И 16 является сигнальным входом блока сдвига фазы и подключён к выходу генератора 1 тактовых импульсов устройства, а также он подключен к первому входу второго элемента И 17,

выход которого подключен к счетному входу счетчика 18, старший разряд которого подключен к первому входу двухвходового элемента ИЛИ 19, выход которого подключен к четному входу триггера 20, нулевой выход

которого Q подключен к второму входу первого элемента И 16, а единичный выход Q подключен к второму входу второго элемента И 17, второй вход элемента ИЛИ 19 является первым установочным входом блока 6

сдвига фазы, установочный вход триггера 20 в нулевое состояние подключен к установочному входу счетчика 18 в исходное нулевое состояние и является вторым установочным входом блока 6 сдвига фазы и подключен к

шине установки начального состояния 3. Счетчик 7 является двоичным счетчиком прямого счета, переключаемым по переднему фронту импульсов, поступающих на его счетный вход, и имеет щ двоичных разрядов. Инвертор 8 предназначен для инверти- рования импульсов, поступающих от старшего разряда счетчика 7 на счетный вход счетчика 9 для обеспечения переключения счетчика 9 в момент перехода счетчика 7 в нулевое состояние. Инвертор 8

реализуется, например, на основе двухвхо- довой схемы 2И-НЕ с объединенными входами. Счетчик 9 является двоичным счетчиком прямого счета, переключаемым по переднему фронту импульсов, поступающих на его счетный вход, и имеет П2 двоичных разрядов. Аналого-цифровой умножитель 10 реализуется на основе множительного ЦАП, формирователь 11 импульсов предназначен для формирования установочных импульсов в момент перехода счетчика 9 в нулевое состояние, сбрасывающих интегратор 13 в нулевое состояние.

Формирователь 11 импульсов реализуется либо на основе ждущего мультивибратора с закрытым входом, либо содержит (фиг. 3)двухвходовый элемент ИЛИ 21, триггер 22, переключаемый по заднему фронту импульсов (по перепаду 1-0), поступающих на его счетный вход, и линию задержки 23, причем первый вход двухвходового элемента ИЛИ 21 является сигнальным входом формирователя импульсов 11 и подключен к старшему разряду счетчика циклов 9 .., выход двухвходового элемента ИЛИ 21 подключен к счетному входу триггера 22, единичный выход триггера 22 подключен к входу линии задержки 23, а также является выходом формирователя импульсов, выход линии задержки 23 подключен к второму входу двухвходового элемента ИЛИ 21, а установочный вход триггера 22 в исходное нулевое состояние является установочным входом формирователя 11 импульсов и подключен к шине 3 установки начального состояния. Аналоговый интегратор 13 со сбросом, блок 14 выделения абсолютной величины сигнала, амплитудный детектор 15 являются аналоговыми блоками и реализуются по одной из известных схем.

Работает устройство следующим образом.

Для измерения величины амплитуды синусоидальной составляющей исследуемого сигнала x(t) на частоте F (на циклической частоте (У 2 п F), поступающего на устройство по входной шине 4, генератор 1 тактовых импульсов настраивается на частоту f

F-2n1, где m - разрядность счетчика 7 формирования адреса, для обеспечения генерации блоком 2 постоянной памяти синусоидального сигнала с той же циклической частотой ш 2 л F. Далее по шине 3 установки начального состояния подается установочный импульс, устанавливающий в начальное нулевое состояние счетчик 18 и триггер 20 в блоке б сдвига фазы, счетчик 7 формирования адреса, счетчик 9 циклов, триггер 22 в формирователе 11 импульсов.

аналоговый интегратор 13 со сбросом и амплитудный детектор 15. Далее включается генератор тактовых импульсов 1. Первые 2П1 импульсов проходят через блок б

5 сдвига фазы беспрепятственно. При этом счетчиком 7 формирования адреса формируется раз полный набор адресов от 00...О до 11...1, по которым из блока 2 постоQ янной памяти последовательно считываются цифровые значения синусоидального сигнала на полном периоде Т 0,2 л. Т.е.

происходит генерация 2п2 периодов синусоидального сигнала в цифровом виде с часто5 той F f/2n1 или с циклической частотой (о- f/2n12 п. После прохождения первой группы на 2n1 2n1 импульсов оба счетчика 7 и 9 сбрасываются в исходное нулевое состоя0 ние. В момент переброса счетчика 9 циклов в нулевое состояние, по перепаду (по фронту) импульса, поступающего со старшего разряда счетчика 9 циклов на счетный вход триггера 20, триггер 20 устанавливается в

5 единичное состояние и 2ПЗ импульсов от генератора 1 тактовых импульсов поступают на счетный вход счетчика 18 причем последним из 2ПЗ импульсов счетчик переводится в нулевое состояние и импульс со старшего разряда счетчика поступает через элемент ИЛИ 19 на счетный вход триггера 20, устанавливая его в исходное нулевое

состояние, и очередные 2n1. импульсов поступают на счетный вход счетчика 7 форе мирования адреса, который к моменту их поступления, как и счетчик 9 циклов, находится в нулевое состояние. Задержкой каждой из групп по 2ПЗ импульсов обеспечивается последовательный сдвиг 0 фазы генерируемых синусоидальных сигналов блоком 2 постоянной памяти на Д)

2лг/2п12 3. Формируемый блоком 2 постоянной памяти цифровой синусоидальный сигнал на аналого-цифровом умножителе 5 перемножается с анализируемым аналоге--, вым сигналом x(t), а их произведение для

каждой серии из периодов синуса интегрируется аналоговым интегратором 13 cq сбросом, который сбрасывается в исходное

-п

чкулевое состояние после генерации 2 периодов синусоидального сигнала с помощью формирователя 11 импульсов, который вырабатывает импульс в момент перехода 5 счетчика 9 циклов в нулевое состояние - в момент переключения старшего разряда счетчика 9 циклов из единичного в нулевое состояние триггер 22 а формирователе импульсов переключается в единичное состоя0

ние, выдавая высокий потенциал, который сбрасывает аналоговый интегратор со сбросом в нулевое состояние и который, далее пройдя через линию задержки 23 и элемент ИЛИ 21, сбрасывает триггер 22 в исходное нулевое состояние. Максимальная абсолютная величина вычисленных интегралов по модулю, вычисленному с помощью блока 1 выделения абсолютной величины сигнала) фиксируется амплитудным детектором 15. Эта величина и является искомой величиной, пропорциональной, с точностью до константы, амплитуде синусоидальной составляющей сигнала x(t) на частоте F. вычис- ляемой в соответствии с известной

формулой A(F) max I/ x(t) sln(2 jfFi + 0dt

t-At

при подборе величины р. Установку частоты генератора 1 тактовых импульсов для измерения величин амплитуд синусоидальных составляющих анализируемого сигнала на заданных частотах можно производить либо вручную, либо с использованием микро- ЭВМ.

Ширина полосы частот анализируемых сигналов при использовании предлагаемого устройства совпадает с шириной полосы частот синусоидального сигнала, воспроизводимого блоком 2 постоянной памяти.

Формула изобретения Устройство для анализа сигналов в реальном масштабе времени, содержащее генератор . тактовых импульсов с регулируемой частотой, блок постоянной

памяти, последовательно соединенные

счетчик циклов, формирователь импульсов и

элемент ИЛИ, шину установки начальных

условий, входную и выходную шины, о т л ичающееся тем, что, с целью повышения быстродействия, в него введены последовательно соединенные блок сдвига фазы, счетчик формирования адреса и инвертор, последовательно соединенные аналогоцифровой умножитель, аналоговый интегратор со сбросом, блок выделения абсолютной величины сигнала и амплитудный детектор, выход которого подключен к выходной шине, а второй вход- к шине установки начальных условий, соединенной с первым установочным входом блока сдвига фазы, с установочным входом счетчика формирования адреса, с установочным входом счетчика циклов, с установочным входом

формирователя импульсов и вторым входом элемента ИЛИ, входная шина подключена к аналоговому входу аналого-цифрового умножителя, выход генератора тактовых импульсов с регулируемой частотой

подключен к сигнальному входу блока сдвига фазы, выходы всех разрядов, кроме старшего, счетчика формирования адреса подключены к входу блока постоянной памяти, своим выходом соединенного с цифровыми входами аналого-цифрового умножителя, выход старшего разряда счетчика циклов подключен к второму установочному входу блока сдвига фазы,/а выход элемента ИЛИ подключен к входу сброса

аналогового интегратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ АНАЛИЗА СИГНАЛОВ В РЕАЛЬНОМ МАСШТАБЕ ВРЕМЕНИ | 2009 |

|

RU2404438C1 |

| УСТРОЙСТВО ДЛЯ АНАЛИЗА СИГНАЛОВ В РЕАЛЬНОМ МАСШТАБЕ ВРЕМЕНИ | 2013 |

|

RU2550309C1 |

| Устройство для считывания графической информации | 1987 |

|

SU1564661A1 |

| Цифровой генератор функций | 1986 |

|

SU1388842A1 |

| Устройство для поверки цифровых измерителей девиации фазы | 1990 |

|

SU1781651A1 |

| Устройство для отображения векторных диаграмм на экране электронно-лучевой трубки | 1985 |

|

SU1316027A1 |

| Цифровой фазометр | 1982 |

|

SU1092430A1 |

| Цифроаналоговый измеритель средней частоты | 1991 |

|

SU1775678A1 |

| Устройство для цифровой записи воспроизведения речевой информации | 1988 |

|

SU1573470A1 |

| Способ преобразования кода угла в напряжения,пропорциональные синусу и косинусу угла, и устройство для его осуществления | 1985 |

|

SU1345346A1 |

Изобретение относится к области измерительной техники и может быть использовано для измерения величин амплитуд гармонических составляющих в исследуемых сигналах. Сущность изобретения: устройство содержит генератор 1 .тактовых импульсов с регулируемой частотой, блок 2 постоянной памяти, блок 6 сдвига фазы, счетчик 7 формирования адреса, счетчик 9 циклов, аналого-цифровой умножитель 10, аналоговый интегратор 13 со сбросом, блок 14 выделения абсолютной величины сигнала, амплитудный детектор 15, шины 3, 4, 5, инвертор 8. формирователь 11 импульсов, элемент ИЛИ 12. 3 ил.

От1

К

К7 -о

V

18

6

0U8.2

ОтЗ

-о

raj

г

Г7ЖП

мt

i

,0т 9

п

. -Н 23

aj

г

Фиг.3

| Цифровой гармонический анализатор | 1979 |

|

SU873148A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1993-04-30—Публикация

1990-12-12—Подача