Изобретение относится к области вычислительной техники и может найти применение в генераторах сигналов сложной формы, а также в моделирующих системах, предназначенных для исследования радиотехнических систем.

Цель изобретения - расширение области применения за счет формирования сигналов с изменяющейся формой спектра.

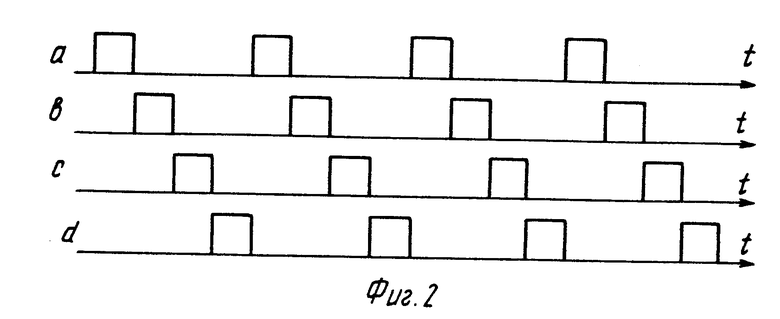

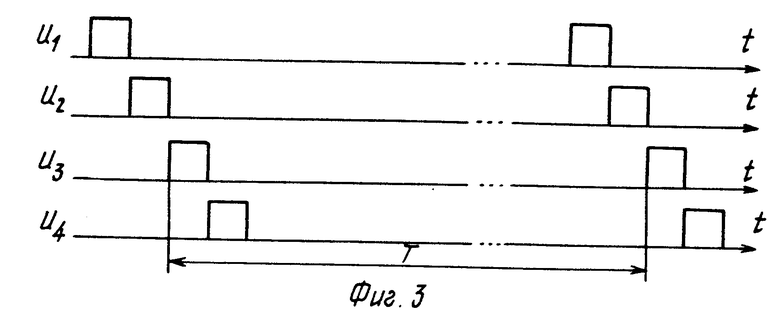

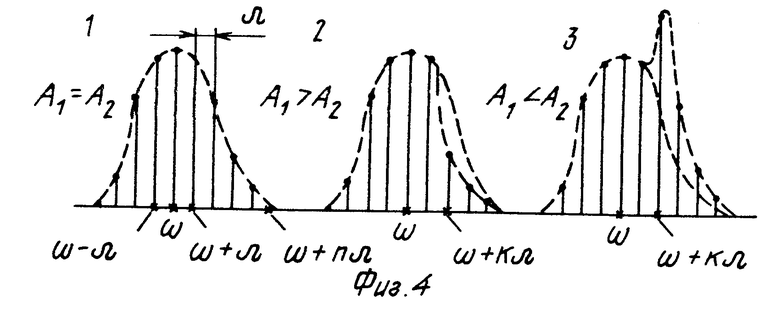

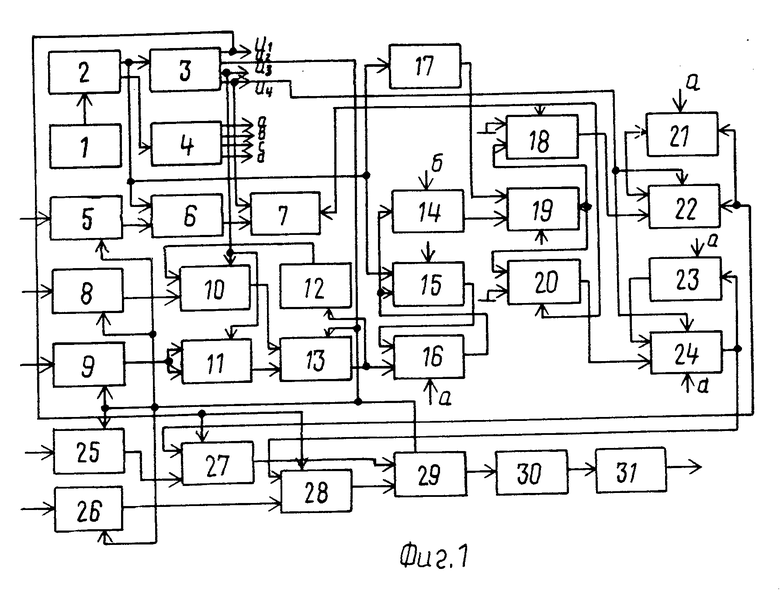

На фиг. 1 изображена функциональная схема устройства; на фиг. 2 - временные диаграммы тактирующих сигналов устройства; на фиг. 3 - временные диаграммы управляющих сигналов устройства; на фиг. 4 - варианты выходных спектров устройства.

Устройство содержит генератор тактовых импульсов 1, счетчик адреса 2, дешифратор управления 3, дешифратор состояний 4, регистр частоты среда 5, блок сравнения 6, триггер 7, регистр частоты 8, регистр ширины спектра 9, первый мультиплексор 10, второй мультиплексор 11, первый регистр 12, сумматор 13, блок постоянной памяти 14, блок памяти 15, сумматор 16, блок постоянной памяти 17, третий мультиплексор 18, первый умножитель 19, четвертый мультиплексор 20, второй регистр 21, сумматор 22, третий регистр 23, сумматор 24, первый регистр амплитуды 25, второй регистр амплитуды 26, второй умножитель 27, третий умножитель 28, сумматор 29, преобразователь код-напряжение 30, аналоговый фильтр 31.

Устройство работает следующим образом.

Устройство реализует модель сигнала, соответствующего математическому выражению:

S(t) = A aicos[(ω+iΩ)t+ϕi]+A

aicos[(ω+iΩ)t+ϕi]+A aicos[(ω+iΩ)t+ϕi]

aicos[(ω+iΩ)t+ϕi]

(1) где i - порядковый номер гармонического сигнала (составляющей спектра), аi - нормированная амплитуда гармонической составляющей сигнала, ω - несущая (средняя) частота формирующего сигнала, Ω - частотный сдвиг спектральных составляющих, определяющий и ширину спектра, ω - n Ω - нижняя частота спектра, ω + n Ω - верхняя частота спектра, ω + K Ω - частота среза (излома) спектра, ϕi - случайная фаза спектральных составляющих, А1, А2 - уровни амплитуд первой (нижней) и второй (верхней) частей спектра.

Подобный вид имеет реальный сигнал, отраженный от подстилающей поверхности типа земной на границе раздела двух неоднородностей (например, типа суша-море). Тригонометрические преобразования позволяют привести выражение (1) к виду:

S(t) = A(t)cos(ω t + Φ (t)), где A(t), Φ (t) - псевдослучайные амплитуды и фаза сигнала.

Следовательно, формируемый сигнал является псевдослучайным. При реализации выражения (1) в устройстве используется рекуррентное вычисление для полной фазы гармонической составляющей:

Θi (tj) = (ω + i Ω)ti + ϕi = Θi (tj-1) + + (ω + i Ω) T , (2) где tj = jT - дискретное время обработки информации, j = 0,+,2,..., Т - период дискретизации (вычисления одного отсчета сигнала).

Параметры сигнала (1) хранятся в следующих блоках устройства. Номер гармоники среза К хранится в регистре частоты среза 5, параметр ω Т - в регистре частоты 8, Ω Т - в регистре ширины спектра 9, значения амплитуд А1 и А2 хранятся соответственно в первом и втором регистрах амплитуды 25 и 26, нормированные отсчеты амплитуд гармонических составляющих аiзаписаны во втором блоке постоянной памяти 17, текущие отсчеты полной фазы составляющих хранятся в блоке памяти 15.

Блоки устройства работают под управлением тактирующих (фиг. 2) и управляющих (фиг. 3) сигналов, вырабатываемых дешифратором состояний 4 и дешифратором управления 3 устройства (фиг. 1). При этом генератор тактовых импульсов 1 вырабатывает равномерную последовательность импульсов, которая подается на счетный вход счетчика адреса 2. Счетчик адреса 2 последовательно изменяет свои состояния. Сигналы с двух младших разрядов счетчика адреса 2 подаются на дешифратор состояний 4. На четырех выходах дешифратора состояний 4 формируются сдвинутые тактирующие последовательности импульсов а, b, c, d (фиг. 2). Совокупность всех разрядных сигналов счетчика адреса 2 подается на дешифратор управления 3, на четырех выходах которого формируются управляющие сигналы U1, U2, U3, U4 (фиг. 3), сдвинутые друг относительно друга, равные по длительности тактирующим с периодом повторения Т, которой равен времени обработки одного отсчета сигнала.

Формирование полной фазы Θj гармонических составляющих сигнала производится согласно выражению (2) блоками 8-13, 15, 16 устройства. При этом под действием управляющего сигнала U3 (фиг. 1, 3) первый мультиплексор 10 подключает к первому информационному входу сумматора 13 цифровое значение ω t с регистра частоты 8, а второй мультиплексор подключает ко второму информационному входу сумматора 13 цифровое значение n Ω T. Умножение величины ΩТ, хранимой в регистре ширины спектра 9, на постоянный коэффициент n = 2m (где m - целое число) достигается благодаря соединению выходных разрядов регистра 9 с номерами q со входными разрядами второго мультиплексора 11 с номерами q + m. По тактирующему сигналу "С" сумматор 13 производит сложение входных данных, в результате чего образуется сумма ( ω + n Ω )Т. Эта сумма является приращением полной фазы гармонической составляющей с номером n за временной интервал Т. По такту "d" результат суммирования запоминается в первом регистре 12. Эта же сумма подается в сумматор 16, где складывается с полной фазой Θn, вычисленной на предыдущем временном интервале Т и хранящейся в ячейке и блока памяти 15. Адрес ячейки памяти блока 15 задает счетчик адреса 2, ведущий счет синхронно с циклом формирования полной фазы каждой гармоники. Результирующая сумма описывается выражением (2) и является полной фазой для n-й гармоники в текущем временном интервале Т. По такту "В" этот результат записывается в ячейку n блока памяти 15, который сигналом "В" кратковременно переводится в режим записи информации. В следующем временном цикле (фиг. 2) аналогично описанному будет вычислятьсяполная фаза Θn-1 для гармонической составляющей сигнала с номером n-1. Процедура вычисления фазы аналогична описанной, за исключением работы сумматора 13, к входам которого в последующих временных циклах подключаются выходы первого регистра 12, который хранит значение результата суммирования сумматора 13, и выход регистра ширины спектра 9 со значением ΩТ. Во всех циклах кроме первого (управляемых сигналом U3) сумматор 13 производит вычитание из суммы, образуемой в предыдущем цикле и хранящейся в первом регистре 12, значение Ω Т. То есть для гармоники n = 1 будет образовано приращение фазы, равное [ ω+ (n-1) Ω ]T, а для произвольной i гармоники приращение [ω + (i-1) Ω ]T. Так цикл за циклом в ячейках блока памяти 15 обновляется и хранится информация полных текущих фаз всех гармонических составляющих сигнала. Если параметры частоты ω и ширины спектра Ω в регистрах частоты 8 и ширины спектра 9 изменяется, то вслед за этим изменится и скорость полных фаз гармоник сигнала.

Параллельно циклам формирования полных фаз гармоник производится работа по формированию целого сигнала вида (1). При этом полная фаза i-й составляющей с выхода сумматора 16 подается на адресные входы блока постоянной памяти 14. В ячейках блока постоянной памяти 14 хранится значение косинуса как функции от фазы на периоде 0-2π . Ограничение фазы величиной 2 π достигается ограничением разрядной сетки сумматора 16. С выхода блока постоянной памяти 14 снимается цифровое значение соs Θi. Это значение перемножается в первом умножителе 19 с нормированной амплитудой ai, выводимой из ячейки блока постоянной памяти 17, адрес которой определяет счетчик адреса 2. На выходе первого умножителя 19 в i-ом цикле формируется величина аicos Θi..

Сложение составляющих сигнала (1) производится в сумматорах 22, 24. Причем в сумматоре 22 формируется первое нормированное слагаемое выражения (1), а в сумматоре 24 второе нормированное слагаемое. Распределение составляющих с номером i по сумматорам 22, 24 производится с помощью третьего и четвертого мультиплексоров 18, 20, которые управляются триггером 7. Триггер 7 фиксирует n - k +1 цикл времени перехода от второго слагаемого выражения (1) к первому слагаемому. Это выполняется следующим образом. Управляющим сигналом U4 триггер 7 устанавливается в единичное состояние. Выходной сигнал триггера 7 подается на третий и четвертый мультиплексоры 18, 20. Третий мультиплексор 18 подает на информационный вход сумматора 22 нулевое цифровое значение, а четвертый мультиплексор 20 замыкает на первый информационный вход сумматора 24 выход первого умножителя 19. Сумматоры 22, 24 ведут циклическое суммирование, складывая результат предыдущего цикла, хранящийся соответственно во втором и третьем регистрах 21, 23, с текущим значением. После n - k + 1 в сумматоре 22 результат суммирование равен нулю, а в сумматоре 24 результат есть второе нормированное слагаемое выражения (1).

Значение n - k + 1 хранится в регистре частоты среза 5. Текущее количество сформированных составляющих сигнала непрерывно подсчитывается счетчиком адреса 2. Блок сравнения 6 непрерывно сравнивает содержимое счетчика адреса 2 с заданным числом n - k + 1. При их выравнивании на выходе блока сравнения 6 вырабатывается сигнал, который сбрасывает в ноль триггер 7. По сигналу триггера 7 третий мультиплексор 18 подключает к первому информационному входу сумматора 22 выход первого умножителя 19, а четвертый мультиплексор 20 подает на сумматор 24 нулевое цифровое значение. В последующие n + k циклы сумматор 22 будет накапливать значения, снимаемые с выхода первого умножителя 19, а сумматор 24 не изменяет накопленную ранее сумму. После прошествия 2n + 1 циклов в сумматорах 22, 24 будут сформированы соответственно первое и второе нормирование слагаемые выражения (1).

Взвешивание сформированных нормированных слагаемых производится во втором и третьем умножителях 27 и 28. При этом на первый информационный вход второго умножителя 27 с первого регистра амплитуды 25 подается цифровое значение амплитуды А1, а на его второй информационный вход значение нормированного первого слагаемого выражения (1). Аналогично на первый информационный вход третьего умножителя 28 со второго регистра амплитуды 26 подается цифровое значение амплитуды А2, а на его второй информационный вход значение нормированного второго слагаемого выражения (1). С приходом управляющего сигнала U1 второй и третий умножитель 27 и 28 производят перемножение входных величин. Результаты умножений передаются на входы сумматора 29, который складывает их по управляющему сигналу U2. На выходе сумматора 29 образуется цифровое значение сигнала (1). С помощью преобразователя код-напряжение 30 цифровое значение сигнала преобразуется в напряжение. Аналоговый фильтр 31 сглаживает высокочастотные ступенчатые составляющие напряжения и формирует на выходе аналоговый сигнал S(t).

При переходе к следующему временному интервалу обработки информации Т в устройстве происходит подготовка к работе ряда блоков. По управляющему сигналу U2 осуществляется обнуление сумматора 13, а также установка новых значений в регистры 5, 8, 9, 25, 26. По сигналу U4сбрасываются в ноль состоянии сумматоров 22, 24. После этого устройство вновь подготовлено к работе и выполняет действия, описанные выше, в новом временном интервале Т.

На фиг. 4 показаны возможные формы спектров сформированного случайного сигнала S(t) для трех практических случаев.

При изменении содержимого регистра частоты 8 изменяется несущая средняя частота в спектре сигнала ω . При изменении содержимого регистра ширины спектра 9 изменяется значение Ω и, следовательно, изменяется расстояние между спектральными составляющими и меняется ширина спектра сигнала. Изменение значения в регистре частоты среза 5 приводит к значению частоты ω + k Ω в спектре сигнала, у которой производится излом формы спектра на две части. Содержимое регистров амплитуды 25 и 26 изменяет величины спектральных составляющих частей спектра и средней амплитуды сигнала. Содержимое регистров 5, 8, 9, 25, 26 может оперативно изменяться в реальном времени аппаратно или под управлением внешней ЭВМ. Тем самым может оперативно изменяться форма спектра сигнала.

| название | год | авторы | номер документа |

|---|---|---|---|

| УНИВЕРСАЛЬНЫЙ ГЕНЕРАТОР СИГНАЛОВ ПРОИЗВОЛЬНОЙ ФОРМЫ | 1994 |

|

RU2060536C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ НИЗКОЧАСТОТНЫХ ДОПЛЕРОВСКИХ СИГНАЛОВ | 1985 |

|

SU1281125A1 |

| Система управления вибростендом | 1984 |

|

SU1275396A1 |

| ФОРМИРОВАТЕЛЬ СИГНАЛОВ МНОГОЧАСТОТНОЙ ЧАСТОТНОЙ ТЕЛЕГРАФИИ | 2002 |

|

RU2212110C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

| Устройство для вычисления скользящего спектра | 1986 |

|

SU1363240A1 |

| ФОРМИРОВАТЕЛЬ СИГНАЛОВ МНОГОЧАСТОТНОЙ ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ ТЕЛЕГРАФИИ | 2002 |

|

RU2233552C2 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2004 |

|

RU2260195C1 |

| Цифровой коррелятор | 1983 |

|

SU1129621A1 |

| Устройство для вычисления функций | 1985 |

|

SU1280391A1 |

Изобретение относится к вычислительной технике и может найти применение в генераторах сигналов сложной формы, а также в моделирующих системах, предназначенных для исследования радиотехнических систем. Цель изобретения - расширение области применения за счет формирования сигналов с изменяющейся формой спектра. Устройство содержит генератор 1 тактовых импульсов, счетчик адреса 2, дешифратор управления 3, дешифратор состояния 4, регистр частоты среза 5, блок сравнения 6, триггер 7, регистр частоты 8, регистр ширины спектра 9, мультиплексоры 10 и 11, регистр 12, сумматоры 13, 16, 22, 24, 29, блоки постоянной памяти 14, 17, блок памяти 15, мультиплексоры 18, 20, умножитель 19, регистры 21, 23, регистры амплитуды 25 и 26, умножители 27 и 28, преобразователь код-напряжение 30, аналоговый фильтр 31. 4 ил.

УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ПСЕВДОСЛУЧАЙНОГО СИГНАЛА, содержащее аналоговый фильтр, преобразователь код-напряжение, три умножителя, четыре сумматора, два блока постоянной памяти, блок памяти, регистр частоты, регистр ширины спектра, первый регистр амплитуды, счетчик адреса и генератор тактовых импульсов, выход которого подключен к счетному входу счетчика адреса, первый информационный выход которого подключен к адресным входам блока памяти и первого блока постоянной памяти, выход которого подключен к первому информационному входу первого умножителя, второй информационный вход которого подключен к выходу второго блока постоянной памяти, адресный вход которого соединен с информационным входом блока памяти и подключен к выходу первого сумматора, первый информационный вход которого подключен к выходу блока памяти, выход второго сумматора подключен к второму информационному входу первого сумматора, выход третьего сумматора подключен к первому информационному входу второго умножителя, второй информационный вход которого подключен к выходу первого регистра амплитуды, информационный вход которого является входом задания первой амплитуды устройства, входами задания частоты и ширины спектра являются информационные входы соответственно регистра частоты и регистра ширины спектра, выход четвертого суматора подключен к первому информационному входу третьего умножителя, выход преобразователя код-напряжение подключен к входу аналогового фильтра, выход которого является информационным выходом устройства, отличающееся тем, что, с целью расширения области применения за счет формирования сигналов с регулируемой формой спектра, в него введены пятый сумматор, три регистра, четыре мультиплексора, дешифратор состояний, дешифратор управления, регистр частоты среза, блок сравнения, триггер и второй регистр амплитуды, выход которого подключен к второму информационному входу третьего умножителя, выход которого подключен к первому информационному входу пятого сумматора, выход которого подключен к входу преобразователя код-напряжение, выход регистра частоты подключен к первому информационному входу первого мультиплексора, выход которого подключен к первому информационному входу второго сумматора, выход которого подключен к информационному входу первого регистра, выход которого подключен к второму информационному входу первого мультиплексора, выход регистра ширины спектра подключен к первому и второму информационным входам второго мультиплексора, выход которого подключен к второму информационному входу второго сумматора, выход региста частоты среза подключен к первому входу блока сравнения, выход которого подключен к первому установочному входу триггера, выход которого подключен к управляющим входам третьего и четвертого мультиплексоров, выходы которых подключены к первым информационным выходам соответственно третьего и четвертого сумматора, выходы которых подключены к информационным входам соответственно второго и третьего регистров, выходы которых подключены к вторым информационным входам соответственно третьего и четвертого сумматоров, выход второго умножителя подключен к второму информационному входу пятого сумматора, выход первого умножителя подключен к первому информационным входам соответственно третьего и четвертого мультиплексоров, вторые информационные входы которых подключены к входу задания логического нуля устройства, первый информационный выход счетчика адреса подключен к второму входу блока сравнения и входу дешифратора управления, первый выход которого подключен к тактовым входам второго и третьего умножителей, второй выход дешифратора управления подключен к тактовым входам регистра частоты среза, регистра частоты, регистра ширины спектра, первого и второго регистров амплитуды, второго и пятого сумматоров, третий выход дешифратора управления подключен к управляющим входам первого и второго мультиплексоров, четвертый выход дешифратора управления подключен к второму установочному входу триггера и тактовым входам третьего и четвертого сумматоров, второй информационный выход счетчика адреса подключен к входу дешифратора состояний, первый выход которого подключен к тактовым входам первого сумматора, второго и третьего регистров, второй выход дешифратора состояний подключен к входу управления записью/считыванием блока памяти, третий выход дешифратора состояний подключен к тактовому входу первого умножителя и входу обнуления второго сумматора, четвертый выход дешифратора состояний подключен к входам обнуления третьего и четвертого сумматоров и тактовому входу первого регистра, информационные входы регистра частоты среза и второго регистра амплитуды являются соответственно входами задания частоты среза и второй амплитуды устройства.

| Авторское свидетельство СССР N 1358615, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1995-01-09—Публикация

1989-09-18—Подача