Область техники, к которой относится изобретение

Настоящее изобретение относится к системе параллельной обработки данных и способу работы системы параллельной обработки данных.

Уровень техники

Систему параллельной обработки данных иногда используют для ускорения вычислительной обработки данных в компьютере. В системе параллельной обработки данных такую обработку осуществляют параллельно множеством компьютеров. Известны системы параллельной обработки данных двух типов - системы параллельной обработки данных с совместно используемой (общей) памятью и системы параллельной обработки с распределенной памятью.

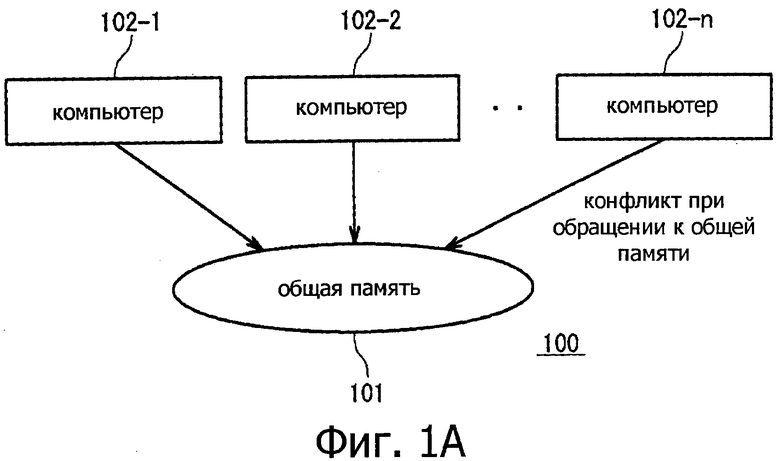

Фиг.1A представляет концептуальную схему, показывающую пример системы параллельной обработки данных с общей памятью. Как показано на фиг.1A, система 100 параллельной обработки данных содержит множество компьютеров 102 (с 102-1 по 102-n) и общую память 101. В системе 100 параллельной обработки данных множество процессов обработки данных назначают соответственно множеству компьютерам 102 (с 102-1 по 102-n). Каждый из множества компьютеров 102 выполняет назначенный ему процесс, обращаясь с этой целью к общей памяти 101.

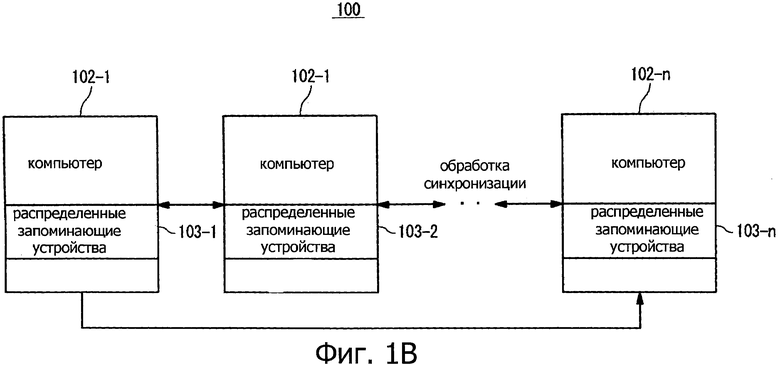

С другой стороны, фиг.1B представляет концептуальную схему, показывающую пример системы параллельной обработки данных с распределенной памятью. Как показано на фиг.1B, система 100 параллельной обработки данных содержит множество компьютеров с 102-1 по 102-n. Компьютеры 102 имеют соответствующие распределенные запоминающие устройства 103 (с 103-1 по 103-n). Каждый компьютер 102 выполняет назначенный ему процесс, обращаясь при этом к распределенной памяти 103. В такой системе 100 параллельной обработки данных необходима синхронизационная обработка для выравнивания данных, записанных в распределенных запоминающих устройствах 103, для множества компьютеров 102. Иными словами, когда в каждом компьютере 102 завершается выполнение назначенной ему обработки, проводится сеанс связи между множеством компьютеров 102 для копирования результата обработки, записанного в распределенном запоминающем устройстве каждого компьютера 102 в распределенные запоминающие устройства 103 других компьютеров 102. После этого каждый компьютер 102 выполняет следующую назначенную ему обработку.

Подобный способ описан в Патентной литературе 1 (Патент Японии No. 2,559,918), где множество независимо работающих компьютеров соединены в виде системы параллельной обработки данных с распределенной памятью. Такая система параллельной обработки данных с распределенной памятью содержит секцию регистра запроса синхронизации для передачи запроса синхронизации независимо от каждого компьютера и сохранения сигнала запроса синхронизации; секцию определения синхронизации для обнаружения сигналов запроса синхронизации от секций регистра запроса синхронизации всех компьютеров; секцию регистра детектора синхронизации для обнаружения факта синхронизации на основе результатов распределенного определения; секцию регистра запроса статуса в каждом компьютере для независимой передачи запроса статуса относительно того, выполняет ли каждый компьютер соответствующую обработку заданным образом и для сохранения сигнала запроса статуса; секцию определения статуса для определения, присутствуют ли сигналы запроса статуса от всех регистров запроса статуса всех компьютеров; секцию распределения статуса для распределения результатов определения всем компьютерам; и секцию регистра детектора статуса для определения статуса на основе результатов определения, распределяемых секцией распределения статуса, и результатов определения, распределяемых секцией распределения синхронизации. Таким образом, можно определить статусы всех компьютеров, когда между всеми этими компьютерами установлена синхронизация.

Список литературы

Патентная литература 1 Патент Японии No. 2,559,918

Раскрытие изобретения

Как показано на фиг.1A, в системе 100 параллельной обработки данных с общей памятью множество компьютеров 102 обращаются к одной и той же общей памяти 101. Поэтому возможны ситуации, когда обращения к памяти от множества разных компьютеров 102 конкурируют один с другим. Если такие конфликты обращений к памяти происходят часто, производительность и качество выполнения обработки улучшить невозможно.

С другой стороны, как показано на фиг.1B, в системе 100 параллельной обработки данных с распределенной памятью конфликты обращений не возникают. Однако необходимо выполнить процедуру синхронизации. Для осуществления такой процедуры синхронизации каждый компьютер 102 должен обладать усложненной функцией управления.

Поэтому одной из целей настоящего изобретения является создание системы параллельной обработки данных и способа работы системы параллельной обработки данных, в которых можно улучшить производительность и качество обработки данных без использования усложненной функции управления.

Система параллельной обработки данных согласно настоящему изобретению содержит множество компьютеров, соединенных один с другими через сеть связи, при этом указанные компьютеры выполнены с возможностью обращения один к другому и распределенного выполнения множества обработок. Каждый из множества компьютеров содержит операционный процессорный модуль для выполнения назначенной обработки, локальную группу запоминающих устройств, содержащую первую область памяти и вторую область памяти, и схему управления вводом/выводом. Операционный процессорный модуль выполнен с возможностью исполнения назначенной обработки с использованием первой области памяти в качестве места назначения для обращений в течение первого периода и выполнения назначенной обработки с использованием второй области памяти в качестве места назначения для обращений в течение второго периода, следующего после первого периода. Схема управления вводом/выводом содержит секцию обновления для обновления данных, хранящихся в локальной группе запоминающих устройств, в соответствии с самыми последними данными посредством осуществления связи между множеством компьютеров. Секция обновления выполнена с возможностью осуществления обновления данных, хранящихся в первой области памяти, в течение второго периода.

Согласно настоящему изобретению, поскольку каждый компьютер выполняет назначенную ему обработку с использованием локальной группы запоминающих устройств в качестве мест назначения обращения, конфликты при доступе к памяти не возникают никогда. Кроме того, в каждом компьютере выполнение обработки с использованием первой области памяти в качестве места назначения для обращений происходит в течение первого периода. Затем в течение второго периода происходит выполнение указанной обработки с использованием второй области памяти в качестве места назначения для обращений. Кроме того, данные, хранящиеся в первой области памяти, обновляют в течение второго периода. Иными словами, в течение второго периода выполнение обработки с использованием второй области памяти в качестве места назначения для обращений и обновление данных в первой области памяти происходят параллельно. Для осуществления процедуры синхронизации нет необходимости останавливать выполнение обработки в каждом компьютере. Поэтому можно повысить производительность выполнения процесса в системе параллельной обработки данных.

Способ работы системы параллельной обработки данных согласно настоящему изобретению представляет собой способ работы системы параллельной обработки данных, содержащей множество компьютеров, соединенных один с другим через сеть связи, так что они могут обращаться один к другому. Каждый из указанного множества компьютеров содержит операционный процессорный модуль, выполненный с возможностью исполнения назначенного процесса, локальную группу запоминающих устройств, содержащую первую область памяти и вторую область памяти, и схему управления вводом/выводом. Способ работы системы включает выполнение обработки посредством операционного процессорного модуля с использованием первой области памяти в качестве места назначения для обращений в течение первого периода; выполнение обработки посредством операционного процессорного модуля с использованием второй области памяти в качестве места назначения для обращений в течение второго периода, следующего после первого периода; и обновление данных, сохраняемых в локальной группе запоминающих устройств, в соответствии с самыми последними данными по командам схемы управления вводом/выводом путем осуществления связи между множеством компьютеров. Процедура обновления включает в себя обновление данных, хранящихся в первой области памяти, в течение второго периода.

Согласно настоящему изобретению предложены система параллельной обработки данных и способ работы указанной системы параллельной обработки данных, позволяющие улучшить качество и производительность обработки данных без использования сложной функции управления.

Краткое описание чертежей

Фиг.1A представляет концептуальную схему, показывающую пример системы параллельной обработки данных с общей памятью;

фиг.1B представляет концептуальную схему, показывающую пример системы параллельной обработки данных с распределенной памятью;

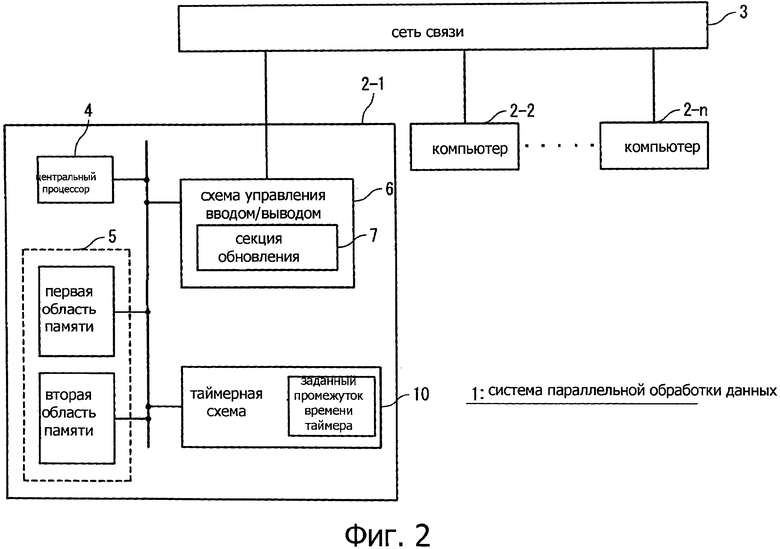

фиг.2 представляет упрощенную схему системы параллельной обработки данных согласно первому варианту осуществления;

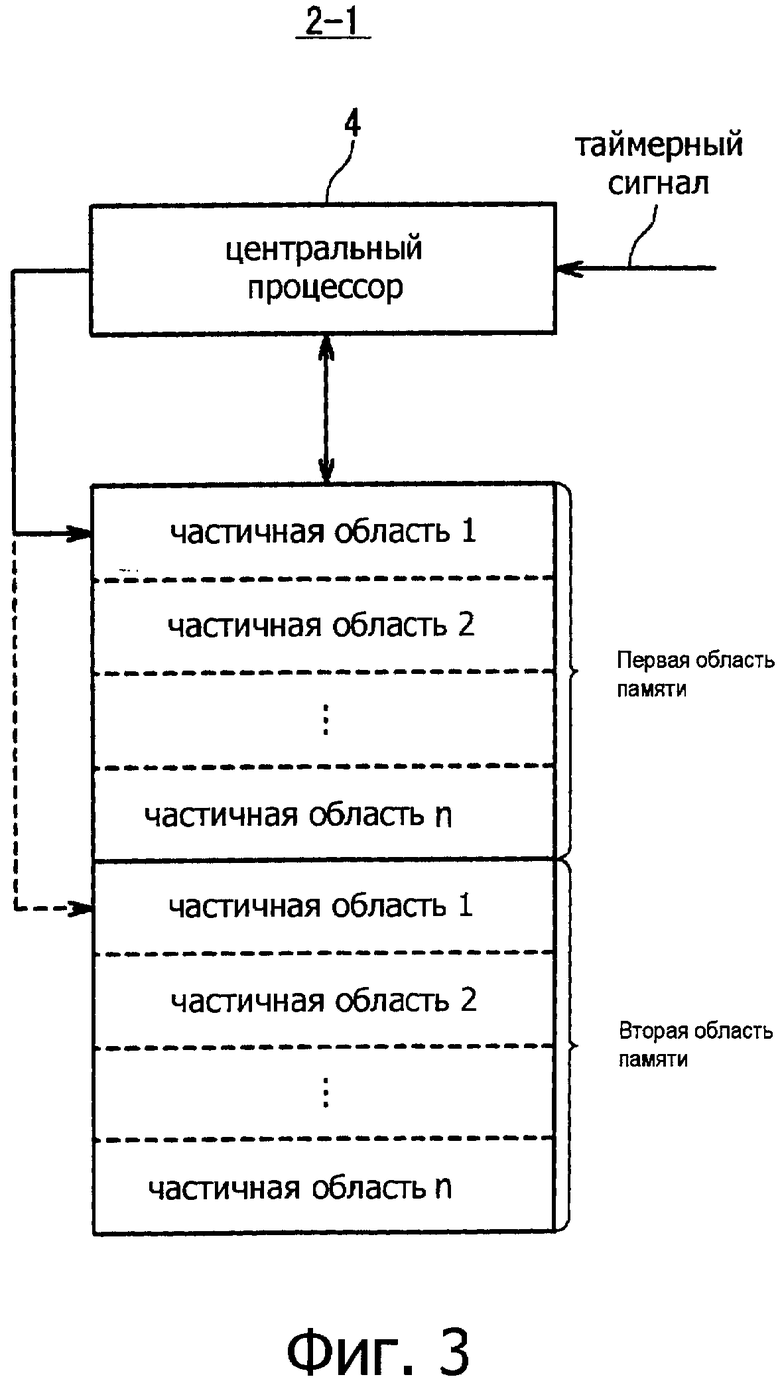

фиг.3 представляет концептуальную схему, показывающую пространство памяти центрального процессора CPU в каждом компьютере;

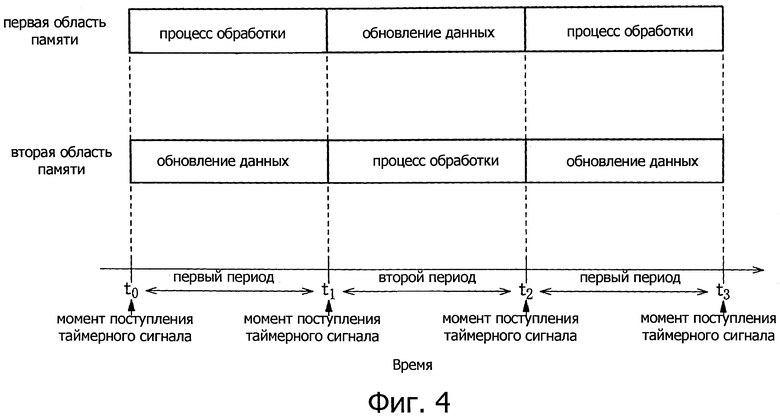

фиг.4 представляет диаграмму, показывающую способ работы системы параллельной обработки данных;

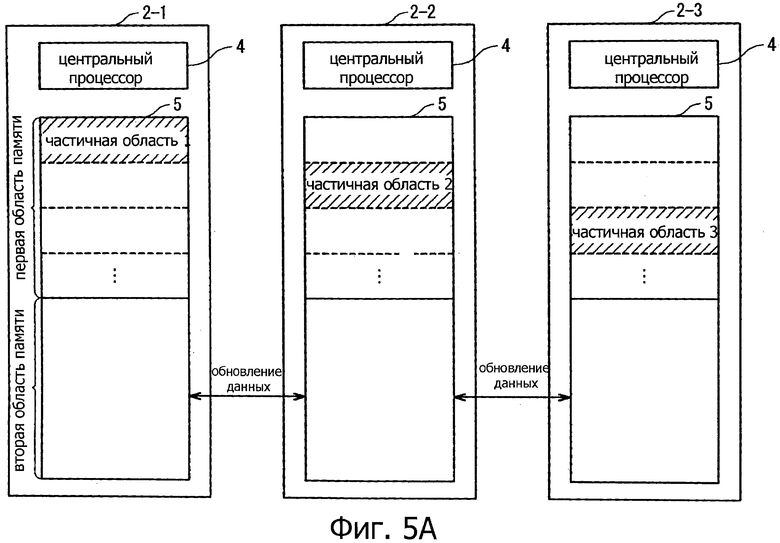

фиг.5A представляет диаграмму, показывающую пример работы в течение первого периода;

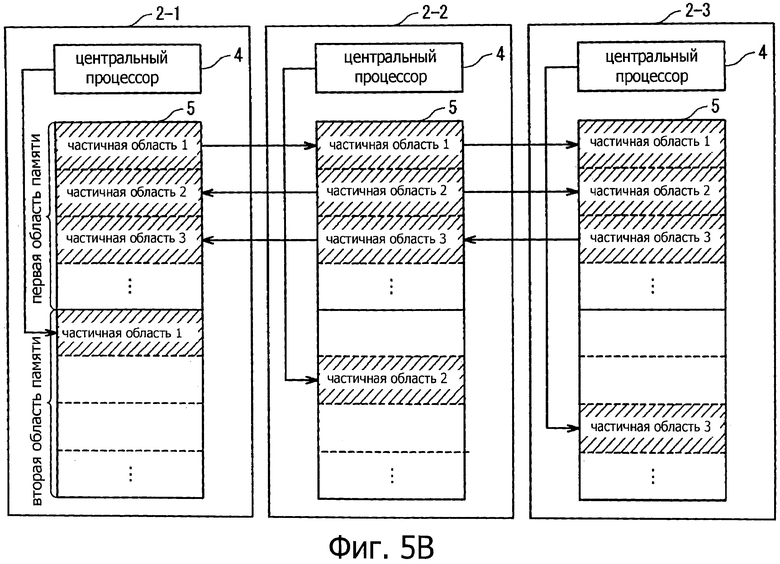

фиг.5B представляет диаграмму, показывающую пример работы в течение второго периода;

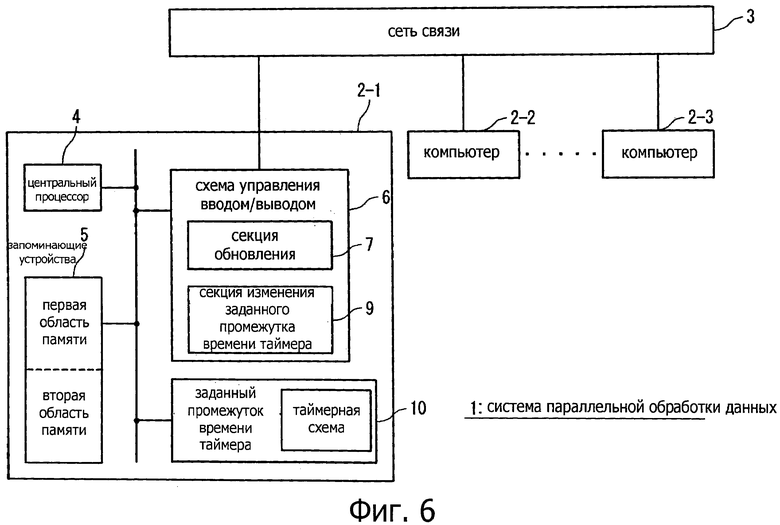

фиг.6 представляет упрощенную схему системы параллельной обработки данных согласно второму варианту;

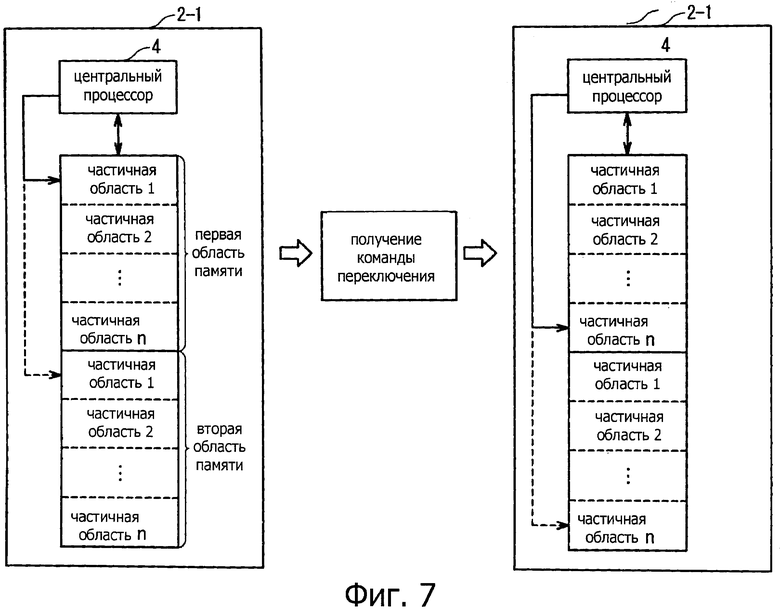

фиг.7 представляет диаграмму, показывающую способ работы системы параллельной обработки данных согласно третьему варианту; и

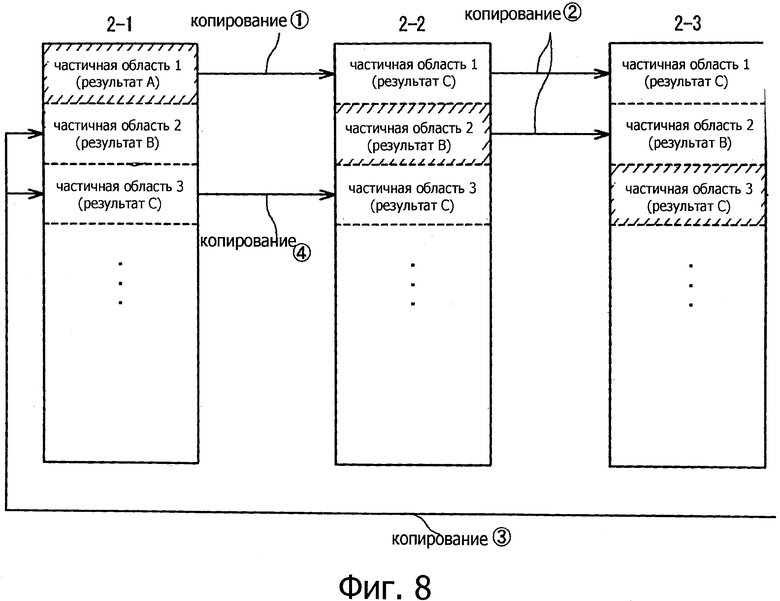

фиг.8 представляет диаграмму, показывающую пример процедуры обновления данных.

Осуществление изобретения

Варианты настоящего изобретения будут описаны ниже со ссылками на прилагаемые чертежи.

Первый вариант осуществления

Фиг.2 представляет упрощенную схему системы 1 параллельной обработки данных согласно рассматриваемому варианту. Как показано на фиг.2, система 1 параллельной обработки данных содержит множество компьютеров с 2-1 по 2-n, причем эти компьютеры соединены один с другими через сеть 3 связи, чтобы иметь возможность обращаться и получать доступ один к другому. Программа, выполняемая системой 1 параллельной обработки данных, содержит множество процессов. Эти множество процессов назначают соответственно указанным множеством компьютеров с 2-1 по 2-n, которые выполняют указанные процессы параллельно.

Каждый из множества компьютеров с 2-1 по 2-n содержит CPU (центральный процессор) 4, локальную группу 5 запоминающих устройств и схему 6 управления I/O (вводом/выводом). Кроме того, по меньшей мере один из множества компьютеров с 2-1 по 2-n имеет таймерную схему. В рассматриваемом варианте таймерная схема 10 находится в компьютере 2-1. Процессор CPU 4, локальная группа 5 запоминающих устройств, схема 6 управления вводом/выводом и таймерная схема 10 соединены одно с другим через шину данных. В каждом компьютере 2 процессор CPU 4 выполняет назначенный процесс с использованием данных, сохраняемых в локальной группе 5 запоминающих устройств.

Таймерная схема 10 генерирует таймерный сигнал и имеет функцию передачи этого сигнала множеству компьютеров с 2-1 по 2-n. В таймерной схеме 10 предварительно задают промежуток времени таймера. Каждый раз, когда истекает очередной заданный промежуток времени таймера, таймерная схема 10 генерирует таймерный сигнал и передает его процессору CPU 4 и на схему 6 управления вводом/выводом. Таймерный сигнал передают на схему 6 управления вводом/выводом и затем передают другим компьютерам с (2-2 по 2-n) через сеть 3 связи. В каждом из этих других компьютеров (с 2-2 по 2-n) таймерный сигнал передают процессору CPU 4 через схему 6 управления вводом/выводом.

Указанная локальная группа 5 запоминающих устройств имеет первую область памяти и вторую область памяти. На фиг.3 представлена концептуальная схема, показывающая пространство памяти процессора CPU 4 в каждом компьютере 2. Как показано на фиг.3, в этом пространстве памяти первая область памяти и вторая область памяти назначены различным зонам.

В каждой области - первой области памяти и второй области памяти, выделены множество частичных областей. Это множество частичных областей назначены соответственно множеству компьютерам с 2-1 по 2-n.

Процессор CPU 4 выполняет назначенную обработку с использованием либо первой области памяти, либо второй области памяти в качестве места назначения для обращений и записывает результат выполнения назначенного процесса в частичной области, назначенной его собственному компьютеру. Например, в компьютере 2-1 процессор CPU 4 записывает результат выполнения назначенного процесса в частичной области 1 (частичная область, соответствующая компьютеру 2-1) первой области памяти или второй области памяти. Кроме того, процессор CPU 4 конфигурирован для переключения места назначения для обращений между первой областью памяти и второй областью памяти, каждый раз, когда он принимает таймерный сигнал. Иными словами, каждый раз, когда истекает заданный промежуток времени таймера, процессор CPU 4 переключает область памяти, являющуюся местом назначения для обращений.

Если снова обратиться к фиг.2, схема 6 управления вводом/выводом соединена с сетью 3 связи и имеет функцию передачи и приема данных к и от других компьютеров 2. Как показано на фиг.2, схема 6 управления вводом/выводом снабжена секцией 7 обновления. Эта секция 7 обновления имеет функцию связи с другими компьютерами 2, чтобы обновлять данные, хранящиеся в локальной группе 5 запоминающих устройств, в соответствии с самыми последними данными.

Далее будет описан способ работы системы 1 параллельной обработки данных.

На фиг.4 представлена диаграмма, показывающая способ работы системы 1 параллельной обработки данных. Эта фиг.4 показывает зависимость процесса обработки и обновления данных от времени в первой области памяти и во второй области памяти. На фиг.4, во-первых, момент времени, когда таймерная схема 10 генерирует и передает таймерный сигнал, обозначен как момент t0. Момент времени, когда таймерный сигнал передают следующий раз после момента t0, указан как момент t1. Момент времени, когда таймерный сигнал передают следующий раз после момента t1, указан как момент t2. Момент времени, когда таймерный сигнал передают следующий раз после момента t2, указан как момент t3.

Когда таймерный сигнал передан в момент t0, процессор CPU 4 выполняет назначенную обработку с использованием первой области памяти в качестве места назначения для обращений в течение периода времени от момента t0 до момента t1, когда поступит следующий таймерный сигнал. Когда приходит таймерный сигнал в момент t1, процессор CPU 4 переключает место назначения для обращений на вторую область памяти. Иными словами, процессор CPU 4 выполняет назначенный процесс с использованием второй области памяти в качестве места назначения для обращений в течение периода времени от момента t1 до момента t2. Когда приходит таймерный сигнал в момент t2, процессор CPU 4 снова переключает место назначения для обращений на первую область памяти. Затем процессор CPU 4 выполняет процесс с использованием первой области памяти в качестве места назначения для обращений в течение периода времени (первый период) от момента t2 до момента t3, аналогично периоду времени от момента t0 до момента t1.

С другой стороны, в период времени от момента t0 до момента t1 секция 7 обновления в составе схемы 6 управления вводом/выводом обновляет данные, хранящиеся во второй области памяти. Кроме того, в период времени от момента t1 до момента t2 секция 7 обновления осуществляет обновление данных, хранящихся в первой области памяти. Затем, в период времени от момента t2 до момента t3 секция 7 обновления осуществляет обновление данных, хранящихся во второй области. Иными словами, в рассматриваемом варианте в период времени (первый период времени), в течение которого процессор CPU 4 выполняет назначенный процесс с использованием первой области памяти в качестве места назначения для обращений, секция 7 обновления осуществляет обновление данных, хранящихся во второй области памяти. Кроме того, в период времени (второй период времени), в течение которого процессор CPU 4 выполняет назначенный процесс с использованием второй области памяти в качестве места назначения для обращений, секция 7 обновления осуществляет обновление данных, хранящихся в первой области памяти.

Пример работы в течение первого периода и второго периода будет подробно рассмотрен со ссылками на фиг.5A и фиг.5B.

На фиг.5A представлена диаграмма, показывающая пример работы в течение первого периода. На фиг.5A показаны рабочие состояния компьютера 2-1, компьютера 2-2 и компьютера 2-3. Как описано выше, в течение первого периода времени процессор CPU 4 выполняет назначенную обработку с использованием первой области памяти. В итоге, в примере, изображенном на фиг.5A, результат обработки записывают в частичной области 1 (частичная область, соответствующая компьютеру 2-1) в составе первой области в компьютере 2-1. Кроме того, в компьютере 2-2 результат обработки записывают в частичной области 2 (частичная область, соответствующая компьютеру 2-2) в первой области памяти. Далее, в компьютере 2-3 результат обработки записывают в частичной области 3 (частичная область, соответствующая компьютеру 2-3) в первой области памяти. С другой стороны, в это время обновляют данные, хранящиеся во второй области памяти, посредством секции 7 обновления.

На фиг.5B представлена диаграмма, показывающая пример работы в течение второго периода. Как описано выше, в течение второго периода происходит обновление данных, хранящихся в первой области памяти, посредством секции 7 обновления. Иными словами, как показано на фиг.5B, данные, записанные в частичной области 1 в составе первой области памяти компьютера 2-1, копируют в частичную область 1 в составе первой области памяти каждого из прочих компьютеров - компьютера 2-2 и компьютера 2-3. Аналогично, данные, записанные в частичной области 2 в составе первой области памяти компьютера 2-2, копируют в частичную область 2 в составе первой области памяти каждого из прочих компьютеров - компьютера 2-1 и компьютера 2-3. Аналогично, данные, записанные в частичной области 3 в составе первой области памяти компьютера 2-3, копируют в частичную область 3 в составе первой области памяти каждого из прочих компьютеров - компьютера 2-1 и компьютера 2-2. Таким образом, данные, записанные в первой области памяти в каждом компьютере 2, оказываются обновлены в соответствии с самыми последними данными. С другой стороны, процессор CPU 4 выполняет назначенный процесс с использованием второй области памяти. Как показано на фиг.5B, процессор CPU 4 записывает результаты выполнения процесса в частичной области 1 в составе второй области памяти компьютера 2-1. Кроме того, в компьютере 2-2 результаты выполнения процесса записывают в частичной области 2 в составе второй области памяти. В компьютере 2-3 результаты выполнения процесса записывают в частичной области 3 в составе второй области памяти. Данные, записанные во второй области памяти каждого компьютера 2, копируют во вторые области памяти в течение следующего первого периода.

Как описано выше, согласно настоящему изобретению, пока назначенная обработка выполняется с использованием первой области памяти, производится обновление второй области памяти, а пока назначенная обработка выполняется с использованием второй области памяти, производится обновление первой области памяти. Поэтому в течение каждого периода каждый компьютер 2 может выполнять назначенную ему обработку в автономном режиме и не нуждается в проведении процедуры синхронизации. Таким образом, можно улучшить производительность и качество обработки данных без инсталлирования сложной функции управления для осуществления процедуры синхронизации.

Следует отметить, что рассматриваемый вариант описан для случая, когда в локальной группе 5 запоминающих устройств выделены первая область памяти и вторая область памяти, а место назначения для обращений переключают между первым периодом и вторым периодом. Здесь, в пределах локальной группы 5 запоминающих устройств могут быть выделены 3 или более областей памяти. В таком случае, в период, когда в каждом компьютере 2 назначенную обработку выполняют с использованием одной из областей памяти, производится обновление данных в других областях памяти. Даже в такой конфигурации можно получить такой же эффект, как и в рассматриваемом варианте.

Кроме того, желательно, чтобы первая область памяти и вторая область памяти были назначены в разных запоминающих устройствах. Иными словами, желательно, чтобы в каждом компьютере 2 локальная группа запоминающих устройств содержала первое запоминающее устройство и второе запоминающее устройство, так что первую область памяти назначают в первом запоминающем устройстве, а вторую область памяти назначают во втором запоминающем устройстве. В такой конфигурации процессору CPU 4 достаточно обращаться только к первому запоминающему устройству в течение первого периода и обращаться только ко второму запоминающему устройству в течение второго периода. Поэтому режим работы, когда процессор CPU 4 обращается к каждому запоминающему устройству, и режим работы, когда секция 7 обновления обращается к каждому запоминающему устройству, могут быть полностью разделены. Это становится возможным, поскольку операции обращения к памяти со стороны процессора CPU 4 и операции обращения к памяти со стороны секции 7 обновления уже не конкурируют, так что можно еще больше улучшить производительность и качество обработки данных.

Второй вариант

Далее будет рассмотрен второй вариант настоящего изобретения. На фиг.6 представлена упрощенная схема, показывающая систему 1 параллельной обработки данных согласно рассматриваемому варианту. Как показано на фиг.6, в рассматриваемом варианте в схему 6 управления вводом/выводом добавлена секция 9 изменения заданного промежутка времени таймера. Поскольку в остальных моментах второй вариант имеет такую же конфигурацию, как и первый вариант, подробное описание будет опущено.

Секция 9 изменения заданного промежутка времени таймера имеет функцию изменения заданного промежутка времени для таймерной схемы 10. Например, секция 9 изменения заданного промежутка времени таймера изменяет настройки таймерной схемы в ответ на команду изменения заданного промежутка времени таймера, получаемую от пользователя через устройство ввода (не показано), соединенное с сетью связи. Во время последующей работы временная протяженность первого периода и второго периода становится равной измененному заданному промежутку времени таймера.

Рассматриваемый вариант позволяет подбирать наилучшую продолжительность заданного промежутка времени таймера в зависимости от характера программы, выполняемой в системе 1 параллельной обработки данных. Например, для выполнения сложного процесса можно установить большую величину заданного промежутка времени таймера. Кроме того, становится возможным повысить производительность и качество обработки данных в реальном времени, если установить короткий заданный промежуток времени таймера.

Третий вариант

Далее будет рассмотрен третий вариант настоящего изобретения. В рассматриваемом варианте процессор CPU может в каждом компьютере 2 заменять частичную область памяти, в которую записывают результат выполнения обработки, другой частичной областью. Поскольку во всех остальных моментах третий вариант имеет такую же конфигурацию, как и описанные выше варианты, подробное описание будет опущено.

На фиг.7 представлена диаграмма, показывающая способ работы системы 1 параллельной обработки данных согласно рассматриваемому варианту. В каждом компьютере 2 согласно рассматриваемому варианту в каждой из областей - первой области памяти и второй области памяти, выделены по множеству частичных областей для установки соответствия со всеми компьютерами 2. На фиг.7 представлена упрощенная схема конфигурации компьютера 2-1. Как показано на фиг.7, в компьютере 2-1 процессор CPU 4 записывает результат выполнения процесса в частичную область (частичная область 1), соответствующую его собственному компьютеру. Здесь, когда число компьютеров, соединенных с сетью 3 связи изменяется, каждый компьютер 2 должен функционировать, как другие компьютеры. В таком случае, в рассматриваемом варианте процессору CPU 4 каждого компьютера 2 передают команду, требующую изменить частичную область, являющуюся местом назначения записи. Например, такую команду передает устройство ввода (не показано), соединенное с сетью 3 связи. В каждом компьютере 2 процессор CPU 4 обновляет (перезаписывает) частичную область, являющуюся местом назначения для записи результатов обработки данных, в ответ на принятую команду. В примере, показанном на фиг.7, частичную область, являющуюся местом назначения для записи данных, в компьютере 2-1 изменяют от частичной области 1 к частичной области n. Таким образом, становится возможным сделать так, чтобы компьютер 2-1 работал в качестве компьютера 2-n.

Согласно рассматриваемому варианту в каждой из областей - первой области памяти и второй области памяти, выделены по множеству частичных областей для установки соответствия со всеми компьютерами 2. Поэтому становится возможным сделать так, чтобы каждый компьютер 2 функционировал в качестве другого компьютера, соединенного с сетью 3 связи, изменив частичную область, служащую местом назначения записи результатов обработки данных. Следовательно, даже если число компьютеров, соединенных с сетью 3 связи изменяется, система 1 параллельной обработки данных может продолжать работать без каких-либо несоответствий. Это позволяет легко реализовать резервирование и расширяемость для системы 1 параллельной обработки данных.

Четвертый вариант

Далее будет рассмотрен четвертый вариант настоящего изобретения. В рассматриваемом варианте модифицирована работа секции 7 обновления. Поскольку четвертый вариант во всем, кроме этого момента, является таким же, как первый вариант, подробное описание опущено.

В рассматриваемом варианте секция 7 обновления осуществляет процедуру обновления данных, выполняя операции копирования и операции ретрансляции между множеством компьютеров 2. На фиг.8 представлена диаграмма, показывающая пример процедуры обновления данных. Следует отметить, что в примере, показанном на фиг.8, число компьютеров 2, соединенных с сетью 3 связи, равно трем. На фиг.8 показаны состояния первых областей памяти в компьютере 2-1, компьютере 2-2 и в компьютере 2-3. Предполагается, что в течение первого периода в примере, показанном на фиг.8, результат A обработки данных записывают в частичной области 1 для компьютера 2-1, результат B обработки данных записывают в частичной области 2 для компьютера 2-2 и результат C обработки данных записывают в частичной области 3 для компьютера 2-3 (участки, заштрихованные наклонными линиями на фиг.8). В таком случае, в течение второго периода данные (результат A обработки), записанные в частичной области 1, сначала копируют из компьютера 2-1 на компьютер 2-2. Затем данные (результат A обработки и результат B обработки), записанные в частичной области 1 и в частичнойобласти 2, копируют из компьютера 2-2 на компьютер 2-3. Далее данные (результаты B и C обработки данных), записанные в частичной области 2 и в частичной области 3, копируют из компьютера 2-3 на компьютер 2-1. Наконец, данные (результат C обработки данных), записанные в частичной области 3, копируют из компьютера 2-1 на компьютер 2-2. Таким образом, результаты с A по C обработки данных сохраняют в первой области памяти в компьютерах 2, так что данные в этой первой области памяти оказываются обновлены в соответствии с самыми последними данными. Процедура обновления второй области памяти происходит точно так же.

Согласно рассматриваемому варианту данные, сохраняемые в локальной группе 5 запоминающих устройств, копируют (по порядку) для ретрансляции между всеми компьютерами 2. Поэтому, даже если число компьютеров 2, соединенных с сетью 3 связи, изменяется, можно легко унифицировать данные, сохраняемые в локальных группах 5 запоминающих устройств во всех компьютерах 2.

Здесь были описаны варианты настоящего изобретения с первого по четвертый. Следует отметить, что эти варианты не являются независимыми, так что при использовании их можно сочетать в тех пределах, в каких такое сочетание не вызывает несоответствий.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПАРАЛЛЕЛЬНАЯ ПРОЦЕССОРНАЯ СИСТЕМА | 1991 |

|

RU2084953C1 |

| УСТРОЙСТВО ХРАНЕНИЯ РАЗЛИЧНЫХ ВЕРСИЙ НАБОРА ДАННЫХ В ОТДЕЛЬНЫХ ОБЛАСТЯХ ПАМЯТИ И СПОСОБ ОБНОВЛЕНИЯ НАБОРА ДАННЫХ В ПАМЯТИ | 1999 |

|

RU2235356C2 |

| СПОСОБ И СИСТЕМА ДЛЯ КОНТРОЛЯ БИОМЕТРИЧЕСКИХ ДАННЫХ | 2014 |

|

RU2616540C2 |

| СЕРВЕР И СПОСОБ РАБОТЫ С СЕРВЕРОМ, ЭНЕРГОНЕЗАВИСИМЫЙ МАШИНОЧИТАЕМЫЙ НОСИТЕЛЬ ДАННЫХ, МОБИЛЬНЫЙ КЛИЕНТСКИЙ ТЕРМИНАЛ И СПОСОБ РАБОТЫ С ТЕРМИНАЛОМ | 2010 |

|

RU2538343C2 |

| СРЕДСТВО РАЗДЕЛЕННОЙ ЗАГРУЗКИ/СОХРАНЕНИЯ И КОМАНДА ДЛЯ НЕГО | 2010 |

|

RU2554546C2 |

| ГРАФИЧЕСКАЯ СИСТЕМА С КОНФИГУРИРУЕМЫМИ КЭШАМИ | 2007 |

|

RU2412469C2 |

| СПОСОБЫ И СИСТЕМЫ ЗАГРУЗКИ ДАННЫХ В ХРАНИЛИЩА ВРЕМЕННЫХ ДАННЫХ | 2012 |

|

RU2599538C2 |

| СПОСОБ И СИСТЕМА ДЛЯ УПРАВЛЕНИЯ ВЫПОЛНЕНИЕМ ВНУТРИ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ | 2012 |

|

RU2577487C2 |

| СПОСОБ ОБРАБОТКИ ДАННЫХ ПОЗИЦИОНИРОВАНИЯ | 2008 |

|

RU2501087C2 |

| АППАРАТУРА ОБРАБОТКИ ИНФОРМАЦИИ, УСТРОЙСТВО, СПОСОБ УПРАВЛЕНИЯ АППАРАТУРОЙ ОБРАБОТКИ ИНФОРМАЦИИ И НОСИТЕЛЬ ХРАНЕНИЯ ДАННЫХ | 2008 |

|

RU2448422C2 |

Группа изобретений относится к области вычислительной техники и может быть использована для параллельной обработки данных. Техническим результатом является улучшение производительности и качества обработки данных. Система содержит множество компьютеров, соединенных один с другими через сеть связи, каждый из которых содержит операционный процессорный модуль для выполнения назначенной компьютеру обработки, локальную группу запоминающих устройств, имеющую первую область памяти и вторую область памяти, и схему управления вводом/выводом. Операционный процессорный модуль выполняет обработку с использованием первой области памяти в качестве места назначения для обращений в течение первого периода и обработку с использованием второй области памяти в качестве места назначения для обращений в течение второго периода. Схема управления вводом/выводом содержит секцию обновления для обновления данных, хранящихся в локальной группе запоминающих устройств, в соответствии с последними данными. Секция обновления выполнена с возможностью обновления данных, хранящихся в первой области памяти, в течение второго периода. 2 н. и 6 з.п. ф-лы, 10 ил.

1. Система параллельной обработки данных, содержащая:

сеть связи;

множество компьютеров, соединенных один с другими через указанную сеть связи, для распределенного выполнения множества обработок,

при этом каждый из множества компьютеров содержит:

операционный процессорный модуль для выполнения одной назначенной указанному компьютеру обработки из множества обработок;

локальную группу запоминающих устройств, содержащую первую область памяти и вторую область памяти; и

схему управления вводом/выводом,

при этом каждая из первой области памяти и второй области памяти содержит множество частичных областей, соответствующих указанному множеству компьютеров;

причем указанный операционный процессорный модуль каждого компьютера выполнен с возможностью:

осуществления, в течение первого периода, назначенной обработки с использованием первой области памяти в качестве места назначения для обращений, и

осуществления, в течение второго периода, следующего после первого периода, назначенной обработки с использованием второй области памяти в качестве места назначения для обращений, и

при этом схема управления вводом/выводом содержит:

секцию обновления для обновления данных, хранящихся во второй области памяти, в соответствии с последними данными от указанного множества компьютеров посредством осуществления связи между множеством компьютеров в течение первого периода, и

данных, хранящихся в первой области памяти, в соответствии с последними данными от указанного множества компьютеров посредством осуществления связи между множеством компьютеров в течение второго периода.

2. Система параллельной обработки данных по п. 1, в которой схема управления вводом/выводом дополнительно содержит секцию изменения заданного промежутка времени, выполненную с возможностью изменения продолжительности первого периода.

3. Система параллельной обработки данных по п. 1, в которой в каждом из множества компьютеров операционный процессорный модуль выполнен с возможностью

записи результата выполнения назначенной обработки в одну из множества частичных областей, соответствующую указанному компьютеру.

4. Система параллельной обработки данных по п. 3, в которой указанный операционный процессорный модуль выполнен с возможностью изменения частичной области, используемой в качестве места назначения записи результатов выполнения назначенной обработки в другую частичную область.

5. Система параллельной обработки данных по п. 1, в которой секция обновления выполнена с возможностью обновления данных в первой области памяти в течение второго периода посредством копирования указанных данных, хранящихся в первой области памяти, в следующий из множества компьютеров, так что происходит ретрансляция данных, хранящихся в первой области памяти, между множеством компьютеров.

6. Система параллельной обработки данных по любому из пп. 1-5, в которой локальная группа запоминающих устройств содержит множество областей памяти, включающее в себя первую область памяти и вторую область памяти,

при этом указанный операционный процессорный модуль выполнен с возможностью:

осуществления назначенной обработки с использованием первой определенной области памяти из множества областей памяти в качестве места назначения для обращений, и

изменения области памяти, являющейся местом назначения для обращений, на вторую определенную область памяти в качестве другой области из указанного множества областей памяти каждый раз, когда истекает заданный промежуток времени,

при этом схема управления вводом/выводом содержит:

секцию обновления, выполненную с возможностью обновления данных, хранящихся во второй определенной области памяти, в соответствии с последними данными множества компьютеров посредством осуществления связи между множеством компьютеров в течение первого периода, и данных, хранящихся в первой определенной области памяти, в соответствии с последними данными множества компьютеров посредством осуществления связи между множеством компьютеров в течение второго периода.

7. Способ функционирования системы параллельной обработки данных, содержащей множество компьютеров, соединенных один с другим через сеть связи, причем каждый из указанного множества компьютеров содержит:

операционный процессорный модуль для выполнения одной назначенной

указанному компьютеру обработки из множества обработок;

локальную группу запоминающих устройств, содержащую первую область памяти и вторую область памяти; и

схему управления вводом/выводом, и

при этом каждая из первой области памяти и второй области памяти содержит множество частичных областей, соответствующих указанному множеству компьютеров;

причем способ функционирования содержит этапы, на которых:

выполняют с помощью операционного процессорного модуля назначенную обработку с использованием первой области памяти в качестве места назначения для обращений в течение первого периода;

выполняют с помощью операционного процессорного модуля назначенную обработку с использованием второй области памяти в качестве места назначения для обращений в течение второго периода, следующего после первого периода;

обновляют с помощью схемы управления вводом/выводом данные, хранящиеся во множестве частичных областей во второй области памяти, в соответствии с последними данными множества компьютеров посредством осуществления связи между множеством компьютеров в течение первого периода; и

обновляют с помощью схемы управления вводом/выводом данные, хранящиеся во множестве частичных областей в первой области памяти, в соответствии с последними данными множества компьютеров посредством осуществления связи между множеством компьютеров в течение второго периода.

8. Способ функционирования по п. 7,

дополнительно содержащий этапы, на которых:

выполняют с помощью операционного процессорного модуля назначенную обработку с использованием первой области памяти или второй области памяти в качестве места назначения для обращений;

изменяют с помощью операционного процессорного модуля область памяти, являющуюся местом назначения для обращений, на вторую область памяти или на первую область памяти каждый раз, когда истекает первый период или второй период в качестве заданного промежутка времени; и

обновляют с помощью схемы управления вводом/выводом данные, хранящиеся во второй области памяти или в первой области памяти, в соответствии с последними данными посредством осуществления связи между множеством компьютеров.

| УСТРОЙСТВО для УПРАВЛЕНИЯ ОБМЕНОМ ИНФОРМАЦИЕЙ | 0 |

|

SU269995A1 |

| US 5765202 A, 09.06.1998 | |||

| JP 4260962 A , 16.09.1992 | |||

| US 5842035 A, 24.11.1998 | |||

| ПАРАЛЛЕЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С ПРОГРАММИРУЕМОЙ АРХИТЕКТУРОЙ | 2001 |

|

RU2202123C2 |

Авторы

Даты

2015-08-10—Публикация

2012-02-24—Подача