Настоящее изобретение относится к компьютерным системам, точнее, к функциональным возможностям команд процессора компьютерной системы.

Товарные знаки: IBM® является зарегистрированным товарным знаком International Business Machines Corporation (Армонк, штат Нью-Йорк, США). S/390, Z900, z990 и z10, а также названия других продуктов, используемые в описании, могут являться зарегистрированными товарными знаками или названиями продуктов International Business Machines Corporation или других компаний.

Начиная с появившихся в 60-х годах машин, известных как IBM® System 360, и до настоящего времени усилиями множества высокоодаренных инженеров IBM была создана особая архитектура, которая получила известность как "мэйнфрейм" в силу своей неотъемлемой принадлежности к вычислительной системе и принципы работы которой определяют архитектуру машины путем описания команд, которые могут выполняться путем реализации в "мэйнфрейме" созданных изобретателями IBM команд, которые с учетом их существенной роли в течение многих лет включены в руководство IBM Principles of Operation. Восьмое издание руководства IBM® z/Architecture® Principles of Operation, опубликованное в феврале 2009 г., стало стандартным справочным материалом SA22-7832-07 и включено в описание серверов на основе мэйнфреймов IBM z10®, включая серверы корпоративного класса на основе системы IBM z10®.

На фиг. 1А представлены характерные элементы известной из техники главной компьютерной системы 50. В компьютерной системе также могут применяться другие варианты размещения элементов, которые хорошо известны из техники. Характерный главный компьютер 50 содержит один или несколько ЦП 1, связанных с основным запоминающим устройством (памятью 2 компьютера), а также интерфейсы ввода-вывода для сопряжения с запоминающими устройствами 11 и подключения к сетям 10 для связи с другими компьютерами или SAN и т.п. ЦП 1 совместим с архитектурой, содержащей структурированную систему команд и структурированные функциональные возможности. ЦП 1 может осуществлять динамическую трансляцию 3 адреса (DAT) с целью преобразования адресов программ (виртуальных адресов) в действительный адрес памяти. DAT обычно содержит буфер 7 быстрого преобразования адреса (TLB) для кэширования преобразований, чтобы при последующих доступах к блоку памяти 2 компьютера не требовалась задержка трансляции адреса. Обычно между памятью 2 компьютера и процессором 1 используется кэш-память 9. Кэш-память 9 может являться иерархической и состоящей из кэша большой емкости, доступного для нескольких ЦП, и более быстродействующих кэшей (низкого уровня) меньшей емкости между кэшем большой емкости и каждым ЦП. В некоторых случаях реализации кэши низкого уровня разделены на отдельные кэши низкого уровня для выборки команд и доступа к данным. В одном из вариантов осуществления блок 4 выборки команд вызывает из памяти 2 команду посредством кэш-памяти 9. Команда декодируется в блоке 6 декодирования команд и отправляется (с другими командами в некоторых вариантах осуществления) в блоки 8 выполнения команд. Обычно используется несколько блоков 8 выполнения команд, например, блок выполнения арифметических команд, блок выполнения команд с плавающей точкой и блок выполнения команд перехода. Команда выполняется блоком, который в зависимости от необходимости осуществляет доступ к операндам из определяемых командами регистров или памяти. Если доступ (загрузка или сохранение) к операнду должен осуществляться из памяти 2, блок 5 загрузки/сохранения обычно обрабатывает процедуру доступа под управлением выполняемой команды. Команды могут выполняться в аппаратных схемах или во внутреннем микрокоде (аппаратно-программном обеспечении) или с использованием сочетания того и другого.

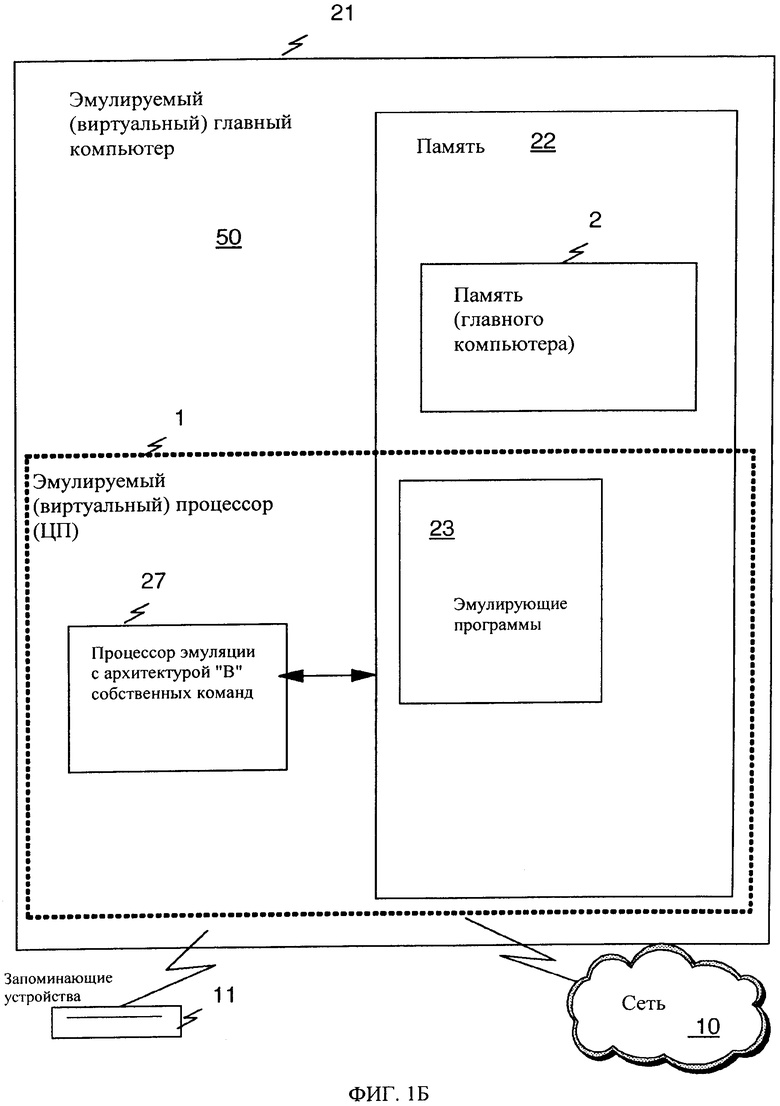

На фиг. 1Б проиллюстрирован один из примеров известной из техники главной компьютерной системы 21 эмуляции, которая эмулирует главную компьютерную систему 50, имеющую главную архитектуру. Главным центральным процессором (ЦП) 1 в главной компьютерной системе 21 эмуляции является главный процессор (или виртуальный главный процессор) эмуляции, представляющий собой процессор 27 эмуляции со структурой собственных команд, отличающейся от структуры команд процессора 1 главного компьютера 50. Главная компьютерная система 21 эмуляции имеет память 22, доступную для процессора 27 эмуляции. В примере осуществления память 22 разделена на память 2 главного компьютера и память 23 программ эмуляции. Память 2 главного компьютера доступна для программ главного компьютера 21 эмуляции в зависимости от архитектуры главного компьютера. Процессор 27 эмуляции выполняет собственные команды структурированной системы команд, структура которых отличается от структуры команд эмулируемого процессора 1 и которые извлекаются из памяти 23 программ эмуляции, и может осуществлять выборку главной команды для выполнения из программы в памяти 2 главного компьютера путем применения одной или нескольких команд из программы контроля последовательности и выборки/декодирования (Sequence & Access/Decode), которая может декодировать выбранную главную команду(-ы) и определять программу выполнения собственных команд с целью эмуляции функции выбранной главной команды. Другие средства, которые предусмотрены в архитектуре главной компьютерной системы 50, могут эмулироваться программами структурированных средств (Architected Facilities Routines), включая такие средства, как, например, регистры общего назначения, управляющие регистры, поддержка подсистемы динамической трансляции адреса и ввода-вывода и кэш-память процессора. Программы эмуляции также могут использовать функции, доступные в процессоре 27 эмуляции (такие как регистры общего назначения и динамическая трансляция виртуальных адресов) для повышения производительности программ эмуляции. Также может быть предусмотрено особое программное обеспечение и механизмы разгрузки, облегчающие процессору 27 эмуляцию функции главного компьютера 50.

В мэйнфрейме структурированные машинные команды используются программаторами, обычно современными программаторами на языке "С" посредством компилирующего приложения. Эти команды, хранящиеся в запоминающей среде, могут выполняться в собственной системе команд сервера IBM® на основе z/Architecture® или в качестве альтернативы в машинах на основе других архитектур. Они могут эмулироваться в существующих и будущих серверах на основе мэйнфреймов IBM® и в других машинах IBM® (например, серверах pSeries® и xSeries®). Они могут выполняться в операционной системе Linux разнообразными машинами, использующими аппаратное обеспечение производства IBM®, Intel, AMD™, Sun Microsystems и других компаний. Помимо выполнения этим аппаратным обеспечением на основе системы Z/Architecture®, может использоваться Linux, а также машины, использующие эмуляцию, как описано на сайтах http://www.turbohercules.com, http://www.hercules-390.org и http://www.funsoft.com. В режиме эмуляции эмулирующее программное обеспечение выполняется собственным процессором, эмулирующим архитектуру эмулируемого процессора.

Собственный процессор 27 обычно выполняет эмулирующее программное обеспечение 23, представляющее собой аппаратно-программное обеспечение или собственную операционную систему для эмуляции эмулируемого процессора. Эмулирующее программное обеспечение 23 отвечает за выборку и выполнение команд архитектуры эмулируемого процессора. Эмулирующее программное обеспечение 23 поддерживает счетчик эмулируемых команд для слежения за границами команд. Эмулирующее программное обеспечение 23 может осуществлять выборку одной или нескольких эмулируемых машинных команд за один раз и преобразование одной или нескольких эмулируемых машинных команд в соответствующую группу собственных машинных команд для выполнения собственным процессором 27. Эти преобразованные команды могут помещаться в кэш, что позволяет ускорять преобразование. Тем не менее, эмулирующее программное обеспечение должно поддерживать правила архитектуры эмулируемого процессора с тем, чтобы обеспечивать правильную работу операционных систем и приложений, написанных для эмулируемого процессора. Кроме того, эмулирующее программное обеспечение должно обеспечивать ресурсы, указанные архитектурой эмулируемого процессора 1, включая без ограничения управляющие регистры, регистры общего назначения, регистры с плавающей точкой, функцию динамической трансляции адреса, включая таблицы сегментов и таблицы страниц, например, механизмы прерывания, механизмы переключения контекста, часы истинного времени (TOD) и структурированные интерфейсы с подсистемами ввода-вывода с тем, чтобы операционная система или прикладная программа, рассчитанная на работу в эмулируемом процессоре, могла быть запущена в собственном процессоре, имеющем эмулирующее программное обеспечение.

Декодируется конкретная эмулируемая команда, и вызывается подпрограмма для выполнения функции отдельной команды. Функция 23 эмулирующего программного обеспечения, эмулирующая функцию эмулируемого процессора 1, реализуется, в подпрограмме или драйвере на языке "С" или каким-либо другим способом обеспечения драйвера для конкретного аппаратного обеспечения, доступным для специалистов в данной области техники, ознакомившихся в описанием предпочтительного варианта осуществления. В различных патентах, в которых предложена эмуляция программного и аппаратного обеспечения, включая без ограничения патент US 5551013 под названием "Multiprocessor for hardware emulation", выданный на имя Beausoleil и др., патент US 6009261 под названием "Preprocessing of stored target routines for emulating incompatible instructions on a target processor", выданный на имя Scalzi и др.; патент US 5574873 под названием "Decoding guest instruction to directly access emulation routines that emulate the guest instructions", выданный на имя Davidian и др.; патент US 6308255 под названием "Symmetrical multiprocessing bus and chipset used for coprocessor support allowing non-native code to run in a system", выданный на имя Gorishek и др.; патент US 6463582 под названием "Dynamic optimizing object code translator for architecture emulation and dynamic optimizing object code translation method", выданный на имя Lethin и др.; патент US 5790825 под названием "Method for emulating guest instructions on a host computer through dynamic recompilation of host instructions", выданный на имя Eric Traut, проиллюстрированы разнообразные известные способы эмуляции формата команд, структурированного для отличающейся машины, в целевой машине, доступные для специалистов в данной области техники, а также используемые ими промышленные средства программного обеспечения.

В публикации заявки US 2009/0249039 А1 от 1 октября 2009 г. (заявитель -Hook и др.) под названием" Providing Extended Precision in SIMD Vector Arithmetic Operations" предложена повышенная точность арифметических операций SIMD в процессоре, имеющем регистровый файл и аккумулятор. В первый и второй векторные регистры, соответственно, загружаются первый набор элементов данных и второй набор элементов данных. Каждый элемент данных содержит N разрядов. Затем из памяти вызывается команда арифметической операции. Команда арифметической операции декодируется. Затем из регистрового файла считываются первый векторный регистр и второй векторный регистр. В первом и втором векторных регистрах выполняется команда арифметической операции с соответствующими элементами данных. Затем полученный в результате выполнения элемент записывается в аккумулятор. После этого полученный элемент трансформируется в N-разрядный элемент и записывается в третий регистр для последующего оперирования или хранения в памяти. Трансформации полученного элемента может включать, например, округление, фиксацию и/или сдвиг элемента.

Существует потребность в командах с новыми функциональными возможностями, согласующимися с существующей архитектурой, уменьшающими зависимость от ресурсов архитектуры, таких как регистры общего назначения, и улучшающими функциональные возможности и производительность версий программного обеспечения, в которых применяется новая команда.

В руководстве International Business Machines Corporation под названием z/Architecture® Principles of Operation, SA22-7832-07, опубликованном в феврале 2009 г., описан порядок обработки сигналов с переключением между (24- или 31-разрядным) режимом архитектуры ESA/390 и (64-разрядным) режимом z/Architecture. Команда, оперирующая в режиме ESA/390 с двоичными разрядами 0-31 32-битового разряда, вместо этого оперирует в z/Architecture с двоичными разрядами 32-63 64-разрядного регистра. В режиме ESA/390 не используются разряды 0-31 64-разрядных регистров z/Architecture.

В заявке WO 98/12627 А1 описаны слова команды, имеющие поле разрядов исходного регистра с указанием исходного регистра множества 32-разрядных регистров, в которых хранится слово данных входных операндов. В слове команды также содержится разряд размера, указывающий, должны ли считываться все 32 разряда регистра или только 16 младших разрядов или 16 старших разрядов.

В соответствии с изобретением, на основе функции старшего слова (High-Word) в компьютере, имеющем первое число больших регистров общего назначения (РОН), увеличено эффективное число РОН, доступных для команд программы, при этом каждая команда содержит код операции и одно или несколько полей РОН для указания соответствующих РОН, каждый большой РОН содержит первую часть и вторую часть, упомянутые большие РОН содержат первые малые РОН, состоящие из первых частей, и вторые малые РОН, состоящие из вторых частей, компьютер имеет режим малых РОН, в котором в качестве основанных на РОН адресов операндов в основной памяти используются только операнды первых малых РОН, и режим больших РОН, в котором в качестве основанных на РОН адресов операндов в основной памяти используются операнды, перекрывающие как первые малые РОН, так и вторые малые РОН. При этом способ увеличения эффективного числа РОН, доступных для команд программы в компьютере, включает: (а) выполняемое на основании слова состояния программы определение того, находится ли компьютер в режиме малых РОН или в режиме больших РОН, причем в режиме малых РОН разрешается выполнение программ, написанных для компьютера с архитектурой малых РОН, в которой адреса памяти и регистровые операнды ограничены размером малого РОН, (б) выполняемое, если функция старшего слова на компьютере включена (разрешена), блокирование выполнения второго набора команд, причем в компьютере имеется поле, управляющее включением или отключением функции старшего слова, (в) выполняемое при нахождении компьютера в режиме малых РОН выполнение команд из первого набора команд, предназначенного для доступа к первым малым РОН, включающее генерирование адресов памяти для доступа к хранимым в памяти операндам на основании первых малых РОН или доступа к операндам первых малых РОН, состоящих из упомянутых первых частей, и выполняемое при включенной функции старшего слова выполнение команд из второго набора команд, предназначенного для доступа ко вторым малым РОН, включающее генерирование адресов памяти для доступа к хранимым в памяти операндам на основании вторых малых РОН или доступа к операндам вторых малых РОН, состоящих из упомянутых вторых частей, и (г) выполняемое при нахождении компьютера в режиме больших РОН выполнение команд из третьего набора команд, включающее генерирование адресов памяти для доступа к хранимым в памяти операндам на основании больших РОН или доступа к операндам больших РОН, содержащих упомянутые первые части и упомянутые вторые части.

В одном из вариантов осуществления, режим малых РОН предусматривает нахождение в режиме 24-разрядной адресации или режиме 31-разрядной адресации.

В одном из вариантов осуществления, первая часть содержит 32 разряда, вторая часть содержит 32 разряда, а третья часть содержит 64 разряда.

В одном из вариантов осуществления выполнение команды из второго набора команд включает в себя выполнение заданной соответствующим кодом операции функции на основании двух операндов и сохранение результата, при этом заданная соответствующим кодом операции функция состоит из функции сложения двух операндов или функции сравнения двух операндов.

В одном из вариантов осуществления выполнение команды из второго набора команд включает в себя выполнение заданной соответствующим кодом операции функции на основании двух операндов и сохранение результата, при этом заданной соответствующим кодом операции функцией является функция загрузки операнда из памяти или функция сохранения операнда в памяти.

В одном из вариантов осуществления выполнение команды из второго набора команд включает в себя выполнение заданной соответствующим кодом операции функции на основании двух операндов и сохранение результата, при этом заданной соответствующим кодом операции функцией является функция поворота с последующей вставкой выбранных разрядов (ROTATE THEN INSERT SELECTED BITS), включающая поворот исходного операнда на заданную командой величину и вставку выбранной части повернутого исходного операнда в выбранную часть целевого операнда.

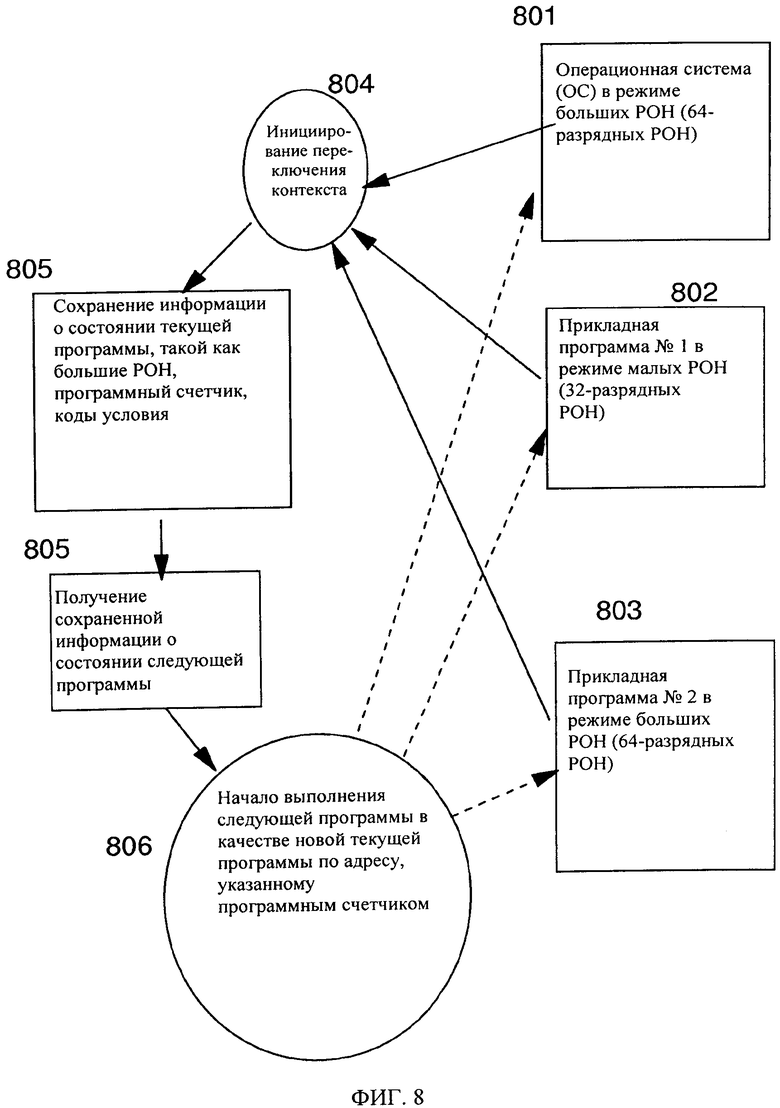

В одном из вариантов осуществления поддерживается операционная система, действующая в режиме больших РОН, при этом большие РОН сохраняются и восстанавливаются при переключениях контекста приложений, действующих в режиме малых РОН.

В одном из вариантов осуществления операционная система действует в режиме больших РОН, при этом большие РОН сохраняются и восстанавливаются при переключениях контекста приложений, действующих в режиме малых РОН.

Перечисленные, а также дополнительные задачи, признаки и выгодные варианты осуществления станут ясны из следующего далее описания.

Далее лишь в качестве примера будут описаны варианты осуществления изобретения со ссылкой на сопровождающие чертежи, на которых:

на фиг. 1А показана блок-схема, иллюстрирующая один из примеров главной компьютерной системы,

на фиг. 1Б - блок-схема, иллюстрирующая один из примеров эмулирующей главной компьютерной системы,

на фиг. 1В - блок-схема, иллюстрирующая один из примеров компьютерной системы,

на фиг. 2 - блок-схема, иллюстрирующая один из примеров компьютерной сети,

на фиг. 3 - блок-схема, иллюстрирующая элементы компьютерной системы,

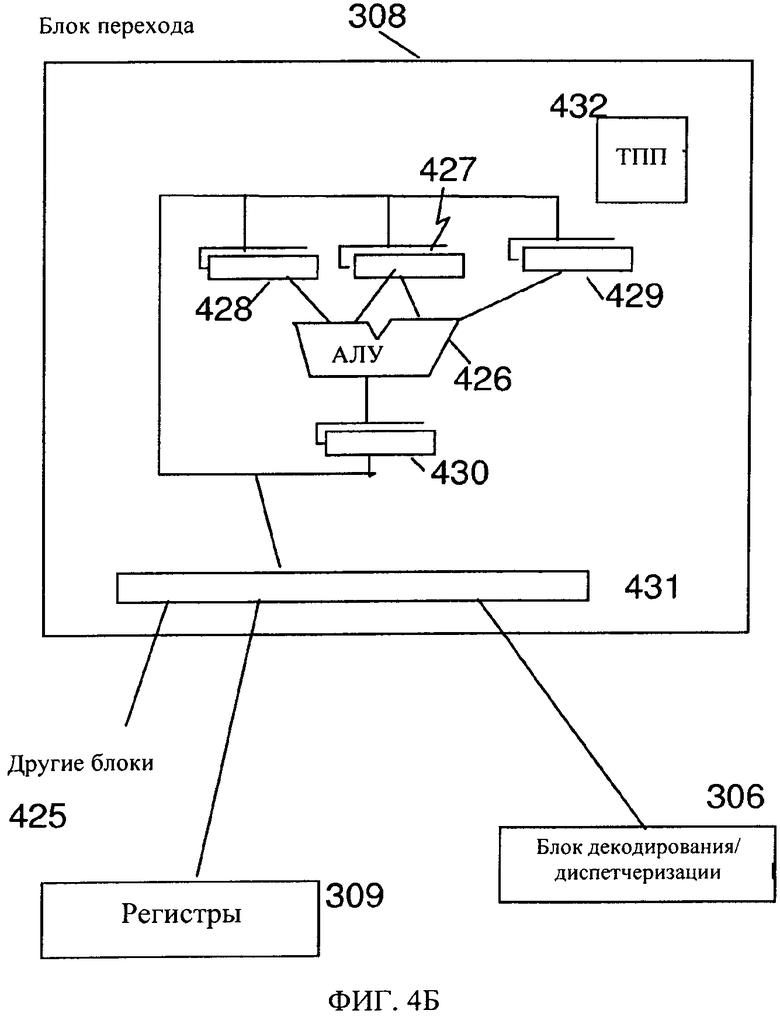

на фиг. 4А-4В - подробные элементы компьютерной системы,

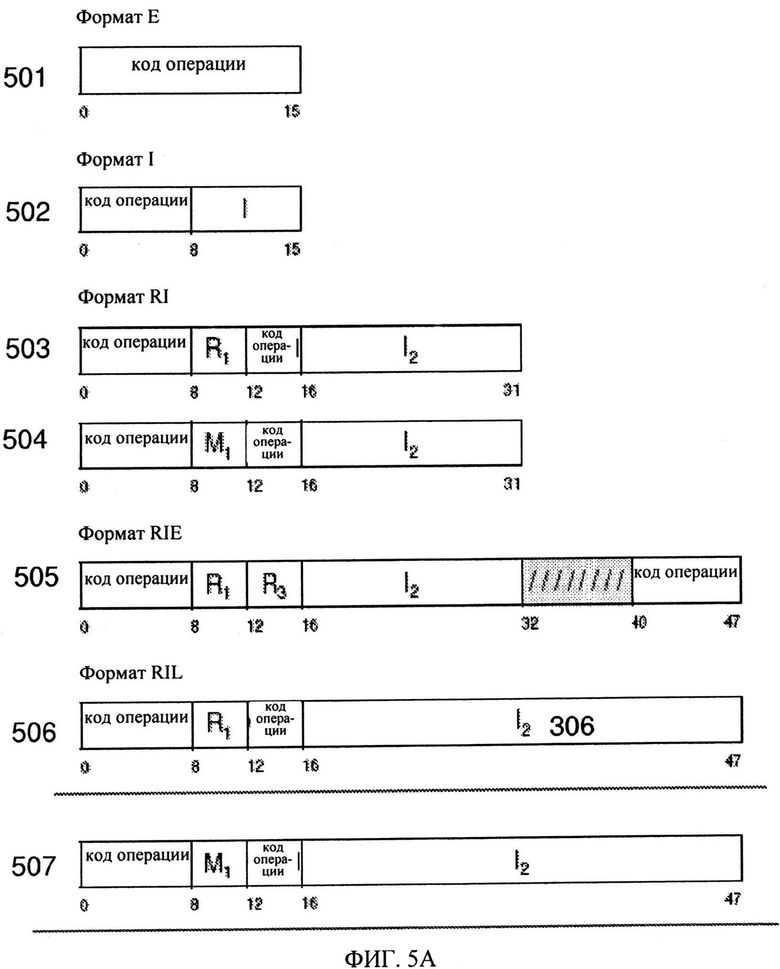

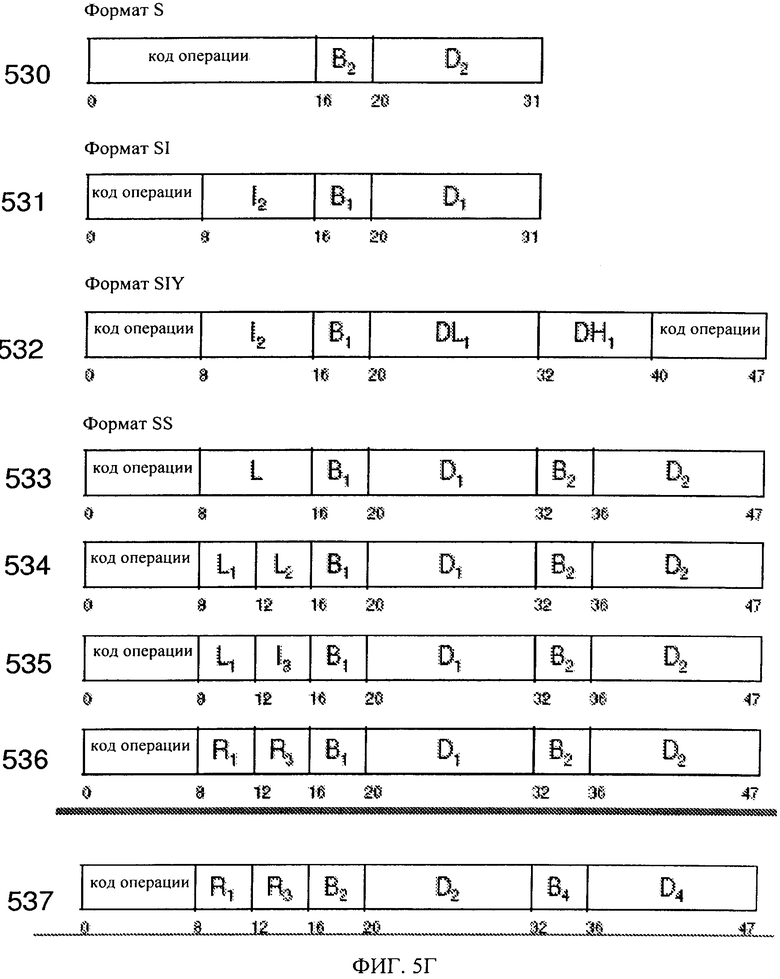

на фиг. 5А-5Е - формат машинных команд компьютерной системы,

на фиг. 6 - один из примеров большого РОН,

на фиг. 7А-7Б - один из примеров потока согласно варианту осуществления старшего слова, и

на фиг. 8 - один из примеров потока переключений контекста.

Варианты осуществления могут быть реализованы на практике посредством программного обеспечения (иногда называемого лицензионным внутренним кодом, аппаратно-программным обеспечением, микрокодом, милликодом, пикокодом и т.п., что во всех случаях согласуется с настоящим изобретением). Как показано на фиг. 1А, обычно процессор, также известный как ЦП (центральный процессор) 1 системы 50, получает доступ к программному коду системы программного обеспечения, в котором воплощено настоящее изобретение, посредством долговременных запоминающих сред 11, таких как ПЗУ на компакт-дисках, накопитель на магнитной ленте или накопитель на жестких дисках. Программный код системы программного обеспечения может быть воплощен в любой из разнообразных известных сред для применения с системой обработки данных, такой как дискета, накопитель на жестких дисках или ПЗУ на компакт-дисках. Код может распределяться в таких средах или может распределяться пользователям из памяти 2 компьютера или запоминающего устройства одной компьютерной системы по сети 10 другим компьютерным системам для применения пользователями таких других систем.

В качестве альтернативы, программный код может быть воплощен в памяти 2 с возможностью доступа к нему для процессора 1, использующего процессорную шину. В таком программном коде содержится операционная система, которая управляет функцией и взаимодействием различных узлов вычислительной машины и одной или нескольких прикладных программ. Обычно подкачка страниц программного кода осуществляется из плотных запоминающих сред 11 в быстродействующее запоминающее устройство 2, в котором он доступен для обработки процессором 1. Методы и способы воплощения программного кода системы программного обеспечения в памяти, в физических средах и/или распределения программного кода посредством сетей хорошо известны и не будут дополнительно рассматриваться в описании. Программный код, созданный и хранящийся в материальной среде (включая без ограничения такие машиночитаемые носители информации, как модули электронной памяти (ОЗУ), флэш-память, компакт-диски (CD), DVD, магнитную ленту и т.п.) часто именуется "компьютерным программным продуктом". Содержащая компьютерный программный продукт среда обычно может считываться устройством обработки данных предпочтительно в компьютерной системе для выполнения устройством обработки данных.

На фиг.1В проиллюстрирована характерная рабочая станция или аппаратная серверная система. В показанную на фиг.1В систему 100 входит характерная компьютерная система 101, такая как персональный компьютер, рабочая станция или сервер, включая необязательные периферийные устройства. Рабочая станция 101 имеет один или несколько процессоров 106 и шину для соединения процессора(-ов) 106 и других компонентов системы 101 и обеспечения связи между ними известными способами. Шина соединяет процессор 106 с памятью 105 и долговременным запоминающим устройством 107, которое может содержать накопитель на жестких дисках (например, включая любое из следующего: магнитный носитель, компакт-диск, цифровой многофункциональный диск и флэш-память) или, например, накопитель на магнитной ленте. В систему 101 также может входить адаптер пользовательского интерфейса, который посредством шины соединяет микропроцессор 106 с одним или несколькими устройствами сопряжения, такими как клавиатура 104, мышь 103, принтер/сканер 110 и/или другие устройства сопряжения, которыми могут являться любое пользовательское устройство сопряжения, такое как сенсорный экран, дополнительная цифровая клавиатура и т.д. Шина посредством дисплейного адаптера также соединяет дисплей 102, такой как ЖК-дисплей или монитор с микропроцессором 106.

Система 101 может поддерживать связь с другими компьютерами или компьютерными сетями посредством сетевого адаптера, способного поддерживать связь 108 с сетью 109. Примерами сетевых адаптеров являются каналы связи, кольцевая сеть с эстафетным доступом, сеть Ethernet или модемы. В качестве альтернативы, рабочая станция 101 может поддерживать связь с использованием беспроводного интерфейса, такого как карта CDPD (сотовой системы передачи пакетов цифровых данных). Рабочая станция 101 может быть связана с другими такими компьютерами в локальной вычислительной сети (ЛВС) или глобальной вычислительной сети (ГВС), или рабочей станцией 101 может являться клиент, связанный отношениями клиент-сервер с другим компьютером и т.д. Все эти конфигурации, а также соответствующее коммуникационное оборудование и программное обеспечение известны из техники.

На фиг.2 проиллюстрирована сеть 200 обработки данных, в которой может быть реализован на практике один из вариантов осуществления. В сеть 200 обработки данных может входить множество отдельных сетей, таких как беспроводная сеть и проводная сеть, в каждую из которых может входить множество отдельных рабочих станций 101, 201, 202, 203, 204. Кроме того, как известно специалистам в данной области техники, в нее может входить одна или несколько ЛВС, в которую может входить множество интеллектуальных рабочих станций, связанных с главным процессором.

Как также показано на фиг.2, в сети также могут входить мэйнфреймы или серверы, такие как шлюз (клиент-сервер 206) или сервер приложений (удаленный сервер 208, который может осуществлять доступ к хранилищу данных, а также может быть доступен непосредственно с рабочей станции 205). Шлюз 206 служит точкой входа в каждую сеть 207. Шлюз необходим при подсоединении одного сетевого протокола к другому. Шлюз 206 предпочтительно может быть связан с другой сетью (например, сетью Интернет 207) линией связи. Шлюз 206 также может быть непосредственно связан с одной или несколькими рабочими станциями 101, 201, 202, 203, 204 с использованием линии связи. Шлюз может быть реализован с использованием сервера IBM eServer™ zSeries® z10™ производства IBM Corp.

Доступ к программному коду системы программного обеспечения обычно осуществляет процессор 106 системы 101 посредством долговременных запоминающих сред 107, таких как ПЗУ на компакт-дисках, или накопитель на жестких дисках. Программный код системы программного обеспечения может быть воплощен в любой из разнообразных известных сред для применения с системой обработки данных, такой как дискета, накопитель на жестких дисках или ПЗУ на компакт-дисках. Код может распределяться в таких средах или может распределяться пользователям 210, 211 из памяти компьютера или запоминающего устройства одной компьютерной системы по сети другим компьютерным системам для применения пользователями таких других систем.

В качестве альтернативы, программный код 111 может быть воплощен в памяти 105 с возможностью доступа к нему для процессора 106 с использованием процессорной шины. В таком программном коде реализована операционная система, которая управляет функцией и взаимодействием различных узлов вычислительной машины и одной или нескольких прикладных программ 112. Обычно подкачка страниц программного кода осуществляется из плотных запоминающих сред 107 в быстродействующее запоминающее устройство 105, в котором он доступен для обработки процессором 106. Методы и способы воплощения программного кода системы программного обеспечения в памяти, в физических средах и/или распределения программного кода посредством сетей хорошо известны и не будут дополнительно рассматриваться в описании. Программный код, созданный и хранящийся в материальной среде (включая без ограничения модули электронной памяти (ОЗУ), флэш-память, компакт-диски, цифровые многофункциональные диски, магнитную ленту и т.п.) часто именуется "компьютерным программным продуктом". Содержащая компьютерный программный продукт среда обычно может считываться устройством обработки данных предпочтительно в компьютерной системе для выполнения устройством обработки данных.

Кэш, который является наиболее легкодоступным для процессора (обычно более быстродействующим и менее объемным, чем другие кэши процессора), представляет собой кэш низшего уровня (L1 или уровня 1), а основное запоминающее устройство (основная память) представляет собой кэш высшего уровня (L3 в случае 3 уровней). Кэш низшего уровня часто поделен кэш команд (I-кэш), в котором хранятся машинные команды для выполнения, и кэш данных (D-кэш), в котором хранятся операнды, хранимые в памяти.

На фиг.3 проиллюстрирован один из примеров осуществления процессора 106. Обычно с целью помещения в буфер блоков памяти и повышения производительности процессора используется один или несколько уровней кэша 303. Кэш 303 представляет собой высокоскоростной буфер, в котором в строках данных кэша хранятся данные в памяти, которые вероятно будут использоваться. Типичные строки данных кэша содержат 64, 128 или 256 байтов данных в памяти. Для кэширования команд и для кэширования данных часто используются раздельные кэши. Согласованность кэшей (синхронизация копий строк в памяти и в кэшах) часто обеспечивается различными алгоритмами слежения ("snoop"), хорошо известными из техники. Основное запоминающее устройство 105 процессорной системы часто называют кэшем. В процессорной системе, имеющей 4 уровня кэша 303, основное запоминающее устройство 105 иногда называют кэшем уровня 5 (L5), поскольку оно обычно является более быстродействующими и представляет собой лишь часть энергонезависимого запоминающего устройство (ЗУПД, ЗУ на ленте и т.д.), которое доступно для компьютерной системы. Основное запоминающее устройство 105 "кэширует" страницы данных, которые подкачиваются в основное запоминающее устройство 105 и откачиваются из него операционной системой.

Программный счетчик (счетчик команд) 311 отслеживает адрес текущей команды для выполнения. Счетчиком команд в процессоре на основе z/Architecture является 64-разрядным, при этом он может быть усечен до 31 или 24 разрядов с целью поддержки ранее существовавших ограничений адресации. Поскольку счетчик команд обычно воплощен в слове состояния программы (PSW) компьютера, оно сохраняется при переключении контекста.

Соответственно, выполняемая программа с показанием счетчика команд может прерываться, например, операционной системой (при переключении контекста из программной среды в среду операционной системы). PSW программы поддерживает показание счетчика команд, пока программа неактивна, а во время выполнения операционной системы используется счетчик команд (в PSW) операционной системы. Обычно показание счетчика команд приращивается на величину, равную числу байтов текущей команды. RISC-команды (на основе вычислений с сокращенным набором команд) обычно имеют фиксированную длину, тогда как CISC-команды (на основе вычислений с полным набором команд) обычно имеют переменную длину. Команды, используемые в системе IBM z/Architecture, являются CISC-командами, имеющими длину 2, 4 или 6 байтов. Показание счетчика 311 команд изменяется, например, в результате операции переключения контекста или операции выбранного перехода согласно команде перехода. При операции переключения контекста в слове состояния программы (PSW) сохраняется текущее показание счетчика команд вместе с другой информацией о состоянии выполняемой программы (такой как коды условий), и загружается новое показание счетчика команд, указывающее команду нового программного модуля для выполнения. Операция выбранного перехода выполняется, чтобы позволить программе принимать решения, или чтобы выполнять программный цикл путем загрузки в счетчик 311 команд результата команды перехода.

Обычно для выборки команд от имени процессора 106 применяется блок 305 выборки команд. Блок выборки осуществляет выборку "очередных последовательных команд", целевых команд из команд выбранного перехода или первых команд программы, следующей за переключением контекста. В современных блоках выборки команд часто применяют методы выборки с целью предварительной выборки команд по предположению, исходя из вероятности использования команд, предварительная выборка которых была осуществлена. Например, блок выборки может осуществлять выборку 16 байтов команды, содержащих очередную последовательную команду, и дополнительных байтов следующих далее команд.

Затем вызванные команды выполняются процессором 106. В одном из вариантов осуществления вызванная команда(-ы) передаются блоку 306 диспетчеризации блока выборки. Блок диспетчеризации декодирует команду(-ы) и пересылает информацию о декодированной команде(-ах) соответствующим блокам 307, 308, 310. Блок 307 выполнения обычно принимает информацию о декодированных арифметических командах от блока 305 выборки команд и выполняет арифметические операции с операндами в соответствии с содержащимся в команде кодом операции. Операнды предоставляются блоку 307 выполнения предпочтительно из памяти 105, структурированных регистров 309 или из непосредственного поля выполняемой команды. Сохраненные результаты выполнения хранятся в памяти 105, регистрах 309 или в другом машинном аппаратном обеспечении (таком как управляющие регистры, регистры PSW и т.п.).

Процессор 106 обычно имеет один или несколько блоков 307, 308, 310, выполнения функции команды. Как показано на фиг.4А, блок 307 выполнения посредством интерфейсной логической схемы 407 может поддерживать связь со структурированными регистрами 309 общего назначения, блоком 306 декодирования/диспетчеризации, блоком 310 загрузки/сохранения и другими процессорными блоками 401. В блоке 307 выполнения может применяться несколько регистровых схем 403, 404, 405 для хранения информации, с которой будет работать арифметическое логическое устройство (АЛУ) 402. АЛУ выполняет арифметические операции, такие как сложение, вычитание, умножение и деление, а также логические функции, такие как И, ИЛИ и исключающее ИЛИ, поворот и смещение. АЛУ предпочтительно поддерживает зависящие от конструкции специализированные операции. В других схемах могут обеспечиваться другие структурированные средства 408, включающие, например, коды условия и логическую схему поддержки восстановления. Обычно результат операции АЛУ хранится в схеме 406 выходного регистра, из которой он может пересылаться целому ряду других функций обработки. Хотя существует множество конструкций процессоров, настоящее описание имеет целью лишь обеспечить понимание одного из вариантов осуществления.

Например, команда сложения выполняется блоком 307 выполнения, обладающим арифметическими и логическими функциональными возможностями, а, например, команда с плавающей точкой выполняется блоком вычислений с плавающей точкой, обладающим специализированными возможностями работы с плавающей точкой. Блок выполнения предпочтительно работает с указанными командой операндами путем выполнения заданной кодом операции функции применительно к операндам. Например, команда сложения может выполняться блоком 307 выполнения применительно к операндам, обнаруженным в двух регистрах 309, указанных в регистровых полях команды.

Блок 307 выполнения выполняет арифметическое сложение двух операндов и сохраняет результат в третьем операнде, которым может являться третий регистр или один из двух исходных регистров. Блок выполнения предпочтительно использует арифметическое логическое устройство (АЛУ) 402, способное выполнять ряд логических функций, таких как смещение, поворот. И, ИЛИ и исключающее ИЛИ, а также ряд алгебраических функций, включая любые из следующих функций: сложение, вычитание, умножение, деление. Некоторые АЛУ 402 рассчитаны на скалярные операции, а некоторые - на операции с плавающей точкой. В зависимости от архитектуры данные могут иметь обратный порядок следования байтов (когда наименьший значимый байт соответствует старшему байтовому адресу) или прямой порядок следования байтов (когда наименьший значимый байт соответствует младшему байтовому адресу). В системе IBM z/Architecture используется обратный порядок следования байтов. В зависимости от архитектуры поля чисел со знаком могут быть представлены в виде прямого кода, дополнения до единицы или дополнения до двух. Число в форме дополнения до двух выгодно в том смысле, что АЛУ не требуется поддерживать возможность вычитания, поскольку при отрицательной или положительной величине дополнения до двух в АЛУ требуется только сложение. Числа обычно описаны в сокращенном виде, в котором 12-разрядное поле определяет адрес блока из 4096 байтов и обычно описано, например, в виде 4-килобайтового блока.

Трехрежимная адресация

Трехрежимная адресация означает способность переключения между режимами 24-разрядной, 31-разрядной и 64-разрядной адресации. Это переключение может осуществляться посредством:

старых команд перехода с сохранением и установки режима (BRANCH AND SAVE AND SET MODE) и перехода и установки режима (BRANCH AND SET MODE). Обе эти команды устанавливают режим 64-разрядной адресации, если разряд 63 регистра R2 общего назначения равен единице. Если разряд 63 равен нулю, команды устанавливают режим 24-разрядной или 31-разрядной адресации, если разряд 32 регистра равен нулю или единице, соответственно.

Новой команды установки режима адресации (SET ADDRESSING MODE) (SAM24, SAM31 и SAM64). Команда устанавливает режим 24-разрядной, 31-разрядной, или 64-разрядной адресации, заданный кодом операции кодом операции.

Трехрежимные команды

Влияние трехрежимной адресации на общие команды проявляется только в том, каким образом обрабатываются логические адреса запоминающих устройств, за исключением следующих случаев.

Команды перехода и возврата (BRANCH AND LINK), перехода с сохранением (BRANCH AND SAVE), перехода с сохранением и установки режима и относительного перехода с сохранением (BRANCH RELATIVE AND SAVE) помещают информацию в разряды 32-39 регистра R1 общего назначения как в ESA/390 в режиме 24-разрядной или 31-разрядной адресации или помещают разряды адреса в соответствующие разряды в режиме 64-разрядной адресации. Новая команда длительного относительного перехода с сохранением (BRANCH RELATIVE AND SAVE LONG) действует таким же образом.

В режиме 64-разрядной адресации команды перехода с сохранением и установки режима и перехода и установки режима помещают единицу в разряд 63 регистра R1 общего назначения. В режиме 24-разрядной или 31-разрядной адресации команда перехода с сохранением и установки режима устанавливает разряд 63 на ноль, а команда перехода и установки режима оставляет его без изменения.

Некоторые команды оставляют разряды 0-31 регистра общего назначения без изменения в режиме 24-разрядной или 31-разрядной адресации, но помещают или обновляют в них сведения об адресе или длине в режиме 64-разрядной адресации. Они перечислены в примечании к программированию на стр.7-7 ранее упомянутого руководства IBM Z/Architecture Principles of Operation и иногда именуются модальными командами.

Влияние на разряды 0-31 регистра общего назначения

Разряды 0-31 регистров общего назначения изменяются посредством команд двух типов. Командой первого типа является модальная команда (смотри предыдущий раздел), когда выполнение команды осуществляется в режиме 64-разрядной адресации. Командой второго типа является команда, которая независимо от режима адресации имеет 64-разрядный операнд результата в едином регистре общего назначения или 128-разрядный операнд результата в четно-нечетной паре регистров общего назначения. Большинство команд второго типа снабжаются мнемоническим обозначением "G" отдельно или в сочетании "GF". Все команды второго типа иногда именуются командами "типа G". Если программа не выполняется в режиме 64-разрядной адресации (в режиме больших РОН) и не содержит команду типа G, разряды 0-31 какого-либо регистра общего назначения (в режиме малых РОН) не могут быть изменены. В некоторых средах часть прикладной программы может выполняться в режиме малых РОН, а другая часть может выполняться в режиме больших РОН. В одном из вариантов осуществления некоторые команды могут являться командами режима малых РОН, а другие команды могут являться командами режима больших РОН, при этом режим работы компьютера зависит от того, выполняет ли он команду режима малых РОН или команду режима больших РОН.

Как показано на фиг.4Б, содержащаяся в команде перехода информация для выполнения команды перехода обычно передается блоку 308 перехода, в котором часто применяется алгоритм предсказания переходов, такой как таблица 432 предыстории переходов (ТПП), для предсказания исхода перехода до завершения других условных операций. Целевой объект текущей команды перехода вызывается и выполняется по предположению до завершения условных операций. Когда условные операции завершены, выполненные по предположению команды перехода завершаются или отбрасываются, исходя из условной операции и предположенного исхода. Типичная команда перехода может предусматривать проверку кодов условий и переход к целевому адресу, если коды условий отвечают требованию команды перехода, при этом целевой адрес может вычисляться на основании нескольких чисел, включая, например, числа из регистровых полей или непосредственного поля команды. В блоке 308 перехода может применяться АЛУ 426, имеющее множество схем 427, 428, 429 входных регистров и схему 430 выходного регистра. Блок 308 перехода, например, может поддерживать связь с регистрами 309 общего назначения, декодировать блок 306 диспетчеризации или другие схемы 425.

Выполнение группы команд может прерываться по ряду причин, включая, например, переключение контекста, инициированное операционной системой, исключительную ситуацию или ошибку в процессе выполнения программы, приводящую к переключению контекста, сигнал прерывания ввода-вывода, приводящий к переключению контекста, или многопоточный режим работы множества программ (в многопоточной среде). Переключение контекста предпочтительно служит для сохранения информации о состоянии выполняемой в данный момент программы и затем для загрузки информации о состоянии другой вызываемой программы. Информация о состоянии может сохраняться, например, в аппаратных регистрах или в памяти. Информация о состоянии предпочтительно содержит показание счетчика команд, указывающее очередную команду для выполнения, коды условий, сведения о преобразовании данных памяти и содержимое структурированного регистра. Переключение контекста может осуществляться аппаратными схемами, прикладными программами, программами операционной системы или аппаратно-программным кодом (микрокодом, пикокодом или лицензионным внутренним кодом (LIC) по отдельности или в сочетании).

Процессор осуществляет доступ к операндам в соответствии с определенными командами способами. Команда может содержать непосредственный операнд, в котором используется значение части команды, может содержать одно или несколько регистровых полей, прямо указывающих регистры общего назначения или регистры особо назначения (например, регистры с плавающей точкой). В команде могут использоваться подразумеваемые регистры, обозначаемые полем кода операции как операнды. В команде могут использоваться ячейки памяти для операндов. Ячейка памяти для операнда может обеспечиваться регистром, непосредственным полем или сочетанием регистров и непосредственного поля, примером чего является средство дальнего смещения на основе системы z/Architecture, в котором команда определяет базовый регистр, индексный регистр и непосредственное поле (поле смещения), которые складываются с целью получения, например, адреса операнда в памяти. Под ячейкой в данном случае подразумевается ячейка основной памяти (основного запоминающего устройства), если не указано иное.

Как показано на фиг.4В, процессор осуществляет доступ к памяти с использованием блока 310 загрузки/сохранения. Блок 310 загрузки/сохранения может выполнять операцию загрузки путем получения адреса целевого операнда в памяти 303 и загрузки операнда в регистр 309 или другую ячейку памяти 303, или может выполнять операцию сохранения путем получения адреса целевого операнда в памяти 303 и сохранения данных, полученных из регистра 309 или другой ячейки памяти 303, в ячейке целевого операнда в памяти 303. Блок 310 загрузки/сохранения может действовать по предположению и осуществлять доступ к памяти в последовательности, которая не соответствует последовательности команд, тем не менее, блок 310 загрузки/сохранения должен обеспечивать для программ видимость выполнения команды по порядку. Блок 310 загрузки/сохранения может поддерживать связь с регистрами 309 общего назначения, блоком 306 декодирования/диспетчеризации, интерфейсом 303 кэша/памяти или другими элементами 455 и содержит различные регистровые схемы, АЛУ 458 и управляющую логику 463 для вычисления адресов ячеек запоминающего устройства и обеспечения последовательного потока для сохранения порядка следования операций. Некоторые операции могут выполняться не по порядку, но блок загрузки/сохранения обеспечивает функциональные возможности для того, чтобы выполняемые не по порядку операции выглядели для программы выполненными по порядку, как хорошо известно из техники.

Адреса, которые "видит" прикладная программа, предпочтительно часто именуются виртуальными адресами. Иногда виртуальные адреса именуются "логическими адресами" и "действительными адресами". Эти виртуальные адреса являются виртуальными в том смысле, что их перенаправляют в ячейку физической памяти посредством одной из ряда технологий динамической трансляции 312 адреса (DAT), включая без ограничения простое приписывание величины смещения к виртуальному адресу, трансляцию виртуального адреса посредством одной или нескольких таблиц трансляции, которые предпочтительно содержат по меньшей мере таблицу сегментов и таблицу страниц по отдельности или в сочетании, предпочтительно таблицу сегментов, содержащую запись с указанием таблицы страниц. В системе z/Architecture предусмотрена иерархия трансляции, в которую входит первая таблица региона, вторая таблица региона, третья таблица региона, таблица сегментов и необязательная таблица страниц. Эффективность трансляции адресов часто повышается за счет использования буфера быстрого преобразования адреса (TLB), который содержит записи, отображающие виртуальный адрес соответствующей ячейки физической памяти. Записи создаются, когда DAT 312 транслирует виртуальный адрес с использованием таблиц перевода. Затем при последующем использовании виртуального адреса может использоваться запись из быстродействующего TLB вместо доступа к таблицам медленной последовательной трансляции. Содержимым TLB может управлять ряд алгоритмов замещения, включая алгоритм замещения наиболее давней по использованию страницы (LRU).

В том случае, когда процессором является процессор мультипроцессорной системы, каждый процессор отвечает за сохранение совместно используемых ресурсов, таких как средства ввода-вывода, кэши, TLB и память, взаимно заблокированных для обеспечения непротиворечивости. Обычно для поддержания непротиворечивости кэшей используются технологии "слежения". Для облегчения совместного использования каждая строка кэша может помечаться в среде слежения как находящаяся в одном из следующих состояний, включающих состояние совместного использования, состояние монопольного использования, измененное состояние, недействительное состояние и т.п.

Блоки 304 ввода-вывода обеспечивают процессор средствами подключения к периферийным устройствам, включая, например, накопители на магнитной ленте, накопители на дисках, принтеры, дисплеи и сети. Блоки ввода-вывода часто представлены в компьютерной программе программными драйверами. В мэйнфреймах, таких как z/Series производства IBM, блоки ввода-вывода мэйнфрейма являются адаптерами каналов и адаптерами открытых систем и обеспечивают связь между операционной системой и периферийными устройствами.

В следующем далее описании, взятом из руководства z/Architecture Principles of Operation, рассмотрено архитектурное представление компьютерной системы.

Запоминающее устройство

В основном запоминающем устройстве компьютерной системы хранится информация, а также адресные, защитные, контрольные и корректирующие записи. Некоторые особенности адресации включают формат адресов, концепцию адресных пространств, различные типы адресов и то, каким образом адрес одного типа транслируется в адрес другого типа. Некоторые из основных запоминающих устройств имеют постоянно абонированные ячейки. Основное запоминающее устройство обеспечивает систему запоминающим устройством с прямой адресацией и быстрой выборкой данных. В основное запоминающее устройство должны загружаться (из устройств ввода) как данные, так и программы, после чего они могут обрабатываться.

Основное запоминающее устройство может содержать одно или несколько буферных запоминающих устройств меньшей емкости с более быстрой выборкой, иногда называемых кэшами. Кэш обычно физически связан с ЦП или процессором ввода-вывода. Физическая конструкция и использование различных запоминающих сред в целом не сказывается на программе за исключением производительности.

Для команд и операндов, хранимых в памяти, могу быть предусмотрены раздельные кэши. Информация содержится в кэше в форме непрерывных байтов на целочисленной границе, называемой блоком или строкой данных кэша (или для краткости строкой). Согласно одной из моделей может быть предусмотрена команда извлечения атрибута кэша (EXTRACT CACHE ATTRIBUTE), которая выдает размер строки кэша в байтах. Согласно одной из моделей также может быть предусмотрена команда упреждающей выборки данных (PREFETCH DATA) и команда упреждающей выборки данных относительно большой длины (PREFETCH DATA RELATIVE LONG) для упреждающей выборки данных из запоминающего устройства в кэш данных или команд или для высвобождения данных из кэша.

Запоминающее устройство рассматривается как длинная горизонтальная битовая строка. В случае большинства операций доступ к запоминающему устройству последовательно осуществляется слева направо. Битовая строка подразделяется на блоки из восьми разрядов. Восьмиразрядный блок называется байтом и является базовым конструктивным блоком всех форматов представления информации. Местоположение каждого байта в запоминающем устройстве идентифицируется однозначно определяемым неотрицательным целым числом, которое является адресом местоположения этого байта или просто адресом байта. Соседние местоположения байтов имеют идущие подряд адреса, начинающиеся слева с 0 и последовательно следующие слева направо. Адреса представляют собой двоичные целые числа без знака, содержащие 24, 31 или 64 разряда.

Обмен информацией между запоминающим устройством и ЦП или канальной подсистемой осуществляется путем передачи одного байта или группы байтов за один раз. Если не оговорено иное, хранящаяся группа байтов адресуется посредством крайнего левого байта из группы. Число байтов в группе подразумевается или прямо оговаривается выполняемой операцией. Используемая в работе ЦП группа байтов называется полем. Разряды в каждой группе байтов последовательно нумеруются слева направо. Крайние левые разряды иногда именуются "старшими" разрядами, а крайние правые разряды - "младшими" разрядами. Тем не менее, номера разрядов не являются адресами ячеек запоминающего устройства. Возможна только адресация байтов. Чтобы оперировать с отдельными разрядами хранящегося байта, осуществляется доступ ко всему байту. Разряды в байте пронумерованы слева направо от 0 до 7. Разряды в адресе могут быть пронумерованы от 8 до 31 или от 40 до 63 в случае 24-разрядных адресов или от 1 до 31 или от 33 до 63 в случае 31-разрядных адресов и от 0 до 63 в случае 64-разрядных адресов. В любом другом имеющем фиксированную длину формате из множества байтов разряды, образующие формат, последовательно пронумерованы, начиная с 0. В целях обнаружения ошибок и предпочтительно их исправления с каждым байтом или группой байтов может передаваться один или несколько контрольных разрядов. Такие контрольные разряды генерируются автоматически машиной и не могут непосредственно управляться программой. Емкость запоминающего устройства выражается в числе байтов. Когда кодом операций команды подразумевается длина хранящегося поля операнда, считается, что поле имеет фиксированную длину, которая может составлять 1, 2, 4, 8 или 16 байтов. Для некоторых команд могут подразумеваться более длинные поля. Когда длина хранящегося поля операнда не подразумевается, а прямо указывается, считается, что поле имеет переменную длину. Операнды переменной длины могут различаться по длине с шагом в 1 байт. При сохранении информации в запоминающем устройстве замещается содержимое местоположений только тех байтов, которые включены в указанное поле, несмотря на то, что ширина физического пути доступа к запоминающему устройству может превышать длину сохраняемого поля.

Некоторые хранящиеся единицы информации должны находиться на целочисленной границе. Применительно к единице информации граница называется целочисленной, когда адрес ее ячейки запоминающего устройства кратен длине единицы информации в байтах. Полям длиной 2, 4, 8 и 16 байтам на целочисленной границе даются особые названия. Полуслово является группой из 2 идущих подряд байтов на двухбайтовой границе и представляет собой базовый конструктивный блок команд. Слово является группой из 4 идущих подряд байтов на четырехбайтовой границе. Двойное слово является группой из 8 идущих подряд байтов на 8-байтовой границе. Учетверенное слово является группой из 16 идущих подряд байтов на 16-байтовой границе. Когда в адресах ячеек запоминающего устройства указаны полуслова, слова, двойные слова и учетверенные слова, в двоичном представлении адреса содержится один, два, три или четыре крайних правых нулевых разряда, соответственно. Команды должны находиться на двухбайтовых целочисленных границах. Хранящиеся операнды большинства команд не содержат требования размещения на границах.

В устройствах, в которых реализованы раздельные кэши для команд и операндов, хранимых в памяти, могут происходить значительные задержки, если программа сохраняется в строке кэша, из которой впоследствии осуществляется выборка команд, независимо от того, изменяются ли при сохранении команды, выборка которых впоследствии осуществляется.

Команды

Обычно работа ЦП управляется посредством хранящихся команд, которые последовательно выполняются по одной за один раз слева направо в возрастающей последовательности адресов ячеек запоминающего устройства. Изменение последовательного выполнения операций может быть вызвано переходом, командой загрузки PSW, прерываниями, командами процессора обработки сигналов или вмешательством оператора.

Команда предпочтительно содержит две основные части:

код операции, который определяет операцию для выполнения,

необязательно указание участвующих операндов.

На фиг.5А-5Е проиллюстрированы форматы команд системы z/Architecture. Команда может содержать только код 501 операции или код операции и ряд полей, содержащих непосредственные операнды или описатели регистров для определения местонахождения операндов в регистрах или в памяти. Код операции может указывать аппаратному обеспечению на необходимость использования подразумеваемых ресурсов (операндов и т.д.), таких как один или несколько конкретных регистров общего назначения (РОН). Операнды могут быть сгруппированы в три класса: операнды, находящиеся в регистрах, непосредственные операнды и хранящиеся операнды. Операнды могут указываться прямо или неявно. Регистровые операнды могут находиться в регистрах общего назначения, регистрах с плавающей точкой, регистрах доступа или управляющих регистрах, при этом тип регистра указывается кодом операции. Регистр, содержащий операнд, определяется путем указания его в 4-разрядном поле команды, называемом полем R. В случае некоторых команд операнд находится в неявно указанном регистре, который подразумевается кодом операции. Непосредственные операнды содержатся в команде, а 8-, 16- или 32-разрядное поле, в котором содержится непосредственный операнд, называется полем I. Хранящиеся операнды могут иметь подразумеваемую длину, обозначаться битом маски, указанием в команде 4- или 8-разрядной длины, которое называется полем L, или могут иметь длину, определяемую содержимым регистра общего назначения. Адреса хранящихся операндов определяются посредством формата, в котором содержимое регистра общего назначения используется в составе адреса. Это позволяет:

указывать полный адрес путем использования сокращенной записи,

выполнять манипуляции с адресом путем использования команд, в которых для операндов используются регистры общего назначения,

изменять адреса программными средствами без изменения потока команд,

действовать независимо от местоположения областей данных путем прямого использования адресов, принимаемых от других программ.

Адрес, используемый для указания запоминающего устройства, содержится в регистре, указанном в поле R команды, или вычисляется на основании базового адреса, индекса и смещения, указанных в полях B, X и D, соответственно, команды. Когда ЦП находится в регистровом режиме доступа, помимо указания адреса поле В или R может использоваться для указания регистра доступа. Для описания выполнения команд операнды предпочтительно обозначаются как первый и второй операнды, а в некоторых случаях как третий и четвертый операнды. Обычно в выполнении команды участвуют два операнда, при этом результат выполнения замещает первый операнд.

Команда имеет длину, составляющую одно, два или три полуслова, и должна храниться на границе полуслова. Как показано на фиг.5А-5Е, на которых проиллюстрированы форматы команд, каждая команда имеет один из 25 основных форматов: Е 501, I 502, RI 503 504, RIE 505 551 552 553 554, RIL 506 507, RIS 555, RR510, RRE 511, RRF 512 513 514, RRS, RS 516 517, RSI 520, RSL 521, RSY 522 523, RX 524, RXE 525, RXF 526, RXY 527, S 530, SI 531, SIL 556, SIY 532, SS 533 534 535 536 537, SSE 541 и SSF 542, при этом формат RRF имеет три разновидности, форматы RI, RIL, RS и RSY имеют по две разновидности, а форматы RIE и SS имеют по пять разновидностей.

В названиях форматов указываются в общих чертах классы операндов, которые участвуют в операции, и некоторые подробные сведения о полях.

RIS обозначает регистровую операцию с непосредственной адресацией (register-and-immediate operation) и операцию обращения к запоминающему устройству.

RRS обозначает операцию типа регистр-регистр (register-and-register operation) и операцию обращения к запоминающему устройству.

SIL обозначает операцию обращения к запоминающему устройству с непосредственной адресацией (storage-and-immediate operation) с использованием 16-разрядного непосредственного поля.

В форматах I, RR, RS, RSI, RX, SI и SS в первом байте команды содержится код операции. В форматах Е, RRE, RRF, S, SIL и SSE в первых двух байты команды содержится код операции за исключением, того, что для некоторых команд в формате S код операции содержится только в первом байте. В форматах RI и RIL код операции содержится в первом байте и в разрядах 12-15 команды. В форматах RIE, RIS, RRS, RSL, RSY, RXE, RXF, RXY и SIY код операции содержится в первом байте и в шестом байте команды. В первых двух разрядах первого или единственного байта кода операции следующим образом указаны длина и формат команды.

В форматах RR, RRE, RRF, RRR, RX, RXE, RXF, RXY, RS, RSY, RSI, R1, RIE и RIL содержимое регистра, указанное в поле R1, называется первым операндом. Регистр, содержащий первый операнд, иногда именуется "местоположением первого операнда", а иногда "регистром R1". В форматах RR, RRE, RRF и RRR в поле R2 указан регистр, содержащий второй операнд, при этом в поле R2 может быть указан тот же регистр, что и поле R1. В форматах RRF, RXF, RS, RSY, RSI и RIE использование поля R3 зависит от команды. В форматах RS и RSY вместо поля R3 может быть указано поле М3, определяющее маску. В поле R обозначен регистр общего назначения или доступа для общих команд, регистр общего назначения для управляющих команд и регистр с плавающей точкой или регистр общего назначения для команд с плавающей точкой. Регистровый операнд регистров общего назначения и управляющих регистров находится в разрядах 32-63 64-разрядного регистра или занимает весь регистр в зависимости от команды.

В формате I содержимое восьмиразрядного поля данных с непосредственной адресацией, т.е. поля I команды непосредственно используется как операнд. В формате SI содержимое восьмиразрядного поля данных с непосредственной адресацией, т.е. поля I2 команды непосредственно используется как второй операнд. В полях В1 и D1 указан первый операнд, имеющий длину 1 байт. Формат SIY аналогичен за исключением того, что вместо поля D1 используются поля DH1 и DL1. В формате RI для команд сложения полуслова с непосредственной адресацией (ADD HALFWORD IMMEDIATE), сравнения полуслова с непосредственной адресацией (COMPARE HALFWORD IMMEDIATE), загрузки полуслова с непосредственной адресацией (LOAD HALFWORD IMMEDIATE) и умножения полуслова с непосредственной адресацией (MULTIPLY HALFWORD IMMEDIATE) содержимое 16-разрядного поля I2 команды используется непосредственно как двоичное целое число со знаком, а в поле R1 указан первый операнд, имеющий длину 32 или 64 разряда в зависимости от команды. Для команды проверки с маскированием (TEST UNDER MASK) (TMHH, TMHL, TMLH, TMLL) содержимое поля I2 используется как маска, а в поле R1 указан первый операнд, имеющий длину 64 разряда.

Для команд вставки с непосредственной адресацией (INSERT IMMEDIATE), И с непосредственной адресацией (AND IMMEDIATE), ИЛИ с непосредственной адресацией (OR IMMEDIATE) и логической загрузки с непосредственной адресацией (LOAD LOGICAL IMMEDIATE) содержимое поля I2 используется как двоичное целое число без знака или логическое значение, а в поле R1 указан первый операнд длиной 64 разряда. Для команд относительного перехода в форматах RI и RSI содержимое 16-разрядного поля I2 используется как двоичное целое число со знаком, указывающее количество полуслов. Это число при его сложении с адресом команды перехода указывает адрес перехода. Для команд относительного перехода в формате RIL поле I2 содержит 32 разряда и используется таким же образом.

Для команд относительного перехода в форматах RI и RSI содержимое 16-разрядного поля I2 используется как двоичное целое число со знаком, указывающее количество полуслов. Это число при его сложении с адресом команды перехода указывает адрес перехода. Для команд относительного перехода в формате RIL таким же образом используется поле I2 длиной 32 разряда. Для команд сравнения с непосредственной адресацией и относительного перехода (COMPARE IMMEDIATE AND BRANCH RELATIVE) и логического сравнения с непосредственной адресацией и относительного перехода (COMPARE LOGICAL IMMEDIATE AND BRANCH RELATIVE) в форматах RIE, содержимое 8-разрядного поля I2 непосредственно используется как второй операнд. Для команд сравнения с непосредственной адресацией и перехода (COMPARE IMMEDIATE AND BRANCH), сравнения с непосредственной адресацией и системного прерывания (COMPARE IMMEDIATE AND TRAP), логического сравнения с непосредственной адресацией и перехода (COMPARE LOGICAL IMMEDIATE AND BRANCH) и логического сравнения с непосредственной адресацией и системного прерывания (COMPARE LOGICAL IMMEDIATE AND TRAP) в формате RIE содержимое 16-разрядного поля I2 непосредственно используется как второй операнд. Для команд сравнения и относительного перехода (COMPARE AND BRANCH RELATIVE), сравнения с непосредственной адресацией и относительного перехода (COMPARE IMMEDIATE AND BRANCH RELATIVE), логического сравнения и относительного перехода (COMPARE LOGICAL AND BRANCH RELATIVE) и логического сравнения с непосредственной адресацией и относительного перехода (COMPARE LOGICAL IMMEDIATE AND BRANCH RELATIVE) в формате RIE содержимое 16-разрядного поля I4 используется как двоичное целое число со знаком, указывающее количество полуслов, складываемых с адресом команды для формирования адреса перехода.

Для команд сложения с непосредственной адресацией (ADD IMMEDIATE), логического сложения с непосредственной адресацией (ADD LOGICAL IMMEDIATE), логического сложения чисел со знаком с непосредственной адресацией (ADD LOGICAL WITH SIGNED IMMEDIATE), сравнения с непосредственной адресацией (COMPARE IMMEDIATE), логического сравнения с непосредственной адресацией (COMPARE LOGICAL IMMEDIATE), загрузки с непосредственной адресацией (LOAD IMMEDIATE) и однопоточного умножения с непосредственной адресацией (MULTIPLY SINGLE IMMEDIATE) в формате RIL содержимое 32-разрядного поля I2 непосредственно используется как второй операнд.

Для команд в формате RIS содержимое 8-разрядного поля I2 непосредственно используется как второй операнд. В формате SIL содержимое 16-разрядного поля I2 непосредственно используется как второй операнд. В полях В1 и D1 указан первый операнд, как описано далее.

В форматах RSL, SI, SIL, SSE и большинстве разновидностей формата SS содержимое регистра общего назначения, указанное в поле В1 прибавляется к содержимому поля D1 для формирования адреса первого операнда. В форматах RS, RSY, S, SIY, SS и SSE содержимое регистра общего назначения, указанное в поле В2, прибавляется к содержимому поля D2 или полей DH2 и DL2 для формирования адреса второго операнда. В форматах RX, RXE, RXF и RXY содержимое регистров общего назначения, указанное в полях Х2 и В2, прибавляется к содержимому поля D2 или полей DH2 и DL2 для формирования адреса третьего операнда. В форматах RIS и RRS и в одной из разновидностей формата SS содержимое регистра общего назначения, указанное в поле В4, прибавляется к содержимому поля D4 для формирования адреса четвертого операнда.

Для команд И (AND) (NC), исключающее ИЛИ (EXCLUSIVE OR) (XC), перемещения (MOVE) (MVC), модификации адреса внутри зоны (MOVE NUMERICS), перемещения зон (MOVE ZONES) и ИЛИ (OR) (ОС) в формате SS с использованием одного 8-разрядного поля в L указывается количество дополнительных байтов операнда справа от байта, указанного в адресе первого операнда. Соответственно, первый операнд имеет длину 1-256 байт, что соответствует длине 0-255 кода в L. В результате сохранения первый операнд замещается и никогда не сохраняется вне поля, заданного адресом и длиной. В этом формате второй операнд имеет такую же длину, как и первый операнд. Существуют разновидности предыдущего определения, которые относятся к командам редактирования (EDIT), редактирования и разметки (EDIT AND MARK), уплотнения согласно стандарту ASCII (PACK ASCII), уплотнения согласно стандарту UNICODE (PACK UNICODE), трансляции (TRANSLATE), трансляции и проверки (TRANSLATE AND TEST), разуплотнения согласно стандарту ASCII (UNPACK ASCII) и разуплотнения согласно стандарту UNICODE (UNPACK UNICODE).

В формате SS с использованием поле двух длин и в формате RSL в L1 указывается количество дополнительных байтов операнда справа от байта, указанного в адресе первого операнда. Соответственно, первый операнд имеет длину 1-16, что соответствует длине 0-15 кода в L1. Аналогичным образом, в L2 указывается количество дополнительных байтов операнда справа от местоположения, указанного в адресе второго операнда. В результате сохранения первый операнд замещается и никогда не сохраняется вне поля, заданного адресом и длиной. Если длина первого операнда превышает длину второго операнда, второй операнд дополняется слева нулями до длины первого операнда. В результате этого дополнения хранящийся второй операнд не изменяется. В формате SS с двумя полями R, которые используются командами перемещения к первичному выражению (MOVE TO PRIMARY), перемещения к вторичному выражению (MOVE TO SECONDARY) и перемещения с ключом, содержимое регистра общего назначения, указанное в поле R1, представляет собой 32-разрядное число без знака, называемое точной длиной. Оба операнда имеют длину, называемую эффективной длиной. Эффективная длина равна точной длине или 256 в зависимости от того, какая величина меньше. Команды устанавливают код условия, чтобы способствовать программному циклу для перемещения общего количества байтов, определенных точной длиной. Формат SS с двумя полями R также используется, чтобы определять интервал регистров и два хранящихся операнда для команды множественной разделенной загрузки (LOAD MULTIPLE DISJOINT) и определять один или два регистра и один или два хранящихся операнда для команды выполнения заблокированной операции (PERFORM LOCKED OPERATION).

Ноль в любом из полей В1, В2, Х2 или В4 указывает на отсутствие соответствующего компонента адреса. Вместо соответствующего компонента используется ноль, передающий промежуточную сумму независимо от содержимого регистра общего назначения 0. Смещение нуля не несет особого смысла.

Разряды 31 и 32 текущего PSW являются разрядами режима адресации. Разряд 31 является разрядом режима расширенной адресации, а разряд 32 является разрядом режима базовой адресации. Эти разряды регулируют размер действительного адреса, полученного путем формирования адреса. Когда оба разряда 31 и 32 текущего PSW равны нулю, ЦП находится в режиме 24-разрядной адресации, и генерируется 24-разрядная команда и действительные адреса операндов. Когда разряд 31 текущего PSW равен нулю, а разряд 32 равен единице, ЦП находится в режиме 31-разрядной адресации, и генерируется 31-разрядная команда и действительные адреса операндов. Когда оба разряда 31 и 32 текущего PSW равны единице, ЦП находится в режиме 64-разрядной адресации, и генерируется 64-разрядная команда и действительные адреса операндов. Выполнение команд ЦП предусматривает генерирование адресов команд и операндов.

При выборке команды из местоположения, указанного текущим PSW, адрес команды увеличивается на количество байтов в команде, и команда выполняется. Эти же шаги затем повторно осуществляются с использованием нового значения адреса команды с целью выборки очередной команды из последовательности. В режиме 24-разрядной адресации происходит круговая адресация команд, при этом за полусловом по адресу 224-2 команды следует полуслово по адресу 0 команды. Таким образом, в режиме 24-разрядной адресации теряется любой перенос двоичного разряда 104 PSW в результате обновления адреса команды. В режиме 31-разрядной или 64-разрядной адресации происходит аналогичная круговая адресация команд, при этом за полусловом по адресу 231-2 или 264-2 команды, соответственно, следует полуслово по адресу 0 команды. Перенос двоичного разряда 97 или 64, соответственно, PSW теряется.

Адрес операнда, который указывает на запоминающее устройство, выводится из промежуточного значения, которое содержится в регистре, указанном в полем R команды, или вычисляется, исходя из суммы трех двоичных чисел: базового адреса, индекса и смещения. Базовым адресом (В) является 64-разрядное число, содержащееся в общем регистре, который указан в программе в 4-разрядном поле команды, называемом полем В. Базовые адреса могут использоваться как средство независимой адресации каждой программы и области данных. В случае матричных вычислений они могут указывать местоположение матрицы, а в случае обработки записей они могут идентифицировать запись. Базовый адрес обеспечивает адресацию всего запоминающего устройства. Базовый адрес также может использоваться для индексации.

Индексом (X) является 64-разрядное число, содержащееся в общем регистре, который указан в программе в 4-разрядном поле команды, называемом полем X. Он входит только в адрес, указанный командами формата RX, RXE и RXY. Команды формата RX, RXE, RXF и RXY допускают двойное индексирование; иными словами, индекс может использоваться для обеспечения адреса элемента в матрице.

Смещением (D) является 12-разрядное или 20-разрядное число, содержащееся в поле команды, называемом полем D. 12-разрядное число смещения является числом без знака и обеспечивает относительную адресацию до 4095 байтов после местоположения, указанного базовым адресом. 20-разрядное число смещения является числом со знаком и обеспечивает относительную адресацию до 524287 байтов после местоположения базового адреса и до 524288 байтов до него. В случае матричных вычислений смещение может использоваться для указания одной из множества составляющих, связанных с элементом. В случае обработки записей смещение может использоваться для идентификации составляющих внутри записи. 12-разрядное число смещения содержится в двоичных разрядах 20-31 команд некоторых форматов. В командах некоторых форматов в двоичных разрядах 36-47 также содержится второе 12-разрядное число смещения.

20-разрядное число смещения содержится в командах только форматов RSY, RXY или SIY. В этих командах поле D состоит из (слабого) DL поля в двоичных разрядах 20-31 и (сильного) поля DH двоичных разрядах 32-39. Если установлено средство длительного смещения, численная величина смещения формируется путем присоединения содержимого поля DH слева к содержимому поля DL. Когда средство длительного смещения не установлено, численная величина смещения формируется путем присоединения восьми нулевых разрядов слева содержимому поля DL, при этом содержимое поля DH не учитывается.

При формировании промежуточной суммы базовый адрес и индекс обрабатываются как 64-разрядные двоичные целые числа. 12-разрядное число смещения обрабатывается как 12-разрядное двоичное целое число без знака, слева к которому присоединены 52 нулевых разряда. 20-разрядное число смещения обрабатывается как 20-разрядное двоичное целое число со знаком, слева к которому присоединены 44 знаковых разряда. Все три числа складываются как 64-разрядные двоичные числа без учета переполнения. Сумма всегда имеет длину 64 разряда и используется как промежуточное значение для формирования генерируемого адреса. Разряды промежуточной суммы пронумерованы от 0 до 63. Нулевой разряд в любом из полей В1, В2, Х2 или В4 указывает на отсутствие соответствующего компонента адреса. Вместо отсутствующего компонента при формировании промежуточной суммы используется ноль независимо от содержимого регистра общего назначения 0. Смещение нуля не несет особого смысла.

Когда в описании команд говорится, что содержимое регистра общего назначения, указанного в поле полем R, используется для адресации хранящегося операнда, содержимое регистра используется как 64-разрядное промежуточное значение.

В команде может быть указан один и тот же регистр общего назначения для вычисления адреса и в качестве местоположения операнда. Вычисление адреса завершается до изменения, если они имеют место, регистров при выполнении операции. Если в определении отдельной команды не указано иное, в генерированном адресе операнда указан крайний левый байт хранящегося операнда.

Генерированный адрес операнда всегда имеет длину 64 разряда, при этом разряды пронумерованы с 0 до 63. Способ получения генерированного адреса из промежуточного значения зависит от текущего режима адресации. В режиме 24-разрядной адресации разряды 0-39 промежуточного значения не учитываются, разряды 0-39 генерированного адреса принудительно приравниваются к нулю, а разряды 40-63 промежуточного значения становятся разрядами 40-63 генерированного адреса. В режиме 31-разрядной адресации разряды 0-32 промежуточного значения не учитываются, разряды 0-32 генерированного адреса принудительно приравниваются к нулю, а разряды 33-63 промежуточного значения становятся разрядами 33-63 генерированного адреса. В режиме 64-разрядной адресации разряды 0-63 промежуточного значения становятся разрядами 0-63 генерированного адреса. В индексе и регистрах базовых адресов могут использоваться отрицательные величины. В режиме 31-разрядной адресации не учитываются разряды 0-32 этих величин, а в режиме 24-разрядной адресации не учитываются разряды 0-39.

В случае команд перехода адрес очередной команды для выполнения при выборе перехода называет адресом перехода. В зависимости от команды перехода она может иметь формат RR, RRE, RX, RXY, RS, RSY, RSI, RI, RIE или RIL. В форматах RS, RSY, RX и RXY адрес перехода определяется базовым адресом, смещением, а в форматах RX и RXY - индексом. В этих форматах промежуточное значение генерируется согласно таким же правилам, как и при генерировании промежуточного значения адреса операнда. В форматах RR и RRE содержимое регистра общего назначения, указанное в поле R2, используется как промежуточное значение, на основании которого формируется адрес перехода. Регистр общего назначения 0 не может быть указан как содержащий адрес перехода. В случае нулевого значения в поле R2 команда выполняется без перехода.

Команды относительного перехода находятся в форматах RSI, RI, RIE и RIL. В форматах RSI, RI и RIE команд относительного перехода содержимое поля I2 обрабатывается как 16-разрядное двоичное целое число со знаком, указывающее количество полуслов. В формате RIL содержимое поля I2 обрабатывается как 32-разрядное двоичное целое число со знаком, указывающее количество полуслов. Адресом перехода является количество полуслов, указанное в поле I2, плюс адрес команды относительного перехода.

64-разрядным промежуточным значением для команды относительного перехода в форматах RSI, RI, RIE или RIL является сумма двух слагаемых без учета переполнения из двоичного разряда 0. В форматах RSI, RI или RIE первым слагаемым является содержимое поля I2 с одним нулевым разрядом, присоединенным справа, и 47 разрядами, равными знаковому разряду содержимого, присоединенными слева, а в случае команд сравнения и относительного перехода (COMPARE AND BRANCH RELATIVE), сравнения с непосредственной адресацией и относительного перехода (COMPARE IMMEDIATE AND BRANCH RELATIVE), логического сравнения и относительного перехода (COMPARE LOGICAL AND BRANCH RELATIVE) и логического сравнения с непосредственной адресацией и относительного перехода (COMPARE LOGICAL IMMEDIATE AND BRANCH RELATIVE) первым слагаемым является содержимое поля I4 с разрядами, присоединенными, как описано выше применительно к полю I2. В формате RIL первым слагаемым является содержимое поля I2 с одним нулевым разрядом, присоединенным справа, и 31 разрядом, равным знаковому разряду содержимого, присоединенным слева. Во всех форматах вторым слагаемым является 64-разрядный адрес команды перехода. Адресом команды перехода является адрес команды в PSW до того, как адрес будет обновлен с целью указания очередной команды из последовательности, или адрес объекта команды выполнения (EXECUTE), если она используется. При использовании команды выполнения в режиме 24-разрядной или 31-разрядной адресации адресом команды перехода является целевой адрес с 40 или 33 нулями, соответственно, присоединенными слева.

Адрес перехода всегда содержит 64 разряда, которые пронумерованы от 0 до 63. Адрес перехода замещает разряды 64-127 текущего PSW. Способ получения адреса перехода из промежуточного значения зависит от режима адресации. Для команд перехода, которые изменяют режим адресации, используется новый режим адресации. В режиме 24-разрядной адресации разряды 0-39 промежуточного значения не учитываются, разряды 0-39 адреса перехода приравниваются к нулю, а разряды 40-63 промежуточного значения становятся разрядами 40-63 адреса перехода. В режиме 31-разрядной адресации разряды 0-32 промежуточного значения не учитываются, разряды 0-32 адреса перехода приравниваются к нулю, а разряды 33-63 промежуточного значения становятся разрядами 33-63 адреса перехода. В режиме 64-разрядной адресации разряды 0-63 промежуточного значения становятся разрядами 0-63 адреса перехода.

В случае нескольких команд перехода переход зависит от того, выполнено ли заданное условие. Когда условие не выполнено, продолжается нормальное последовательное выполнение команд, и адрес перехода не используется. При выборе перехода разряды 0-63 адреса перехода замещают разряды 64-127 текущего PSW. В ходе операции перехода адрес перехода не используется до доступа к запоминающему устройству. Исключительная ситуация при нарушении заданных условий вследствие нечетного адреса перехода и исключительные ситуации при доступе вследствие выборки команд в местоположении перехода распознаются не как часть операцию перехода, а как исключительные ситуации, связанные с выполнением команды в местоположении перехода.

В команде перехода, такой как команда перехода с сохранением (BRANCH AND SAVE), один и тот регистр общего назначения может указываться для вычисления адреса перехода и как местоположение операнд. Вычисление адреса перехода завершается до завершения остальной операции.

В слове состояния программы (PSW), описанном в главе 4 "Управление", содержится информация, необходимая для надлежащего выполнения программы. PSW используется для управления порядком следования команд и для фиксации и указания состояния ЦП в зависимости от выполняемой программы. Активное или управляющее PSW называется текущим PSW. Команды перехода выполняют функции принятия решений, управления циклом и компоновки подпрограмм. Команда перехода влияет на порядок следования команд путем включения нового адреса команды в текущее PSW. Команды относительного перехода с использованием 16-разрядного поля I2 позволяют выбирать переход в местоположение со смещением до плюс 64 килобайта - 2 байта или минус 64 килобайта относительно местоположения команды перехода без использования базового регистра. Команды относительного перехода с использованием 32-разрядного поля I2 позволяют выбирать переход в местоположение со смещением до плюс 4 гигабайта - 2 байта или минус 4 гигабайта относительно местоположения команды перехода без использования базового регистра.