Область техники, к которой относится изобретение

Настоящее изобретение относится к компьютерным системам, более точно, к функциональным возможностям команд процесса компьютерной системы.

Предпосылки создания изобретения

Товарные знаки: IBM® является зарегистрированным товарным знаком International Business Machines Corporation (Армонк, штат Нью-Йорк, США). S/390, Z900 и z990 и z10, а названия других продуктов могут являться зарегистрированными товарными знаками или названиями продуктов International Business Machines Corporation или других компаний.

Начиная с появившихся в 60-х годах машин, известных как IBM® System 360, и до настоящего времени усилиями множества высокоодаренных инженеров IBM была создана особая архитектура, которая получила известность как "мэйнфрейм" в силу своей неотъемлемой принадлежности к вычислительной системе, и принципы работы которой определяют архитектуру машины путем описания команд, которые могут выполняться путем реализации в "мэйнфрейме" созданных изобретателями IBM команд, которые с учетом их существенной роли в течение многих лет включены в руководство IBM Principles of Operation. Восьмое издание руководства IBM® z/Architecture® Principles of Operation, опубликованное в феврале 2009 г., стало стандартным справочным материалом SA22-7832-07 и включено в описание серверов на основе мэйнфреймов IBM Z10TM.

На фиг.1A представлены характерные элементы известной из техники главной компьютерной системы 50. В компьютерной системе также могут применяться другие варианты размещения элементов, которые хорошо известны из техники. Характерный главный компьютер 50 содержит один или несколько ЦП 1, связанных с основным запоминающим устройством (памятью 2 компьютера), а также интерфейсы ввода-вывода для сопряжения с запоминающими устройствами 11 и подключения к сетям 10 для связи с другими компьютерами или SAN и т.п. ЦП 1 совместим с архитектурой, содержащей структурированную систему команд и структурированные функциональные возможности. ЦП 1 может осуществлять динамическую трансляцию 3 адреса (DAT) с целью преобразования адресов программ (виртуальных адресов) в действительный адрес памяти. DAT обычно содержит буфер 7 быстрого преобразования адреса (TLB) для кэширования преобразований, чтобы при последующих доступах к блоку памяти 2 компьютера не требовалась задержка трансляции адреса. Обычно между памятью 2 компьютера и процессором 1 используется кэш-память 9. Кэш-память 9 может являться иерархической и состоящей из кэша большой емкости, доступного для нескольких ЦП, и более быстродействующих кэшей (низкого уровня) меньшей емкости между кэшем большой емкости и каждым ЦП. В некоторых случаях реализации кэши низкого уровня разделены на отдельные кэши низкого уровня для вызова команд и доступа к данным. В одном из вариантов осуществления блок 4 вызова команд вызывает из памяти 2 команду посредством кэш-памяти 9. Команда декодируется в блоке 6 декодирования команд и отправляется (с другими командами в некоторых вариантах осуществления) в блоки 8 выполнения команд. Обычно используется несколько блоков 8 выполнения команд, например, блок выполнения арифметических команд, блок выполнения команд с плавающей точкой и блок выполнения команд перехода. Команда выполняется блоком, который в зависимости от необходимости осуществляет доступ к операндам из определяемых командами регистров или памяти. Если доступ (загрузка или сохранение) к операнду должен осуществляться из памяти 2, блок 5 загрузки/сохранения обычно обрабатывает процедуру доступа под управлением выполняемой команды. Команды могут выполняться в аппаратных схемах или во внутреннем микрокоде (аппаратно-программном обеспечении) или с использованием сочетания того и другого.

На фиг.1Б проиллюстрирован один из примеров известной из техники главной компьютерной системы 21 эмуляции, которая эмулирует главную компьютерную систему 50, имеющую главную архитектуру. Главным центральным процессором (ЦП) 1 в главной компьютерной системе 21 эмуляции является главный процессор (или виртуальный главный процессор) эмуляции, представляющий собой процессор 27 эмуляции со структурой собственных команд, отличающейся от структуры команд процессора 1 главного компьютера 50. Главная компьютерная система 21 эмуляции имеет память 22, доступную для процессора 27 эмуляции. В примере осуществления память 22 разделена на память 2 главного компьютера и память 23 программ эмуляции. Память 2 главного компьютера доступна для программ главного компьютера 21 эмуляции в зависимости от архитектуры главного компьютера. Процессор 27 эмуляции выполняет собственные команды структурированной системы команд, структура которых отличается от структуры команд эмулируемого процессора 1 и которые извлекаются из памяти 23 программ эмуляции, и может осуществлять выборку главной команды для выполнения из программы в памяти 2 главного компьютера путем применения одной или нескольких команд из программы контроля последовательности и выборки/декодирования (Sequence & Access/Decode), которая может декодировать выбранную главную команду(-ы) и определять программу выполнения собственных команд с целью эмуляции функции выбранной главной команды. Другие средства, которые предусмотрены в архитектуре главной компьютерной системы 50, могут эмулироваться программами структурированных средств (Architected Facilities Routines), включая такие средства, как, например, регистры общего назначения, управляющие регистры, поддержка подсистемы динамической трансляции адреса и ввода-вывода и кэш-память процессора. Программы эмуляции также могут использовать функции, доступные в процессоре 27 эмуляции (такие как общие регистры и динамическая трансляция виртуальных адресов) для повышения производительности программ эмуляции. Также может быть предусмотрено особое программное обеспечение и механизмы разгрузки, облегчающие процессору 27 эмуляцию функции главного компьютера 50.

В мэйнфрейме структурированные машинные команды используются программаторами, обычно современными программаторами на языке "С" посредством компилирующего приложения. Эти команды, хранящиеся в запоминающей среде, могут выполняться в собственной системе команд сервера IBM® на основе z/Architecture® или в качестве альтернативы в машинах на основе других архитектур. Они могут эмулироваться в существующих и будущих серверах на основе мэйнфреймов IBM® и в других машинах IBM® (например, серверах pSeries® и xSeries®). Они могут выполняться в операционной системе Linux разнообразными машинами, использующими аппаратное обеспечение производства IBM®, Intel®, AMD™, Sun Microsystems и других компаний. Помимо выполнения этим аппаратным обеспечением на основе системы Z/Architecture®, может использоваться Linux, а также машины, использующие эмуляцию, как описано на сайтах http://www.turbohercules.com, http://www.hercu и http://www.funsoft.com. В режиме эмуляции эмулирующее программное обеспечение выполняется собственным процессором, эмулирующим архитектуру эмулируемого процессора.

Собственный процессор 27 обычно выполняет эмулирующее программное обеспечение 23, представляющее собой аппаратно-программное обеспечение или собственную операционную систему для эмуляции эмулируемого процессора. Эмулирующее программное обеспечение 23 отвечает за выборку и выполнение команд архитектуры эмулируемого процессора. Эмулирующее программное обеспечение 23 поддерживает счетчик эмулируемых команд для слежения за границами команд. Эмулирующее программное обеспечение 23 может осуществлять выборку одной или нескольких эмулируемых машинных команд за один раз и преобразование одной или нескольких эмулируемых машинных команд в соответствующую группу собственных машинных команд для выполнения собственным процессором 27. Эти преобразованные команды могут помещаться в кэш, что позволяет ускорять преобразование. Тем не менее, эмулирующее программное обеспечение должно поддерживать правила архитектуры эмулируемого процессора с тем, чтобы обеспечивать правильную работу операционных систем и приложений, написанных для эмулируемого процессора. Кроме того, эмулирующее программное обеспечение должно обеспечивать ресурсы, указанные архитектурой эмулируемого процессора 1, включая без ограничения управляющие регистры, регистры общего назначения, регистры с плавающей точкой, функцию динамической трансляции адреса, включая таблицы сегментов и таблицы страниц, например, механизмы прерывания, механизмы переключения контекста, часы истинного времени (TOD) и структурированные интерфейсы с подсистемами ввода-вывода с тем, чтобы операционная система или прикладная программа, рассчитанная на работу в эмулируемом процессоре, могла быть запущена в собственном процессоре, имеющем эмулирующее программное обеспечение.

Декодируется конкретная эмулируемая команда, и вызывается подпрограмма для выполнения функции отдельной команды. Функция 23 эмулирующего программного обеспечения, эмулирующая функцию эмулируемого процессора 1, реализуется в подпрограмме или драйвере на языке "C" или каким-либо другим способом обеспечения драйвера для конкретного аппаратного обеспечения, доступным для специалистов в данной области техники, ознакомившихся с описанием предпочтительного варианта осуществления. В различных патентах, в которых предложена эмуляция программного и аппаратного обеспечения, включая без ограничения патент US 5551013 под названием "Multiprocessor for hardware emulation", выданный на имя Beausoleil и др., патент US 6009261 под названием "Preprocessing of stored target routines for emulating incompatible instructions on a target processor", выданный на имя Scalzi и др.; патент US 5574873 под названием "Decoding guest instruction to directly access emulation routines that emulate the guest instructions", выданный на имя Davidian и др.; патент US 6308255 под названием "Symmetrical multiprocessing bus and chipset used for coprocessor support allowing non-native code to run in a system", выданный на имя Gorishek и др.; патент US 6463582 под названием "Dynamic optimizing object code translator for architecture emulation and dynamic optimizing object code translation method", выданный на имя Lethin и др.; патент US 5790825 под названием "Method for emulating guest instructions on a host computer through dynamic recompilation of host instructions", выданный на имя Eric Traut, проиллюстрированы разнообразные известные способы эмуляции формата команд, структурированного для отличающейся машины, в целевой машине, доступные для специалистов в данной области техники, а также используемые ими промышленные средства программного обеспечения.

Согласно публикации заявки US 2009/0222814 A1 от 3 сентября 2009 г. (заявитель - Astrand) под названием "Selective Exposure to USB Device Functionality for a Virtual Machine" приложение виртуальной машины (VM) может выполнять гостевую операционную систему (OC) и позволять гостевой OC подключаться к USB-устройствам, подключенным к компьютеру. Приложение VM может фильтровать функции, соответствующие USB-устройству с тем, чтобы для гостевой OC были доступны лишь некоторые из функций USB-устройства.

В статье Edel T.R. и др. под названием "Dynamic Instruction Set definition", IBM Technical Disclosure Bulletin, International Business Machines Corp., том 16, №6, 1 ноября 1973 г., стр. 1929-1930 дано определение набора команд, являющегося уникальным для каждого пользователя компьютера. В управляющем регистре аппаратного обеспечения содержится двоичный индикатор для каждой команды или класса команд, определяющий набор команд для пользователя. Всякий раз при попытке несанкционированного использования команды аппаратное обеспечение сигнализирует об исключительной ситуации. Возможности набора команд могут содержаться в профиле каждого пользователя и управляться системным администратором.

В заявке US 2004/230816 А1 описаны команда шифрования сообщения (CIPHER MESSAGE) (КМ) и команда шифрования сообщения со сцеплением (CIPHER MESSAG Е WITH CHAINING) (KMC), которые используются вместе с кодом функции, указывающим, какая из множества функций, таких как запрос (Query), алгоритм шифрования данных (Data Encryption Algorithm) (DEA), тройной DEA (128-разрядный) или тройной DEA (192-разрядный), должна выполняться.

Краткое изложение сущности изобретения

В соответствии с изобретением скрывают выбранные установленные функции многофункциональной команды, рассчитанной на выполнение определенной функции из множества установленных функций, при этом скрывание включает установку значения, регулирующего доступность установленных функций для многофункциональной команды главного компьютера, содержащего один или несколько процессоров, имеющих первое множество упомянутых установленных функций многофункциональной команды, в которое входит одна или несколько первых установленных функций и одна или несколько вторых установленных функций, и выполнение многофункциональной команды, содержащей поле кода операции, причем упомянутое выполнение включает: осуществляемое в ответ на задание многофункциональной командой функции запроса выполнение этой функции запроса с целью определения установленных функций, доступных для многофункциональной команды, при этом выполнение функции запроса включает использование указанного значения для определения одной или нескольких вторых установленных функций, при этом выполнение функции запроса включает сохранение результирующего значения, указывающего на то, что одна или несколько первых установленных функций недоступны для многофункциональной команды, и осуществляемое в ответ на задание многофункциональной командой функции из первого множества упомянутых установленных функций, не являющейся функцией запроса, выполнение этой не являющейся функцией запроса функции, когда эта не являющаяся функцией запроса функция является одной из вторых установленных функций, и блокирование выполнения не являющейся функцией запроса функции, когда эта не являющаяся функцией запроса функция не является одной из вторых установленных функций.

В одном из вариантов осуществления гипервизором главного компьютера устанавливается значение для виртуальной машины главного компьютера, которая содержит один или несколько логических процессоров, закрепленных за одним или несколькими физическими процессорами, имеющими одну или несколько вторых установленных функций многофункциональной команды, которая выполняется в виртуальной машине логическим процессором из одного или нескольких логических процессоров посредством физического процессора из одного или нескольких физических процессоров.

В одном из вариантов осуществления одна или несколько вторых установленных функций определяется на основании кода операции многофункциональной команды.

В одном из вариантов осуществления гипервизор устанавливает другое значение, регулирующее доступность установленных функций для многофункциональной команды, выполняемой в другой виртуальной машине главной компьютерной системы, и обеспечивает выполнение в другой виртуальной машине другим логическим процессором из одного или нескольких других логических процессоров другой многофункциональной команды, если в ней задана другая функция запроса, которая выполняется с целью определения установленных функций, доступных для другой многофункциональной команды, при этом выполнение другой функции запроса включает использование другого значения с целью определения одной или нескольких третьих установленных функций и выполнение другой функции запроса включает сохранение другого результирующего значения, указывающего на то, что одна или несколько из одной или несколько третьих установленных функций недоступны для другой многофункциональной команды.

В одном из вариантов осуществления сохраненное результирующее значение является содержащей значащие разряды величиной, в которой каждый двоичный разряд соответствует определенной функции, при этом разряд, равный 1, указывает, что соответствующая функция установлена.

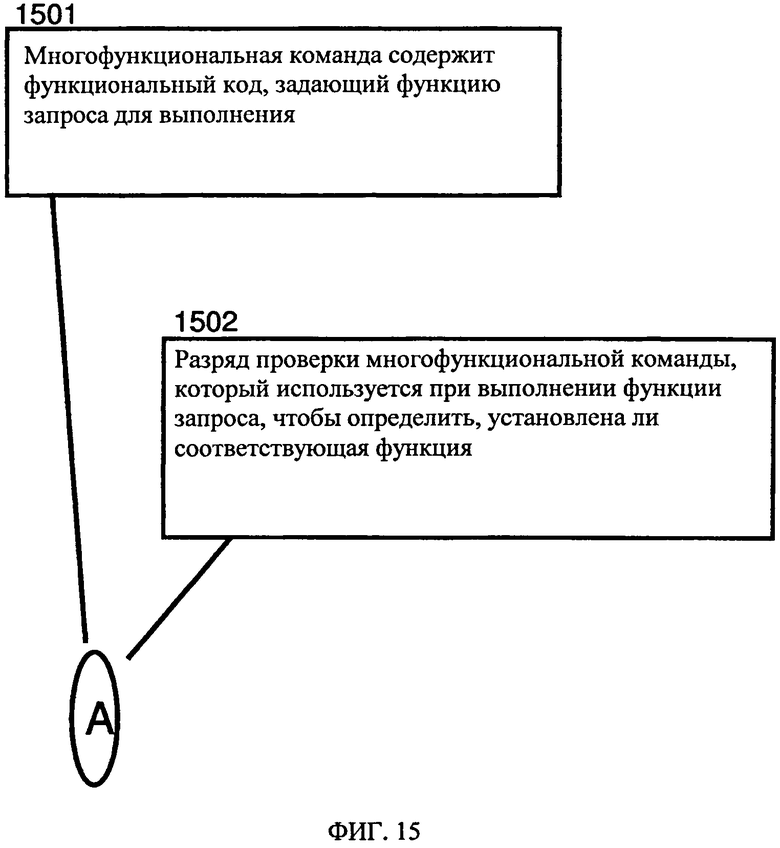

В одном из вариантов осуществления функция запроса определяется заданным многофункциональной командой кодом функции или заданным многофункциональной командой разрядом проверки.

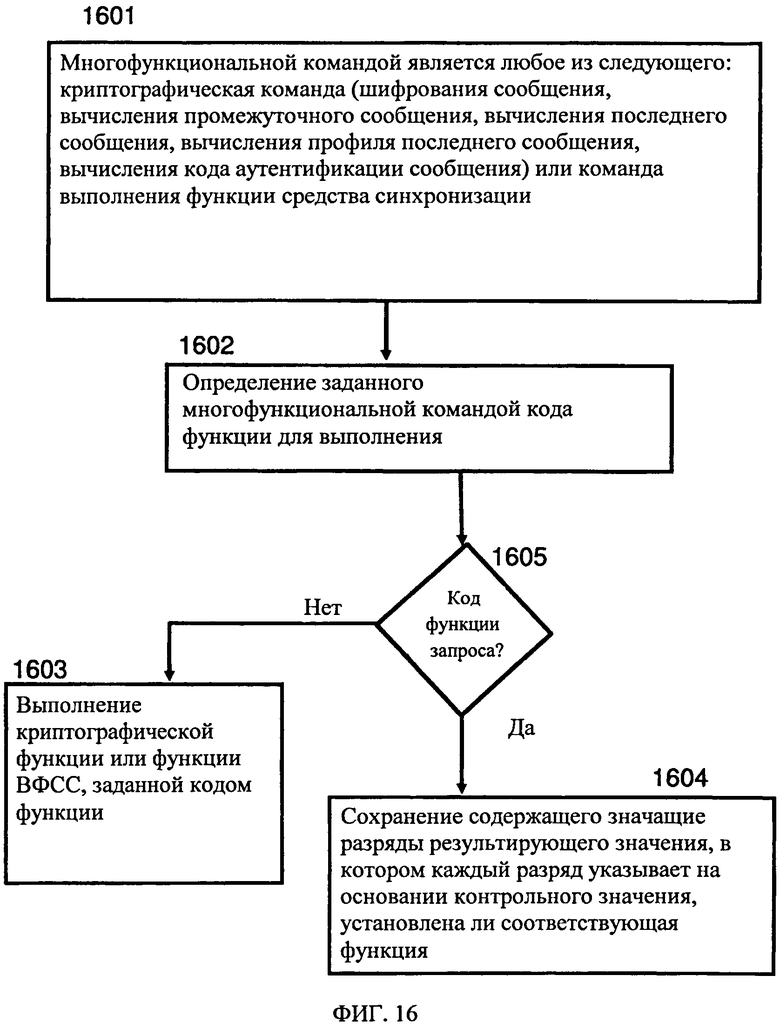

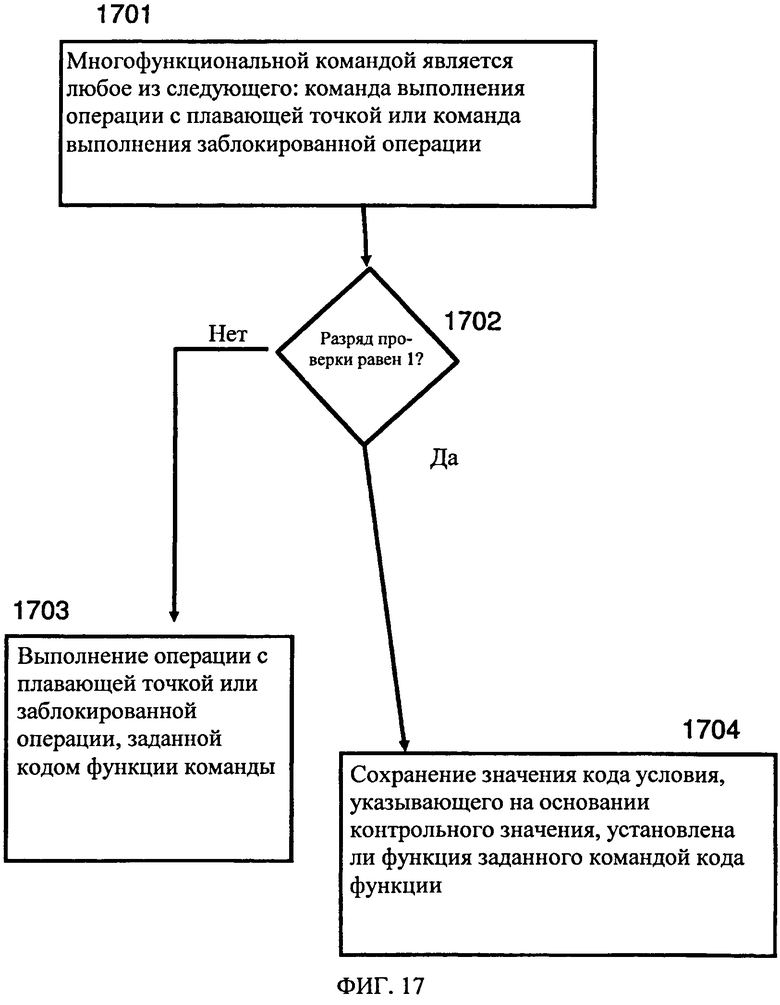

В одном из вариантов осуществления многофункциональной командой является команда системы z/Architecture, состоящая из любого из следующего: криптографической команды, команды выполнения функции средства синхронизации (PerformTiming Facility Function, англ. сокр. PTFF) (ВФСС), команды выполнения операции с плавающей точкой (Perform Floating Point Operation) или команды выполнения заблокированной операции (Perform Locked Operation), при этом криптографической командой является любое из следующего: команда шифрования сообщения, команда вычисления промежуточного сообщения (Compute Intermediate Message), команда вычисления последнего сообщения (Compute Last Message), команда вычисления профиля последнего сообщения (Compute Last Message Digest), команда вычисления кода аутентификации сообщения (Compute Message Authentication Code), а в многофункциональной команде задана функция запроса; если многофункциональной командой является криптографическая команда или команда ВФСС, определяется заданный многофункциональной командой код выполняемой функции, содержащий функцию запроса, при этом сохраненным результирующим значением является множество разрядов, каждый из которых указывает, поддерживается ли соответствующий код функции; если многофункциональной командой является криптографическая команда или команда ВФСС, определяется заданный многофункциональной командой код выполняемой функции, не содержащий функцию запроса, и выполняется криптографическая функция или функция ВФСС в соответствии с полученным кодом функции; если многофункциональной командой является команда выполнения заблокированной операции или команда выполнения операции с плавающей точкой, а заданный многофункциональной командой разряд проверки равен 1, определяется, установлен ли заданный многофункциональной командой код функции, при этом сохраненным результирующим значением является значение кода условия; и, если многофункциональной командой является команда выполнения заблокированной операции или команда выполнения операции с плавающей точкой, а заданный многофункциональной командой разряд проверки равен 0, выполняется функция с плавающей точкой или заблокированная операция в соответствии с полученным кодом функции.

Перечисленные выше и другие задачи, признаки и преимущества изобретения станут ясны из следующего далее описания.

В изобретении подробно описаны другие его варианты осуществления и особенности, считающиеся входящими в заявленное изобретение. Для обеспечения лучшего понимания преимуществ и признаков изобретения описание сопровождается чертежами.

Краткое описание чертежей

Далее будут лишь в качестве примера описаны варианты осуществления изобретения со ссылкой на сопровождающие его чертежи, на которых:

на фиг. 1А показана блок-схема, иллюстрирующая один из примеров главной компьютерной системы,

на фиг. 1Б - блок-схема, иллюстрирующая один из примеров эмулирующей главной компьютерной системы,

на фиг.1В - блок-схема, иллюстрирующая один из примеров компьютерной системы,

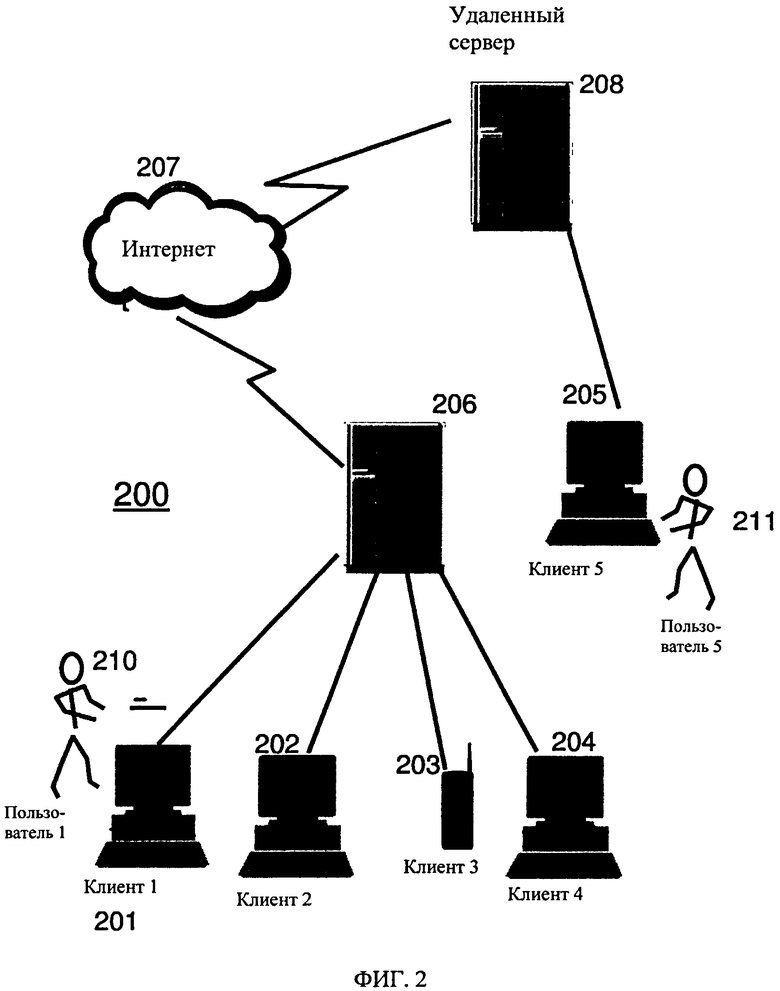

на фиг.2 - блок-схема, иллюстрирующая один из примеров компьютерной

сети,

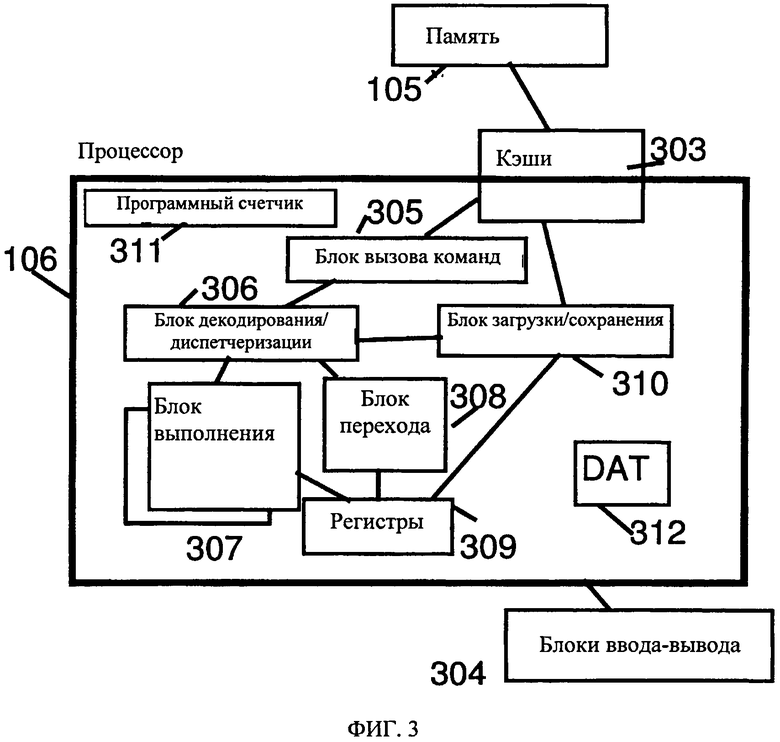

на фиг.3 - блок-схема, иллюстрирующая примеры элементов компьютерной системы,

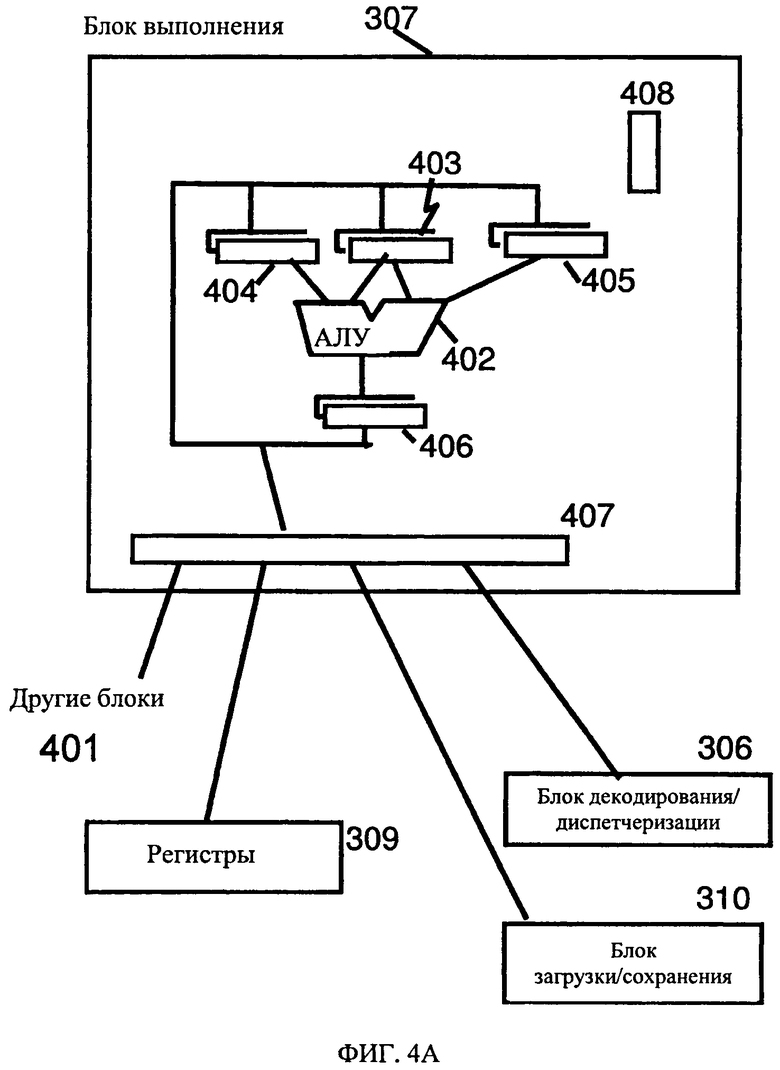

на фиг.4А - блок-схема, иллюстрирующая один из примеров блока выполнения,

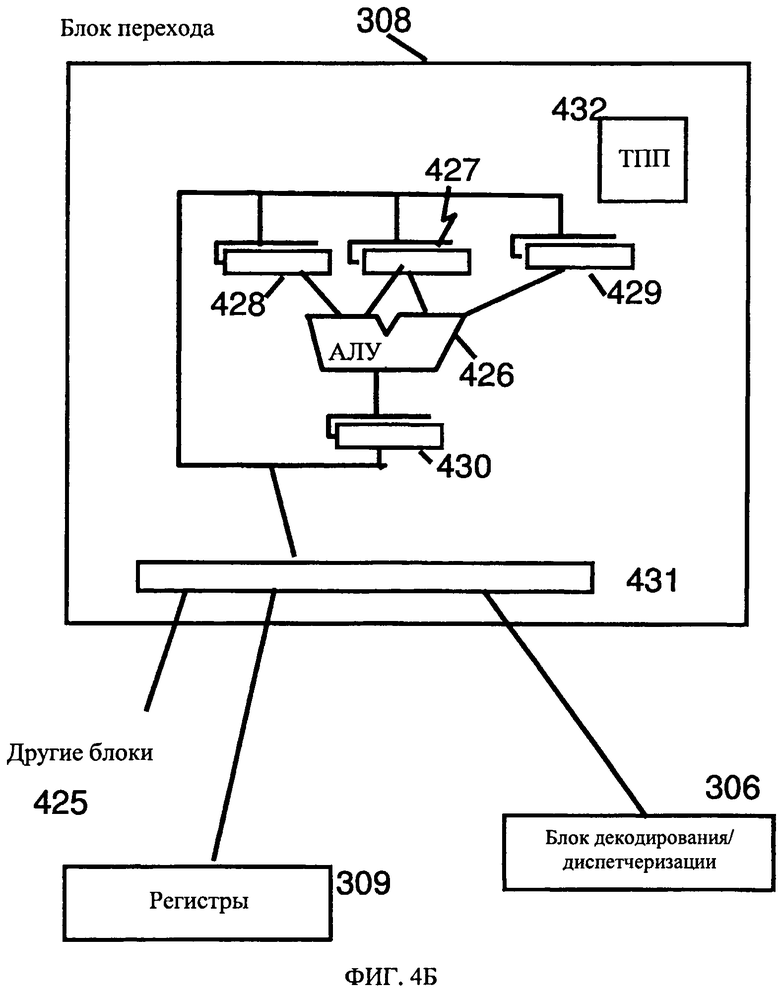

на фиг.4Б - блок-схема, иллюстрирующая один из примеров блока выполнения команд перехода,

на фиг.4В - блок-схема, иллюстрирующая один из примеров блока выполнения команд загрузки/сохранения,

на фиг.5 - блок-схема, иллюстрирующая один из примеров логического разделения,

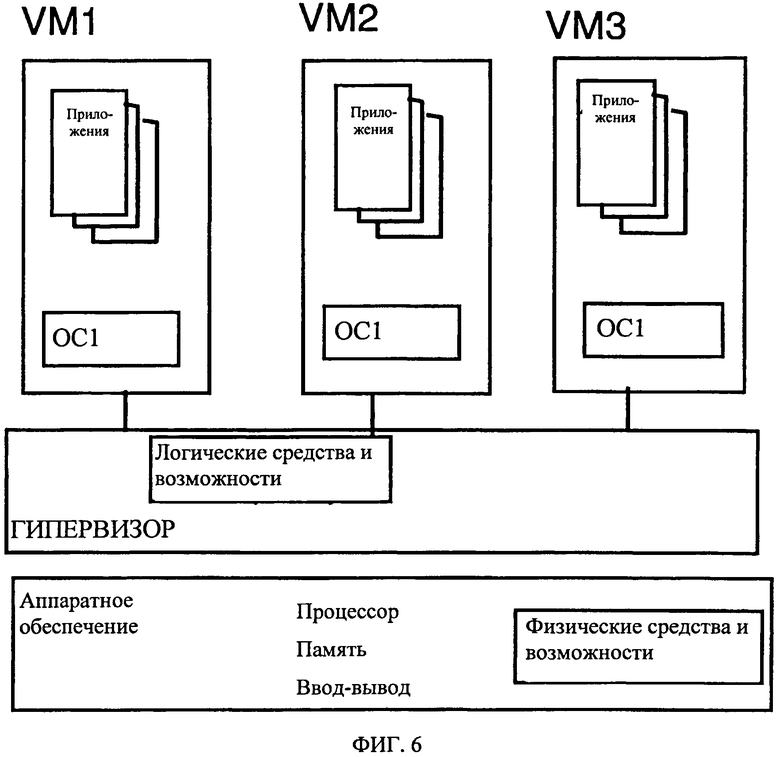

на фиг.6 - блок-схема, иллюстрирующая примеры элементов логического разделения,

на фиг.7 - блок-схема, иллюстрирующая примеры элементов логического разделения;

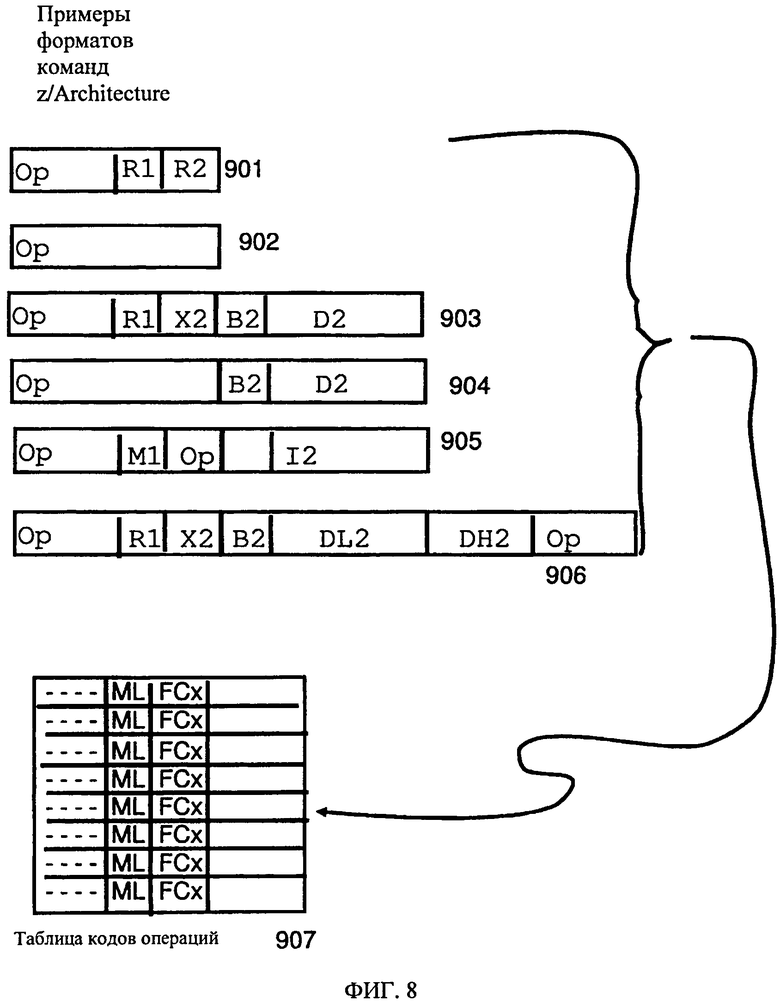

на фиг.8 - блок-схема, иллюстрирующая один из примеров таблицы кодов операций,

на фиг.9 - блок-схема, иллюстрирующая один из примеров метода блокирования,

на фиг.10 - блок-схема, иллюстрирующая один из примеров метода блокирования,

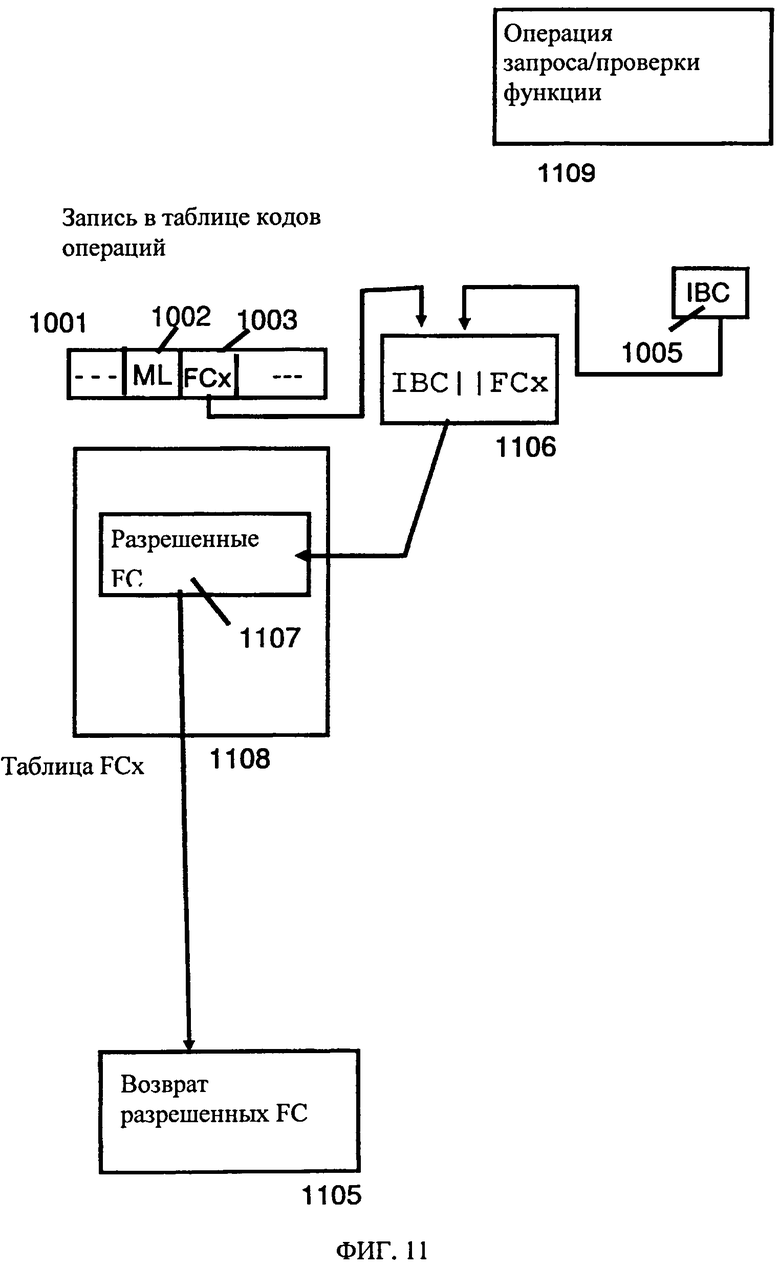

на фиг.11 - блок-схема, иллюстрирующая один из примеров метода блокирования, и

на фиг.12-17 - блок-схемы методов блокирования запроса функции.

Подробное описание

Варианты осуществления могут быть реализованы на практике посредством программного обеспечения (иногда называемого лицензионным внутренним кодом, аппаратно-программным обеспечением, микрокодом, милликодом, пикокодом и т.п., что во всех случаях согласуется с настоящим изобретением). Как показано на фиг.1A, обычно процессор, также известный как ЦП (центральный процессор) 1 системы 50, получает доступ к программному коду системы программного обеспечения, в котором воплощено настоящее изобретение, посредством долговременных запоминающих сред 11, таких как ПЗУ на компакт-дисках, накопитель на магнитной ленте или накопитель на жестких дисках. Программный код системы программного обеспечения может быть воплощен в любой из разнообразных известных сред для применения с системой обработки данных, такой как дискета, накопитель на жестких дисках или ПЗУ на компакт-дисках. Код может распределяться в таких средах или может распределяться пользователям из памяти 2 компьютера или запоминающего устройства одной компьютерной системы по сети 10 другим компьютерным системам для применения пользователями таких других систем.

В качестве альтернативы, программный код может быть воплощен в памяти 2 с возможностью доступа к нему для процессора 1, использующего процессорную шину. В таком программном коде содержится операционная система, которая управляет функцией и взаимодействием различных узлов вычислительной машины и одной или нескольких прикладных программ. Обычно подкачка страниц программного кода осуществляется из плотных запоминающих сред 11 в быстродействующее запоминающее устройство 2, в котором он доступен для обработки процессором 1. Методы и способы воплощения программного кода системы программного обеспечения в памяти, в физических средах и/или распределения программного кода посредством сетей хорошо известны и не будут дополнительно рассматриваться в описании. Программный код, созданный и хранящийся в материальной среде (включая без ограничения модули электронной памяти (ОЗУ), флэш-память, компакт-диски (CD), DVD, магнитную ленту и т.п.), часто именуется "компьютерным программным продуктом". Содержащая компьютерный программный продукт среда обычно может считываться устройством обработки данных предпочтительно в компьютерной системе для выполнения устройством обработки данных.

На фиг.1В проиллюстрирована характерная рабочая станция или аппаратная серверная система, в которой могут быть на практике реализованы варианты осуществления. В показанную на фиг.1В систему 100 входит характерная компьютерная система 101, такая как персональный компьютер, рабочая станция или сервер, включая необязательные периферийные устройства. Рабочая станция 101 имеет один или несколько процессоров 106 и шину для соединения процессора(-ов) 106 и других компонентов системы 101 и обеспечения связи между ними известными способами. Шина соединяет процессор 106 с памятью 105 и долговременным запоминающим устройством 107, которое может содержать накопитель на жестких дисках (например, включая любое из следующего: магнитный носитель, компакт-диск, цифровой многофункциональный диск и флэш-память) или, например, накопитель на магнитной ленте. В систему 101 также может входить адаптер пользовательского интерфейса, который посредством шины соединяет микропроцессор 106 с одним или несколькими устройствами сопряжения, такими как клавиатура 104, мышь 103, принтер/сканнер 110 и/или другие устройства сопряжения, которыми могут являться любое пользовательское устройство сопряжения, такое как сенсорный экран, дополнительная цифровая клавиатура и т.д. Шина посредством дисплейного адаптера также соединяет дисплей 102, такой как ЖК-дисплей или монитор с микропроцессором 106.

Система 101 может поддерживать связь с другими компьютерами или компьютерными сетями посредством сетевого адаптера, способного поддерживать связь 108 с сетью 109. Примерами сетевых адаптеров являются каналы связи, кольцевая сеть с эстафетным доступом, сеть Ethernet или модемы. В качестве альтернативы, рабочая станция 101 может поддерживать связь с использованием беспроводного интерфейса, такого как карта CDPD (сотовой системы передачи пакетов цифровых данных). Рабочая станция 101 может быть связана с другими такими компьютерами в локальной вычислительной сети (ЛВС) или глобальной вычислительной сети (ГВС), или рабочей станцией 101 может являться клиент, связанный отношениями клиент-сервер с другим компьютером и т.д. Все эти конфигурации, а также соответствующее коммуникационное оборудование и программное обеспечение известны из техники.

На фиг.2 проиллюстрирована сеть 200 обработки данных, в которой может быть реализован на практике один из вариантов осуществления. В сеть 200 обработки данных может входить множество отдельных сетей, таких как беспроводная сеть и проводная сеть, в каждую из которых может входить множество отдельных рабочих станций 101, 201, 202, 203, 204. Кроме того, как известно специалистам в данной области техники, в нее может входить одна или несколько ЛВС, в которую может входить множество интеллектуальных рабочих станций, связанных с главным процессором.

Как также показано на фиг.2, в сети также могут входить мэйнфреймы или серверы, такие как шлюз (клиент-сервер 206) или сервер приложений (удаленный сервер 208, который может осуществлять доступ к хранилищу данных, а также может быть доступен непосредственно с рабочей станции 205). Шлюз 206 служит точкой входа в каждую сеть 207. Шлюз необходим при подсоединении одного сетевого протокола к другому. Шлюз 206 предпочтительно может быть связан с другой сетью (например, сетью Интернет 207) линией связи. Шлюз 206 также может быть непосредственно связан с одной или несколькими рабочими станциями 101, 201, 202, 203, 204 с использованием линии связи. Шлюз может быть реализован с использованием сервера IBM eServerтм zSeries®zl0тм производства IBM Corp.

Доступ к программному коду системы программного обеспечения обычно осуществляет процессор 106 системы 101 посредством долговременных запоминающих сред 107, таких как ПЗУ на компакт-дисках, или накопитель на жестких дисках. Программный код системы программного обеспечения может быть воплощен в любой из разнообразных известных сред для применения с системой обработки данных, такой как дискета, накопитель на жестких дисках или ПЗУ на компакт-дисках. Код может распределяться в таких средах или может распределяться пользователям 210, 211 из памяти компьютера или запоминающего устройства одной компьютерной системы по сети другим компьютерным системам для применения пользователями таких других систем.

В качестве альтернативы, программный код 111 может быть воплощен в памяти 105 с возможностью доступа к нему для процессора 106 с использованием процессорной шины. В таком программном коде реализована операционная система, которая управляет функцией и взаимодействием различных узлов вычислительной машины и одной или нескольких прикладных программ 112. Обычно подкачка страниц программного кода осуществляется из плотных запоминающих сред 107 в быстродействующее запоминающее устройство 105, в котором он доступен для обработки процессором 106. Методы и способы воплощения программного кода системы программного обеспечения в памяти, в физических средах и/или распределения программного кода посредством сетей хорошо известны и не будут дополнительно рассматриваться в описании. Программный код, созданный и хранящийся в материальной среде (включая без ограничения модули электронной памяти (ОЗУ), флэш-память, компакт-диски, цифровые многофункциональные диски, магнитную ленту и т.п.), часто именуется "компьютерным программным продуктом". Содержащая компьютерный программный продукт среда обычно может считываться устройством обработки данных предпочтительно в компьютерной системе для выполнения устройством обработки данных.

Кэш, который является наиболее легкодоступным для процессора (обычно более быстродействующим и менее объемным, чем другие кэши процессора), представляет собой кэш низшего уровня (L1 или уровня 1), а основное запоминающее устройство (основная память) представляет собой кэш высшего уровня (L3 в случае 3 уровней). Кэш низшего уровня часто поделен кэшем команд (I-кэш), в котором хранятся машинные команды для выполнения, и кэш данных (D-кэш), в котором хранятся операнды, хранимые в памяти.

На фиг.3 проиллюстрирован один из примеров осуществления процессора 106. Обычно с целью помещения в буфер блоков памяти и повышения производительности процессора используется один или несколько уровней кэша 303. Кэш 303 представляет собой высокоскоростной буфер, в котором в строках данных кэша хранятся данные в памяти, которые вероятно будут использоваться. Типичные строки данных кэша содержат 64, 128 или 256 байтов данных в памяти. Для кэширования команд и для кэширования данных часто используются раздельные кэши. Согласованность кэшей (синхронизация копий строк в памяти и в кэшах) часто обеспечивается различными алгоритмами слежения ("snoop"), хорошо известными из техники. Основное запоминающее устройство 105 процессорной системы часто называют кэшем. В процессорной системе, имеющей 4 уровня кэша 303, основное запоминающее устройство 105 иногда называют кэшем уровня 5 (L5), поскольку оно обычно является более быстродействующими и представляет собой лишь часть энергонезависимого запоминающего устройство (ЗУПД, ЗУ на ленте и т.д.), которое доступно для компьютерной системы. Основное запоминающее устройство 105 "кэширует" страницы данных, которые подкачиваются в основное запоминающее устройство 105 и откачиваются из него операционной системой.

Программный счетчик (счетчик команд) 311 отслеживает адрес текущей команды для выполнения. Счетчик команд в процессоре на основе z/Architecture является 64-разрядным, при этом он может быть усечен до 31 или 24 разрядов с целью поддержки ранее существовавших ограничений адресации. Поскольку счетчик команд обычно воплощен в слове состояния программы (PSW) компьютера, оно сохраняется при переключении контекста. Соответственно, выполняемая программа с показанием счетчика команд может прерываться, например, операционной системой (при переключении контекста из программной среды в среду операционной системы). PSW программы поддерживает показание счетчика команд, пока программа неактивна, а во время выполнения операционной системы используется счетчик команд (в PSW) операционной системы. Обычно показание счетчика команд приращивается на величину, равную числу байтов текущей команды. RISC-команды (на основе вычислений с сокращенным набором команд) обычно имеют фиксированную длину, тогда как CISC-команды (на основе вычислений с полным набором команд) обычно имеют переменную длину. Команды, используемые в системе IBM z/Architecture, являются CISC-командами, имеющими длину 2, 4 или 6 байтов. Показание счетчика 311 команд изменяется, например, в результате операции переключения контекста или операции выбранного перехода согласно команде перехода. При операции переключения контекста в слове состояния программы (PSW) сохраняется текущее показание счетчика команд вместе с другой информацией о состоянии выполняемой программы (такой как коды условий), и загружается новое показание счетчика команд, указывающее команду нового программного модуля для выполнения. Операция выбранного перехода выполняется, чтобы позволить программе принимать решения, или чтобы выполнять программный цикл путем загрузки в счетчик 311 команд результата команды перехода.

Обычно для вызова команд от имени процессора 106 применяется блок 305 вызова команд. Блок выборки осуществляет выборку "очередных последовательных команд", целевых команд из команд выбранного перехода или первых команд программы, следующей за переключением контекста. В современных блоках вызова команд часто применяют методы выборки с целью предварительного вызова команд по предположению, исходя из вероятности использования команд, предварительная выборка которых была осуществлена. Например, блок выборки может осуществлять выборку 16 байтов команды, содержащих очередную последовательную команду, и дополнительных байтов следующих далее команд.

Затем вызванные команды выполняются процессором 106. В одном из вариантов осуществления вызванная команда(-ы) передается блоку 306 диспетчеризации блока выборки. Блок диспетчеризации декодирует команду(-ы) и пересылает информацию о декодированной команде(-ах) соответствующим блокам 307, 308, 310. Блок 307 выполнения обычно принимает информацию о декодированных арифметических командах от блока 305 вызова команд и выполняет арифметические операции с операндами в соответствии с содержащимся в команде кодом операции. Операнды предоставляются блоку 307 выполнения предпочтительно из памяти 105, структурированных регистров 309 или из непосредственного поля выполняемой команды. Сохраненные результаты выполнения хранятся в памяти 105, регистрах 309 или в другом машинном аппаратном обеспечении (таком как управляющие регистры, регистры PSW и т.п.).

Рассмотрим фиг.5, на которой показан один из примеров среды виртуальной машины (VM). Программа-гипервизор (которая сама может являться операционной системой (ОС), такой как система zVM производства IBM) действует в мультипроцессорном аппаратном обеспечении, содержащем множество физических процессоров, физическую основную память и физические адаптеры для связи с периферийными устройствами ввода-вывода, включающими запоминающее устройство, сети, дисплеи и т.п. Гипервизор создает отображения VM (например, VM1, VM2 и VM3), позволяющие программному обеспечению, включая ОС и прикладные программы, действовать в виртуальной машине, использующей виртуальные ресурсы. Программному обеспечению, действующему в VM, не известно о том, что оно действует в VM, при этом оно использует виртуальные ресурсы, как если бы они являлись физическими ресурсами. Операционная система zVM производства IBM способна создавать отображения "гостей", каждое из которых фактически является виртуальной машиной. Кроме того, любая гостевая программа zVM может сама выполнять операционную систему zVM, создавая "гостей второго уровня". Соответственно, виртуальная машина (отображение гостя) может входить в иерархию виртуальных машины, при этом каждая zVM играет роль гипервизора для отображений своих гостей. С другой стороны, мультипроцессорная платформа может состоять из "физических разделов", каждый из которых может представлять собой закрепленные ресурсы (процессоры, память, систему ввода-вывода). Каждый физический раздел представляет собой VM, поскольку программному обеспечению, действующему в разделе, не известно о ресурсах машины, не закрепленной за разделом. Соответственно, ресурсы машины "виртуализируются". В другом варианте осуществления главная машина может поддерживать логические разделы, каждый из которых представляет собой VM.

Визуализация представлена, например, в техническом описании VMware® под названием "Virtualization Overview" и в описании инфраструктуры 3 VMware® "VMware VMotion and CPU Compatibility". Кроме того, в патентной заявке US 2009/0070760 под названием "VIRTUAL MACHINE (VM) MIGRATION BETWEEN PROCESSOR ARCHITECTURES" (заявитель - Khatri и др.), поданной 6 сентября 2007 г., рассмотрена эмуляция определенного набора средств, обеспечивающая миграцию VM между сходными пулами машин путем маскирования выборочных разрядов регистра CPUID.

Как показано на фиг.6, каждая VM может иметь отличающуюся OC и отличающиеся приложения. Например, OC1 может представлять собой систему z/OS производства IBM, а OC2 может представлять собой систему zLinux производства IBM, или все OC могут представлять собой одинаковые OC, такие как z/OS.

Гипервизор создает логические средства, ресурсы и возможности для каждой VM на основании физических средств, ресурсов и возможностей. В одном из примеров системы каждой VM выделяются части физической памяти путем динамической трансляции адреса, при этом физические процессоры, как и возможности ввода-вывода, используются VM с разделением времени.

Как показано на фиг.7, каждый логический процессор имеет доступ к регистрам физических средств посредством управляемой гипервизором маски логических средств. Соответственно, программное обеспечение, действующее в логических процессорах, может создавать видимость работы на общем уровне архитектуры процессоров, даже если архитектура реальных процессоров находится на различных уровнях. В одном из примеров регистром физических средств может являться регистр CPUID Intel, в котором указан уровень архитектуры процессора Intel, а также конкретные средства, доступные для программатора. Маска логических средств запрограммирована на предоставление программному обеспечению в виртуальной машине (VM) всех или подмножества CPUID физических процессоров, когда VM запрашивает CPUID соответствующего логического процессора.

В руководстве по архитектуре процессоров х86 Intel® "Intel® Itanium® Architecture Software Developer's Manual" том 2, пересмотренное издание 2.2, январь 2006 г., описаны регистры CPUID для определения средств, поддерживаемых процессором. Регистры CPUID являются непривилегированными, и доступ к ним осуществляется с использованием команды косвенного переноса данных (из регистров). Все регистры сверх числа регистров CPUID зарезервированы, и в случае доступа к ним распознается ошибка вследствие доступа к зарезервированному регистру/полю. Операции записи не разрешены, и для таких операций не существуют команды. В регистрах 0 и 1 CPUID 0 задано имя поставщика в формате ASCII для реализации процессора. Все байты по окончании строки вплоть до 16-го байта равны нулю. Символы ASCII помещаются в более низкий регистр числа или более низкие нумерованные положения байтов. Регистр 4 CPUID содержит общую информацию прикладного уровня о возможностях процессора. В нем содержится набор флаговых разрядов, используемых, чтобы указывать, поддерживается ли заданное средство в модели процессора. Если разряд равен единице, средство поддерживается, если разряд равен нулю, средство не поддерживается. При добавлении (или исключении) новых средств в будущих моделях процессоров наличие (или исключение) новых средств будет указываться разрядами новых возможностей. Регистр 4 CPUID логически разделен на две половины, в каждой из которых содержится информация об общих средствах и возможностях, но которые имеют различные модели использования и возможности доступа; эта информация отображает состояние любых действующих или заблокированных средств. Как верхняя, так и нижняя половины регистра 4 CPUID доступны посредством команды косвенного перемещения регистра; в зависимости от реализации время ожидания этого доступа может являться длительным, и этот способ доступа неприменим для управления версиями кодов с малым временем ожидания с использованием самовыбора. Кроме того, верхняя половина регистра 4 CPUID также доступна с использованием команды проверки средств; время ожидания этого доступа сравнимо со временем ожидания выполнения команды разряда проверки, и этот способ обеспечивает управление версиями кодов с малым временем ожидания с использованием самовыбора.

В принципах действия системы z/Architecture описана команда сохранения расширенного списка средств (Store Facility List Extended) (STFLE), которая подобно регистру CPUID Intel предоставляет программному обеспечению сведения о средствах (или уровнях архитектуры) базовых центральных процессоров (ЦП) или процессоров. Команда STFLE имеет формат, проиллюстрированный далее в Таблице 1.

Команда STFLE (Таблица 1) содержит разряды поля кода операции (0-15), разряды поля В2 регистра (16-19) и разряды (непосредственного) поля D2 смещения (20-31). При выполнении команды STFLE машиной сохраняется список разрядов, содержащих информацию о средствах в памяти программ, адрес которой определяется путем сложения содержимого регистра, заданного в поле В2 команды, и 12-разрядного непосредственного поля D2, при этом адрес памяти начинается с двойного слова (длиной 8 байтов, длина одного слова - 4 байта), заданного адресом второго операнда ((B2)+D2). Адрес памяти программ в системе z/Architecture является объектом динамической трансляции адреса (DAT).

Зарезервированными разрядами являются разряды, которые в данный момент не назначены для отображения какого-либо средства. Зарезервированные разряды для крайних левых двойных слов, в которых назначены разряды средства, хранятся в виде нулей. Двойные слова справа от двойного слова, в котором назначен разряд средства с наибольшим номером для модели, хранятся необязательно. Для двойных слов, которые не хранятся, не распознаются исключительные ситуации при доступе и события PER. Второй операнда в двойных словах имеет размер на единицу больше значения, заданного в разрядах 56-63 общего регистра 0. Остальные разряды общего регистра 0 не назначены и должны содержать нули; в противном случае в будущем может не обеспечиваться программная совместимость.

Когда второй операнд имеет достаточный размер, чтобы вместить все разряды средства, назначенные для модели, в местоположении второго операнда сохраняется полный список средств, разряды 56-63 общего регистра 0 обновляются таким образом, чтобы иметь значение на единицу меньше числа двойных слов, необходимого для вмещения всех разрядов средства, назначенных для модели, и устанавливается код 0 условия.

Когда второй операнд не имеет достаточного размера, чтобы вместить все разряды средства, назначенные для модели, сохраняется только число двойных слов, заданное размером второго операнда, разряды 56-63 общего регистра 0 обновляются таким образом, чтобы иметь значение на единицу меньше числа двойных слов, необходимого для вмещения всех разрядов средства, назначенных для модели, и устанавливается код 3 условия.

В результате выполнения команды устанавливается значение кода условия, которое сохраняется во время переключения контекста с помощью слова состояния программы (PSW).

Особые условия

Второй операнд должен быть указан на границе двойного слова; в противном случае распознается исключительная ситуация при нарушении заданных условий.

Результирующий код условия

0 Сохранен полный список средств

1 -

2 -

3 Сохранен неполный список средств

Исключительные ситуации в процессе выполнения программы Доступ (сохранение, второй операнд)

Операция (если не установлено средство сохранения расширенного списка средств)

Спецификация

Комментарии к программированию

Команда сохранения расширенного списка средств может выполняться значительно медленнее, чем просто при проверке байта в запоминающем устройстве. Программы, которые часто требуется проверять на присутствие какого-либо средства, например, кода с двумя ветвями, в одной из ветвей которой используется средство, а в другой - не используется, должны выполнять команду сохранения расширенного списка средств один раз при инициализации. Впоследствии программа может проверяться на присутствие средства путем изучения сохраненного результата с использованием какой-либо команды, такой как команда проверки с маскированием (TEST UNDER MASK).

Когда установлен код 0 условия, разряды 56-63 общего регистра 0 обновляются и указывают число сохраненных двойных слов. Если во время выполнения программы игнорируются результаты в общем регистре 0, должно быть обеспечено, что весь второй операнд в запоминающем устройстве установлен на ноль до выполнения команды сохранения расширенного списка средств.

В Таблице 2 показаны назначаемые известной системой z/Architecture STFLE разряды и их значение. Значение разряда устанавливается на единицу независимо от текущего режима архитектуры, если его значение является истинным. Значение применимо к текущему режиму архитектуры, если только не указано, что оно применимо к конкретному режиму архитектуры.

Неназначенные разряды резервируются для указания новых средств; в будущем эти разряды могут сохраняться как единицы.

Список средств согласно известной системе z/Architecture определяется, как показано далее в Таблице 2.

Таблица 2

Значение разряда, когда разряд равен единице

0 Установлены команды, снабженные отметкой "N3" на сводных диаграммах команд в главах 7 и 10 описания системы z/Architecture.

1 Установлен режим архитектуры системы z/Architecture.

2 Действует режим архитектуры системы z/Architecture. Когда этот разряд равен нулю, действует режим архитектуры системы ESA/390.

3 Установлено средство расширенной DAT в режиме архитектуры системы z/Architecture. Средство расширенной DAT содержит команду аннулирования записи в таблице DAT (INVALIDATE DAT TABLE ENTRY) (IDTE) и команду сравнения, свопинга и удаления (COMPARE AND SWAP AND PURGE) (CSPG).

4 В случае команды аннулирования записи в таблице DAT (IDTE) выполняется операция аннулирования и очистки путем выборочной очистки записей из комбинированной таблицы региона и сегментов, когда аннулируется запись или записи из таблицы сегментов. В случае IDTE также выполняется операция очистки путем ASCE. При условии, что значением разряда 4 не является единица, IDTE просто удаляет все TLB. Разряд 3 равен единице, если разряд 4 равен единице.

5 В случае команды аннулирования записи в таблице DAT (IDTE) выполняется операция аннулирования и очистки путем выборочной очистки записей из комбинированной таблицы регионов и сегментов, когда аннулируется запись или записи из таблицы региона. Разряды 3 и 4 равны единице, если разряд 5 равен единице.

6 Установлено средство повторного использования ASN и LX в режиме архитектуры системы z/Architecture.

7 Установлено средство сохранения расширенного списка средств.

8 Установлено средство расширенной DAT в режиме архитектуры системы z/Architecture.

9 Установлено средство восприятия состояния выполнения в режиме архитектуры системы z/Architecture.

10 Установлено средство условного SSKE в режиме архитектуры системы z/Architecture.

11 Установлено средство конфигурационной топологии в режиме архитектуры системы z/Architecture.

16 Установлено средство 2 расширенной трансляции.

17 Установлено средство содействия засекречиванию сообщений.

18 Установлено средство длительного смещения в режиме архитектуры системы z/Architecture.

19 Средство длительного смещения является высокоэффективным. Разряд 18 равен единице, если разряд 19 равен единице.

20 Установлено средство умножения и сложения/вычитания HFP.

21 Установлено расширенное промежуточное средство в режиме архитектуры системы z/Architecture.

22 Установлено средство 3 расширенной трансляции в режиме архитектуры системы z/Architecture.

23 Установлено средство ненормализованного расширения HFP в режиме архитектуры системы z/Architecture.

24 Установлено средство расширения ETF2.

25 Установлено средство быстрого сохранения показания часов в режиме архитектуры системы z/Architecture.

26 Установлено средство расширения анализа в режиме архитектуры системы z/Architecture.

27 Установлено средство переноса с необязательными заданными условиями в режиме архитектуры системы z/Architecture.

28 Установлено средство управления часами TOD в режиме архитектуры системы z/Architecture.

30 Установлено средство расширения ETF3 в режиме архитектуры системы z/Architecture.

31 Установлено средство вывода машинного времени в режиме архитектуры системы z/Architecture.

32 Установлено средство сравнения, свопинга и сохранения сравнения, в режиме архитектуры системы z/Architecture.

33 Установлено средство 2 сравнения, свопинга и сохранения в режиме архитектуры системы z/Architecture.

34 Установлено средство расширения общих команд в режиме архитектуры системы z/Architecture.

35 Установлено средство выполнения расширений в режиме архитектуры системы z/Architecture.

39 Выделено для внутреннего использования IBM.

41 Установлены средства расширения поддержки операций с плавающей точкой (переноса FPR-GR, оперирования со знаками FPS и округления DFP) в режиме архитектуры системы z/Architecture.

42 Установлено средство DFP (десятичной плавающей точки) в режиме архитектуры системы z/Architecture.

43 Средство DFP является высокоэффективным. Разряд 42 равен единице, если разряд 43 равен единице.

44 Установлена команда PFPO в режиме архитектуры системы z/Architecture.

Команда может предусматривать выполнение одной функции в какой-либо архитектуре или в некоторых случаях любой из множества выбираемых функций. Выбираемые функции, определенные для команды, могут различаться в зависимости от машины. Например, когда многофункциональная команда впервые вводится в структурированный набор команд, она может иметь всего несколько выбираемых функций. В позднее структурированном наборе команд для ранее введенной многофункциональной команды может быть предусмотрено большее число выбираемых функций. В одном из вариантов осуществления VM может быть выделено подмножество выбираемых функций физического процессора, при этом команда, выполняемая в логическом процессоре VM, может осуществлять запрос списка доступных функций логического процессора, в ответе на который указаны только функции, выделенные VM, несмотря на то, что физический процессор способен выполнять большее число выбираемых функций. В одном из вариантов осуществления для этого используется средство перехвата указывающей функцию команды (Function-Indicating-Instruction Interception Facility) (FIIIF), которое позволяет гипервизору прерывать или перехватывать выполнение данной функции запроса гостем (виртуальной машиной) и представлять сокращенный список доступных функций. В другом варианте осуществления гипервизор задает, например, посредством битовой маски множество функций для сообщения гостю, а функция запроса многофункциональной команды сообщает этот список. Кроме того, в одном из вариантов осуществления при попытке выполнения выбранной выбираемой функции командой, выполняемой в логическом процессоре, возникает исключительная ситуация в процессе выполнения программы.

В случае многофункциональной команды, способной запрашивать наличие установленных функций, а также выполнять выбранную из установленных функций, выполнение установленных функций, включая функцию запроса, может происходить в аппаратном обеспечении (включая, например, схему и микрокод) для достижения наибольшей эффективности. В одном из вариантов осуществления, когда установлено FIIIF, выполнение функции запроса перехватывается программным, а не аппаратным обеспечением. Соответственно, только выполнение функции запроса будет связано с дополнительной задержкой, чтобы определить, о каких установленных средствах следует сообщать. В одном из вариантов осуществления за перехват отвечает код гипервизора, который выполняет функцию запроса и передает соответствующие результаты от имени виртуальной машины.

Одним из примеров команды, содержащей выбираемые функции, является команда шифрования сообщения системы z/Architecture.

Команда шифрования сообщения (КМ) может предусматривать выполнение любых из множества функций шифрования сообщения. Одной из функций, предусмотренных командой шифрования сообщения, является запрос у процессора, содержащего значащие разряды списка функций шифрования сообщения, поддерживаемых процессором.

Команда шифрования сообщения (Таблица 3) имеет следующий формат, в котором R1 означает первый общий регистр, a R2 означает второй общий регистр.

30 Команда шифрования сообщения (Таблица 3) выполняется следующим образом.

Выполняется функция, заданная кодом функции в подразумеваемом общем регистре 0.

Разряды 16-23 команды игнорируются.

Двоичные разряды 57-63 общего регистра 0 содержат код функции.

В Таблице 4 показаны текущие коды функций, присвоенные команда шифрования сообщения и шифрования сообщения со сцеплением, соответственно (0-3 и 18-20). Все остальные коды функции являются свободными. В случае функций шифрования разряд 56 является модифицирующим разрядом, который указывает, должно осуществляться шифрование или дешифрование. В случае всех остальных функций модифицирующий разряд игнорируется. Все остальные разряды общего регистра 0 игнорируются.

В подразумеваемом общем регистре 1 содержится логический адрес крайнего левого байта блока параметров в запоминающем устройстве. В режиме 24-разрядной адресации содержимое двоичных разрядов 40-63 общего регистра 1 образует адрес, а содержимое двоичных разрядов 0-39 игнорируется. В режиме 31-разрядной адресации содержимое двоичных разрядов 33-63 общего регистра 1 образует адрес, а содержимое двоичных разрядов 0-32 игнорируется. В режиме 64-разрядной адресации содержимое двоичных разрядов 0-63 общего регистра 1 образует адрес.

Функция запроса обеспечивает средство индикации доступности остальных функций. В случае функции запроса игнорируется содержимое общих регистров, указанных в полях (Rl, R2) и R2+1 команды.

В случае всех остальных функций второй операнд (заданный в поле R2) шифруется, как указано кодом функции, с использованием криптографического ключа в блоке параметров, а полученный результате помещается в местоположение первого операнда.

В случае команды шифрования сообщения со сцеплением при шифровании также используется исходное значение сцепления в блоке параметров, которое обновляется в ходе выполнения операции. Использование регистров для 24-разрядной адресации показано в Таблице 5.

В поле R1 указан общий регистр, и должен быть указан регистр с четным номером; в противном случае распознается исключительная ситуация при нарушении заданных условий.

В поле R2 указана четно-нечетная пара общих регистров, и должен быть указан регистр с четным номером; в противном случае распознается исключительная ситуация при нарушении заданных условий.

Местоположение крайнего левого байта первого и второго операндов задано содержимым общих регистров R1 и R2. Число байтов в местоположении второго операнда задано в общем регистре R2+1. Первый операнд имеет такую же длину, как и второй операнд.

В ходе выполнения операции адреса в общих регистрах R1 и R2 увеличивается на число обработанных байтов, а длина в общем регистре R2+1 уменьшается на такую же величину. Формирование и обновление адреса и длины зависят от режима адресации.

В режиме 24-разрядной адресации содержимое двоичных разрядов 40-63 общих регистров R1 и R2 образует адреса первого и второго операндов, соответственно, а содержимое двоичных разрядов 0-39 игнорируется; разряды 40-63 обновленных адресов заменяют соответствующие разряды в общих регистрах R1 и R2, переносы двоичного разряда 40 обновленного адреса игнорируются, а содержимое двоичных разрядов 32-39 общих регистров R1 и R2 устанавливается на ноль. В режиме 31-разрядной адресации содержимое двоичных разрядов 33-63 общих регистров R1 и R2 образует адреса первого и второго операндов, соответственно, а содержимое двоичных разрядов 0-32 игнорируется; разряды 33-63 обновленных адресов заменяют соответствующие разряды в общих регистрах R1 и R2, переносы двоичного разряда 33 обновленного адреса игнорируются, а содержимое двоичного разряда 32 общих регистров R1 и R2 устанавливается на ноль. В режиме 64-разрядной адресации содержимое двоичных разрядов 0-63 общих регистров R1 и R2 образует адреса первого и второго операндов, соответственно; разряды 0-63 обновленных адресов заменяют содержимое общих регистров R1 и R2, а переносы двоичного разряда 0 игнорируются.

В режиме как 24-разрядной, так и 31-разрядной адресации содержимое двоичных разрядов 32-63 общего регистра R2+1 образует 32-разрядное двоичное целое число без знака, которое задает число байтов в первом и втором операндах, а содержимое двоичных разрядов 0-31 игнорируется; разряды 32-63 обновленного значения заменяют соответствующие разряды в общем регистре R2+1. В режиме 64-разрядной адресации содержимое двоичных разрядов 0-63 общего регистра R2+1 образует 64-разрядное двоичное целое число без знака, которое задает число байтов в первом и втором операндах; а обновленное значение заменяет содержимое общего регистра R2+1.

В режиме 24-разрядной или 31-разрядной адресации содержимое двоичных разрядов 0-31 общих регистров R1, R2 и R2+1 всегда остается без изменения. Содержимое только что описанных общих регистров проиллюстрировано на прилагаемых чертежах.

В режиме регистрации доступа в регистрах 1, R1 и R2 доступа заданы адресные пространства, содержащие блок параметров, первый и второй операнды, соответственно.

Результат получают, как если бы обработка начиналась с левого конца как первого, так и второго операндов, и блок за блоком продолжалась вправо. Операция завершается после того, как во втором операнде обработано и помещено в местоположение первого операнда число байтов, заданное в общем регистре R2+1 (что именуется успешным завершением), или после того, как обработано определенное ЦП число блоков, меньшее, чем длина второго операнда (что именуется частичным завершением). Определенное ЦП число блоков зависит от модели и может отличаться при каждом выполнении команды. Определенное ЦП число блоков обычно отличается от нуля. В некоторых необычных ситуациях это число может быть равным нулю, и может быть установлен неизменяющийся код 3 условия. Тем не менее, ЦП защищает от бесконечного повторения этой неизменяющейся ситуации.

Результаты в местоположении первого операнда и поле значений сцепления являются непредсказуемыми при возникновении любой из следующих ситуаций.

Поле криптографического ключа перекрывает какую-либо часть первого операнда.

Поле значений сцепления перекрывает какую-либо часть первого операнда или второго операнда.

Первый и второй операнды перекрывают друг друга с разрушением. Считается, что операнды перекрывают друг друга с разрушением, когда местоположение первого операнда используется в качестве источника после того, как в него перемещены данные, при условии, что обработка осуществляется слева направо по одному байту за один раз.

Когда операция заканчивается вследствие успешного завершения, устанавливается код 0 условия, а результирующее значение в R2+1 равно нулю. Когда операция заканчивается вследствие частичного завершения, устанавливается код 3 условия, а результирующее значение в R2+1 не равно нулю.

Когда распознается событие PER изменения запоминающего устройства, в местоположениях первого операнда сохраняется менее 4 дополнительных килобайт прежде, чем о событии сообщается.

Когда длина второго операнда изначально равна нулю, к блоку параметров, первому и второму операндам не осуществляется доступ, общие регистры R1, R2 и R2+1 не изменяются, и устанавливается код 0 условия.

Когда содержимое полей R1 и R2 является одинаковым, содержимое указанных регистров увеличивается лишь на число обработанных байтов, а не на удвоенное число обработанных байтов.

С точки зрения других ЦП и канальных программ обращения к операндам блоков параметров и памяти могут являться обращениями с коллективным доступом, выборка блоков из этих местоположений запоминающего устройства необязательно осуществляется параллельно, и последовательность этих доступов или обращений является неопределенной.

В некоторых необычных ситуациях выполнение команды может завершаться путем установки кода 3 условия без обновления регистров значения сцепления для отображения последнего блока первого и второго обработанных операндов. Размер обработанного блока в этом случае зависит от ситуации и модели, но ограничен таким образом, что части первого и второго операндов, которые были обработаны без сообщения об этом, не перекрываются в запоминающем устройстве. Во всех случаях, когда это применимо, устанавливаются разряды и сообщается о событиях PER изменения запоминающего устройства для всех обработанных местоположений первого операнда.

Об исключительных ситуациях при доступе может сообщаться для большей части операнда, чем часть, обработанная при разовом выполнении команды; тем не менее, исключительные ситуации при доступе не распознаются для местоположений за пределами длины операнда, а также местоположений далее 4 килобайт за пределами текущего обрабатываемого местоположения.

Команда шифрования сообщения имеет следующие коды функции.

Пояснение: - неприменимо

В одном из примеров машины функции шифрования сообщения могут быть реализованы с использованием в качестве примера команды шифрования сообщения. В примере реализации главные процессоры могут выполнять все показанные функции (с кодами 0-3 и 18-20 функции). Операционная система (ОС) главного компьютера (или гипервизора) может создавать одну или несколько виртуальных машинных для гостевых OC. Для архитектуры предыдущего уровня может быть определена одна виртуальная машина без команд шифрования сообщения.

Если установлено средство блокирования команды, а команды шифрования сообщения указаны как заблокированные команды для VM, в одном из вариантов осуществления виртуальная машина не разрешает выполнение команды шифрования сообщения программами, действующими в виртуальной машине, несмотря на то, что базовая главная машина поддерживает команды шифрования сообщения. Попытка выполнения команды шифрования сообщения в VM приведет к проверке программы (исключительной ситуации в процессе выполнения программы).

Если установлено средство блокирования функции, и в VM разрешено только подмножество функций шифрования сообщения (например, коды 0-3 функции), в другом варианте осуществления виртуальная машина разрешает выполнение команды шифрования сообщения, но не разрешает выполнение команд шифрования сообщения с кодом функции помимо 0-3 программами, действующими в виртуальной машине, несмотря на то, что базовая главная машина поддерживает команды шифрования с кодами функций (0-3 и 18-20). Попытка выполнения команды шифрования сообщения с кодами функции помимо 0-3, такими как любой из 18-20, приведет к проверке программы (исключительной ситуации в процессе выполнения программы).

Если установлено средство проверки/запроса функция, и в VM разрешено только подмножество функций шифрования сообщения (например, коды функции 0-3), в другом варианте осуществления выполнение запроса шифрования сообщения возможно только с кодами 0-3 функции, хотя базовая главная машина поддерживает коды 0-3 и 18-20 функции.

Другие примеры многофункциональных команд системы z/Architecture

Команды вычисления профиля промежуточного сообщения (COMPUTE INTERMEDIATE MESSAGE DIGEST) (KIMD) и вычисления профиля последнего сообщения (COMPUTE LAST MESSAGE DIGEST) (KLMD)

При выполнении компьютерной системой выполняется функция, заданная кодом функции в общем регистре 0. Разряды 16-23 команды и поле R1 игнорируются. Двоичные разряды 57-63 общего регистра 0 содержат код функции. Разряд 56 общего регистра 0 должен быть равен нулю; в противном случае распознается исключительная ситуация при нарушении заданных условий. Все остальные разряды общего регистра 0 игнорируются. В общем регистре 1 содержится логический адрес крайнего левого байта блока параметров в запоминающем устройстве. В режиме 24-разрядной адресации содержимое двоичных разрядов 40-63 общего регистра 1 образует адрес, а содержимое двоичных разрядов 0-39 игнорируется. В режиме 31-разрядной адресации содержимое двоичных разрядов 33-63 общего регистра 1 образует адрес, а содержимое двоичных разрядов 0-32 игнорируется. В режиме 64-разрядной адресации содержимое двоичных разрядов 0-63 общего регистра 1 образует адрес. Все остальные коды функции не назначены. Функция запроса обеспечивает средство индикации доступности остальных функций. Содержимое общих регистров R2 и R2+1 игнорируется в случае функции запроса. В случае всех остальных функций второй операнд обрабатывается, как задано кодом функции, с использованием исходного значения сцепления в блоке параметров, а полученный результат заменяет значение сцепления. Для вычисления профиля последнего сообщения в операции также используется длина сообщения в битах в блоке параметров. Операция выполняется до достижения конца местоположения второго операнда или обработки определенного ЦП числа байтов, в зависимости от того, что наступит раньше. Результат указывается в коде условия. В поле R2 указана четно-нечетная пара общих регистров, и в нем должен быть указан регистр с четным номером; в противном случае распознается исключительная ситуация при нарушении заданных условий. Местоположение крайнего левого байта второго операнда задано содержимым общего регистра R2. Число байтов в местоположении второго операнда задано в общем регистре R2+1. В ходе выполнения операции адрес в общем регистре R2 увеличивается на число байтов, обработанных во втором операнде, а длина в общем регистре R2+1 уменьшается на такую же величину. Формирование и обновление адреса и длины зависят от режима адресации. В режиме 24-разрядной адресации содержимое двоичных разрядов 40-63 общего регистра R2 образует адрес второго операнда, а содержимое двоичных разрядов 0-39 игнорируется; разряды 40-63 обновленного адреса заменяют соответствующие разряды в общем регистре R2, переносы двоичного разряда 40 обновленного адреса игнорируются, а содержимое двоичных разрядов 32-39 общего регистра R2 устанавливается на ноль. В режиме 31-разрядной адресации содержимое двоичных разрядов 33-63 общего регистра R2 образует адрес второго операнда, а содержимое двоичных разрядов 0-32 игнорируется; разряды 33-63 обновленного адреса заменяют соответствующие разряды в общем регистре R2, переносы двоичного разряда 33 обновленного адреса игнорируются, а содержимое двоичного разряда 32 общего регистра R2 устанавливается на ноль. В режиме 64-разрядной адресации содержимое двоичных разрядов 0-63 общего регистра R2 образует адрес второго операнда; разряды 0-63 обновленного адреса заменяют содержимое общего регистра R2, а переносы двоичного разряда 0 игнорируются. В режиме как 24-разрядной, так и 31-разрядной адресации содержимое двоичных разрядов 32-63 общего регистра R2+1 образует 32-разрядное двоичное целое число без знака, которое задает число байтов во втором операнде; а обновленное значение заменяет содержимое двоичных разрядов 32-63 общего регистра R2+1. В режиме 64-разрядной адресации содержимое двоичных разрядов 0-63 общего регистра R2+1 образует 64-разрядное двоичное целое число без знака, которое задает число байтов во втором операнде; а обновленное значение заменяет содержимое общего регистра R2+1. В режиме 24-разрядной или 31-разрядной адресации содержимое двоичных разрядов 0-31 общих регистров R2 и R2+1 всегда остается без изменения. В режиме регистрации доступа регистры 1 и R2 доступа задают адресные пространства, содержащие блок параметров и второй операнд, соответственно. Результат получают, как если бы обработка начиналась с левого конца второго операнда и блок за блоком продолжалась вправо. Операция завершается после того, как во втором операнде обработаны все исходные байты (что именуется успешным завершением), или после того, как обработано определенное ЦП число блоков, меньшее, чем длина второго операнда (что именуется частичным завершением). Определенное ЦП число блоков зависит от модели и может отличаться при каждом выполнении команды. Определенное ЦП число блоков обычно не равно нулю. В некоторых необычных ситуациях это число может быть равно нулю и может быть установлен неизменяющийся код 3 условия. Тем не менее, ЦП защищает от бесконечного повторения этой неизменяющейся ситуации. Когда поле значений сцепления перекрывает какую-либо часть второго операнда, результат в поле значений сцепления является непредсказуемым. При вычислении профиля промежуточного сообщения успешное завершение имеет место, когда во втором операнде обработано число байтов, заданное в общем регистре R2+1. При вычислении профиля последнего сообщения после того, как во втором операнде обработаны все байты, заданные в общем регистре R2+1, выполняется операция заполнения, а затем происходит успешное завершение. Когда операция заканчивается вследствие успешного завершения, устанавливается код 0 условия, а результирующее значение R2+1 равно нулю. Когда операция заканчивается вследствие частичного завершения, устанавливается код 3 условия, а результирующее значение R2+1 не равно нулю. Когда длина второго операнда изначально равна нулю, ко второму операнду не осуществляется доступ, общие регистры R2 и R2+1 не изменяются, и устанавливается код 0 условия. В случае вычисления профиля промежуточного сообщения не осуществляется доступ к блоку параметров. Тем не менее, в случае вычисления профиля последнего сообщения выполняется операция заполнения в случае пустого блока (L=0), а результат сохраняется в блоке параметров. С точки зрения других ЦП и канальных программ обращения к операндам блоков параметров и памяти могут являться обращениями с коллективным доступом, выборка блоков из этих местоположений запоминающего устройства необязательно осуществляется параллельно, и последовательность этих доступов или обращений является неопределенной. Об исключительных ситуациях при доступе может сообщаться для большей части операнда, чем часть, обработанная при разовом выполнении команды; тем не менее, исключительные ситуации при доступе не распознаются для местоположений за пределами длины операнда, а также местоположений далее 4 килобайт за пределами текущего обрабатываемого местоположения.

Запрос KIMD (код 0 функции KIMD)

В блоке параметров хранится 128-разрядное слово состояния. Разряды 0-127 этого поля соответствуют кодам 0-127 функции, соответственно, команды вычисления профиля промежуточного сообщения. Когда разряд равен единице, соответствующая функция установлена; в противном случае функция не установлена. По завершении выполнения функции запроса KIMD устанавливается код 0 условия; код 3 условия неприменим к этой функции.

KIMD-SHA-1 (код 1 функции KIMD)

Для 64-байтовых блоков сообщений в операнде 2 генерируется 20-байтовый профиль промежуточного сообщения с использованием блочного алгоритма SHA-1 представления сообщения в краткой форме и 20-байтового значения сцепления в блоке параметров. Генерированный профиль промежуточного сообщения, также называемый выходным значением сцепления (OCV), сохраняется в поле значений сцепления блока параметров.

KIMD-SHA-256 (код 2 функции KIMD)

Для 64-байтовых блоков сообщений в операнде 2 генерируется 32-байтовый профиль промежуточного сообщения с использованием блочного алгоритма SHA-256 представления сообщения в краткой форме и 32-байтового значения сцепления в блоке параметров. Генерированный профиль промежуточного сообщения, также называемый выходным значением сцепления (OCV), сохраняется в поле значений сцепления блока параметров.

KIMD-SHA-512 (код 3 функции KIMD)

Для 128-байтовых блоков сообщений в операнде 2 генерируется 64-байтовый профиль промежуточного сообщения с использованием блочного алгоритма SHA-512 представления сообщения в краткой форме и 64-байтового значения сцепления в блоке параметров. Генерированный профиль промежуточного сообщения, также называемый выходным значением сцепления (OCV), сохраняется в поле значений сцепления блока параметров.

Запрос KLMD (код 0 функции KLMD)

В блоке параметров хранится 128-разрядное слово состояния. Разряды 0-127 этого поля соответствуют кодам 0-127 функции, соответственно, команды вычисления профиля последнего сообщения. Когда разряд равен единице, соответствующая функция установлена; в противном случае функция не установлена. По завершении выполнения функции запроса KLMD устанавливается код 0 условия; код 3 условия неприменим к этой функции.

KLMD-SHA-1 (код 1 функции KLMD)

Для сообщения (М) в операнде 2 генерируется профиль сообщения с использованием алгоритма SHA-1, а также значения сцепления и информации о длине сообщения в битах в блоке параметров. Если длина сообщения в операнде 2 составляет 64 байта или более, для каждого 64-байтового блока сообщений генерируется профиль промежуточного сообщения с использованием блочного алгоритма SHA-1 представления сообщения в краткой форме и 20-байтового значения сцепления в блоке параметров, а генерированный профиль промежуточного сообщения, также называемый выходным значением сцепления (OCV), сохраняется в поле значений сцепления блока параметров. Эта операция повторяется до тех пор, пока остающееся сообщение не будет иметь длину менее 64 байтов. Если длина сообщения или остающегося сообщения составляет ноль байтов, операция выполняется. Если длина сообщения или остающегося сообщения составляет от 1 байта до 55 байтов включительно, операция выполняется; если длина составляет от 56 байтов до 63 байтов включительно, операция выполняется. Профиль сообщения, также называемый выходным значением сцепления (OCV), сохраняется в поле значений сцепления блока параметров.

KLMD-SHA-256 (код 2 функции KLMD)

Для сообщения (М) в операнде 2 генерируется профиль сообщения с использованием алгоритма SHA-256, а также значения сцепления и информации о длине сообщения в битах в блоке параметров. Если длина сообщения в операнде 2 составляет 64 байта или более, для каждого 64-байтового блока сообщений генерируется профиль промежуточного сообщения с использованием блочного алгоритма SHA-256 представления сообщения в краткой форме и 32-байтового значения сцепления в блоке параметров, а генерированный профиль промежуточного сообщения, также называемый выходным значением сцепления (OCV), сохраняется в поле значений сцепления блока параметров. Эта операция повторяется до тех пор, пока остающееся сообщение не будет иметь длину менее 64 байтов. Если длина сообщения или остающегося сообщения составляет ноль байтов, операция выполняется. Если длина сообщения или остающегося сообщения составляет от 1 байта до 55 байтов включительно, операция выполняется; если длина составляет от 56 байтов до 63 байтов включительно, операция выполняется. Профиль сообщения, также называемый выходным значением сцепления (OCV), сохраняется в поле значений сцепления блока параметров.

KLMD-SHA-512 (код 3 функции KLMD)

Для сообщения (M) в операнде 2 генерируется профиль сообщения с использованием алгоритма SHA-512, а также значения сцепления и информации о длине сообщения в битах в блоке параметров. Если длина сообщения в операнде 2 составляет 128 байтов или более, для каждого 128-байтового блока сообщений генерируется профиль промежуточного сообщения с использованием блочного алгоритма SHA-512 представления сообщения в краткой форме и 64-байтового значения сцепления в блоке параметров, а генерированный профиль промежуточного сообщения, также называемый выходным значением сцепления (OCV), сохраняется в поле значений сцепления блока параметров. Операция повторяется до тех пор, пока остающееся сообщение не будет иметь длину менее 128 байтов. Если длина сообщения или остающегося сообщения составляет ноль байтов, операция выполняется. Если длина сообщения или остающегося сообщения составляет от 1 байта до 111 байтов включительно, операция выполняется; если длина составляет от 112 байтов до 127 байтов включительно, операция выполняется. Профиль сообщения, также называемый выходным значением сцепления (OCV), сохраняется в поле значений сцепления блока параметров.

Команда вычисления кода аутентификации сообщения (КМАС)