Изобретение относится к электронике и может быть использовано в интегральных схемах (ИС) цифро-аналоговых преобразователей (ЦАП).

Цель изобретения - улучшение интегральной нелинейности (INL) и дифференциальной нелинейности (DNL) ИС ЦАП использованием калибровки.

Известны, например, схемы ЦАП с калибровкой по патентам США US 5451946, US 7468686 B2, US 8089380 B2.

Основой этих схем являются различные схемы и способы реализации компенсации или калибровки ошибок ЦАП для улучшения их точностных параметров, таких как интегральная и дифференциальная нелинейность.

В патенте США US 5451946 (М. кл. H03M 1/06, пр. 28.01.1993 г., опубл. 19.09.1995 г.) предлагается ЦАП с калибровкой, включающий ЦАП старших разрядов (грубый) и младших разрядов (точный), аналоговый сумматор напряжений двух ЦАП, 16-разрядный АЦП, формирующий цифровой код, соответствующий выходному напряжению ЦАП, цифровой контроллер, рассчитывающий коды ошибок ЦАП по цифровым кодам АЦП, и блок хранения кодов ошибок, управляющий ЦАП младших разрядов. В этой схеме цифровой контроллер по выходному напряжению ЦАП, оцифрованному АЦП, вычисляет ошибки ЦАП и формирует таблицу входных кодов ЦАП младших разрядов, устраняющих вычисленные ошибки ЦАП. Основным недостатком такого ЦАП является его сложность, поскольку требуются прецизионный АЦП с разрядностью и точностью лучше, чем разрядность и точность, требуемые для ЦАП.

Часто для улучшения точностных параметров и быстродействия в ЦАП используется сегментирование K-старших разрядов, заключающееся в замене обычно используемых K-двоично-взвешенных старших разрядов на 2K-1 одинаковых сегментов, управляемых термометрическим кодом. В ЦАП с сегментированием K-старших разрядов требования к допустимой ошибке согласования сегментов уменьшаются в K0,5 раз, однако и этого недостаточно для реализации высокоразрядных (16-18 бит) ЦАП.

В ЦАП по патенту США US 7468686 B2 (М. кл. H03M 1/10, пр. 06.02.2007 г., опубл. 23.12.2008 г.) для улучшения точностных параметров используется калибровка, устраняющая ошибки согласования сегментов в сегментированном ЦАП. Рассматривается известный сегментированный K-разрядный ЦАП, включающий 2K-1 одинаковых сегментов, состоящих из резистора и ключа. Один из выводов резисторов всех сегментов объединен и образует выход ЦАП, а второй подключен к ключу, коммутирующему резисторы сегментов к источнику опорного напряжения (Vref), или земле (Gnd) в соответствии с входным цифровым кодом. Ошибки согласования суммы сопротивлений резистора и ключа для разных сегментов приводят к ошибкам напряжения на выходе ЦАП, ухудшающим INL и DNL. Отметим, что в описанном ЦАП к ошибкам линейности приведет и зависимость сопротивления ключа от потенциала, к которому коммутируется сегмент (Vref или Gnd). В предложенном ЦАП калибровка реализуется двумя 8 бит ЦАПами калибровки, управляемыми цифровыми кодами, хранящимися в программируемой памяти ROM (Read Only Memory). Первый ЦАП калибровки подключен к резистору первого сегмента, а второй - к резистору последнего сегмента. ЦАПы калибровки изменяют сопротивления первого и последнего сегментов, так чтобы согласовать суммарное сопротивление всех сегментов, подключенных к земле с суммарным сопротивлением всех сегментов, подключенных к Vref, при заданном значении входного кода ЦАП.

Процедура калибровки включает

- определение ошибок ЦАП, например ошибок линейности, при каждом значении входного кода;

- генерацию и запись (программирование) в ROM цифровых кодов калибровки, компенсирующих ошибки линейности, для каждого значении входного кода.

При работе ЦАП из ROM на входы ЦАПов калибровки подают цифровые коды компенсации ошибки линейности, соответствующие текущим значениям входного кода.

Основным недостатком предложенных схемы и способа калибровки ЦАП является необходимость предварительного измерения ошибок линейности ЦАП внешним измерителем, а также генерацию и запись в ROM кодов калибровки. Процедура измерения и записи в ROM кодов проводится изготовителем ЦАП, имеющим измеритель соответствующей точности, однократно для фиксированных условий измерения. При этом ошибки ЦАП, возникающие при последующей эксплуатации вследствие временного или температурного дрейфов сопротивлений резисторов и (или) ключей, а также зависимости сопротивлений ключей от напряжения питания или Vref, уже не могут быть устранены.

В патенте США «Current compensation for digital-to-analog converter» US 7564385 B2 (M. кл. H03M 1/06, пр. 18.10.2007 г., опубл. 21.07.2009 г.) для устранения нелинейности, вызванной кодозависимым током, протекающим через сегментированный резистивный делитель ЦАП, предложено использовать компенсирующий токовый ЦАП. Компенсирующий ЦАП для каждого значения входного кода потребляет от источника Vref ток, дополняющий ток, протекающий через сегментированный резистивный делитель, до его максимального значения, и тем самым обеспечивает постоянство суммарного тока от источника Vref и устраняет описанную составляющую нелинейности. Поскольку величина тока, протекающего через сегментированный резистивный делитель ЦАП, детерминирована сопротивлением резисторов, опорным напряжением и входным кодом, величина требуемого тока компенсации также детерминирована для каждого входного кода и может быть задана при проектировании ЦАП. Отметим, что компенсирующий токовый ЦАП позволяет устранить или уменьшить любые детерминированные конструкцией и известные на этапе проектирования погрешности сегментированного ЦАП, например нелинейность, вызванную зависимостью сопротивления резисторов от напряжения. Недостатком предложенного решения является невозможность устранения погрешностей ЦАП, вызванных случайными отклонениями сопротивлений резисторов при изготовлении (далее будем называть данный вид погрешностей общепринятым в технической литературе термином «mismatch»).

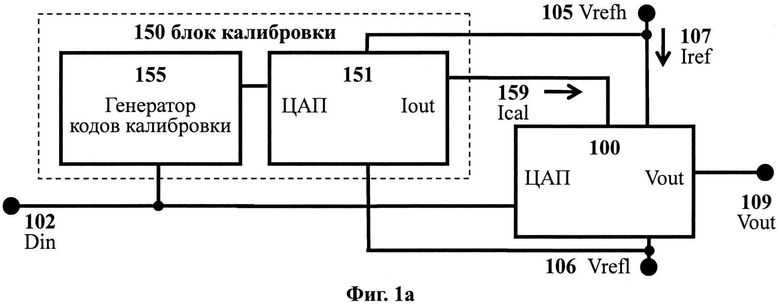

Наиболее близкой к заявляемой является схема ЦАП по патенту США «Voltage mode DAC with calibration circuit using current mode DAC and ROM lookup» US 8089380 B2 (M. кл. H03M 1/10, пр. 22.10.2009 г., опубл. 03.01.2012 г.), представленная на Фиг.1а, 1б.

Схема включает ЦАП с выходом по напряжению 100 и блок калибровки 150, подключенные к входам опорного напряжения высокого Vrefh 105 и низкого Vrefl 106 уровней. Блок калибровки содержит ЦАП с токовым выходом 151, управляемый генератором кодов калибровки 155. Входной код Din 102 поступает на входы ЦАП 100 и генератора кодов калибровки 155. ЦАП калибровки 151 формирует ток калибровки Ical 159, подаваемый на ЦАП 100.

Предложена часто используемая схема ЦАП с выходом по напряжению 100 на основе коммутируемого резистивного делителя, включающая сегментированный K-разрядный ЦАП1 110 (Фиг.1б) из 2K-1 одинаковых сегментов и N-K-разрядный ЦАП0 120 на основе R2R резистивного делителя. Сегменты ЦАП1 состоят из резистора 111 и ключа 113. Один из выводов резисторов всех сегментов объединен и образует выход ЦАП 109, второй подключен к ключу 113, коммутирующему резисторы сегментов к высокому (Vrefh) 105 или низкому (Vrefl) 106 входам опорного напряжения в соответствии с входным кодом ЦАП Din 102. Двоично-взвешенные разряды R2R ЦАП0 образованы резисторами 121 и 122 с сопротивлениями 2R и R соответственно и ключами 123. Выходы ЦАП0 и ЦАП1 объединены и образуют выход ЦАП 109, на котором формируется напряжение, пропорциональное величине Din. Как уже отмечалось, ошибки согласования суммы сопротивлений резистора и ключа в разных сегментах приводят к ошибкам напряжения на выходе ЦАП, ухудшающим INL и DNL. Для компенсации ошибок согласования сопротивлений сегментов предложен токовый ЦАП калибровки 151, подающий на ЦАП 100 ток калибровки Ical 159, причем ток Ical может подаваться как на объединенный выход ЦАП0 и ЦАП1, так и во внутренние узлы ЦАП0 между резисторами цепи R. Ток калибровки Ical пропорционален коду, задаваемому генератором кодов калибровки 155 для каждого значения кода K-старших разрядов 103 входного кода ЦАП. Ток калибровки формируется источниками тока ЦАПа калибровки 151 от источников питания Vdd 152 и Vss 153, которые должны иметь потенциалы выше Vrefh и ниже Vrefl соответственно для обеспечения постоянного тока калибровки при изменении потенциала на Vout в диапазоне от Vrefh до Vrefl. Отметим, что для корректной калибровки масштаб тока калибровки должен быть строго согласован с масштабом тока опорного источника, протекающего через резистивный делитель ЦАП, во всех требуемых условиях эксплуатации: в диапазоне рабочих напряжений питания и опорного источника, а также в диапазоне температур. Это достигается конструкцией ЦАПа калибровки, задающего масштаб ток калибровки в виде фиксированной доли от величины (Vrefh-Vrefl)/2R, где 2R - сопротивление сегмента ЦАП1.

Процедура калибровки в предлагаемом ЦАП аналогична уже описанной калибровке ЦАП по патенту США US 7468686 B2 и включает:

- определение ошибок ЦАП, например ошибок линейности, при каждом значении входного кода;

- генерацию и запись (программирование) в ROM цифровых кодов калибровки, компенсирующих ошибки линейности, для каждого значении входного кода.

Соответственно аналогичны и недостатки такой калибровки, а именно необходимость предварительного измерения ошибок линейности ЦАП внешним измерителем, а также генерацию и запись в ROM кодов калибровки. Процедура измерения и записи в ROM кодов также проводится изготовителем ЦАП, имеющим измеритель соответствующей точности, однократно для фиксированных условий измерения. При этом ошибки ЦАП, возникающие при последующей эксплуатации вследствие временного или температурного дрейфов сопротивлений резисторов и (или) ключей, а также зависимости сопротивлений ключей от напряжения питания или Vref уже не могут быть устранены.

Целью изобретения является улучшение INL и DNL ИС ЦАП использованием автоматической калибровки (далее автокалибровки).

Поставленная цель достигается тем, что в сегментированном N-разрядном ЦАП, включающем K-разрядный ЦАП1 старших разрядов, состоящий из 2K-1 одинаковых сегментов, и N-K-разрядный ЦАП0 младших разрядов, подключенные к общему источнику опорного напряжения Vref и имеющие общий выход, образующий выход ЦАП, блок калибровки, содержащий ЦАП2 источника тока калибровки, подключенного к выходу ЦАП, блок калибровки определяет коды ЦАП2, дополняющие ток каждого сегмента ЦАП1 до тока опорного сегмента в стадии калибровки, а при работе подает на ЦАП2 коды компенсации ошибок ЦАП1, вычисленные для каждого значения кода старших разрядов по кодам ЦАП2, определенным при калибровке.

В частном случае исполнения поставленная цель достигается тем, что в сегментированном N-разрядном ЦАП, включающем K-разрядный ЦАП1 старших разрядов, состоящий из 2K-1 одинаковых сегментов, и N-K-разрядный ЦАП0 младших разрядов, подключенные к общему источнику опорного напряжения Vref и имеющие общий выход, образующий выход ЦАП, блок калибровки, содержащий ЦАП2 источника тока калибровки, подключенного к выходу ЦАП, сегмент ЦАП1 включает резистор 2R, соединенный с выходом и ключом, коммутирующим его к источнику Vref или земле, ЦАП0 включает R-2R резистивный делитель и ключи, коммутирующие резисторы 2R к Vref или земле, опорный сегмент образован делителем из резистора 2R, подключенного к Vref и подключенного к земле резистора с сопротивлением, большим 2R/(2K-1), а блок калибровки включает компаратор напряжения (КН) выхода ЦАП и средней точки делителя опорного сегмента и в стадии калибровки поочередно подключает один из сегментов ЦАП1 к Vref.

В другом частном случае исполнения поставленная цель достигается тем, что в сегментированном N-разрядном ЦАП, включающем K-разрядный ЦАП1 старших разрядов, состоящий из 2K-1 одинаковых сегментов, и N-K-разрядный ЦАП0 младших разрядов, подключенные к общему источнику опорного напряжения Vref и имеющие общий выход, образующий выход ЦАП, блок калибровки, содержащий ЦАП2 источника тока калибровки, подключенного к выходу ЦАП, сегмент ЦАП1 включает источник тока и ключ, коммутирующий его на выход или землю, ЦАП0 включает N-K двоично-взвешенных источников тока и ключи, коммутирующие выходы источников тока на выход или землю, опорный сегмент образован источником тока, большего тока сегмента ЦАП1, а блок калибровки включает компаратор напряжения (КН) выхода ЦАП и выхода опорного сегмента и в стадии калибровки поочередно подключает один из сегментов ЦАП1 к выходу.

Поставленная цель достигается также тем, что в способе калибровки сегментированного N-разрядного ЦАП, включающем калибровку ошибок сегментов K-разрядного ЦАП1, в стадии калибровки поочередно включают каждый из 2K-1 сегментов ЦАП1, определяют коды ЦАП2, дополняющие ток каждого сегмента ЦАП1 до тока опорного сегмента, и вычисляют коды ЦАП2, соответствующие току компенсации ошибки ЦАП1 для каждого значения K-разрядного кода, причем коды ЦАП2, соответствующие токам компенсации ошибок ЦАП1, вычисляют суммированием кодов компенсации ошибок сегментов ЦАП1, определенных по кодам, дополняющим ток каждого сегмента до тока опорного сегмента, и кодов компенсации погрешностей калибровки.

В частном случае поставленная цель достигается тем, что в способе калибровки сегментированного N-разрядного ЦАП, включающем калибровку ошибок сегментов K-разрядного ЦАП1, коды компенсации погрешностей калибровки включают коды компенсации систематических погрешностей калибровки от воздействия факторов, отсутствующих в стадии калибровки.

В другом частном случае поставленная цель достигается тем, что в способе калибровки сегментированного N-разрядного ЦАП, включающем калибровку ошибок сегментов K-разрядного ЦАП1, коды компенсации погрешностей калибровки включают также коды компенсации случайных погрешностей калибровки, возникших в процессе калибровки.

Сущность изобретения поясняется чертежами:

На Фиг.1 представлены блок схема (а) и схема (б) ЦАП с калибровкой по прототипу.

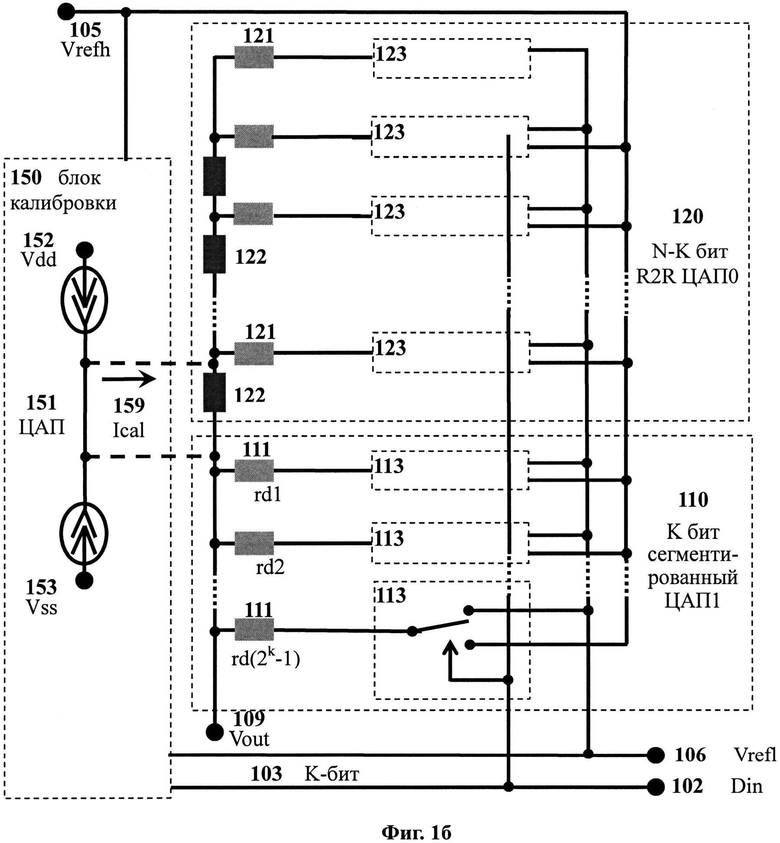

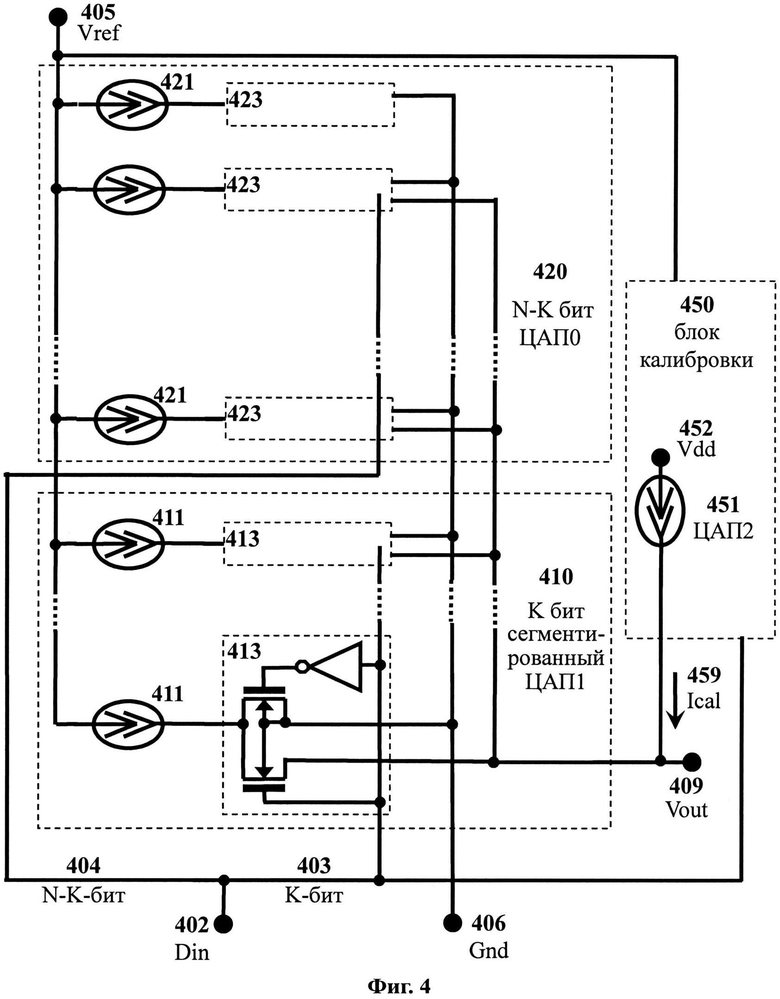

На Фиг.2 представлена блок схема заявляемого сегментированного ЦАП с калибровкой по пп.1, 2, 3, 4 Формулы.

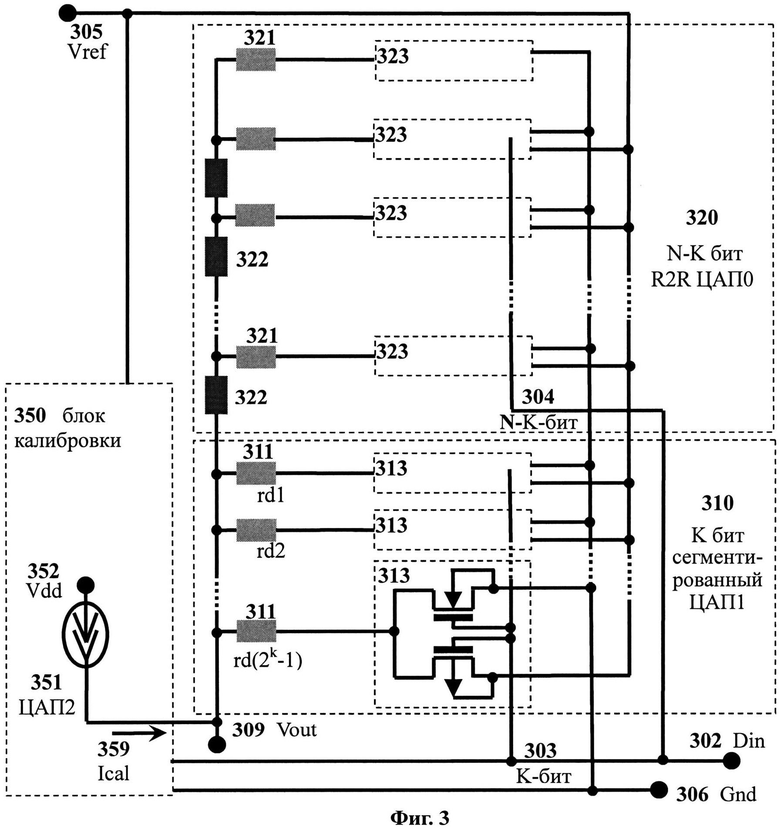

На Фиг.3 представлена схема заявляемого ЦАП с калибровкой на основе сегментированного резистивного делителя по пп.1, 2, 4 Формулы.

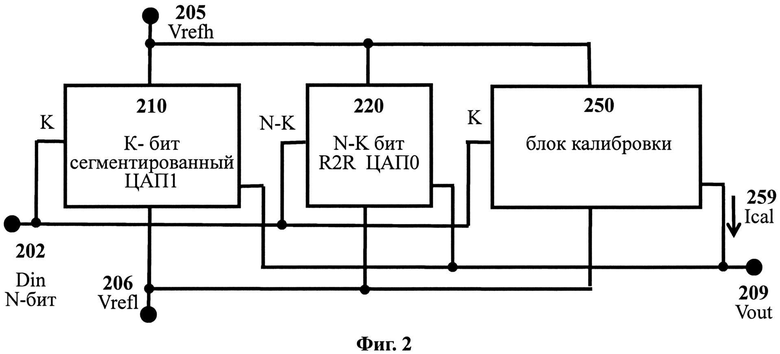

На Фиг.4 представлена схема заявляемого сегментированного ЦАП с калибровкой на основе источников тока по пп.1, 3, 4 Формулы.

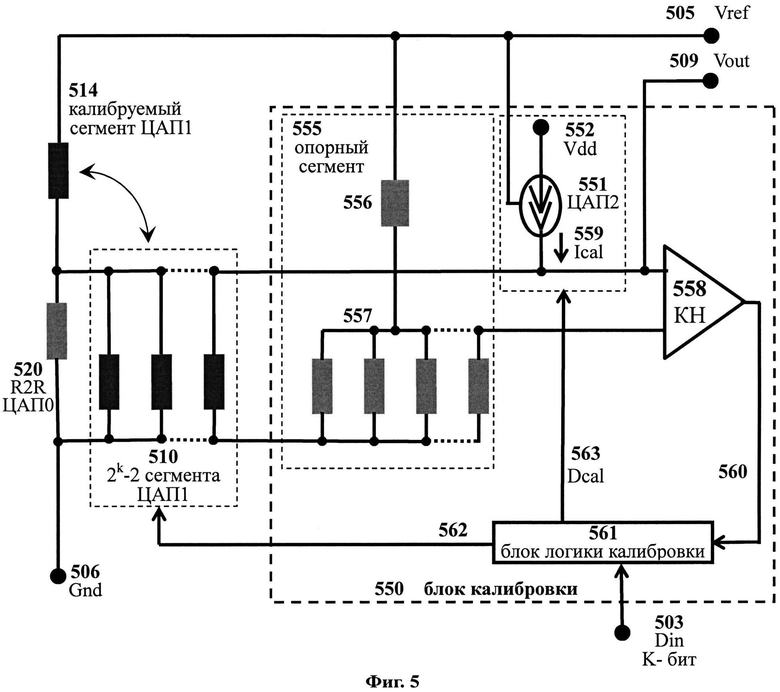

На Фиг.5 представлена схема организации автокалибровки в заявляемом ЦАП на основе сегментированного резистивного делителя по пп.1, 2, 4 Формулы.

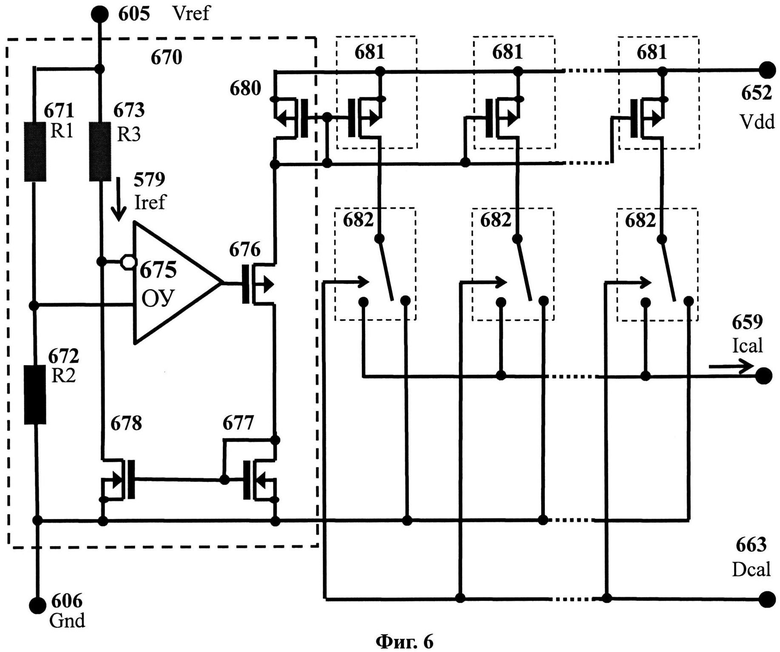

На Фиг.6 представлен ЦАП калибровки для заявляемого ЦАП.

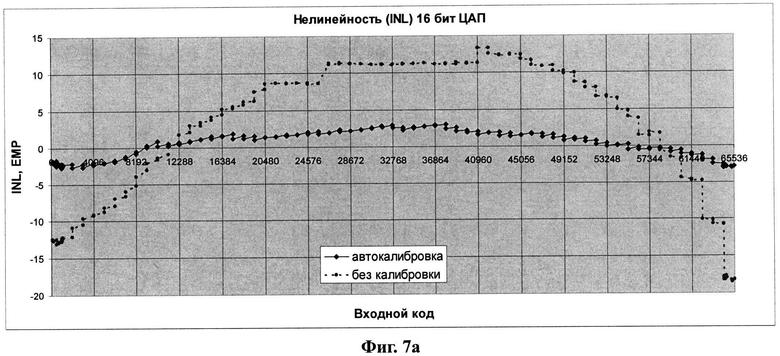

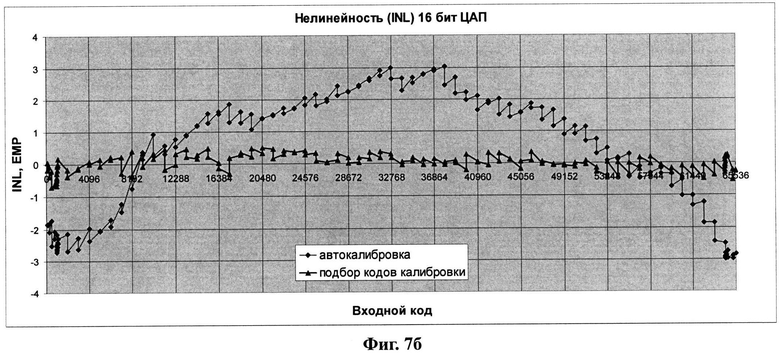

На Фиг.7 представлены измеренные INL тестовых 16 бит ЦАП с сегментированным резистивным делителем по пп.2, 4 Формулы до и после калибровки.

Рассмотрим устройство и работу заявляемого ЦАП с калибровкой.

Блок схема заявляемого N-разрядного ЦАП представлена на Фиг.2. ЦАП включает сегментированный ЦАП1 K-старших разрядов 210 и R2R ЦАП0 N-K-младших разрядов 220 с общим выходом Vout 209, а также блок калибровки 250, задающий на выход ЦАП 209 ток калибровки Ical 259, формируемый для каждого значения K-разрядного кода старших разрядов. ЦАП0, ЦАП1 и блок калибровки используют общий источник опорного напряжения, подключаемый к входам опорного напряжения высокого уровня Vrefh 205 и низкого уровня Vrefl 206. К-старших бит входного N-разрядного кода ЦАП Din 202 поступают на цифровые входы ЦАП1 и блока калибровки, а N-K-младших бит поступают на цифровые входы ЦАП0.

Более подробная схема заявляемого по пп.1, 2, 4 Формулы N-разрядного ЦАП представлена на Фиг.3. Отметим, что в частном случае исполнения по п.2 Формулы ЦАП выполнен на основе резистивного делителя, а в качестве низкого уровня опорного напряжения принята земля. Схема ЦАП включает сегментированный ЦАП1 K-старших разрядов 310 и R2R ЦАП0 N-K-младших разрядов 320 с общим выходом Vout 309, а также блок калибровки 350, задающий на выход ЦАП 309 ток калибровки Ical 359, формируемый для каждого значения K-разрядного кода старших разрядов. ЦАП0, ЦАП1 и блок калибровки используют общий источник опорного напряжения, подключаемый между входом опорного напряжения Vref 305 и выводом земли Gnd 306. К старших бит 303 входного N-разрядного кода ЦАП Din 302 поступают на цифровые входы ЦАП1 и блока калибровки, а N-K-младших бит 304 поступают на цифровые входы ЦАП0. Сегментированный ЦАП1 включает 2K-1 одинаковых сегментов, состоящих из резистора с сопротивлением 2R 311 и КМОП ключа 313. Один из выводов резисторов 311 всех сегментов объединен и образует выход ЦАП1, а второй подключен к ключу 313, коммутирующему сегмент к входу Vref 305 или земле Gnd 306 в соответствии с значением K-старших бит 303 входного кода. ЦАП0 320 включает N-K-двоично-взвешенных разрядов R2R резистивного делителя, состоящего из последовательно включенных резисторов с сопротивлением R 322 и резисторов с сопротивлением 2R 321, один из выводов которых подключен к узлам цепи резисторов R, а второй подключен к ключу 323, коммутирующему резистор 321 к входу Vref 305 или земле Gnd 306 в соответствии с значением N-K младших бит 304 входного кода. На выходе ЦАП 309 формируется напряжение Vout, пропорциональное входному коду Din 302. Блок калибровки 350 включает ЦАП2 351 с токовым выходом, являющийся источником тока калибровки Ical 359, задаваемого на выход ЦАП 309 от источника питания Vcc 352. Масштаб тока калибровки Ical задается источником опорного напряжения Vref.

На Фиг.4 представлен N-разрядный ЦАП, заявляемый по пп.1, 3, 4 Формулы. В частном случае исполнения по п.3 Формулы ЦАП выполнен на основе источников тока, а в качестве низкого уровня опорного напряжения также принята земля. Этот ЦАП также включает сегментированный ЦАП1 K-старших разрядов 410 и ЦАП0 N-K-младших разрядов 420 с общим выходом Vout 409, а также блок калибровки 450, задающий на выход ЦАП ток калибровки Ical 459, формируемый для каждого значения K-разрядного кода старших разрядов 403. ЦАП0, ЦАП1 и блок калибровки используют общий источник опорного напряжения, подключаемый к между входом опорного напряжения Vref 405 и выводом земли Gnd 406. К старших бит 403 входного N-разрядного кода ЦАП Din 402 поступают на цифровые входы ЦАП1 и блока калибровки, а N-K-младших бит 404 поступают на цифровые входы ЦАП0. Сегментированный ЦАП1 включает 2K-1 одинаковых сегментов, состоящих из источников тока 411 и n-канальных МОП ключей 413. Один из выводов источников тока 411 всех сегментов объединен и подключен к входу опорного напряжения Vref 405, а второй подключен к ключу 413, коммутирующему сегмент к выходу ЦАП 409 или земле Gnd 406 в соответствии с значением K-старших бит 403 входного кода. ЦАП0 420 включает N-K-двоично-взвешенных разрядов, состоящих из последовательно включенных двоично-взвешенных источников тока 421 и ключей 423, коммутирующих ток источников на выход ЦАП 409 или на землю Gnd 406 в соответствии с значением N-K младших бит 404 входного кода. На выходе ЦАП 409 формируется напряжение Vout, пропорциональное входному коду Din 402. Блок калибровки 450 включает ЦАП2 451 с токовым выходом, являющийся источником тока калибровки Ical 459, задаваемого на выход ЦАП 409 от источника питания Vcc 452. Масштаб тока калибровки Ical задается источником опорного напряжения Vref.

Как уже отмечалось ранее, и резисторы делителя в резистивном ЦАП, и источники токов в ЦАП на источниках тока имеют случайные ошибки (mismatch), вызванные их рассогласованием при изготовлении. Очевидно, что эти ошибки, вследствие их случайного характера, не могут быть заранее спрогнозированы, и единственный способ устранения их негативного влияния на INL, DNL - измерение конкретного образца ЦАП для определения ошибок линейности при каждом коде старших разрядов, определение кодов калибровки Deal, формирующих ток калибровки Ical, устраняющий ошибки для каждого значения кода старших разрядов и запись кодов Dcal в память данного образца ЦАП. При работе ЦАП блок калибровки для текущего значения входного кода ЦАП задает на вход ЦАПа калибровки соответствующий код калибровки Deal и ЦАП калибровки задает на выход ЦАП ток калибровки Ical, уменьшающий или устраняющий ошибку выходного напряжения ЦАП.

В заявляемом ЦАП процесс калибровки может быть проведен с использованием внутренних ресурсов ЦАП без использования внешнего измерителя. Это позволяет проводить (повторять) калибровку пользователем в любое время, например при изменений условий эксплуатации (температуры, напряжений питания и опоры), или после длительной работы ЦАП, приведшей к увеличению ошибок из-за старения.

Рассмотрим схему организации калибровки (автокалибровки), представленную на Фиг.5 на примере ЦАП и способа его калибровки, заявляемых по пп.1, 2, 4 Формулы.

Блок калибровки 550 содержит опорный сегмент 555, компаратор напряжения (КН) 558, блок логики калибровки 561, управляющий процессом калибровки, рассчитывающий и хранящий коды калибровки Dcal 563 для каждого значения K старших бит входного кода ЦАП Din 503 и ЦАП2 источника тока калибровки 551, формирующий ток калибровки Ical 559, пропорциональный коду калибровки Dcal. Опорный сегмент 555 представляет собой резистивный делитель из подключенного к Vref 505 резистора 556 с сопротивлением 2R, эквивалентным сопротивлению одного сегмента ЦАП1, и подключенного к земле резистора 557 с сопротивлением, большим 2R/(2K-1). Средняя точка опорного сегмента с напряжением, большим Vref/2K , подключена к опорному входу КН 558. Второй вход КН подключен к выходу ЦАП Vout 509, объединяющему выходы ЦАП0 520, ЦАП1 (общая точка всех сегментов 510, 514) и ЦАП2 551.

На Фиг.6 приведен вариант исполнения ЦАП2 калибровки, включающий блок 670 формирования опорного тока Iref 579 и ряд двоично-взвешенных источников тока 681, коммутируемых на выход ЦАП2 двоично-взвешенными токовыми ключами 682. Как уже упоминалось, для корректной работы калибровки при изменении условий эксплуатации выходной ток калибровки Ical 659 должен отслеживать изменения тока, протекающего через резистивный делитель ЦАП. Такую корреляцию обеспечивает блок 670, подключенный к входу источника Vref 605 и формирующий опорный ток Iref, пропорциональный максимальному току резистивного делителя ЦАП. Блок 670 включает операционный усилитель (ОУ) 675, выход которого подключен к затвору p-МОП транзистора 676, неинвертирующий вход которого подключен к средней точке опорного делителя из резисторов R1 671 и R2 672, эквивалентных резисторам сегментов ЦАП1, а инвертирующий вход к резистору R3 673, равному R1, и выходу токового зеркала на n-МОП транзисторах 677, 678, транслирующего ток транзистора 676 в резистор R3. Ток исток-сток транзистора 676, пропорциональный Iref, транслируется на выход ЦАП токовыми зеркалами на p-канальных МОП транзисторах 680 и 681 пропорционально коду Dcal. В отличие от ЦАП калибровки прототипа ЦАП, предложенный в рассмотренном частном случае, однополярный и обеспечивает только ток, протекающий от источника питания Vdd на выход калибруемого ЦАП с напряжением Vout, которое должно быть меньше Vdd на величину падения напряжения на источниках тока 681 и ключах 682 ЦАПа калибровки. Отметим, что однополярный ток калибровки при прочих равных условиях обеспечивает более точную калибровку, чем при использовании биполярного тока калибровки, так как отсутствует ошибка согласования токов калибровки разной полярности, неизбежная в биполярном ЦАП калибровки. Кроме того, для ЦАП с однополярным питанием Vdd относительно земли невозможно реализовать линейный источник тока на землю от близкого к земле выходного напряжения ЦАП Vout. Использование однополярного тока калибровки только от Vdd приводит к необходимости повышения напряжения выхода опорного сегмента (от его идеального значения Vref/2K) на величину, большую суммы максимальной ошибки калибруемого сегмента, ошибки опорного сегмента и максимального смещения нуля КН 558. Повышенное напряжение выхода опорного сегмента приводит к увеличению величин всех токов калибровки, однако это увеличение токов аддитивно и приводит к увеличению смещения нуля ЦАП, которое обычно некритично.

Процесс автокалибровки ЦАП включает:

- поочередное подключение блоком логики калибровки одного из сегментов ЦАП1 (i-го калибруемого сегмента) 514 (Фиг.5) к Vref;

- определение последовательным приближением кода ЦАП2 Dcali, при котором выходной ток ЦАП2 Icali дополняет ток, протекающий через i-ый сегмент, подключенный к Vref, до величины тока опорного сегмента. Критерием этого дополнения является повышение напряжения на выходе ЦАП Vout до уровня, превышающего напряжение средней точки опорного сегмента, фиксируемое КН 558;

- расчет по кодам Dcali кодов калибровки Dcals, соответствующих токам калибровки, компенсирующим суммарную ошибку всех выбранных (подключенных к Vref) сегментов, для каждого значения K-старших бит входного кода ЦАП.

- расчет для каждого значения K-старших бит входного кода ЦАП итоговых кодов калибровки Dcal, включающих сумму кодов Dcals и кодов Dcal0, соответствующих токам калибровки, компенсирующим погрешности линейности, от воздействия факторов, отсутствующих в стадии калибровки при определении кодов Dcals.

При работе откалиброванного ЦАП на вход ЦАП2 подается код калибровки Dcal, соответствующий текущему значению K-старших бит входного кода. Выходной ток ЦАП2 Ical, втекающий в выход ЦАП Vout, корректирует выходное напряжение ЦАП, компенсируя его ошибку для текущего входного кода ЦАП.

Расчет по кодам Dcali кода калибровки Dcals, компенсирующего суммарную ошибку всех сегментов, выбранных для заданного значения K-старших бит входного кода, может быть проведен, например, суммированием по всем выбранным сегментам разности кода Dcali и минимального значения Dcali_min из кодов Dcali всех сегментов.

Суть предложенной автокалибровки заключается в сравнении каждого отдельного сегмента ЦАП1 старших разрядов с опорным сегментом и определение ошибки этого сегмента относительно опорного в фиксированных условиях при одинаковых токах и напряжениях на выбранном сегменте.

Очевидно, что такая автокалибровка не может устранить ошибки линейности ЦАП, вызванные отстутствующими в процессе калибровки факторами, например, связанными с изменяющимся количеством сегментов, подключенных к Vref и земле, при разных входных кодах ЦАП.

К таким ошибкам относятся следующие:

- ошибки линейности, связанные с кодозависимым током через резистивный делитель ЦАП, описанные ранее при рассмотрении калибровки по патенту US 7564385 B2;

- ошибки линейности, связанные с нелинейностью вольт-амперных характеристик (ВАХ) резисторов, или источников тока, например, из-за зависимости сопротивления резисторов от напряжения на резисторе, или подложке;

- ошибки линейности, связанные с различием сопротивлений ключей, коммутирующих сегменты к источнику Vref или земле.

В калиброванном ЦАП также могут присутствовать ошибки линейности, связанные с нелинейностью ВАХ транзисторных источников тока ЦАПа калибровки.

Четыре вышеуказанные ошибки линейности носят в первом приближении систематический характер, то есть большая часть этих ошибок определяется конструктивными параметрами ЦАП и может быть рассчитана на этапе его разработки. Для определенности, эти не устраняемые автокалибровкой сегментов ошибки линейности назовем систематическими погрешностями калибровки.

Поскольку большая часть систематических погрешностей калибровки поддается определению на этапе разработки ЦАП, коды компенсации этих систематических погрешностей калибровки Dcal0 могут быть рассчитаны и сохранены в блоке логики на этапе разработки. Суммирование кодов компенсации ошибок сегментов Dcals, определенных в процессе автокалибровки, с определенными при разработке ЦАП кодами компенсации систематических погрешностей калибровки Dcal0 позволяет получить финальные коды калибровки Dcal, наиболее полно компенсирующие систематические и случайные ошибки ЦАП. Такая калибровка предусмотрена способом заявляемым по пп.4 и 5 Формулы.

В процессе калибровки также имеют место случайные погрешности калибровки, вызванные случайными ошибками КН, помехами и ошибками установления напряжения Vout при калибровке. Очевидно, что случайные погрешности калибровки не могут быть устранены автокалибровкой. Однако, при необходимости достижения минимальной ошибки конкретных образцов ЦАП, измерением этих образцов могут быть определены и записаны в блок логики калибровки дополняющие коды калибровки этих случайных погрешностей Dcalm. В этом случае при работе ЦАП блок логики калибровки определяет финальные коды калибровки Dcal в виде суммы Dcals, Dcal0 и Dcalm. Такая калибровка предусмотрена способом, заявляемым по п.6 Формулы.

Отметим, что рассмотренная схема организации автокалибровки, приведенная для ЦАП с резистивным делителем, пригодна и для ЦАП на основе источников тока по п.3 Формулы с заменой резисторов на соответствующие источники тока. При этом следует учесть, что для ЦАП на источниках тока часто используют внешний резистор нагрузки выхода, изменением номинала которого можно управлять величиной выходного напряжения ЦАП. В этом случае и резистор опорного сегмента 557 (Фиг.5) должен быть внешним и согласованным с резистором нагрузки ЦАП.

Проверка реализуемости и эффективности предложенных схемы ЦАП и способа его калибровки проведена при разработке 16-разрядного КМОП ЦАП с поликремниевым резистивным делителем в соответствии с п.2 Формулы. Использован 6-разрядный сегментированный ЦАП1 и 10-разрядный R2R ЦАП2 (см. Фиг.3). Резисторы 2R имеют типовое сопротивление 1000 кОм, что при типовом опорном напряжении 4.096 В дает максимальный ток через резистивный делитель ЦАП - 64 мкА. 9 бит ЦАП2 (см. Фиг.6) обеспечивает максимальный ток калибровки 0,3 мкА от источника питания Vdd=5B.

Типовая измеренная зависимость INL тестовых образцов ЦАП от входного кода до и после автокалибровки представлена на Фиг.7а. Исходная INL ЦАП без калибровки достигала 20 ЕМР (единиц младшего разряда), a DNL - 9 ЕМР. После автокалибровки INL уменьшилась до 3 ЕМР, a DNL до 0.7 ЕМР. Остаточная после калибровки INL в основном обусловлена ранее рассмотренными систематическими погрешностями калибровки от воздействия факторов, отсутствующих при калибровке ошибок сегментов (нелинейность из-за кодовой зависимости тока резистивного делителя, нелинейность ВАХ резисторов, нелинейность источников тока ЦАПа калибровки). Предполагается рассчитать и записать в блок логики калибровки коды Dcal0 компенсации систематических погрешностей, что позволит уменьшить INL до уровня менее 1.0 ЕМР. На Фиг.7б представлены измеренные зависимости INL тестовых образцов ЦАП от входного кода после автокалибровки и после «ручного» подбора кодов калибровки. Подбор кодов калибровки обеспечил уменьшение INL ЦАП до 0.75 ЕМР, что указывает на низкую погрешность ЦАПа калибровки.

Таким образом, заявляемые ЦАП и способ его калибровки обладают новизной, могут быть реализованы и позволяют существенно улучшить INL, DNL ЦАП даже при высоких исходных ошибках резистивного делителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ И СПОСОБ ЕГО КАЛИБРОВКИ | 2006 |

|

RU2335844C2 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ И СПОСОБ ЕГО КАЛИБРОВКИ | 2013 |

|

RU2520421C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ И СПОСОБ ЕГО КАЛИБРОВКИ | 2010 |

|

RU2442279C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ И СПОСОБ ЕГО КАЛИБРОВКИ | 2006 |

|

RU2341017C2 |

| Преобразователь напряжения в частоту и способ его калибровки | 2020 |

|

RU2755017C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ И СПОСОБ КАЛИБРОВКИ СМЕЩЕНИЯ НУЛЯ | 2013 |

|

RU2520427C1 |

| ИНТЕГРАЛЬНЫЙ N-РАЗРЯДНЫЙ ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ (ЦАП) (ВАРИАНТЫ) | 1995 |

|

RU2113055C1 |

| Прецизионный преобразователь напряжения в частоту | 2022 |

|

RU2819791C1 |

| ДАТЧИК ДАВЛЕНИЯ | 2013 |

|

RU2523754C1 |

| КМОП-усилитель с чоппер-стабилизацией и способ калибровки | 2022 |

|

RU2809617C1 |

Группа изобретений относится к электронике и может быть использована в интегральных схемах (ИС) цифро-аналоговых преобразователей (ЦАП). Техническим результатом является улучшение интегральной нелинейности и дифференциальной нелинейности ИС ЦАП посредством использования автоматической калибровки. Устройство содержит сегментированный N-разрядный ЦАП, включающий K-разрядный ЦАП1 старших разрядов, состоящий из 2K-1 одинаковых сегментов, и N-K-разрядный ЦАП0 младших разрядов, подключенные к общему источнику опорного напряжения Vref и имеющие общий выход, образующий выход ЦАП, блок калибровки, содержащий ЦАП2 источника тока калибровки, подключенный к выходу ЦАП, блок калибровки определяет коды ЦАП2, дополняющие ток каждого сегмента ЦАП1 до тока опорного сегмента в стадии калибровки, а при работе подает на ЦАП2 коды компенсации ошибок ЦАП1, вычисленные для каждого значения кода старших разрядов по кодам ЦАП2, определенным при калибровке. 2 н. и 4 з.п. ф-лы, 9 ил.

1. Сегментированный N-разрядный цифро-аналоговый преобразователь (ЦАП), включающий K-разрядный ЦАП1 старших разрядов, состоящий из 2K-1 одинаковых сегментов, и N-K-разрядный ЦАП0 младших разрядов, подключенные к общему источнику опорного напряжения Vref и имеющие общий выход, образующий выход ЦАП, блок калибровки, содержащий ЦАП2 источника тока калибровки, подключенного к выходу ЦАП, отличающийся тем, что блок калибровки определяет коды ЦАП2, дополняющие ток каждого сегмента ЦАП1 до тока опорного сегмента в стадии калибровки, а при работе подает на ЦАП2 коды компенсации ошибок ЦАП1, вычисленные для каждого значения кода старших разрядов по кодам ЦАП2, определенным при калибровке.

2. Сегментированный N-разрядный ЦАП по п. 1, отличающийся тем, что сегмент ЦАП1 включает резистор 2R, соединенный с выходом и ключом, коммутирующим его к источнику Vref или земле, ЦАП0 включает R-2R резистивный делитель и ключи, коммутирующие резисторы 2R к Vref или земле, опорный сегмент образован делителем из резистора 2R, подключенного к Vref и подключенного к земле резистора с сопротивлением, большим 2R/(2K-1), а блок калибровки включает компаратор напряжения (КН) выхода ЦАП и средней точки делителя опорного сегмента и в стадии калибровки поочередно подключает один из сегментов ЦАП1 к Vref.

3. Сегментированный N-разрядный ЦАП по п. 1, отличающийся тем, что сегмент ЦАП1 включает источник тока и ключ, коммутирующий его на выход или землю, ЦАП0 включает N-K двоично-взвешенных источников тока и ключи, коммутирующие выходы источников тока на выход или землю, опорный сегмент образован источником тока, большего тока сегмента ЦАП1, а блок калибровки включает компаратор напряжения (КН) выхода ЦАП и выхода опорного сегмента и в стадии калибровки поочередно подключает один из сегментов ЦАП1 к выходу.

4. Способ калибровки сегментированного N-разрядного ЦАП по любому из пп. 1, 2, 3, включающий калибровку ошибок сегментов K-разрядного ЦАП1, отличающийся тем, что в стадии калибровки поочередно включают каждый из 2K-1 сегментов ЦАП1, определяют коды ЦАП2, дополняющие ток каждого сегмента ЦАП1 до тока опорного сегмента, и вычисляют коды ЦАП2, соответствующие току компенсации ошибки ЦАП1 для каждого значения K-разрядного кода, причем коды ЦАП2, соответствующие токам компенсации ошибок ЦАП1, вычисляют суммированием кодов компенсации ошибок сегментов ЦАП1, определенных по кодам, дополняющим ток каждого сегмента до тока опорного сегмента, и кодов компенсации погрешностей калибровки.

5. Способ калибровки сегментированного N-разрядного ЦАП по п. 4, отличающийся тем, что коды компенсации погрешностей калибровки включают коды компенсации систематических погрешностей калибровки от воздействия факторов, отсутствующих в стадии калибровки.

6. Способ калибровки сегментированного N-разрядного ЦАП по п. 4 или 5, отличающийся тем, что коды компенсации погрешностей калибровки включают коды компенсации случайных погрешностей калибровки, возникших в процессе калибровки.

| US 8089380 B2, 03.01.2012 | |||

| US 2008186215 A1, 07.08.2008 | |||

| US 2009153380 A1, 18.06.2009 | |||

| СПОСОБ КАЛИБРОВКИ ПЕРЕДАТОЧНОЙ ХАРАКТЕРИСТИКИ ЦИФРОАНАЛОГОВОГО ПРЕОБРАЗОВАТЕЛЯ | 1991 |

|

RU2022464C1 |

| Устройство для контроля погрешности цифро-аналоговых преобразователей | 1980 |

|

SU938389A1 |

Авторы

Даты

2015-11-20—Публикация

2013-08-01—Подача