Изобретение относится к автоматике и интегральной электронике и может быть использовано в системах преобразования цифровой информации в аналоговую.

Цель изобретения - повышение скорости преобразования цифрового кода в аналоговый сигнал, а также расширение диапазона выходного аналогового сигнала вплоть до напряжений питания.

Известен интегральный цифроаналоговый преобразователь (ЦАП) по патенту [1] , включающий цепочку последовательно соединенных резисторов и аналоговых МОП-ключей со схемой управления, коммутирующей выбранный в соответствии со входным кодом отвод резистивной цепочки на выход ЦАП. При этом потенциал с резистивной цепочки на выход ЦАП проходит 7 последовательно соединенных МОП-ключей, что снижает быстродействие ЦАП. Кроме того, большое количество ключей определяет большие размеры кристалла интегральных ЦАП.

Наиболее близким к заявляемому является интегральный ЦАП с двумя уровнями декодирования по патенту [2].

Такой n-разрядный ЦАП (фиг. 1) содержит цепочку 2n последовательно соединенных резисторов, объединенных в M групп по 2n/M резисторов в каждой группе, 2n N-канальных МОП-ключей, объединенных в M групп по 2n/M ключей в каждой группе, (M + 1)-ю группу из (2n/M) N-канальных МОП-ключей и два дешифратора, причем первый вывод первого резистора первой группы и второй вывод 2n/M-го резистора M-й группы соединены с выводами источника опорного напряжения, информационный вход i-го МОП-ключа (где  ) j-й группы (где

) j-й группы (где  ) соединен с первым выводом i-го резистора j-й группы, выходы i-х МОП-ключей всех M групп объединены и подключены к информационному входу i-го МОП-ключа (M + 1)-й группы, управляющие входы всех МОП-ключей j-й группы объединены и подключены к выходам j-го разряда первого дешифратора, входы которого являются входами старших разрядов преобразователя, управляющие входы i-х МОП-ключей (M + 1) группы подключены к выходам i-х разрядов второго дешифратора, входы которого являются входами младших разрядов преобразователя, а выходы всех ключей (M + 1)-й группы объединены и являются аналоговым выходом преобразователя.

) соединен с первым выводом i-го резистора j-й группы, выходы i-х МОП-ключей всех M групп объединены и подключены к информационному входу i-го МОП-ключа (M + 1)-й группы, управляющие входы всех МОП-ключей j-й группы объединены и подключены к выходам j-го разряда первого дешифратора, входы которого являются входами старших разрядов преобразователя, управляющие входы i-х МОП-ключей (M + 1) группы подключены к выходам i-х разрядов второго дешифратора, входы которого являются входами младших разрядов преобразователя, а выходы всех ключей (M + 1)-й группы объединены и являются аналоговым выходом преобразователя.

Известный ЦАП работает следующим образом: Ток от источника опорного напряжения ЦАП, протекающий через резистивную цепочку, формирует сетку (2n) равноотстоящих потенциалов в диапазоне от положительного до отрицательного потенциала источника опорного напряжения, соответствующих (2n) значениям входного n-разрядного кода ЦАП. Дешифраторы в соответствии с n-разрядным входным кодом ЦАП формируют сигналы управления, подаваемые на управляющие входы МОП-ключей, таким образом, что при любом значении входного кода открыты все ключи только одной из M групп, а также открыт только один из i ключей (M + 1)-й группы, при этом выход ЦАПа через открытый ключ (M + 1)-й группы и открытый ключ одной из M групп подключен к первому выводу i-го резистора резистивной цепочки с потенциалом, соответствующим значению входного кода. Следовательно, через некоторое время, определяемое постоянной времени заряда эквивалентной емкости выхода ЦАП через сопротивление 2-х МОП-ключей и сопротивление резистивной цепочки, на выходе ЦАП установится потенциал, соответствующий входному n-разрядному коду ЦАП.

Описанная конструкция ЦАП обеспечивает компактную его реализацию в интегральном виде при выполнении резистивной цепочки в виде группы диффузионных полос в кристалле полупроводника, одновременно являющихся областями истоков МОП-ключей М-групп, однако имеются и существенные недостатки, ограничивающие скорость преобразования цифрового кода в аналоговый сигнал, и диапазон выходного аналогового сигнала.

Действительно, конструктивное исполнение известного ЦАП с диффузионными резисторами предполагает возможность использования в качестве ключей M групп МОП-транзисторов только с каналом одного типа проводимости, соответствующего типу проводимости диффузионных резисторов. При этом напряжение, которое может коммутировать МОП-транзистор с каналом одного типа, должно быть меньше напряжения питания на величину порогового напряжения, повышенного из-за обратного смещения на истоке транзистора относительно подложки, что сужает диапазон выходного аналогового напряжения на 1,5 - 2,5 В при типовом напряжении питания 5 В. Учитывая, что сопротивление канала МОП-транзистора обратно пропорционально разности между напряжением затвор-исток и пороговым напряжением транзистора, очевидно, что чем ближе уровень коммутируемого аналогового сигнала к напряжению питания (т.е. чем меньше разность между напряжением затвор-исток и пороговым напряжением), тем выше сопротивление ключевого МОП-транзистора и тем больше время перезаряда выходной емкости ЦАПа, определяющее его быстродействие.

Кроме того, постоянную времени перезаряда выходной емкости ЦАП увеличивает эквивалентное сопротивление резистивной цепочки, имеющее максимальное значение в ее средней части, т.е. для групп ключей (M/2) и (M/2 + 1), сопротивление которых существенно выше, чем у ключей, например, 1 группы.

Целью настоящего изобретения является повышение быстродействия, а также расширение диапазона выходного аналогового сигнала интегрального ЦАП.

Поставленная цель достигается тем, что в интегральном n-разрядном цифроаналоговом преобразователе (ЦАП), содержащем 2n последовательно соединенных резисторов, объединенных в M групп по 2n/M резисторов в каждой группе, 2n МОП-ключей, объединенных в M групп по 2n/M ключей в каждой группе, (M + 1) группу из 2n/M МОП-ключей и два дешифратора, причем первый вывод первого резистора первой группы и второй вывод 2n/M-го резистора M-й группы соединены с выводами источника опорного напряжения, информационный вход i-го МОП-ключа (где  ) j-й группы (где

) j-й группы (где  ) соединен с первым выводом i-го резистора j-й группы, выходы i-х МОП-ключей всех M групп объединены и подключены к информационному входу i-го МОП-ключа (M + 1)-й группы, управляющие входы всех МОП-ключей j-й группы объединены и подключены к выходам j-го разряда первого дешифратора, входы которого являются входами старших разрядов преобразователя, управляющие входы i-х МОП-ключей (M + 1) группы подключены к выходам i-х разрядов второго дешифратора, входы которого являются входами младших разрядов преобразователя, а выходы всех ключей (M + 1)-й группы объединены и являются аналоговым выходом преобразователя, ключи групп с первой по J1 выполнены из N-канальных МОП-транзисторов, ключи групп с J2 по M выполнены из P-канальных МОП-транзисторов, а ключи групп с (J1 + 1) по (J2 - 1) и (M + 1) группы выполнены из параллельно включенных P- и N-канальных МОП-транзисторов, а их управляющие входы соединены с парафазными выходами соответствующих разрядов дешифраторов, причем J1 может иметь значения от 1 до (J2 - 2) включительно, а J2 может иметь значения от (J1 + 2) до M включительно.

) соединен с первым выводом i-го резистора j-й группы, выходы i-х МОП-ключей всех M групп объединены и подключены к информационному входу i-го МОП-ключа (M + 1)-й группы, управляющие входы всех МОП-ключей j-й группы объединены и подключены к выходам j-го разряда первого дешифратора, входы которого являются входами старших разрядов преобразователя, управляющие входы i-х МОП-ключей (M + 1) группы подключены к выходам i-х разрядов второго дешифратора, входы которого являются входами младших разрядов преобразователя, а выходы всех ключей (M + 1)-й группы объединены и являются аналоговым выходом преобразователя, ключи групп с первой по J1 выполнены из N-канальных МОП-транзисторов, ключи групп с J2 по M выполнены из P-канальных МОП-транзисторов, а ключи групп с (J1 + 1) по (J2 - 1) и (M + 1) группы выполнены из параллельно включенных P- и N-канальных МОП-транзисторов, а их управляющие входы соединены с парафазными выходами соответствующих разрядов дешифраторов, причем J1 может иметь значения от 1 до (J2 - 2) включительно, а J2 может иметь значения от (J1 + 2) до M включительно.

В частном исполнении интегрального ЦАП номер граничной группы J1 соответствует минимальному значению j, при котором выполняется условие Rp(j) < 4Rn(j), а номер граничной группы J2 соответствует максимальному значению j, при котором выполняется условие Rn(j) < 4Rp(i), где Rn(i) и Rp(i) - максимальные сопротивления соответственно открытых N- и P-канальных МОП-транзисторов ключей в группе с номером j.

В другом частном исполнении интегрального ЦАП ключи групп с первой по M/4 выполнены из N-канальных МОП-транзисторов, ключи групп с (3M/4 + 1) по M выполнены из P-канальных МОП-транзисторов, а ключи групп с (M/4 + 1) по (3M/4) и (M + 1) группы выполнены из параллельно включенных P- и N-канальных МОП-транзисторов.

В других случаях поставленная цель достигается тем, что интегральный n-разрядный цифроаналоговый преобразователь, содержащий 2n последовательно соединенных резисторов, объединенных в M групп по 2n/M резисторов в каждой группе, 2n МОП-ключей, объединенных в M групп по 2n/M ключей в каждой группе, (M + 1) группу из 2n/M МОП-ключей и два дешифратора, причем первый вывод первого резистора первой группы и второй вывод 2n/M-го резистора M-й группы соединены с выводами источника опорного напряжения, информационный вход i-го МОП-ключа (где  ) j-й группы (где

) j-й группы (где  ) соединен с первым выводом i-го резистора j-й группы, выходы i-х МОП-ключей всех M групп объединены и подключены к информационному входу i-го МОП-ключа (M + 1)-й группы, управляющие входы всех МОП-ключей j-й группы объединены и подключены к выходам j-го разряда первого дешифратора, входы которого являются входами старших разрядов преобразователя, управляющие входы i-х МОП-ключей (M + 1) группы подключены к выходам i-х разрядов второго дешифратора, входы которого являются входами младших разрядов преобразователя, а выходы всех ключей (M + 1)-й группы объединены и являются аналоговым выходом преобразователя, отличающийся тем, что ключи групп с первой по M/4 выполнены из N-канальных МОП-транзисторов, ключи групп с (M/4 + 1) по M и (M + 1) группы выполнены из параллельно включенных P- и N-канальных МОП-транзисторов, а их управляющие входы соединены с парафазными выходами соответствующих разрядов дешифраторов.

) соединен с первым выводом i-го резистора j-й группы, выходы i-х МОП-ключей всех M групп объединены и подключены к информационному входу i-го МОП-ключа (M + 1)-й группы, управляющие входы всех МОП-ключей j-й группы объединены и подключены к выходам j-го разряда первого дешифратора, входы которого являются входами старших разрядов преобразователя, управляющие входы i-х МОП-ключей (M + 1) группы подключены к выходам i-х разрядов второго дешифратора, входы которого являются входами младших разрядов преобразователя, а выходы всех ключей (M + 1)-й группы объединены и являются аналоговым выходом преобразователя, отличающийся тем, что ключи групп с первой по M/4 выполнены из N-канальных МОП-транзисторов, ключи групп с (M/4 + 1) по M и (M + 1) группы выполнены из параллельно включенных P- и N-канальных МОП-транзисторов, а их управляющие входы соединены с парафазными выходами соответствующих разрядов дешифраторов.

Сущность изобретения поясняется чертежами.

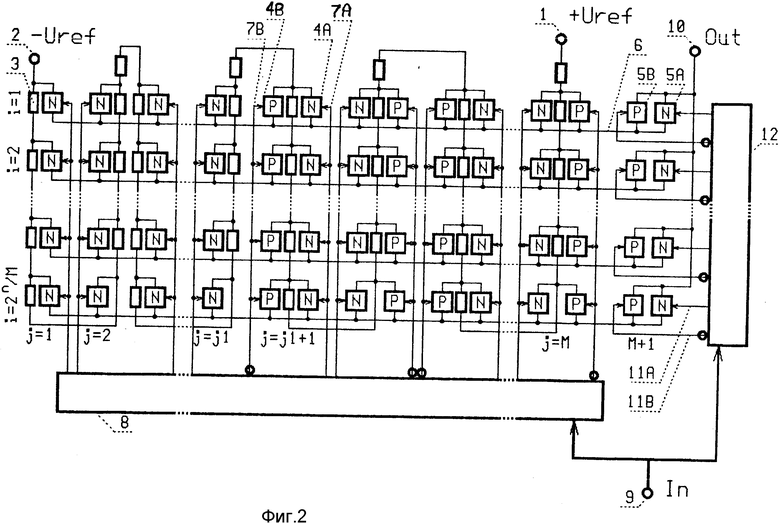

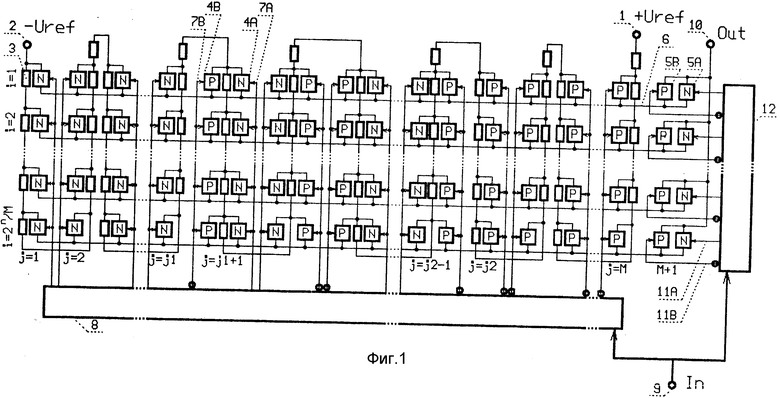

На фиг. 1. представлена схема заявляемого n-разрядного интегрального ЦАП, включающего ключи как на N и P, так и на параллельно включенных N- и P-канальных МОП-транзисторах, в соответствии с п. 1, 2 и 3 формулы изобретения; на фиг. 2 - схема заявляемого n-разрядного интегрального ЦАП, включающего ключи на N- и параллельно включенных N- и P-канальных МОП-транзисторах, в соответствии с п. 4 формулы изобретения; на фиг. 3 - пример топологической реализации заявляемого ЦАП в кристалле КМОП интегральной схемы.

Заявляемый n-разрядный ЦАП (фиг. 1) содержит подключенную между выводами источника опорного напряжения положительной (1) и отрицательной (2) полярностей, резистивную цепочку из (2n) равных резисторов (3), объединенных в прямоугольную матрицу из M групп по i = (2n/M) резисторов в группе, (2n) МОП-ключей (4A, 4B), также объединенных в прямоугольную матрицу из M групп по i = (2n/M) ключей в группе и (M + 1) группу из (2n/M) МОП-ключей (5A, 5B). Информационный вход каждого i-го МОП-ключа (4A, 4B) (где i =  ) j-й группы (где j =

) j-й группы (где j =  ) соединен с первым выводом i-го резистора своей (j-й) группы, выходы i-х МОП-ключей (4A, 4B) всех M групп объединены между собой и подключены к информационным входам (6) соответственно i-х МОП-ключей (5A, 5B) (M + 1) группы, эквивалентные управляющие входы МОП-ключей (4A, 4B) в пределах каждой j-й группы объединены и подключены к выходам (7A, 7B) j-го разряда первого дешифратора (8), входы которого являются входами (9) старших разрядов ЦАП, выходы МОП-ключей (5A, 5B)(M + 1)-й группы объединены и являются аналоговым выходом ЦАП (10), а их управляющие входы - подключены к выходам (11A, 11B) i-х разрядов второго дешифратора (12), входы которого являются входами младших разрядов ЦАП. При этом ключи групп с 1 по J1 выполнены из N-канальных МОП-транзисторов, ключи групп с J2 по M выполнены из P-канальных МОП-транзисторов, а ключи групп с (J1 + 1) по (J2 - 1) и (M + 1) группы выполнены из параллельно включенных N- и P-канальных МОП-транзисторов.

) соединен с первым выводом i-го резистора своей (j-й) группы, выходы i-х МОП-ключей (4A, 4B) всех M групп объединены между собой и подключены к информационным входам (6) соответственно i-х МОП-ключей (5A, 5B) (M + 1) группы, эквивалентные управляющие входы МОП-ключей (4A, 4B) в пределах каждой j-й группы объединены и подключены к выходам (7A, 7B) j-го разряда первого дешифратора (8), входы которого являются входами (9) старших разрядов ЦАП, выходы МОП-ключей (5A, 5B)(M + 1)-й группы объединены и являются аналоговым выходом ЦАП (10), а их управляющие входы - подключены к выходам (11A, 11B) i-х разрядов второго дешифратора (12), входы которого являются входами младших разрядов ЦАП. При этом ключи групп с 1 по J1 выполнены из N-канальных МОП-транзисторов, ключи групп с J2 по M выполнены из P-канальных МОП-транзисторов, а ключи групп с (J1 + 1) по (J2 - 1) и (M + 1) группы выполнены из параллельно включенных N- и P-канальных МОП-транзисторов.

Заявляемый ЦАП работает следующим образом.

Ток от источника опорного напряжения ЦАП, протекающий через резистивную цепочку, формирует сетку (2n) равноотстоящих потенциалов в диапазоне от положительного до отрицательного потенциала источника опорного напряжения, соответствующих (2n) значениям входного n-разрядного кода ЦАП. Первый и второй дешифраторы (8) и (12) в соответствии с n-разрядным входным кодом ЦАП формируют сигналы управления, подаваемые на управляющие входы (7), (11) МОП-ключей (4) и (5) таким образом, что при любом значении входного кода открыты все ключи (4) только одной из M групп, а также открыт только один из i ключей M + 1 группы, при этом аналоговый выход ЦАПа (10) через открытый ключ (M + 1)-й группы и открытый ключ одной из j групп подключен к резистору резистивной цепочки с потенциалом, соответствующим значению входного кода. Следовательно, через некоторое время, определяемое постоянной времени заряда эквивалентной емкости выхода ЦАП через сопротивление 2-х МОП-ключей и сопротивление резистивной цепочки, на аналоговом выходе ЦАП установится потенциал, соответствующий входному n-разрядному коду ЦАП. При этом ключи с 1 по J1 групп, коммутирующие напряжения, близкие к напряжению отрицательного вывода источника опорного напряжения (и напряжению "земли" источника питания ЦАП) и выполненные на N-канальных МОП-транзисторах, ключи с J2 по M групп, коммутирующие напряжения, близкие к напряжению положительного вывода источника опорного напряжения (и следовательно, близкие к напряжению питания ЦАП при расширении диапазона выходного аналогового сигнала до напряжения питания) и выполненные на P-канальных МОП-транзисторах, а также ключи групп с (J1 + 1) по (J2 - 1), выполненные на параллельно включенных N- и P-канальных МОП-транзисторах, имеют на своих управляющих входах потенциалы, обеспечивающие минимально возможные сопротивления, что обеспечивает снижение времени заряда выходной емкости ЦАП и, тем самым, повышает его быстродействие.

Таким образом, поставленные цели расширения диапазона выходных аналоговых сигналов вплоть до диапазона напряжений питания ЦАП и повышение быстродействия ЦАП достигается в заявляемом ЦАП возможностью выполнения МОП-ключей в любой из групп на транзисторах с каналом любого типа проводимости, в зависимости от того, какой потенциал должны коммутировать соответствующие ключи.

Действительно, из теории МОП-транзистора максимальное сопротивление ключей на N- и P-канальных МОП-транзисторах в j группе можно записать соответственно в виде:

Rn(j) = {2Kn [Ucc + Uref2 - ((Uref1 + Uref2) (j)/M) - U*тn]}-1 (1)

Rp(j) = {2Kp [Ucc + Uref2 - ((Uref1 + Uref2) (M - j + 1)/M) - U*тp]}-1 (2)

где

Kn, Kp - удельные крутизны N- и P-канальных МОП-транзисторов соответственно;

Ucc, Uref1, Uref2 - напряжение питания и положительное и отрицательное опорные напряжения ЦАП соответственно;

j - текущий номер группы МОП-ключей (от 1 до M);

U*тn, U*тp - эффективные пороговые напряжения N- и P-канальных МОП-транзисторов с учетом обратного смещения на их подложках относительно истоков соответственно.

Из выражений (1), (2) видно, что с увеличением текущего номера группы j от 1 до M сопротивление N-канального МОП-транзистора увеличивается от минимально-возможного в 1 группе, определяемого по формуле (3),

Rn(1) = {2Kn [Ucc + Uref2 - ((Uref1 + Uref2)/M - U*тn]}-1 (3)

до бесконечно большого для закрытых транзисторов при j, близких к M, т. е. при:

j≥M(Ucc + Uref2 - U*тn)/(Uref1 + Uref2) (4)

Аналогично с увеличением текущего номера группы j от 1 до M сопротивление P-канального МОП-транзистора уменьшается от бесконечно большого для закрытых транзисторов при:

j≤M(Ucc + Uref2 - U*тp)/(Uref1 + Uref2) (5)

до минимально-возможного при j = M, определяемого по формуле (6).

Rp(M) = {2Kp [Ucc + Uref2 - ((Uref1 + Uref2)/M) - U*тp]}-1 (6)

Очевидно, что для любой совокупности значений напряжения питания и опорного напряжения ЦАП существует значение Jm, для которого сопротивления N- и P-канальных транзисторов примерно равны и соответствуют минимально-возможному сопротивлению ключа в данной (Jm) группе. Это значение (Jm) можно приближенно определить по формуле (8), полученной из уравнения (7) с учетом (1), (2).

Rn = Rp (7)

Jm = M [(Kn/Kp + 1) (Ucc + Uref2) - U*тn Kn/Kp + U*тp + (Uref1 + Uref2)

(M + 1)/M]/[Kn/Kp + 1) (Uref1 + Uref2)] (8)

Отсюда очевидно, также, что в группах ключей с номерами от 1 до (Jm - 1) минимальное сопротивление имеют N-канальные МОП-транзисторы, а в группах от (Jm + 1) до M минимальное сопротивление у P- канальных транзисторов, что и определяет оптимальную границу между группами P- и N- канальных транзисторов для обеспечения максимального быстродействия ЦАП.

Существует возможность дальнейшего повышения быстродействия ЦАП, выполнением ключей средних групп (в области оптимального значения j) из параллельно включенных транзисторов с каналами N- и P-типа, при этом среднее сопротивление таких ключей снижается на величину до 50% от сопротивления униполярных. Задаваясь требованием снижения сопротивлений ключей средних групп не менее, чем на 20%, можно определить номера двух граничных групп J1 и J2, отделяющих крайние группы с униполярными ключами от средних, в которых необходимы ключи с параллельно включенными N- и P-канальными транзисторами, из следующих условий:

J1 из условия: Rp(j) = 4Rn(j) (9)

J2 из условия: Rn(j) = 4Rp(j) (10)

Решая уравнения (9) и (10) с учетом (1) и (2), получаем:

J1 = M[(Kn/(4Kp) - 1) (Ucc + Uref2) - U*тn Kn/(4Kp) + U* тp + (Uref1 + Uref2) • (M + 1)/M]/[(Kn/(4Kp) + 1) (Uref1 + Uref2)] (11)

J2 = M [(4Kn/Kp - 1) (Ucc + Uref2) - U*тn 4Kn/Kp + U*тp + (Uref1 + Uref2) • (M + 1)/M]/[(4Kn/Kp + 1) (Uref1 + Uref2)] (12)

Отметим, что для более точного определения оптимальных значений граничных групп Jm, J1, J2 необходимо в выражениях (1), (2) учитывать зависимость порогового напряжения МОП-транзисторов от обратного смещения на их подложках относительно истоков, представляемую формулами (13), (14), (15):

U*т = Uто + A [(B + Uип)-0,5 - (B)-0,5] (13)

Uипn = (Uref1 + Uref2) j/M (14)

Uипp = (Uref1 + Uref2) (M - j + 1)/M (15)

где Uт и Uто - пороговые напряжения МОП-транзистора со смещением подложки относительно истока величиной Uип и без смещения соответственно;

A и B - коэффициенты, зависящие от конструкции МОП-транзисторов.

Поскольку, Uип зависит от j, то аналитическое выражение для граничных групп J1 и J2 существенно усложняется и поэтому здесь не приводится, однако численный расчет J1 и J2 не представляет больших проблем.

Например, для 8 разрядного ЦАП (n = 8), M = 16, Ucc = Uref = 5 В, Uтоp = Uтоn = 1 В, Kn = 2Kp, что соответствует типовым характеристикам, можно получить: J1 = 5, J2 = 11, т.е. ключи групп с 1 по 5 могут быть N-канальными, ключи групп с 6 по 10 должны быть на параллельно включенных N- и P-канальных МОП-транзисторах, а ключи групп с 11 по 16 должны быть на P- канальных МОП-транзисторах. Следует учесть, что в реальных условиях интегральной схемы топологически удобнее использовать ключи на транзисторах одного типа в четном количестве групп, а дешифраторы упрощаются при использовании транзисторов одинакового типа в (2, 4, 8, 16 и т.д.) группах, поэтому целесообразно расширить количество групп с параллельно включенными N- и P- канальными МОП-транзисторами с 5 по 12, что соответствует п. 3 формулы изобретения.

В другом типовом случае для Uref = 2,5 В и Uccmin = 4,7 В, в том же ЦАП с n = 8, M = 16 получаем J1 = 11, J2 > 16, т.е. ключи групп с 1 по 11 могут быть N-канальными, ключи групп с 12 по 16 должны быть только на параллельно включенных N- и P-канальных МОП-транзисторах, а ключи на P-канальных МОП-транзисторах в таком ЦАП не смогут функционировать. Отсюда следует, что для универсального АЦП, предназначенного для работы в обоих указанных режимах для получения максимального быстродействия, необходимо использовать ключи на N-канальных МОП-транзисторах в группах с 1 по 4, а в группах с 5 по 16 должны быть только ключи на параллельно включенных N- и P-канальных МОП-транзисторах, что соответствует варианту реализации ЦАП по п. 4 формулы.

Пример реализации конструкции фрагмента заявляемого интегрального ЦАП в кристалле КМОП-интегральной схемы, приведенный на фиг. 3, включает резисторы, выполненные из идентичных фрагментов поликремния 13 и соединенные в цепочку металлическими перемычками 14 через контактные окна 15, МОП-транзисторы ключей 1 - M групп, выполненные в областях подложки, ограниченных контурами диффузионных областей 16, 17 и соединенные истоками с соответствующими металлическими перемычками резистивной цепочки через контактные окна 18, стоками - через контактные окна 20 с металлическими шинами 19, подключенными к истокам транзисторов ключей M + 1 группы, а управляющие входы (затворы) МОП-транзисторов ключей j-х групп выполнены поликремниевыми шинами 21, 22.

Как видно из фиг. 3, приведенная конструкция кристалла интегрального ЦАП позволяет просто реализовать ключи любой группы на МОП-транзисторах с каналом любого типа или на параллельно включенных транзисторах с каналами дополняющих типов. Действительно, к любому резистору цепочки в заявляемом ЦАП могут быть подключены два МОП транзистора, размещенные слева и справа от резистивной цепочки, причем эти два транзистора изолированы от резисторов и друг от друга и могут быть как одного, так и разных типов проводимости.

В заявляемом ЦАП во всех ключах M + 1 группы необходимо применять параллельно включенные транзисторы N- и P-типов проводимости, поскольку все они должны при минимальном сопротивлении коммутировать потенциалы во всем диапазоне опорного напряжения.

Моделирование электрической схемы 8 разрядного ЦАП, заявляемого по п. 1, 2, 4 формулы изобретения с приведенной на фиг. 2 конструкцией кристалла при Ucc = Uref = 5В, M = 16, Uтоp = Uтnn = 1,0 В, Kn = 2Kp и при J1 = 4, т.е. с N-канальными МОП-транзисторами в ключах 1 - 4 групп и ключами на комплементарных МОП-транзисторах в 5 - 16 и 17 группах, показало, что ЦАП при напряжении питания 5 В способен формировать выходной аналоговый сигнал также до 5 В и имеет точность преобразования 0,2 - 0,3 единицы младшего разряда при времени установления выходного сигнала ЦАП - не более 200 нс.

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ И СПОСОБ ЕГО КАЛИБРОВКИ | 2010 |

|

RU2442279C1 |

| КМОП-усилитель с чоппер-стабилизацией и способ калибровки | 2022 |

|

RU2809617C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ И СПОСОБ КАЛИБРОВКИ СМЕЩЕНИЯ НУЛЯ | 2013 |

|

RU2520427C1 |

| СПОСОБ И СХЕМА УМЕНЬШЕНИЯ УТЕЧЕК И СТАБИЛИЗАЦИИ ПОРОГОВЫХ НАПРЯЖЕНИЙ МОП ТРАНЗИСТОРОВ В ИС | 2013 |

|

RU2520426C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ И СПОСОБ ЕГО КАЛИБРОВКИ | 2013 |

|

RU2520421C1 |

| ПРЕЦИЗИОННЫЙ КМОП УСИЛИТЕЛЬ | 2005 |

|

RU2310270C1 |

| КМОП усилитель с чоппер стабилизацией и способ калибровки | 2019 |

|

RU2724989C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ И СПОСОБ ЕГО КАЛИБРОВКИ | 2006 |

|

RU2341017C2 |

| ЦИФРО-АНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ И СПОСОБ ЕГО КАЛИБРОВКИ | 2013 |

|

RU2568323C2 |

| Прецизионный преобразователь напряжения в частоту | 2022 |

|

RU2819791C1 |

Изобретения относятся к области электронной техники и могут быть использованы в системах преобразования аналоговой информации в цифровую. Цель изобретения заключается в расширении диапазона выходного аналогового сигнала. Оба преобразователя содержат 2n последовательно соединенных резисторов, объединенных в M групп по 2n/M резисторов в каждой, 2n МОП-ключей, объединенных в M групп по 2n/M в каждой, (M + 1) группу из 2n/M МОП-ключей и два дешифратора. В первом изобретении ключи групп с первой по J1 выполнены из N - канальных МОП-транзисторов, ключи групп с J2 по M выполнены из Р-канальных МОП-транзисторов, ключи групп с (J1 + 1) по (J2 - 1) и (M + 1) групп выполнены из параллельно включенных P- и N - канальных МОП транзисторов. Во втором изобретении ключи групп с первой по M/4 выполнены из N - канальных МОП-транзисторов, ключи групп с (M/4 + 1) по M и (M + 1) группы выполнены из параллельно включенных P- и N-канальных МОП-транзисторов. 2 с. и 2 з.п. ф-лы, 3 ил.

) j-й группы (где

) j-й группы (где  соединен с первым выводом i-го резистора j-й группы, выходы i-х МОП-ключей всех М групп объединены и подключены к информационному входу i-го МОП-ключа (М+1)-й группы, управляющие входы всех МОП-ключей j-й группы объединены и подключены к выходам j-го разряда первого дешифратора, входы которого являются входами старших разрядов преобразователя, управляющие входы i-х МОП-ключей (М+1)-й группы подключены к выходам i-х разрядов второго дешифратора, входы которого являются входами младших разрядов преобразователя, а выходы всех ключей (М+1)-й группы объединены и являются аналоговым выходом преобразователя, отличающийся тем, что ключи групп с первой по J1 выполнены из N-канальных МОП-транзисторов, ключи групп с J2 по М выполнены из Р-канальных МОП-транзисторов, а ключи групп с (J1+1)-й (J2-1)-у и (М+1)-й группы выполнены из параллельно включенных Р- и N-канальных МОП-транзисторов, а их управляющие входы соединены с парафазными выходами соответствующих разрядов дешифраторов.

соединен с первым выводом i-го резистора j-й группы, выходы i-х МОП-ключей всех М групп объединены и подключены к информационному входу i-го МОП-ключа (М+1)-й группы, управляющие входы всех МОП-ключей j-й группы объединены и подключены к выходам j-го разряда первого дешифратора, входы которого являются входами старших разрядов преобразователя, управляющие входы i-х МОП-ключей (М+1)-й группы подключены к выходам i-х разрядов второго дешифратора, входы которого являются входами младших разрядов преобразователя, а выходы всех ключей (М+1)-й группы объединены и являются аналоговым выходом преобразователя, отличающийся тем, что ключи групп с первой по J1 выполнены из N-канальных МОП-транзисторов, ключи групп с J2 по М выполнены из Р-канальных МОП-транзисторов, а ключи групп с (J1+1)-й (J2-1)-у и (М+1)-й группы выполнены из параллельно включенных Р- и N-канальных МОП-транзисторов, а их управляющие входы соединены с парафазными выходами соответствующих разрядов дешифраторов. j-й группы (где

j-й группы (где  соединен с первым выводом i-го резистора j-й группы, выходы i-х МОП-ключей всех М групп объединены и подключены к информационному входу i-го МОП-ключа (М+1)-й группы, управляющие входы всех МОП-ключей j-й группы объединены и подключены к выходам j-го разряда первого дешифратора, входы которого являются входами старших разрядов преобразователя, управляющие входы i-х МОП-ключей (М+1)-й группы подключены к выходам i-х разрядов второго дешифратора, входы которого являются входами младших разрядов преобразователя, а выходы всех ключей (М+1)-й группы объединены и являются аналоговым выходом преобразователя, отличающийся тем, что ключи групп с первой по М/4 выполнены из N-канальных МОП-транзисторов, ключи групп с (М/4+1)-й по М-у и (М+1)-й группы выполнены из параллельно включенных Р- и N-канальных МОП-транзисторов, а их управляющие входы соединены с парафазными выходами соответствующих разрядов дешифраторов.

соединен с первым выводом i-го резистора j-й группы, выходы i-х МОП-ключей всех М групп объединены и подключены к информационному входу i-го МОП-ключа (М+1)-й группы, управляющие входы всех МОП-ключей j-й группы объединены и подключены к выходам j-го разряда первого дешифратора, входы которого являются входами старших разрядов преобразователя, управляющие входы i-х МОП-ключей (М+1)-й группы подключены к выходам i-х разрядов второго дешифратора, входы которого являются входами младших разрядов преобразователя, а выходы всех ключей (М+1)-й группы объединены и являются аналоговым выходом преобразователя, отличающийся тем, что ключи групп с первой по М/4 выполнены из N-канальных МОП-транзисторов, ключи групп с (М/4+1)-й по М-у и (М+1)-й группы выполнены из параллельно включенных Р- и N-канальных МОП-транзисторов, а их управляющие входы соединены с парафазными выходами соответствующих разрядов дешифраторов.

Даты

1998-06-10—Публикация

1995-05-03—Подача