В современной радиоэлектронной аппаратуре находят применение симметричные активные нагрузки [1-10], обеспечивающие преобразование выходных токов симметричных дифференциальных каскадов и их согласование с промежуточными выходными каскадами, например, в операционных усилителях (ОУ). На их основе реализуется широкий класс устройств преобразования и усиления сигналов [1-10].

Для работы в условиях космического пространства в экспериментальной физике необходимы радиационно-стойкие микроэлектронные изделия, допускающие одновременное воздействие на них низких температур, потока нейтронов и накопленной дозы радиации. Мировой опыт проектирования устройств данного класса показывает, что решение этих задач возможно с использованием биполярно-полевых технологических процессов [11].

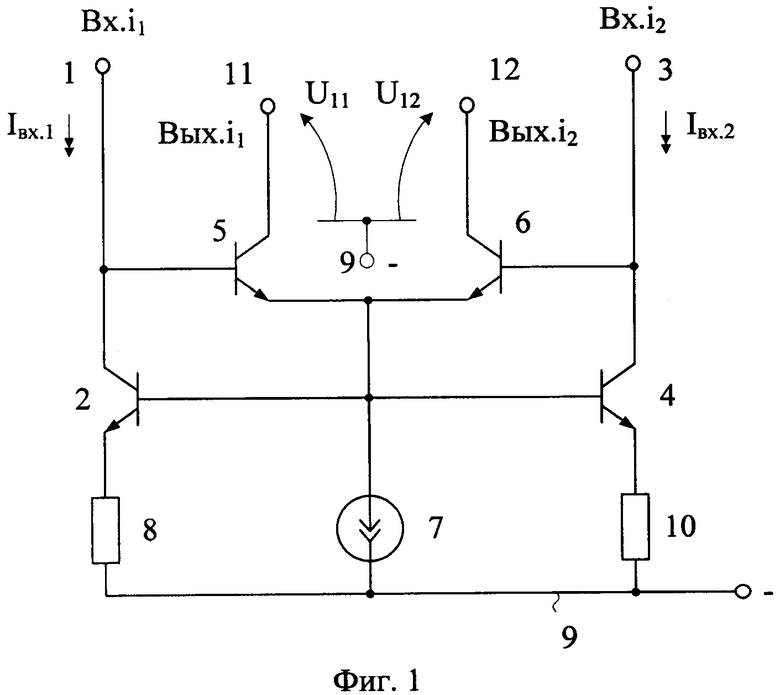

Ближайшим прототипом (фиг. 1) заявляемого устройства является симметричная активная нагрузка (САН) по патенту US №7411451, fig. 2. Она содержит первый (1) токовый вход, связанный с коллектором первого (2) входного транзистора, второй (3) противофазный токовый вход, связанный с коллектором второго (4) входного транзистора, первый (5) выходной транзистор, базовый управляющий вывод которого соединен с первым (1) токовым входом, второй (6) выходной транзистор, базовый управляющий вывод которого соединен со вторым (3) токовым входом, токостабилизирующий двухполюсник (7), первый вывод которого соединен с базами первого (2) и второго (4) входных транзисторов, а также инжектирующими выводами первого (5) и второго (6) выходных транзисторов, первый (8) вспомогательный резистор, включенный между эмиттером первого (2) входного транзистора и первой (9) шиной источника питания, второй (10) вспомогательный резистор, включенный между эмиттером второго (4) входного транзистора и первой (9) шиной источника питания, первый (11) и второй (12) токовые выходы устройства.

Основной существенный недостаток известной схемы САН состоит в том, что наиболее ответственные элементы схемы (транзисторы 5, 6), определяющие коэффициенты ее усиления по току, а также радиационную и низкотемпературную зависимость основных характеристик САН, реализуются здесь на n-p-n транзисторах 5 и 6. Однако при отрицательных температурах коэффициент усиления по току базы β n-p-n транзисторов 5 и 6 уменьшается до 2÷5 единиц, в то время как полевые транзисторы АБМК [11] устойчиво работают до -190°C. Это не позволяет применять полевые транзисторы с управляющим p-n переходом в САН при построении радиационно-стойких и низкотемпературных микросхем на основе хорошо зарекомендовавшего себя биполярно-полевого технологического процесса [11], который обеспечивает формирование p-канальных полевых транзисторов с радиационной стойкостью до 1 Мрад и потоком нейтронов до 1013н/см2.

Кроме этого, известная схема САН может работать только при относительно больших значениях статических напряжений на первом 11 и втором 12 выходах устройства. Это отрицательно сказывается на диапазонах изменения выходных напряжений известной САН, либо требует повышенных напряжений источников питания.

Основная задача предлагаемого изобретения состоит в создании радиационно-стойкой и низкотемпературной симметричной активной нагрузки с использованием в структуре ее наиболее ответственных узлов (транзисторы 5, 6) полевых транзисторов с управляющим p-n переходом биполярно-полевого технологического процесса [11].

Дополнительная задача - уменьшение на 0.7-0.8 В минимального значения статических напряжений на первом 11 и втором 12 выходах устройства. Это позволяет применять заявляемую САН при более низких напряжениях питания или увеличить диапазон изменения выходных напряжений при включении САН в структуру аналоговых микросхем, например операционных усилителей.

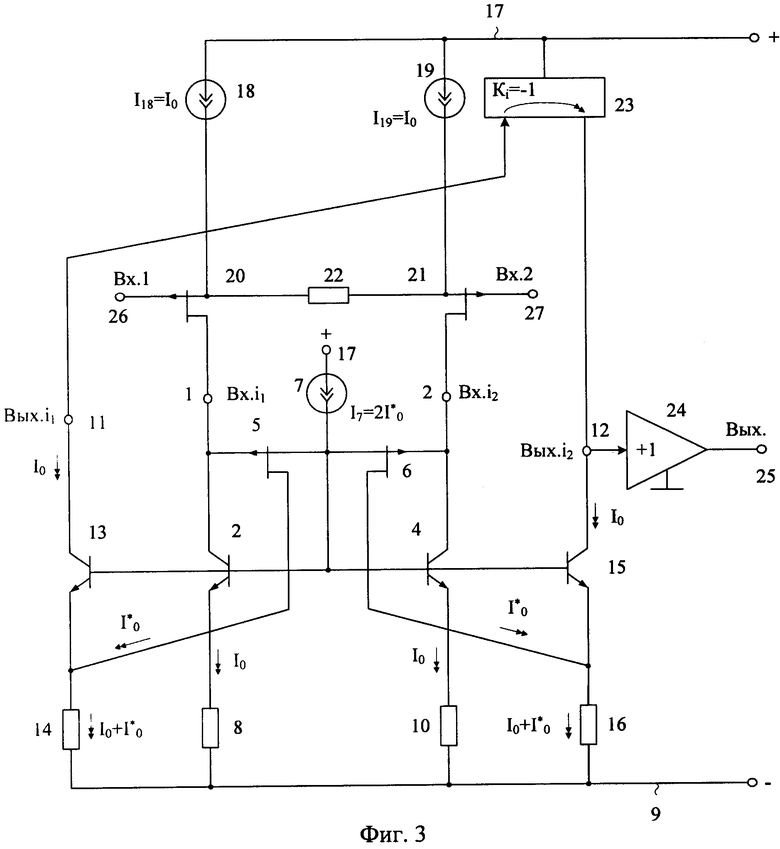

Поставленные задачи достигаются тем, что в симметричной активной нагрузке (фиг. 1), содержащей первый (1) токовый вход, связанный с коллектором первого (2) входного транзистора, второй (3) противофазный токовый вход, связанный с коллектором второго (4) входного транзистора, первый (5) выходной транзистор, базовый управляющий вывод которого соединен с первым (1) токовым входом, второй (6) выходной транзистор, базовый управляющий вывод которого соединен со вторым (3) токовым входом, токостабилизирующий двухполюсник (7), первый вывод которого соединен с базами первого (2) и второго (4) входных транзисторов, а также инжектирующими выводами первого (5) и второго (6) выходных транзисторов, первый (8) вспомогательный резистор, включенный между эмиттером первого (2) входного транзистора и первой (9) шиной источника питания, второй (10) вспомогательный резистор, включенный между эмиттером второго (4) входного транзистора и первой (9) шиной источника питания, первый (11) и второй (12) токовые выходы устройства, предусмотрены новые элементы и связи - в качестве первого (5) и второго (6) выходных транзисторов используются полевые транзисторы с управляющим p-n переходом, причем сток первого (5) выходного полевого транзистора с управляющим p-n переходом соединен с эмиттером первого (13) дополнительного транзистора и через первый (14) дополнительный резистор соединен с первой (9) шиной источника питания, сток второго (6) выходного полевого транзистора с управляющим p-n переходом соединен с эмиттером второго (15) дополнительного транзистора и через второй (16) дополнительный резистор соединен с первой (9) шиной источника питания, причем второй вывод токостабилизирующего двухполюсника (7) подключен ко второй (17) шине источника питания, согласованной с первым (11) и вторым (12) токовыми выходами устройства, коллектор первого (13) дополнительного транзистора соединен с первым (11) токовым выходом устройства, коллектор второго (15) дополнительного транзистора соединен со вторым (12) токовым выходом устройства, а базы первого (13) и второго (14) дополнительных транзисторов связаны с базами первого (2) и второго (4) входных транзисторов.

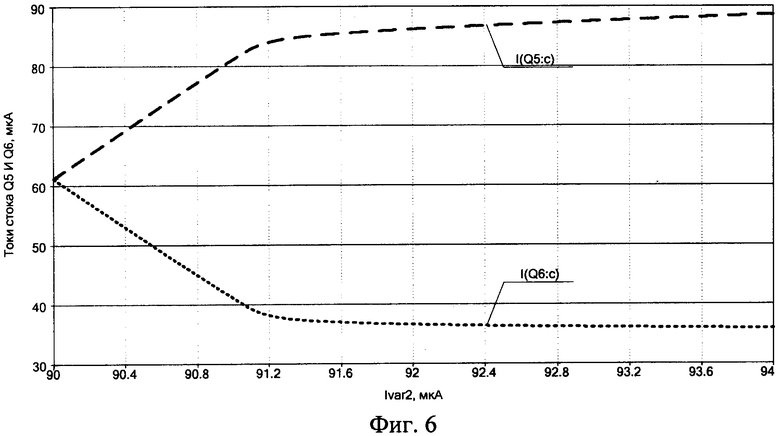

На фиг. 1 показана схема симметричной активной нагрузки - прототипа, на фиг. 2 - схема заявляемого устройства в соответствии с формулой изобретения.

На фиг. 3 показана схема заявляемого устройства в структуре операционного усилителя с одним высокоимпедансным узлом.

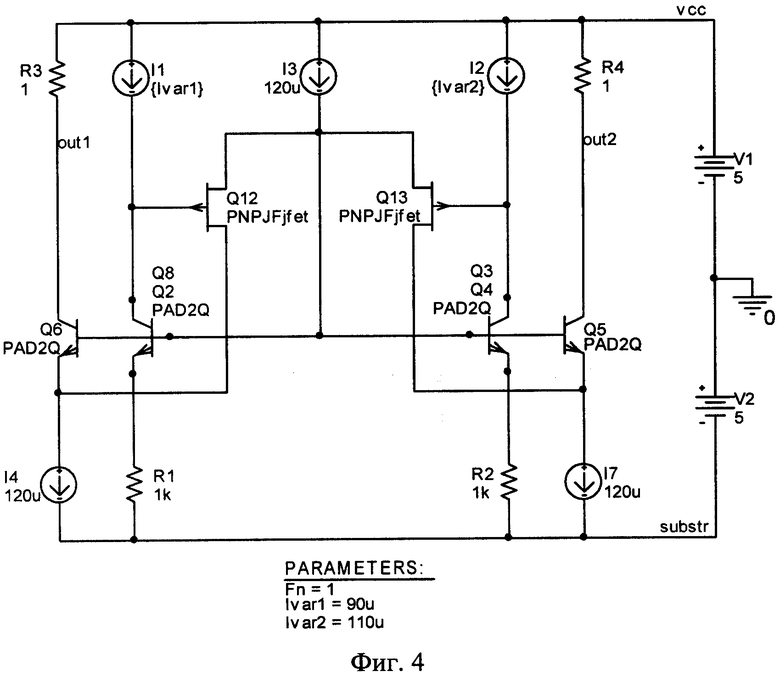

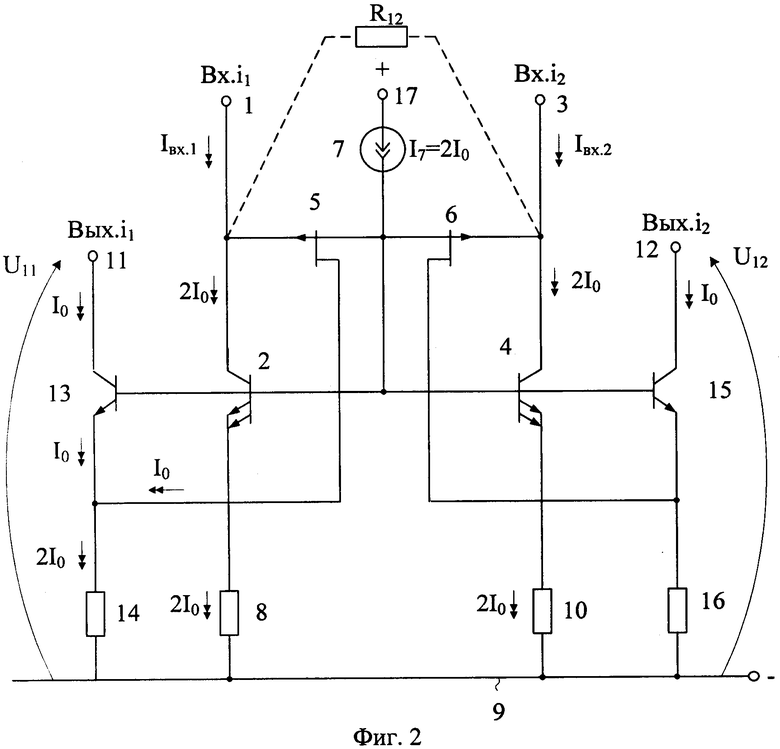

На фиг. 4 показана схема заявляемого устройства фиг. 2 в среде PSpice на моделях интегральных транзисторов АБМК_1_3 НПО «Интеграл» (г. Минск).

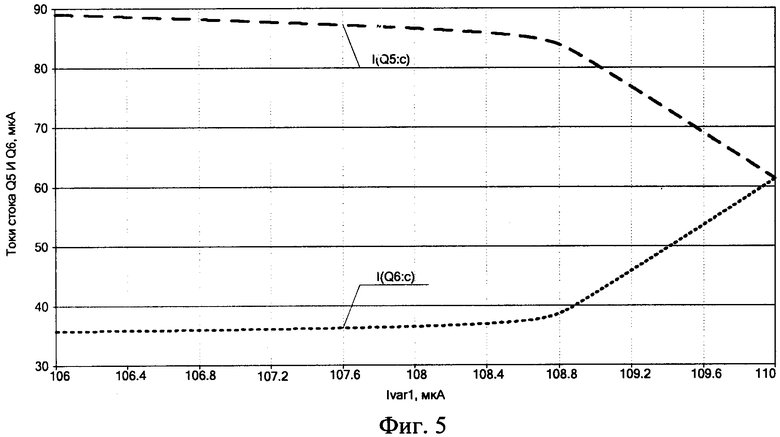

На фиг. 5 показана зависимость коллекторных токов транзисторов Q5 и Q6 схемы САН фиг. 4 (выходных токов устройства) от изменения первого входного тока I1=Ivar1.

На фиг. 6 показана зависимость коллекторных токов транзисторов Q5 и Q6 схемы САН фиг. 4 от изменения второго входного тока I2=Iyar2.

Симметричная активная нагрузка (САН) дифференциальных усилителей фиг. 2 содержит первый (1) токовый вход, связанный с коллектором первого (2) входного транзистора, второй (3) противофазный токовый вход, связанный с коллектором второго (4) входного транзистора, первый (5) выходной транзистор, базовый управляющий вывод которого соединен с первым (1) токовым входом, второй (6) выходной транзистор, базовый управляющий вывод которого соединен со вторым (3) токовым входом, токостабилизирующий двухполюсник (7), первый вывод которого соединен с базами первого (2) и второго (4) входных транзисторов, а также инжектирующими выводами первого (5) и второго (6) выходных транзисторов, первый (8) вспомогательный резистор, включенный между эмиттером первого (2) входного транзистора и первой (9) шиной источника питания, второй (10) вспомогательный резистор, включенный между эмиттером второго (4) входного транзистора и первой (9) шиной источника питания, первый (11) и второй (12) токовые выходы устройства.

В качестве первого (5) и второго (6) выходных транзисторов используются полевые транзисторы с управляющим p-n переходом, причем сток первого (5) выходного полевого транзистора с управляющим p-n переходом соединен с эмиттером первого (13) дополнительного транзистора и через первый (14) дополнительный резистор соединен с первой (9) шиной источника питания, сток второго (6) выходного полевого транзистора с управляющим p-n переходом соединен с эмиттером второго (15) дополнительного транзистора и через второй (16) дополнительный резистор соединен с первой (9) шиной источника питания, причем второй вывод токостабилизирующего двухполюсника (7) подключен ко второй (17) шине источника питания, согласованной с первым (11) и вторым (12) токовыми выходами устройства, коллектор первого (13) дополнительного транзистора соединен с первым (11) токовым выходом устройства, коллектор второго (15) дополнительного транзистора соединен со вторым (12) токовым выходом устройства, а базы первого (13) и второго (14) дополнительных транзисторов связаны с базами первого (2) и второго (4) входных транзисторов.

В схеме фиг. 3, представляющей собой операционный усилитель с заявляемой САН фиг. 2, в которой схема входного каскада ОУ содержит источники опорного тока 18, 19, входные полевые транзисторы 20, 21, масштабирующий резистор 22, токовое зеркало 23, а также неинвертирующий буферный усилитель 24, связанный с выходом устройства 25.

Рассмотрим работу заявляемой САН фиг. 2.

Статический режим первого 2 и второго 4 входных транзисторов САН определяется входными статическими токами Iвх.1, Iвх.2, которые подаются, например, от какого-либо дифференциального каскада (на схеме - не показан).

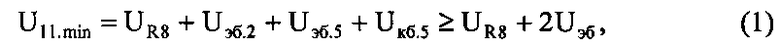

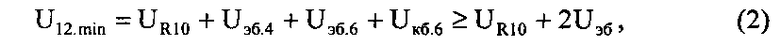

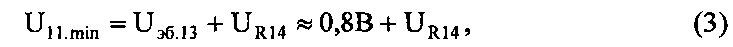

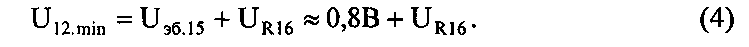

В схеме САН-прототипа (фиг. 1) минимальные выходные статические напряжения на токовых выходах 11 и 12 (относительно первой 9 шины источника питания) не могут быть меньше, чем

где UR8, UR10 - статическое напряжение на резисторах 8 и 10;

Uэб.2≈Uэб.5≈Uэб≈0,8 В - напряжение эмиттер-база транзисторов 2 и 5.

В заявленной схеме фиг. 2

где UR14, UR16 - статическое напряжение на резисторах 14 и 16.

Сравнение формул (1), (2) и (3), (4) показывает, что минимальное рабочее напряжений на токовых выходах 11 и 12 устройства фиг. 2 на 0,8 В меньше, чем в схеме САН-прототипа.

Кроме этого, коэффициент преобразования входных токов САН фиг. 2 в выходные токи узлов 11 и 12 в заявленной схеме значительно выше, чем в САН-прототипе (фиг. 1). Это объясняется более высоким уровнем эквивалентного сопротивления R12 между первым (1) и вторым (3) входами устройства. Данный эффект обеспечивается применением полевых транзисторов 5 и 6 в соответствии с пунктом 1 формулы изобретения.

Замечательная особенность схемы фиг. 2 состоит также в том, что в отличие от схемы прототипа здесь наиболее ответственные узлы реализуются на основе полевых транзисторов с управляющим p-n переходом радиационно-стойкого биполярно-полевого технологического процесса НПО «Интеграл» (г. Минск) [11]. Это позволяет согласовать выходные токи транзисторов 5 и 6 с отрицательной (9) шиной источника питания. Как следствие, данное решение обеспечивает более высокие уровни коэффициента усиления входного сигнала и его малую низкотемпературную и радиационную нестабильность.

Таким образом, заявляемое устройство имеет существенные преимущества в сравнении с прототипом.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US №7411451, fig. 2.

2. Патент US №5736899, fig. 4.

3. Патент US №4271394, fig. 3.

4. Патент US №4420726, fig. 4.

5. Патент US №4359693, fig. 1.

6. Патент US №6529070.

7. Патент US №4069460, fig. 18. Патент US №4348602, fig. 2.

9. Патент US №3614645.

10. Патент US №5963085.

11. Элементная база радиационно-стойких информационно-измерительных систем: монография / Н.Н. Прокопенко, О.В. Дворников, С.Г. Крутчинский; под общ. ред. д.т.н. проф. Н.Н. Прокопенко; ФГБОУ ВПО «Южно-Рос. гос. ун-т. экономики и сервиса». - Шахты: ФГБОУ ВПО ЮРГУЭС, 2011. - 208 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ РАДИАЦИОННО СТОЙКОГО БИПОЛЯРНО-ПОЛЕВОГО ТЕХНОЛОГИЧЕСКОГО ПРОЦЕССА | 2014 |

|

RU2568384C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ "ПЕРЕГНУТОГО" КАСКОДА | 2015 |

|

RU2604684C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2015 |

|

RU2613842C1 |

| ПРЕЦИЗИОННЫЙ ДВУХКАСКАДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2615070C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ "ПЕРЕГНУТОГО" КАСКОДА | 2015 |

|

RU2592429C1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ ДЛЯ РАДИАЦИОННО-СТОЙКОГО БИПОЛЯРНО-ПОЛЕВОГО ТЕХНОЛОГИЧЕСКОГО ПРОЦЕССА | 2014 |

|

RU2571569C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2615068C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2595926C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2616573C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2589323C1 |

Изобретение относится к применению симметричных активных нагрузок, обеспечивающих преобразование выходных токов симметричных дифференциальных каскадов и их согласование с промежуточными выходными каскадами. Технический результат заключается в создании радиационно-стойкой и низкотемпературной симметричной активной нагрузки с использованием в структуре полевых транзисторов биполярно-полевого технологического процесса, что позволяет применять их при более низких напряжениях питания или увеличить диапазон изменения выходных напряжений при включении в структуру аналоговых микросхем, например, операционных усилителей. В составе симметричной активной нагрузки в качестве первого (5) и второго (6) выходных транзисторов используются полевые транзисторы с управляющим p-n переходом, причем сток первого (5) выходного полевого транзистора с управляющим p-n переходом соединен с эмиттером первого (13) дополнительного транзистора и через первый (14) дополнительный резистор соединен с первой (9) шиной источника питания, сток второго (6) выходного полевого транзистора с управляющим p-n переходом соединен с эмиттером второго (15) дополнительного транзистора и через второй (16) дополнительный резистор соединен с первой (9) шиной источника питания, причем второй вывод токостабилизирующего двухполюсника (7) подключен ко второй (17) шине источника питания, согласованной с первым (11) и вторым (12) токовыми выходами устройства, коллектор первого (13) дополнительного транзистора соединен с первым (11) токовым выходом устройства, коллектор второго (15) дополнительного транзистора соединен со вторым (12) токовым выходом устройства, а базы первого (13) и второго (14) дополнительных транзисторов связаны с базами первого (2) и второго (4) входных транзисторов. 6 ил.

Симметричная активная нагрузка дифференциальных усилителей, содержащая первый (1) токовый вход, связанный с коллектором первого (2) входного транзистора, второй (3) противофазный токовый вход, связанный с коллектором второго (4) входного транзистора, первый (5) выходной транзистор, базовый управляющий вывод которого соединен с первым (1) токовым входом, второй (6) выходной транзистор, базовый управляющий вывод которого соединен со вторым (3) токовым входом, токостабилизирующий двухполюсник (7), первый вывод которого соединен с базами первого (2) и второго (4) входных транзисторов, а также инжектирующими выводами первого (5) и второго (6) выходных транзисторов, первый (8) вспомогательный резистор, включенный между эмиттером первого (2) входного транзистора и первой (9) шиной источника питания, второй (10) вспомогательный резистор, включенный между эмиттером второго (4) входного транзистора и первой (9) шиной источника питания, первый (11) и второй (12) токовые выходы устройства, отличающаяся тем, что в качестве первого (5) и второго (6) выходных транзисторов используются полевые транзисторы с управляющим p-n переходом, причем сток первого (5) выходного полевого транзистора с управляющим p-n переходом соединен с эмиттером первого (13) дополнительного транзистора и через первый (14) дополнительный резистор соединен с первой (9) шиной источника питания, сток второго (6) выходного полевого транзистора с управляющим p-n переходом соединен с эмиттером второго (15) дополнительного транзистора и через второй (16) дополнительный резистор соединен с первой (9) шиной источника питания, причем второй вывод токостабилизирующего двухполюсника (7) подключен ко второй (17) шине источника питания, согласованной с первым (11) и вторым (12) токовыми выходами устройства, коллектор первого (13) дополнительного транзистора соединен с первым (11) токовым выходом устройства, коллектор второго (15) дополнительного транзистора соединен со вторым (12) токовым выходом устройства, а базы первого (13) и второго (14) дополнительных транзисторов связаны с базами первого (2) и второго (4) входных транзисторов.

| US 7411451B2, 12.08.2008 | |||

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ВХОДНЫМ СОПРОТИВЛЕНИЕМ | 2009 |

|

RU2413356C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ "ПЕРЕГНУТОГО" КАСКОДА | 2008 |

|

RU2391768C2 |

| Предохранительное устройство для паровых котлов, работающих на нефти | 1922 |

|

SU1996A1 |

| US 5374859A1, 20.12.1994. | |||

Авторы

Даты

2016-01-10—Публикация

2014-11-18—Подача