ПЕРЕКРЕСТНАЯ ССЫЛКА НА РОДСТВЕННУЮ ЗАЯВКУ

Согласно 37 C.F.R. § 1.78, настоящая заявка является частичным продолжением заявки и испрашивает приоритет по более ранней дате подачи заявки c серийным номером 12/542,976, поданной 18 августа 2009 года под названием «An Integrated Circuit Including a Programmable Logic Analyzer with Enhanced Analyzing and Debugging Capabilities and a Method Therefor» (Интегральная схема, включающая в себя программируемый логический анализатор с расширенными возможностями анализа и отладки и способ для этого), содержание которой полностью включено сюда путем ссылки.

ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

Настоящее изобретение относится, в целом, к встроенному логическому анализатору и, в частности, к программируемому встроенному логическому анализатору для анализа электронной схемы.

УРОВЕНЬ ТЕХНИКИ

Логический анализатор представляет собой электронный измерительный прибор, который используется для захвата и отображения сигналов данных электронной схемы. Обычно логический анализатор захватывает сигналы данных, которые являются слишком быстрыми для того, чтобы их мог наблюдать пользователь. Пользователь наблюдает за сигналами данных, захваченными логическим анализатором, для эффективного анализа электронной схемы и принятия упреждающих мер или отладки на основании анализа.

В целом, логические анализаторы можно разделить на внешние логические анализаторы и встроенные логические анализаторы. Встроенный логический анализатор обычно входит в программируемое логическое устройство или интегральную схему (ИС), например в сложное программируемое логическое устройство (CPLD), программируемую логическую матрицу (FPGA), специализированную интегральную микросхему (ASIC). Встроенный логический анализатор имеет возможность захвата большого количества высокоскоростных сигналов данных внутри ИС.

Встроенный логический анализатор может включать в себя память для хранения захваченных сигналов данных. Обычно встроенный логический анализатор является программируемым для захвата и хранения сигналов данных, указанных пользователем. Сигналы данных, которые сохраняет встроенный логический анализатор, могут передаваться в компьютер для дальнейшего анализа. Сигналы данных обычно подаются в компьютер через интерфейс, предусмотренный на ИС.

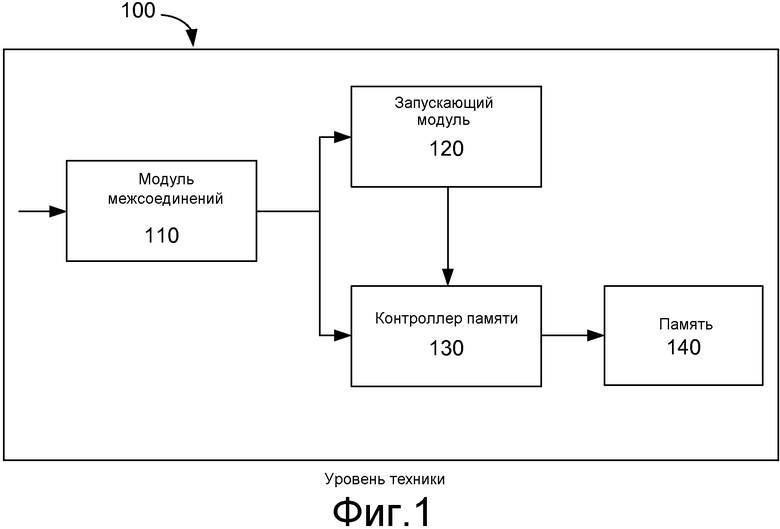

На фиг.1 изображена блок-схема традиционного встроенного логического анализатора (ELA) 100, входящего в интегральную схему (не показано). ELA 100 включает в себя модуль 110 межсоединений для приема множества сигналов данных внутри интегральной схемы. Модуль 110 межсоединений является программируемым для выбора множества сигналов, которые должны быть подвергнуты выборке, и по меньшей мере одного запускающего сигнала для задействования выборки из множества принятых сигналов. По меньшей мере один запускающий сигнал передается в запускающий модуль 120. Запускающий модуль 120 является программируемым для установки условия запуска и обнаружения, удовлетворяет ли по меньшей мере один запускающий сигнал условию запуска. Если удовлетворено условие запуска, запускающий модуль 120 инициирует процесс выборки. После инициирования процесса выборки, контроллер 130 памяти начинает выборку множества сигналов, которые должны быть подвергнуты выборке, из модуля 110 межсоединений. Выборочные сигналы можно хранить в памяти 140 для дальнейшего анализа. Поэтому ELA 100 запускает выполнение общего кода, приведенного ниже:

IF (<TRIGGER CONDITION> THEN (SAMPLE SIGNALS(X)) (IF (<условие запуска>) THEN (выполнять выборку сигналов(X))),

где TRIGGER CONDITION - любая логическая операция или последовательность логических операций, и SIGNALS (X) - множество сигналов, которые должны быть подвергнуты выборке, из модуля 110 межсоединений. Согласно коду, который выполняет ELA 100, когда выполнено условие запуска, ELA 100 осуществляет выборку по меньшей мере одного выборочного сигнала и сохраняет выборочный сигнал в памяти 140.

Однако ELA не может выполнить действие, которое отличается от выборки, когда выполнено условие запуска. Кроме того, традиционные ELA не захватывают, не анализируют и/или не отлаживают сигналы данных программного обеспечения или данных программно-аппаратных средств внутри ИС, и может потребоваться дополнительный(е) инструмент(ы) для того, чтобы анализировать эти типы данных. В дополнение, для того чтобы запрограммировать ELA или проанализировать данные, сохраненные в ELA, пользователю необходимо присутствовать на рабочей станции, где установлен ELA.

Поэтому было бы желательно выполнить ELA с расширенными возможностями анализа и отладки для устранения вышеупомянутых недостатков.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

Примерный вариант осуществления настоящего раскрытия устраняет недостатки в известных логических анализаторах и, таким образом, удовлетворяет значительную потребность в механизме для эффективного тестирования и отладки системы. Согласно примерному варианту осуществления, раскрыта интегральная схема, коммуникативно связанная в пределах системы, причем интегральная схема включает в себя логический анализатор, имеющий вход, принимающий множество сигналов, и выход для обеспечения показания обнаружения, с помощью логического анализатора по меньшей мере одного запускающего события относительно по меньшей мере одного из принятых сигналов. Интегральная схема дополнительно включает в себя блок со встроенным самотестированием (BIST), имеющий первый вход для приема одного или более сигналов, появляющихся на входе логического анализатора, и второй вход, соединенный с выходом логического анализатора для избирательного подключения блока BIST. Блок BIST генерирует и поддерживает в нем сигнатуру на основании первого и второго входных сигналов блока BIST. За счет поддержания сгенерированной сигнатуры на основании одного или более сигналов, появляющихся на входе логического анализатора и обеспечения в нем сгенерированной сигнатуры для запуска или выборки события и хранения в нем, логический анализатор позволяет более эффективно тестировать и отлаживать систему.

Дополнительные признаки и преимущества будут изложены в приведенном ниже подробном описании и частично будут очевидны специалистам в данной области техники из этого описания и исследованы при практической реализации настоящего изобретения, которое описано здесь, включая приведенное ниже подробное описание, формулу изобретения, а также прилагаемые чертежи.

Следует понимать, что вышеизложенное общее описание и нижеследующее подробное описание настоящих вариантов осуществления изобретения предназначены для того, чтобы обеспечить общее представление или основные принципы для понимания сущности и особенности изобретения, как изложено в формуле изобретения. Сопроводительные чертежи включены для лучшего понимания настоящего изобретения, и включены и образуют часть этого описания. Чертежи иллюстрируют различные варианты осуществления настоящего изобретения и вместе с описанием служат для объяснения принципов и работы настоящего изобретения.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Вышеупомянутые и другие особенности и преимущества различных вариантов осуществления и способ достижения их станут более очевидными и станут более понятными со ссылкой на сопроводительные чертежи, на которых:

фиг.1 - блок-схема традиционного встроенного логического анализатора;

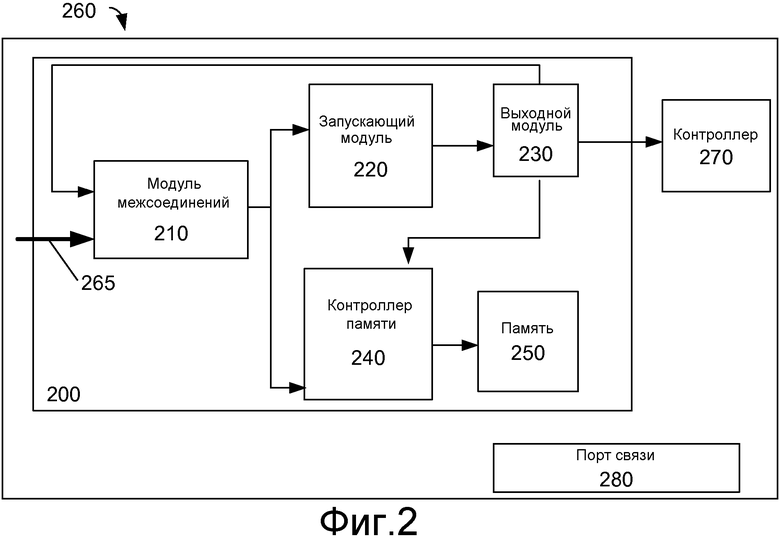

фиг.2 - блок-схема одного варианта осуществления интегральной схемы, включающей в себя логический анализатор;

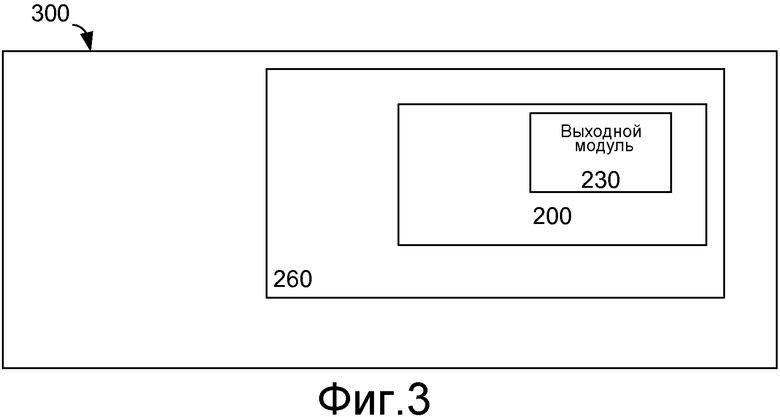

фиг.3 - блок-схема устройства, встраиваемого в интегральную схему (фиг.2);

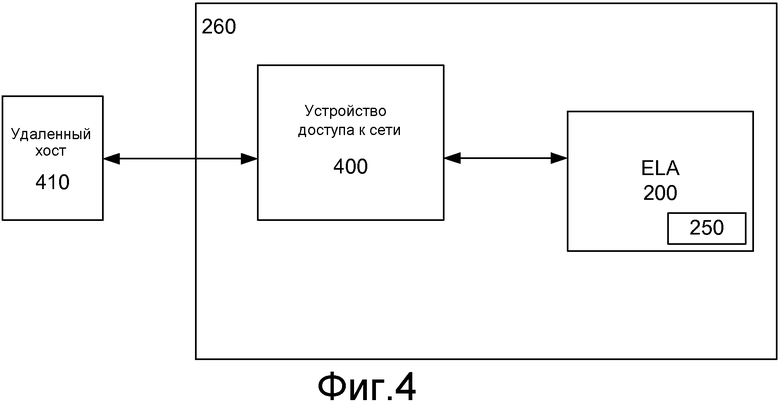

фиг.4 - блок-схема, иллюстрирующая устройство доступа к сети, связывающее удаленный хост с интегральной схемой (фиг.2);

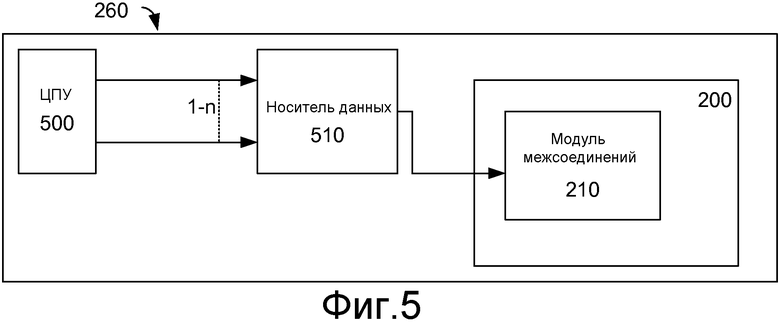

фиг.5 - блок-схема, иллюстрирующая интерфейс для подачи программных сигналов в логический анализатор, входящий в интегральную схему (фиг.2);

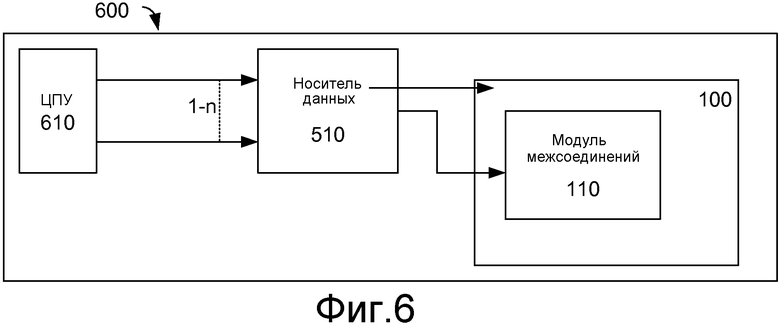

фиг.6 - блок-схема, иллюстрирующая интерфейс, выполненный с возможностью подачи программных сигналов в логический анализатор (фиг.1), согласно настоящему изобретению;

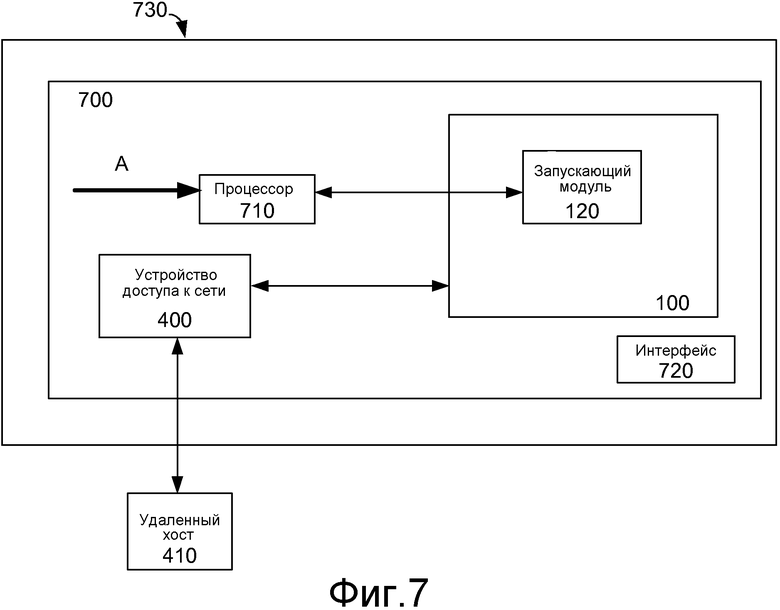

фиг.7 - блок-схема, показывающая процессор, поддерживающий связь с логическим анализатором, входящим в интегральную схему (фиг.2);

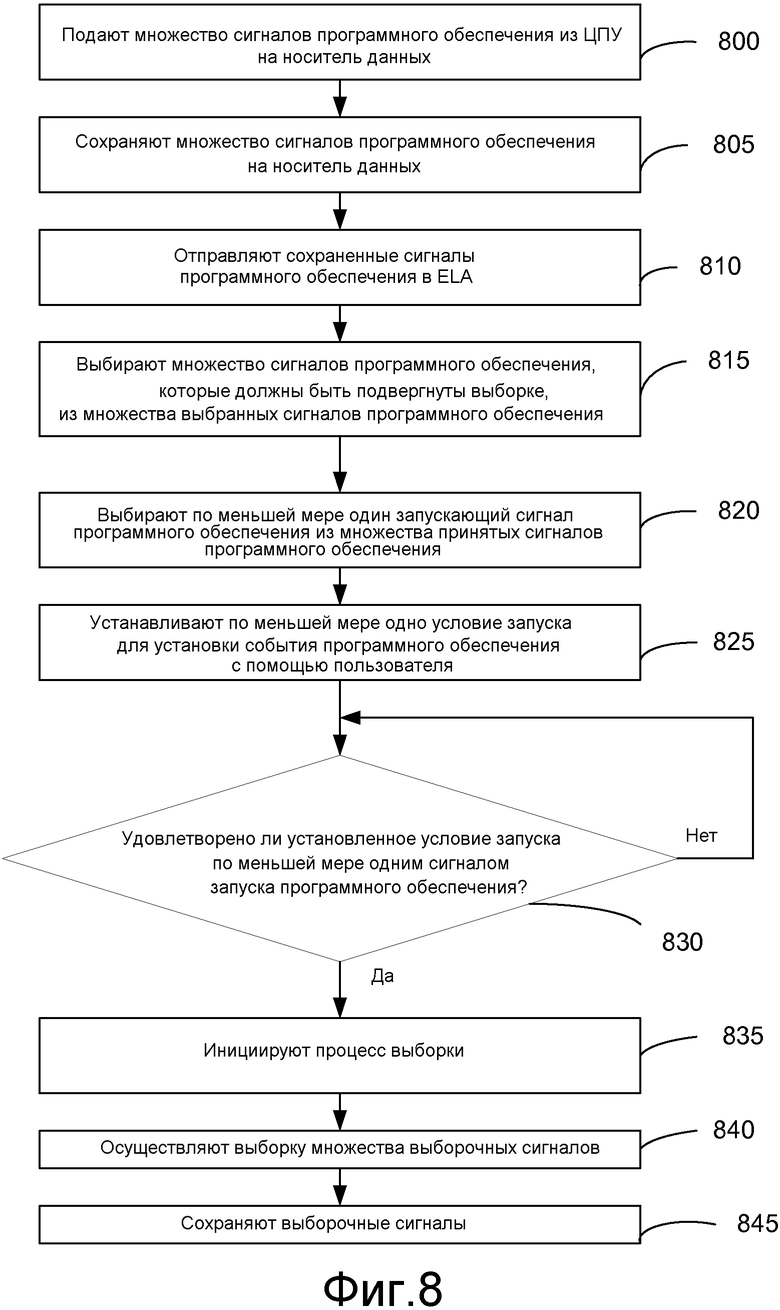

фиг.8 - блок-схема последовательности операций, иллюстрирующая действия, выполняемые для захвата программных сигналов внутри интегральной схемы (фиг.2);

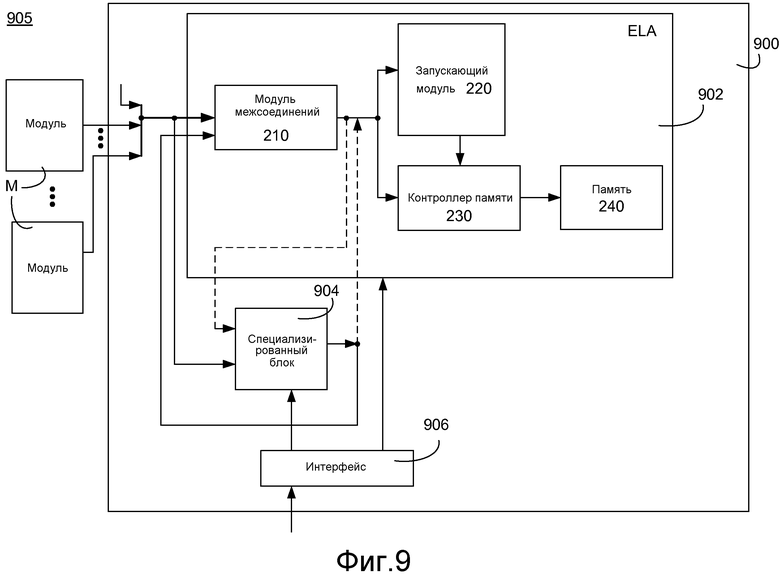

фиг.9 - блок-схема, иллюстрирующая систему, имеющую интегральную схему, согласно примерному варианту осуществления;

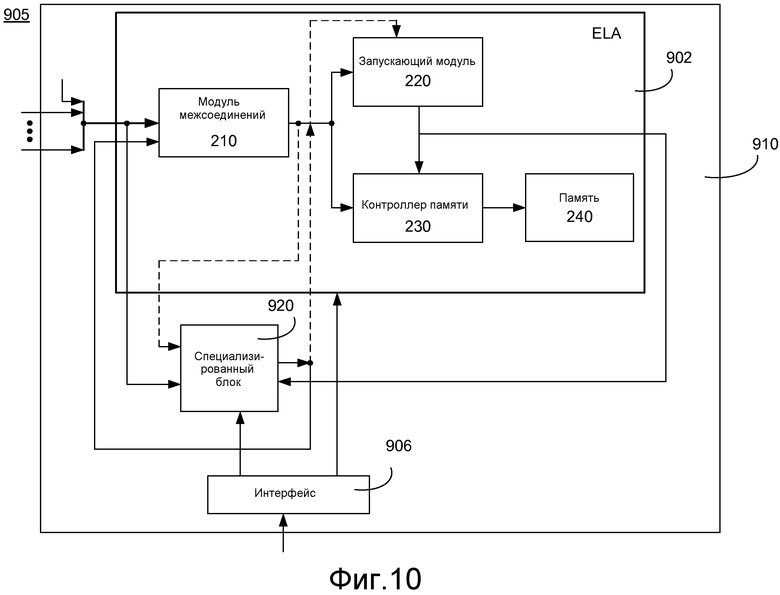

фиг.10 - блок-схема, иллюстрирующая систему, имеющую интегральную схему, согласно примерному варианту осуществления;

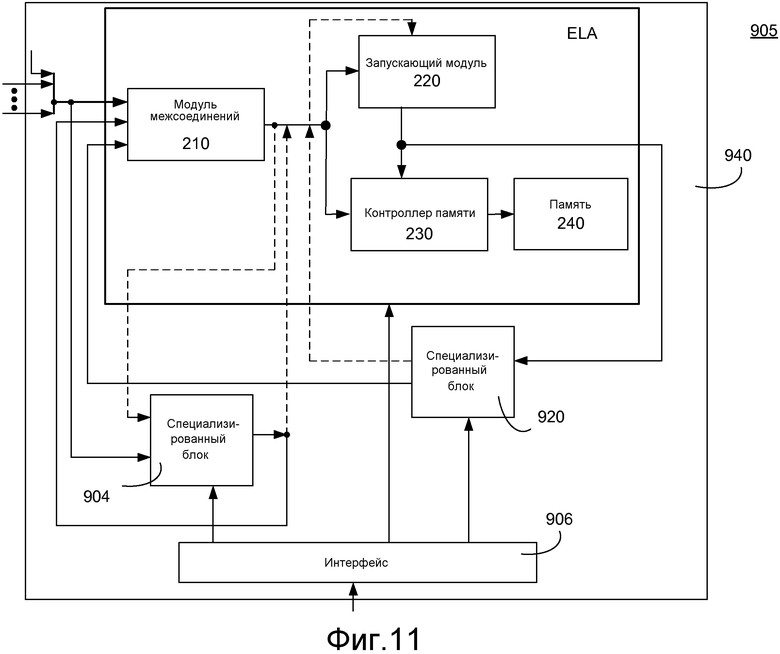

фиг.11 - блок-схема, иллюстрирующая систему, имеющую интегральную схему, согласно примерному варианту осуществления;

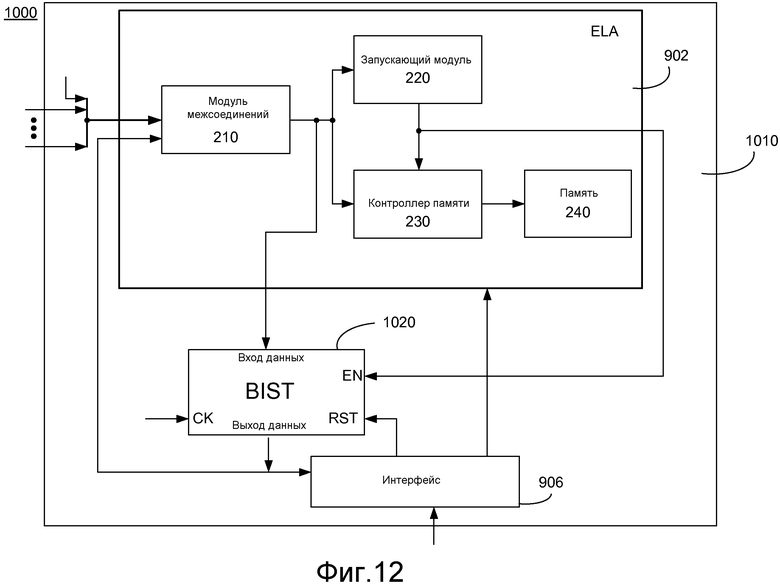

фиг.12 - блок-схема, иллюстрирующая систему, имеющую блок BIST, связанный с логическим анализатором, согласно другому примерному варианту осуществления;

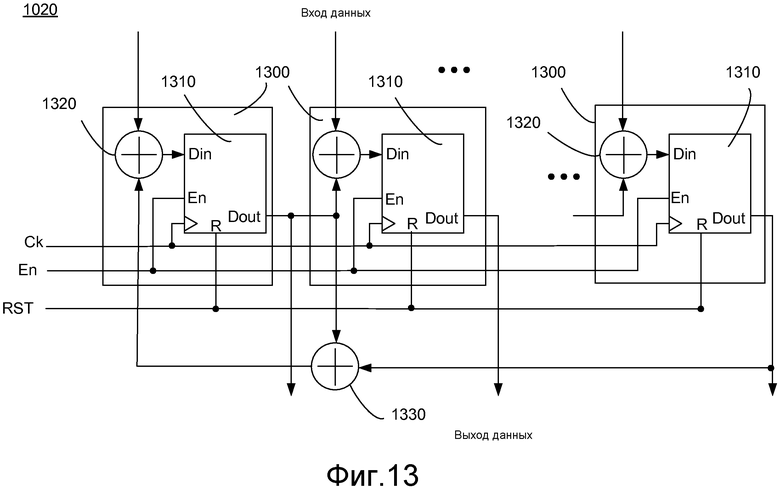

фиг.13 - блок-схема блока BIST (фиг.12);

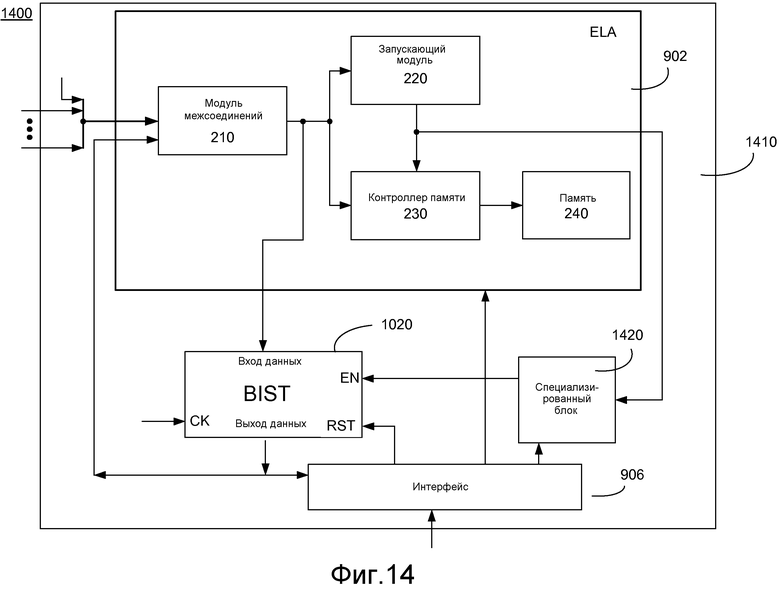

фиг.14 - блок-схема системы, включающей в себя интегральную схему, имеющую блок BIST, связанный с логическим анализатором, согласно другому примерному варианту осуществления;

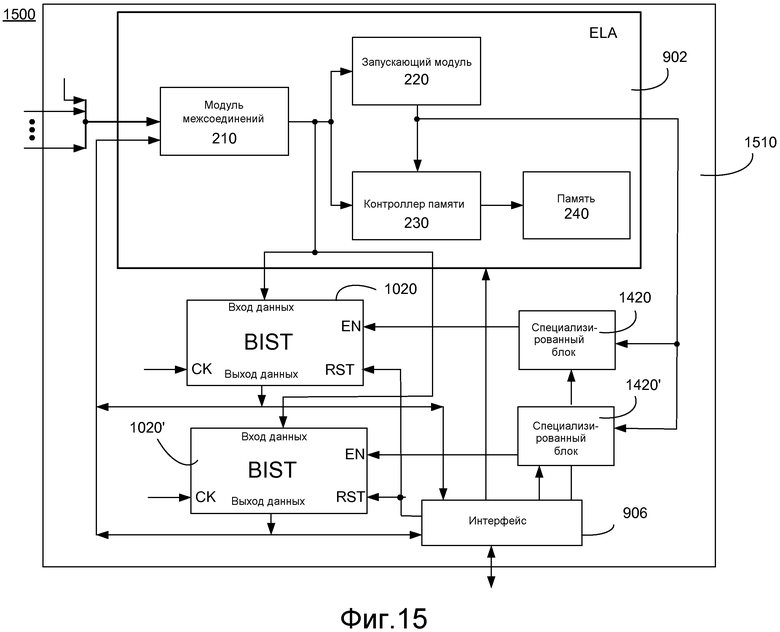

фиг.15 - блок-схема системы, включающей в себя интегральную схему, имеющую блок BIST, связанный с логическим анализатором, согласно другому примерному варианту осуществления; и

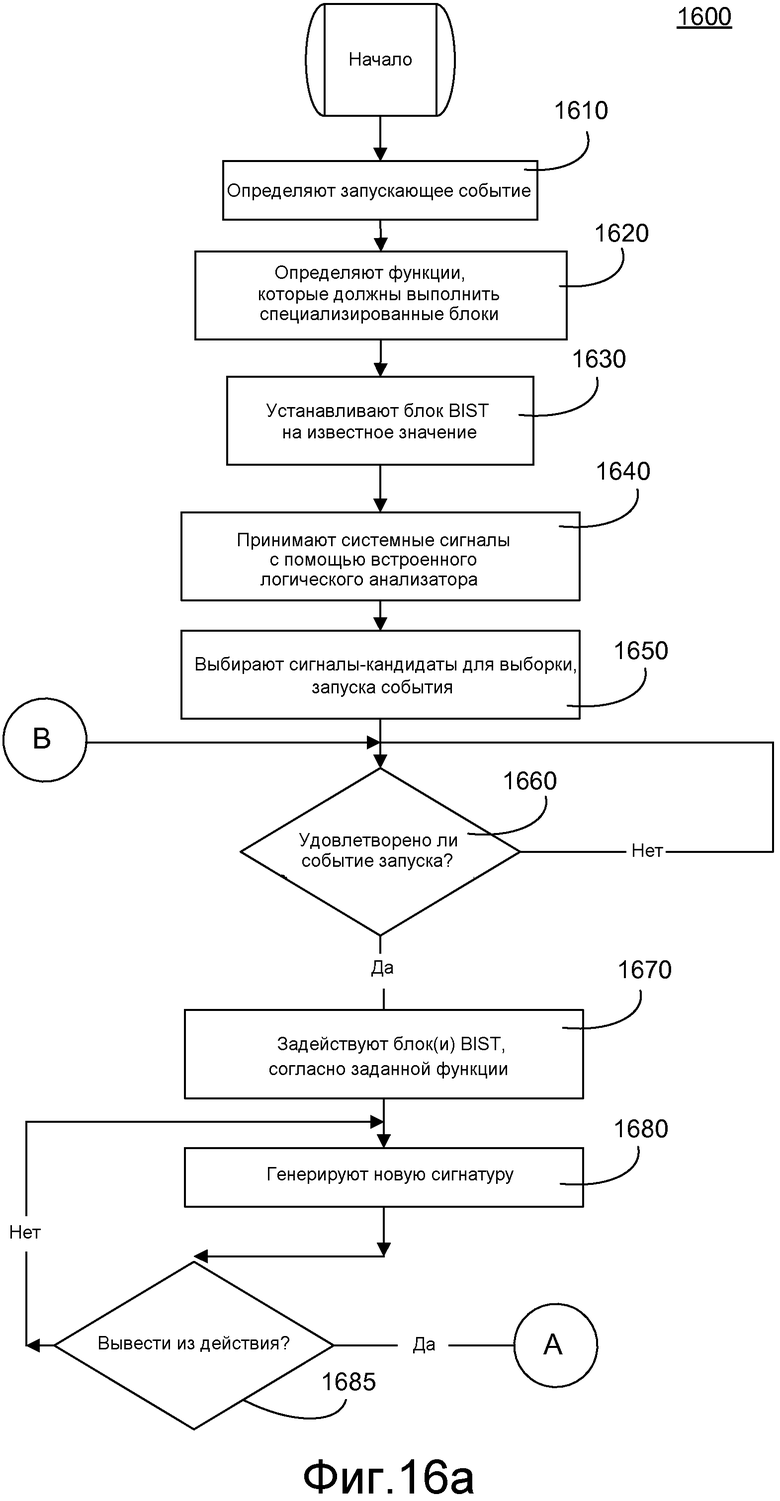

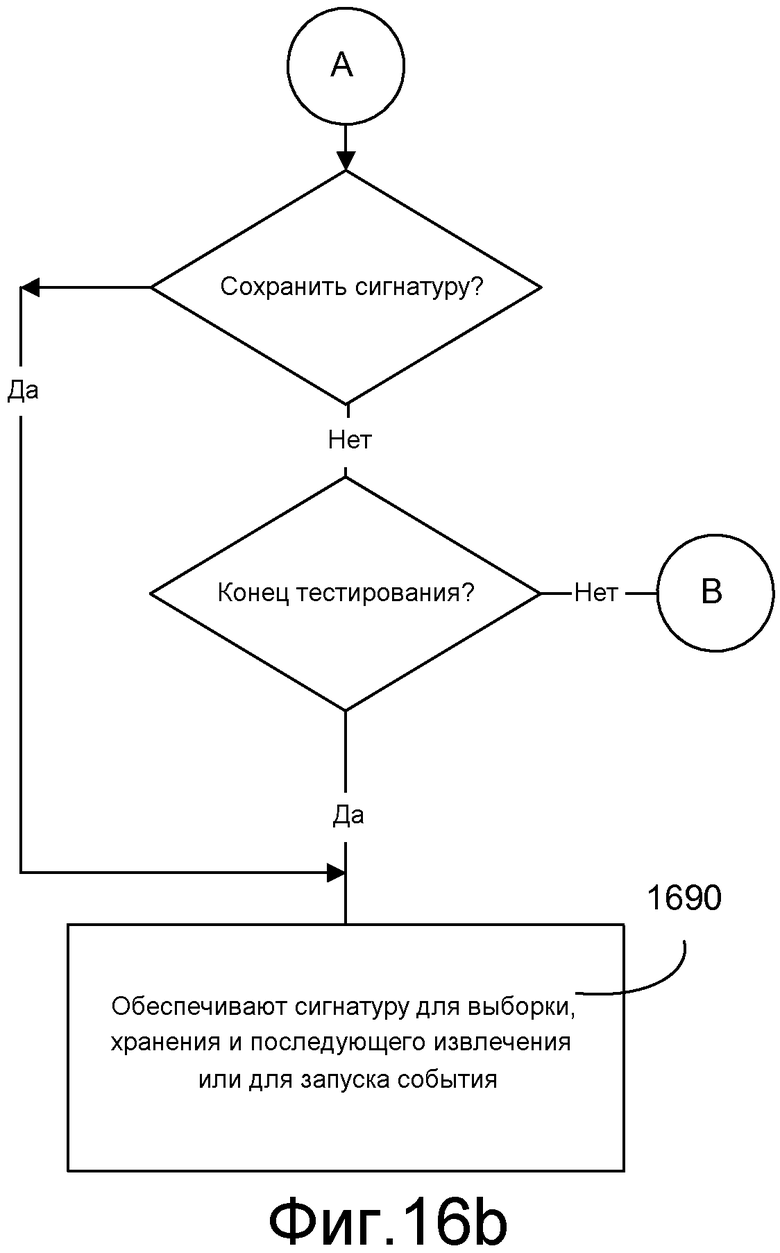

фиг.16а и 16b - блок-схема последовательности операций, иллюстрирующая работу системы на фиг.12, 14 и 15.

ПОДРОБНОЕ ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Теперь будет сделана ссылка на подробное описание примерного варианта осуществления (примерных вариантов осуществления) настоящего изобретения, как изображено на сопроводительных чертежах. Во всех возможных случаях подобные ссылочные позиции будут использоваться везде на чертежах для ссылки на подобные или похожие части.

Настоящее изобретение относится к программируемому встроенному логическому анализатору, включенному в интегральную схему, имеющую расширенные возможности для анализа и отладки. На фиг.2 изображен один вариант осуществления встроенного логического анализатора (ELA) 200, расположенного на интегральной схеме (ИС) 260. ELA 200 включает в себя модуль 200 межсоединений, который является программируемым для выбора по меньшей мере одного из множества сигналов-кандидатов в пределах ИС 260. Множество сигналов-кандидатов, выбранных модулем 210 межсоединений, может включать в себя по меньшей мере один запускающий сигнал и/или один сигнал, который должен быть подвергнуты выборке (то есть выборочный сигнал). Модуль 210 межсоединений маршрутизирует по меньшей мере один запускающий сигнал в запускающий модуль 220. Запускающий модуль 220 обнаруживает, удовлетворяет ли по меньшей мере один запускающий сигнал по меньшей мере одному условию запуска, установленному пользователем. Если удовлетворено условие запуска, то выходной модуль 230 выполняет по меньшей мере одну задачу. Например, выходной модуль 230 может модифицировать по меньшей мере один сигнал в пределах ИС 260.

ИС 260 включает в себя множество шин 265, которые переносят множество сигналов-кандидатов. Множество сигналов включает в себя по меньшей мере один выборочный сигнал и по меньшей мере один запускающий сигнал. Модуль 210 межсоединений принимает множество сигналов из множества шин 265. Модуль 210 межсоединений является программируемым для выбора по меньшей мере одного выборочного сигнала и/или по меньшей мере одного запускающего сигнала из множества принятых сигналов. По существу, модуль 210 межсоединений выбирает выборочный сигнал (выборочные сигналы) и/или запускающий сигнал (запускающие сигналы), установленные пользователем. В одном варианте осуществления, модуль 210 межсоединений может быть мультиплексором.

Модуль 210 межсоединений маршрутизирует запускающий сигнал в запускающий модуль 220. Запускающий модуль 220 является программируемым для установки условия запуска. Условие запуска может быть одной логической операцией (например, простым событием) или рядом логических операций (например, сложная последовательность событий, выполняемая машиной с конечным числом состояний). Запускающий модуль 220 обнаруживает, удовлетворяет ли запускающий сигнал по меньшей мере одному условию запуска. Если удовлетворено условие запуска, то запускающий модуль 220 подает информацию в выходной модуль 230.

Выходной модуль 230 выполняет по меньшей мере одну задачу из группы задач на основании, в ответ на или в результате удовлетворения по меньшей мере одного условия запуска. Группа задач может включать с себя модификацию по меньшей мере одного сигнала из множества принятых сигналов, модификацию по меньшей мере одного условия запуска и инициирование процесса выборки. В одном варианте осуществления, выходной модуль 230 представляет собой программируемую логическую матрицу.

Если выходной модуль 230 инициирует процесс выборки, контроллер 240 выборки начинает выборку выборочного сигнала из модуля 210 межсоединений. Выборочный сигнал, отобранный с помощью контроллера 240 выборки, можно сохранить в памяти 250. Сигналы, сохраненные в памяти 250, можно передать в компьютер (не показан) для анализа. Такая передача сигнала в компьютер может происходить через порт 280 связи, такой как порт USB-порт. Пользователь в дальнейшем может анализировать сигналы, переданные в компьютер.

Хотя на фиг.2 показано, что память 250 находится в ELA 200, специалисты в данной области техники смогут оценить, что память может представлять собой отдельный компонент на интегральной схеме 260 в другом варианте осуществления. В еще одном варианте осуществления, память может располагаться отдельно от интегральной схемы 260 при условии, что она остается коммуникативно связанной с ELA. После анализа этих сигналов по меньшей мере одно действие внутри устройства 300, включающего в себя ИС 260, как показано на фиг.3, можно выполнить путем конфигурирования или программирования выходного модуля 230 для выполнения конкретной задачи на основании анализа. Например, пользователь может отладить ошибку или неисправность или исправить действие компонента устройства 300. Поэтому устройство 300 может быть диагностировано более эффективно, чтобы обеспечить правильное функционирование устройства 300. В одном варианте осуществления, устройство 300 может быть устройством формирования изображения, таким как принтер, сканер или многофункциональное устройство, которое позволяет печатать, сканировать, использовать факсимильную связь или копировать.

Выходной модуль 230 можно запрограммировать или выполнить с возможностью модификации по меньшей мере одного сигнала на основании, в ответ на или в результате удовлетворенного условия запуска. Если удовлетворенное условие запуска показывает ошибку, выходной модуль 230 может модифицировать по меньшей мере один сигнал из множества сигналов, принятых с помощью ELA 200 для исправления указанной ошибки. Например, если значение сигнала 'X' должно быть равным 30 для безошибочной работы устройства 300, и если не удовлетворено условие запуска X≠30, выходной модуль 230 модифицирует значение сигнала Х до доведения значения сигнала до 30 для безошибочной работы устройства 300.

Выходной модуль 230 может также инструктировать контроллер 270, который показан (на фиг.2), для модификации по меньшей мере одного сигнала из множества сигналов, принятых ELA 200 для исправления указанной ошибки. Например, выходной модуль 230 может инструктировать контроллеры 270 для выключения широтно-импульсного модулятора (ШИМ), если обнаружено, что ШИМ, который регулирует скорость вращения двигателя, завис, таким образом предотвращая повреждение двигателя. Выходной модуль 230 может также остановить операцию прямого доступа к памяти (DMA). Кроме этого, выходной модуль 230 может модифицировать, при необходимости, условие запуска. Эти возможности выходного модуля 230 значительно повышают эффективность отладки ELA 200. Поэтому ELA 200 обычно выполняет код, приведенный ниже:

IF (<CONDITION>) THEN (<ACTION(S)>) (IF (<условие>) THEN (<действие(я)>)),

где ACTION(S) - по меньшей мере любое одно из вышеупомянутых действий, которое выполняет выходной модуль или контроллер, и CONDITION - условие запуска, которое устанавливает пользователь.

В одном варианте осуществления, как показано на фиг.4, ИС 260 включает в себя устройство 400 доступа к сети. Устройство 400 доступа к сети коммуникативно связано с ELA 200 и соединено с удаленным хостом 410 непосредственно или через сеть. Это соединение может включать в себя проводное соединение и/или беспроводное соединение, и сеть может представлять собой Интернет, локальную сеть, глобальную сеть или городскую сеть. Удаленный хост 410 позволяет запрограммировать ELA 200 в ИС 260. Удаленный хост 410 позволяет также анализировать выборочные сигналы, сохраненные в памяти. Удаленный хост 410 осуществляет доступ к ELA 200 через устройство 400 доступа к сети.

ELA 200 можно запрограммировать на автоматическое или периодическое отправление сохраненных выборочных сигналов в удаленный хост 410 для анализа. Например, ELA 200, встроенный в принтер, можно запрограммировать на автоматическую и периодическую передачу сигнала кодера в удаленный хост 410. Сигнал кодера показывает вращение двигателя внутри принтера. Если определено, что сигналы кодера затухают или переходят в плохое состояние, удаленный пользователь может предоставить инструкцию для технического обслуживания принтера. В одном варианте осуществления ELA 200 на передачу сохраненных сигналов данных в удаленный хост 410, если такая инструкция или команда была принята из удаленного хоста 410.

В другом варианте осуществления, как показано на фиг.5, ИС 260 включает в себя центральное процессорное устройство (ЦПУ) 500. ЦПУ 500 подает множество сигналов данных в ELA 200. Сигналы данных могут представлять собой сигналы аппаратных средств, программного обеспечения или программно-аппаратных средств. Сигналы данных подаются из ЦПУ 500 в ELA 200 через интерфейс. Интерфейс коммуникативно связан с ЦПУ 500 и ELA 200. Интерфейс включает в себя носитель 510 данных и множество линий (1-n) связи. Множество линий связи коммуникативно связаны с ЦПУ 500 и носителем 510 данных. Множество линий (1-n) связи выполнено с возможностью подачи множества сигналов данных из ЦПУ 500 в носитель 510 данных. Носитель 510 данных выполнен с возможностью хранения множества сигналов данных.

Каждый сигнал данных из множества сигналов данных связан с полем данных и полем адреса. Поле данных предусматривает значение сигнала данных, которое необходимо сохранить, и поле адреса точно определяет местоположение в носителе 10 данных, где хранится сигнал данных. Носитель 510 данных включает в себя множество ячеек памяти. Каждая из множества ячеек памяти имеет уникальный адрес. Множество сигналов данных, которые хранятся на носителе 500 данных, подается через модуль 200 межсоединений через множество шин на ИС 260. По существу, носитель 510 данных находится в электрическом сообщении с множеством шин на ИС 260 для подачи сохраненных сигналов данных в модуль 210 межсоединений.

Сохраненные сигналы данных, поданные в модуль 210 межсоединений, включают в себя сигналы данных аппаратных средств, программного обеспечения и/или программно-аппаратных средств. Сигналы данных включают в себя множество выборочных сигналов и по меньшей мере один запускающий сигнал. Модуль 210 межсоединений выбирает множество выборочных сигналов и по меньшей мере один запускающий сигнал из множества принятых сигналов данных. Запускающий сигнал подается в запускающий модуль 220. Запускающий модуль 220 обнаруживает, удовлетворяет ли запускающий сигнал по меньшей мере одному условию запуска. Если удовлетворено условие запуска, то контроллер 240 выборки осуществляет выборку множества выборочных сигналов из модуля 210 межсоединений. Множество выборочных сигналов сохраняется в памяти 250. Множество сохраненных сигналов наряду с другими сохраненными сигналами передаются в компьютер для анализа. Поэтому сигналы программного обеспечения, аппаратных средств и/или программно-аппаратных средств можно анализировать одновременно на компьютере.

В другом варианте осуществления, как показано на фиг.6, интерфейс, то есть множество линий (1-n) связи и носитель 510 данных расположены на ИС 600. ИС 600 включает в себя ELA 100 (фиг.1) и ЦПУ 610. ЦПУ 610 подает множество сигналов данных в ELA 100. Множество сигналов данных включает в себя по меньшей мере один сигнал данных программного обеспечения или программно-аппаратных средств. Множество сигналов данных подается из ЦПУ 610 в ELA 100 через множество линий (1-n) связи и носитель 510 данных. Множество линий (1-n) связи выполнено с возможностью подачи множества сигналов данных из ЦПУ 610 в носитель 510 данных. Носитель 510 данных выполнен с возможностью сохранения множества сигналов данных. Сигналы данных, сохраненные на носителе 510 данных, подаются в модуль 110 межсоединений через множество шин на ИС 600. По существу, носитель 510 данных находится в электрическом сообщении с множеством шин ИС 600 для подачи сохраненных сигналов данных в модуль 110 межсоединений.

В еще одном варианте осуществления, как показано на фиг.7, ELA 100 расположен на ИС 700, который включает в себя процессор 710. Процессор 710 принимает множество сигналов из множества шин на ИС 700. Такие сигналы могут представлять собой любую комбинацию сигналов аппаратных средств, программного обеспечения и/или программно-аппаратных средств (показанных стрелкой А) внутри ИС 700. Процессор 710 коммуникативно связан с ELA 100, размещенным на ИС 700. Более конкретно, процессор 700 может быть коммуникативно связан с запускающим модулем 120 ELA 100.

В альтернативном варианте осуществления, ИС 700 может быть коммуникативно связана с ELA 200 (фиг.2). В этом варианте осуществления, процессор 700 принимает по меньшей мере один запускающий сигнал из запускающего модуля 220 для обнаружения, удовлетворено ли по меньшей мере одно условие запуска. Если удовлетворено по меньшей мере одно условие запуска, процессор 700 модифицирует по меньшей мере один сигнал из множества сигналов данных, принятых с помощью процессора 710. Процессор 710 также является программируемым для модификации по меньшей мере одного условия запуска в запускающем модуле 220, когда удовлетворено по меньшей мере одно условие запуска. Процессор 710 возможно программировать через интерфейс 720, предусмотренный на ИС 700.

ИС 700 может включать в себя устройство 400 доступа к сети. Устройство 400 доступа к сети коммуникативно связывает ИС 700 с удаленным хостом 410. Удаленный хост 410 может программировать ELA 100, расположенный на ИС 700. Удаленный хост 410 может также анализировать выборочные сигналы, сохраненные в ELA 100. Поэтому удаленный хост 410 может диагностировать устройство 730, включающее в себя ELA 100, и устройство 400 доступа к сети.

На фиг.8 изображена блок-схема последовательности операций, иллюстрирующая способ захвата сигналов программного обеспечения или событий внутри ИС 260. На этапе ЦПУ 500, расположенное на ИС 260, подает множество сигналов программного обеспечения на носитель 510 данных. Носитель данных выполнен с возможностью хранения множества сигналов программного обеспечения (этап 805). На этапе 810, носитель 510 данных отправляет сигналы сохраненного программного обеспечения в модуль 210 межсоединений ELA 200. Модуль 210 межсоединений запрограммирован на выбор множества сигналов программного обеспечения, которые должны быть подвергнуты выборке, из множества принятых сигналов программного обеспечения (этап 815). Модуль 210 межсоединений также запрограммирован на выбор по меньшей мере одного запускающего сигнала программного обеспечения из множества принятых сигналов программного обеспечения (этап 820). Пользователь устанавливает в запускающем модуле 220 по меньшей мере одно условие запуска для события программного обеспечения (этап 825). Запускающий модуль 220 обнаруживает, удовлетворено ли установленное условие запуска с помощью по меньшей мере одного сигнала запуска программного обеспечения (этап 830). Если удовлетворено условие запуска, то запускающий модуль 220 инициирует процесс выборки на этапе 835. В противном случае, запускающий модуль повторяет обнаружение удовлетворенного установленного условия запуска.

После инициирования процесса выборки, контроллер 240 выборки осуществляет выборку множества сигналов программного обеспечения, которые должны быть подвергнуты выборке, из модуля 210 межсоединений (этап 840). Выборочные сигналы программного обеспечения можно затем сохранить в памяти 250 на этапе 845. Сигналы сохраненного программного обеспечения можно также передать в компьютер для анализа с помощью запуска программы на компьютере или с помощью пользователя.

Специалисты в данной области техники могут оценить, что настоящее изобретение не ограничено сигналами программного обеспечения. Напротив, другие сигналы, такие как сигналы аппаратных средств и программно-аппаратных средств, можно захватывать вместо и/или совместно с сигналами программного обеспечения.

На фиг.9 изображена интегральная схема 900 системы, согласно другому варианту осуществления настоящего изобретения. Интегральную схему 900 можно расположить в системе 905, имеющей множество модулей М. Интегральная схема 900 может включать в себя встроенный логический анализатор 902, имеющий модуль 210 межсоединений, запускающий модуль 220, контроллер 240 памяти и память 250, как описано выше. Встроенный логический анализатор 902 может быть связан с системными модулями М таким образом, чтобы можно было использовать встроенный логический анализатор 902 для эффективного тестирования или отладки системы 905, в котором она расположена.

Кроме того, следует понимать, что фразы "тестирование" и "отладка" предназначены для того, чтобы включать в себя эти операции, которые обычно выполняются во время разработки, тестирования, отладки анализа системы и контроля по месту эксплуатации и обслуживания системы и ее системных модулей М, и не предназначены для ограничения только одной фразой или периодом времени активности системы от проектирования до используемого срока службы системы.

Интегральная схема 900 может также включать в себя специализированный блок 904, который принимает один или более сигналов, связанный со встроенным логическим анализатором 902. В частности, специализированный блок 904 может принимать в качестве входного сигнала один или более сигналов, поданных во встроенный логический анализатор 902 из других модулей М системы. Такие сигналы могут включать в себя сигналы, которые имеются в наличие для выборки или запуска события с помощью встроенного логического анализатора 902. Специализированный блок 904 может генерировать на своем выходе один или более выходных сигналов, которые основаны на одном или более принятых входных сигналах и которые подаются обратно во встроенный логический анализатор 902 для выборки или запуска. За счет подачи во встроенный логический анализатор 902 одного или более дополнительных сигналов для выборки и/или запуска события, которое основано на сигналах, связанных со встроенным логическим анализатором 902, встроенный логический анализатор 902 позволяет более эффективно отладить систему, в которой расположена интегральная схема 900.

Специализированный блок 904 может включать в себя схему, которая является специальной для конкретной системы и/или системных модулей М, которые доступны для тестирования и/или отладки с использованием встроенного логического анализатора 902. В примерном варианте осуществления настоящего изобретения специализированный блок 904 выполнен таким образом, чтобы сигналы, сгенерированные таким образом можно было сконфигурировать. Наличие специализированного блока 904, выполненного предпочтительным образом, позволяет обеспечить существенную гибкость для тестирования и/или отладки большого разнообразия системных модулей М и системных сигналов, сгенерированных таким образом. Специализированный блок 904 можно реализовать в виде FPGA или CPLD. Альтернативно, специализированный блок 904 можно реализовать с помощью процессора, имеющего память, связанную с ним, для хранения кода, который исполняет процессор. При наличии памяти, доступной для загрузки другого кода, специализированный блок 904 может обеспечить достаточную гибкость для тестирования и/или отладки по существу большого числа различных системных модулей М. В еще одном альтернативном варианте, специализированный блок 904 может включать в себя схему машины состояний, которая программируется частично путем программирования и/или хранения информации в регистрах, которые расположены в или связаны с машиной состояний. Следует понимать, что специализированный блок 904 можно реализовать большим количеством способов для обеспечения конфигурируемых функциональных возможностей и генерации сигнала.

Как показано на фиг.9, специализированный блок 904 может принимать один или более сигналов, которые подаются во встроенный логический анализатор 902. Такие сигналы, которые подаются во встроенный логический анализатор 902, можно принимать с помощью специализированного блока 904 путем прямого соединения одного или более входов специализированного блока 904 с одним или более входами встроенного логического анализатора 902. В дополнение или альтернативно, такие сигналы, поданные во встроенный логический анализатор, можно принимать с помощью специализированного блока 904 путем непосредственного соединения одного или более входов специализированного блока 904 с одним или более выходов модуля 210 межсоединений, которые должны запускать событие, и/или должны быть подвергнуты выборке, как показано пунктирными линиями на фиг.9. Как дополнительно показано на фиг.9, выход специализированного блока 904 позволяет обеспечить во встроенном логическом анализаторе 902 один или более выходных сигналов для запуска события или выборки. Такие, один или более выходных сигналов можно подать во встроенный логический анализатор 902 путем прямого соединения выхода специализированного блока 904 с входом встроенного логического анализатора 902. В дополнение или альтернативно, такие один или более выходных сигналов можно подать во встроенный логический анализатор 902 путем прямого соединения выхода специализированного блока 904 с входом запускающего модуля 920 и/или с входом контроллера 240 памяти, как показано пунктирными линиями на фиг.9.

Интегральная схема 900 может дополнительно включать в себя интерфейс 906, который можно использовать для осуществления доступа к специализированному блоку 904 и встроенному логическому анализатору 902. В частности, интерфейс 906 может обеспечивать проводное или беспроводное соединение с сетевым устройством по сети, таким как удаленный хост (не показан). Интерфейс 906 может обеспечить необходимый интерфейс между сетевым устройством и различными блоками в интегральной схеме 900, включающей в себя встроенный логический анализатор 902 и специализированный блок 904. Встроенным логическим анализатором 902, и, в частности, модулем 210 межсоединений, и запускающим модулем 220 можно управлять, конфигурировать и/или программировать с использованием интерфейса 906. Кроме этого, данные, подвергнутые выборке с помощью встроенного логического анализатора 902, можно загрузить в сетевое устройство для анализа через интерфейс 906.

Как упомянуто выше, доступ к специализированному блоку 904 можно осуществить с использованием интерфейса 906. Например, если специализированный блок 904 является реконфигурируемым и/или программируемым, то специализированный блок 904 можно сконфигурировать с помощью сетевого устройства с использованием интерфейса 906 для генерации одного или более выходных сигналов специально для тестируемых или отлаживаемых конкретных системных модулей М. В дополнение или в качестве альтернативы, специализированным блоком 904 можно управлять с помощью удаленного хоста во время тестирования или отладки системы с использованием интерфейса 906. В результате, специализированный блок 904 можно сконфигурировать во время выполнения сеанса тестирования или отладки на уровне системы.

На фиг.9 показан специализированный блок 904 отдельно от встроенного логического анализатора 902 в интегральной схеме 900. Понятно, что, альтернативно, специализированный блок 904 может быть расположен во встроенном логическом анализаторе 902 в интегральной схеме 900 и соединен с модулем 210 межсоединений, запускающим модулем 220 и контроллером 240 памяти, как описано выше.

На фиг.10 изображена интегральная схема 910 системы 905, согласно другому примерному варианту осуществления настоящего изобретения. Интегральная схема 910 может включать в себя встроенный логический анализатор 902, как описано выше в отношении фиг.9, имеющий модуль 210 межсоединений, запускающий модуль 220, контроллер 240 памяти и память 250. Интегральная схема 910 может также включать в себя специализированный блок 220 для генерации одного или более сигналов для выборки или запуска события с помощью встроенного логического анализатора 902 на основании сигналов, поданных в и/или сгенерированных внутри встроенного логического анализатора 902.

Подобно специализированному блоку 904, показанному на фиг.9, специализированный блок 920 соединен со встроенным логическим анализатором 902 для приема в качестве входного сигнала одного или более сигналов, поданных во встроенный логический анализатор 902. Специализированный блок 920, подобно специализированному блоку 904, может генерировать один или более выходных сигналов на основании одного или более принятых входных сигналов, которые подаются во встроенный логический анализатор 902, запускающий модуль 220 (для запуска события) и/или контроллер 940 памяти для избирательной выборки. Подобно специализированному блоку 904, специализированный блок 920 может включать в себя схему, которая является специальной для системных модулей М, которые можно тестировать или отлаживать с помощью встроенного логического анализатора 902. В одном варианте осуществления, функции, выполняемые специализированным блоком 920 при генерации одного или более выходных сигналов, можно сконфигурировать или запрограммировать с использованием схемы FPGA или CPLD, процессора, исполняющего загруженный код тестирования/отладки, схемы машины состояний и т.д. Интерфейс 906 может быть соединен со специализированным блоком 920 для обеспечения доступа к нему для того, чтобы специализированным блоком можно было управлять, конфигурировать и/или программировать, используя сетевое устройство, такое как хост-устройство.

Кроме того, специализированный блок 920 может принимать в качестве входного сигнала один или более сигналов, сгенерированных запускающим модулем 220. В частности, один или более запускающих сигналов, сгенерированных запускающим модулем 220, который указывает на обнаружение по меньшей мере одного события, можно подать в качестве входного сигнала в специализированный блок 220. Один или более выходных сигналов, сгенерированных специализированным блоком 220, могут быть основаны на одном или более запускающих сигналах, сгенерированных запускающим модулем 220. Таким образом, выходной сигнал, сгенерированный специализированным блоком 920, можно задать на основании сигналов, сгенерированных системными модулями М при тестировании и/или отладке, а также действий, которые заданы или выполняются во время сеанса тестирования или отладки.

Например, запускающий сигнал, сгенерированный с помощью запускающего модуля 220 встроенного логического анализатора 902 и поданный в специализированный блок 920, можно использовать для избирательного задействования схемы генерации сигналов внутри специализированного блока 920. В одной реализации, специализированный блок 920 можно сконфигурировать в виде накопителя для подсчета числа событий, таких как число слов, считанных из памяти с помощью модуля системы с прямым доступом к памяти (DMA). При тестировании или отладке, система выбирает модуль DMA для контроля и управляет, программирует и/или конфигурирует запускающий модуль 220, соответственно, с использованием интерфейса 906. Запускающая программа, с помощью которой запускающий модуль 220 сконфигурирован, может включать в себя действие для запуска накопления. После обнаружения условия одного или более сигналов, поданных в запускающий модуль 220, запускающий сигнал, сгенерированный с помощью запускающего модуля 220, указывает на обнаружение условия и задействует накопитель, сконфигурированный внутри специализированного блока 920, для начала накопления синхронно с тактовым сигналом (не показано). Запускающий модуль 220 может также, либо с помощью того же самого запускающего сигнала, используемого для задействования накопителя, либо другого запускающего сигнала, вывести из действия накопитель после его задействования. Сигнал, используемый для вывода из действия, может быть запущен схемой, которая является конфигурируемой и/или программируемой и обнаруживает возникновение по меньшей мере одного запускающего события, относящегося к одному или более сигналам, принятым запускающим модулем 220. После вывода из действия, выходной сигнал накопителя можно подать на вход встроенного логического анализатора 902 для избирательной выборки с помощью контроллера 240 памяти или запуска события с помощью запускающего модуля 220. За счет управления функционированием накопителя внутри специализированного блока 920 для накопления только после возникновения запускающего события, особого для пользователя, и подачи накопленного результата во встроенный логический анализатор 902, по существу, для хранения выборок выходного сигнала функционирования накопителя необходимо меньше памяти, чем было бы необходимо для того, чтобы подсчитать число слов, считанных с помощью системного модуля DMA.

Понятно, что специализированные блоки 904 и 920 можно использовать в виде одного и того же кристалла интегральной схемы. На фиг.11 изображена такая интегральная схема 940 системы 905 системы 905, согласно примерному варианту осуществления настоящего изобретения, включающего в себя оба специализированных блока 904 и 920.

Понятно, что интегральные схемы 900, 910 и 940 можно использовать практически в любой системе, которая позволяет извлечь пользу из встроенного механизма для облегчения эффективного тестирования и отладки системы и его системных модулей М. Например, принтер, печатающее устройство "все в одном" или многофункциональный принтер может включать в себя интегральную схему 900.

Использование специализированных блоков 904 и 920 показало существенное уменьшение объема памяти, необходимого для хранения сигналов, подвергнутых выборке с помощью логического анализатора 902. Например, принтер, или другое устройство формирования изображения, может включать в себя последовательный интерфейс для подачи в печатающую головку принтера данных печати для полноценной работы печати, которая может потребовать гигабайты памяти. Если требуется узнать, сколько раз срабатывает конкретное сопло печатающей головки, специализированный блок 904 или 920 можно выполнить с возможностью приема сигнала из последовательного интерфейса и генерировать сигнал, показывающий конкретное количество срабатываний сопла без какой-либо информации, относящейся к любому другому соплу головки. Сгенерированный сигнал можно поддать в качестве входного сигнала во встроенный логический анализатор 902 для избирательной выборки во время сеанса тестирования/отладки. Обнаружено, что выборка и хранение в памяти специально сгенерированного сигнала, занимает только килобайты памяти, что существенно меньше, чем объем памяти, необходимый для выборки и хранения всего последовательного интерфейса.

На фиг.12 изображена блок-схема интегральной схемы 1010 в системе 1000, согласно другому варианту осуществления. Интегральная схема может включать в себя встроенный логический анализатор 902, имеющий модуль 210 межсоединений, запускающий модуль 220, контроллер 240 памяти и память 250, коммуникативно связанные вместе, как описано выше. Встроенный логический анализатор 902 может принимать сигналы, сгенерированные с помощью системных модулей, появляющихся в системе 1000. Интегральная схема 1010 может дополнительно включать в себя блок 1020 со встроенным самотестированием (BIST), соединенный со встроенным логическим анализатором 902. В общих чертах, блок 1020 BIST имеет сигнатуру, сохраненную в нем, и создает новую сигнатуру путем захвата сигнала и установки сигналов в конкретные периоды времени, как определено статусом разрешающего входного сигнала или тактового сигнала. Таким образом, новая сигнатура основана на ранее сохраненной сигнатуре, а также на захваченных сигналах. За счет захвата сигналов, связанных со встроенным логическим анализатором 902, многочисленное число раз на всем протяжении процедуры теста или отладки, например, сигнатура, которая хранится в блоке 1020 BIST, может показывать, работает ли правильно система во время тестирования посредством простого сравнения сохраненной сигнатуры с ожидаемым значением.

Как показано на фиг.12, блок 1020 BIST можно соединить со встроенным логическим анализатором 902 для приема в качестве входных сигналов данных одного или более сигналов, принятых таким образом. Например, вход данных блока 1020 BIST можно соединить с одним или более выходами модуля 210 межсоединений для приема там одного или более сигналов. Блок 1020 BIST может включать в себя разрешающий вход для избирательного разрешения захвата сигналов, появляющихся на его входе данных, таким образом, создавая новую сигнатуру. Предполагается, что при возникновении сигнала на разрешающем входе, сигналы, возникающие на входе данных блока 1020 BIST, захватываются, и генерируется новая сигнатура после появления каждого запускающего фронта сигнала, возникающего на тактовом входе блока 1020 BIST. Разрешающий вход блока 1020 BIST можно соединить с выходом запускающего модуля 220 для приема из него по меньшей мере одного сигнала. Таким образом, после обнаружения по меньшей мере одного события с помощью запускающего модуля 220, блок 1020 BIST захватывает набор одного или более сигналов, появляющихся на его входе данных и, таким образом, генерирует новую сигнатуру с помощью каждого запускающего фронта, принятого тактового сигнала. На тактовый вход блока 1020 BIST для управления захватом сигнала и генерацией новой сигнатуры, можно подавать системный тактовый сигнал или тестовый тактовый сигнал, используемый для синхронизации операций внутри встроенного логического анализатора 202, например.

После задействования блока 1020 BIST, запускающий модуль 220 может генерировать сигнал, который подается в блок 1020 BIST для его вывода из действия. В частности, запускающий модуль 220 можно сконфигурировать или, с другой стороны, запрограммировать на вывод из действия блока 1020 BIST после его задействования. Например, запускающий модуль 220 может вывести из действия блок 1020 BIST в ответ на обнаружение запускающего события, которое основано на одном или более сигналах, принятых с помощью запускающего модуля 220. В частности, запускающее событие можно сконфигурировать или запрограммировать во время сеанса тестирования или отладки, аналогично любому другому запускающему событию, контролируемому запускающим модулем 220. Запускающее событие для вывода из действия блока 1020 BIST, например, может быть основано частично на предопределенном периоде времени, истекшим после его задействования, где предопределенный период времени сконфигурирован или иным способом запрограммирован во время выполнения. Тем не менее понятно, что запускающее событие может быть основано на любом числе функций или операций, заданных в запускающем модуле 220 и, таким образом, после приема одного или более сигналов.

Сохраненную сигнатуру блока 1020 BIST можно обеспечить на его выходе данных, который может быть соединен со встроенным логическим анализатором 902 для запуска события или хранения в нем. Например, выход данных блока 1020 BIST можно соединить с входом встроенного логического анализатора 202 таким образом, чтобы выход данных был соединен с входом модуля 210 межсоединений. В дополнение или в качестве альтернативы выход данных блока 1020 BIST может быть непосредственно соединен с входом запускающего модуля 220 и/или контроллера 240 памяти. В результате, сигнатуру, которая поддерживается в блоке 1020 BIST, можно использовать с помощью встроенного логического анализатора 902 в качестве любого другого сигнала, связанного с ним.

Блок 1020 BIST можно соединить с интерфейсом 906 для обеспечения прямого пользовательского доступа к сохраненной сигнатуре, как показано на фиг.12. Интерфейс 906, подсоединенный к блоку 1020 BIST, позволяет также относительно легко установить блок 1020 BIST в заданное состояние, как будет объяснено более подробно ниже.

На фиг.13 изображена одна возможная реализация блока 1020 BIST. Блок 1020 BIST может включать в себя ряд последовательно соединенных секционированных микропроцессоров 1300, которые объединены для того, чтобы служить в качестве сдвигового регистра с линейной обратной связью. В частности, каждый секционный микропроцессор 1300 может включать в себя защелку, такую как D-триггер 1310, имеющий вход данных, тактовый вход, вход сброса, тактовый разрешающий вход и выход данных. Вход тактового сигнала каждого триггера 1310 можно соединить вместе с одинаковым входом блока 1020 BIST, и вход разрешающего тактового сигнала каждого триггера 1310 можно соединить вместе с одинаковым входом блока 1020 BIST, как показано на фиг.13. В результате, триггеры 1310 блока 1020 BIST можно тактировать и задействовать с помощью одних и тех же сигналов.

Каждый секционированный микропроцессор 1300 может дополнительно включать в себя по меньшей мере один логический вентиль 1320, такой как логический вентиль, выполняющий операцию "исключающего ИЛИ", имеющий первый вход, соединенный с выходом данных блока 1020 BIST, второй вход и выход, который соединен с выходом данных триггера 1310. Выход данных триггера 1310 можно соединить с входом следующего триггера 1310 в виде последовательной цепочки сдвиговых регистров через второй вход логического вентиля 1320 в следующем триггере 1310, как показано на фиг.13. Кроме того, второй вход логического вентиля 1320 в первом и/или самом верхнем по потоку в секционированном микропроцессоре 1300 в последовательной цепочке сдвиговых регистров можно соединить с одним или более выходов данных триггеров 1310 секционированных микропроцессоров 1300 в виде последовательной цепочки сдвиговых регистров через логический вентиль 1330 (вентиль, выполняющий операцию исключающего ИЛИ). Выход данных каждого триггера 1310 секционированных микропроцессоров 1300 можно соединить с выходом данных блока 1020 BIST.

Например, в начале сеанса тестирования или отладки желательно установить триггеры 1310 в известное, заданное состояние. Соответственно блок 1020 BIST может включать в себя вход сброса, который соединен с входом сброса каждого триггера 1310, логическое выражение которого устанавливает триггеры 1310 в заданное состояние или состояние сброса. Понятно, что все триггеры 1310 могут иметь одинаковое булево состояние в качестве заданного состояния или состояния сброса, или что некоторые триггеры 1310 могут иметь первое булево состояние в качестве заданного состояния, тогда как другие триггеры 1310 могут иметь второе булево состояние в качестве заданного состояния. Вход сброса блока 1020 BIST можно соединить с интерфейсом 906 таким образом, чтобы триггеры 1310 можно было относительно легко установить в заданное состояние.

Понятно, что блок 1020 BIST, и, более конкретно, секционированные микропроцессоры 1300 можно реализовать любым количеством способов, выполняя при этом роль сдвигового регистра с линейной обратной связью или т.п. для создания сигнатуры на основании ранее поддерживаемой сигнатуры и на основании сигналов, захваченных после появления каждого запускающего фронта тактового сигнала.

На фиг.14 изображена блок-схема системы 1400, согласно другому варианту осуществления. Система 1400 может включать в себя интегральную схему 1410, имеющую встроенный логический анализатор 902, который может включать в себя модуль 210 межсоединений, запускающий модуль 220, контроллер 240 памяти и память 250, как описано выше, и принимать сигналы из различных системных модулей для тестирования или отладки. Кроме этого, интегральная схема 1410 может включать в себя блок 1020 BIST, как описано выше в отношении фиг.13, имеющий вход данных и выход данных, соединенный со встроенным логическим анализатором 902, а также разрешающий вход. Интерфейс 906 можно соединить со встроенным логическим анализатором 902 и блоком 1020 BIST для обеспечения пользовательского доступа к нему. Кроме этого, интегральная схема 1410 может включать в себя специализированный блок 1420.

Специализированный блок 1420 можно подсоединить между запускающим модулем 220 встроенного логического анализатора 902 и блоком 1020 BIST. В частности, специализированный блок 1420 может включать в себя вход, соединенный по меньшей мере с одним выходом запускающего модуля 220, и выходом, соединенным с разрешающим входом блока 1020 BIST. Специализированный блок 1420 позволяет генерировать по меньшей мере один сигнал на своем выходе, который основан на обнаружении по меньшей мере одного запускающего события с помощью запускающего модуля 220.

Аналогично специализированному модулю 920, специализированный блок 1420 может включать в себя схему, которая является специальной для системных модулей М, которые может тестировать и отлаживать встроенный логический анализатор 902. В одном варианте осуществления, функции, выполняемые специализированным блоком 1420 при генерации одного или более выходных сигналов можно сконфигурировать и/или запрограммировать с использованием схемы FPGA или CPLD, процессора, исполняющего загруженный код тестирования/отладки, схемы машины состояний и т.д. Интерфейс 906 можно соединить со специализированным блоком 1420 для выполнения доступа к нему таким образом, чтобы специализированным блоком 1420 можно было управлять, конфигурировать и/или программировать с использованием сетевого устройства, такого как хост-устройство.

Как упомянуто выше, специализированный блок 1420 может принимать в качестве входного сигнала один или более сигналов, сгенерированных запускающим модулем 220. В частности, один или более запускающих сигналов, сгенерированных запускающим модулем 220, который указывает на обнаружение по меньшей мере одного события, можно подать в качестве входного сигнала в специализированный блок 1420. Один или более выходных сигналов, сгенерированных специализированным блоком 1420 и поданных в блок 1020 BIST, могут быть, таким образом, основаны на одном или более запускающих сигналах, сгенерированных запускающим модулем 220, а также функциях, которые сконфигурированы и/или запрограммированы в специализированном блоке 1420. Таким образом, выходной сигнал, сгенерированный специализированным блоком 1420, который избирательно задействует блок 1020 BIST, можно задать на основании сигналов, сгенерированных системными модулями М во время тестирования или отладки, а также действий и функций, которые заданы и выполняются во время сеанса тестирования или отладки.

Один или более выходных сигналов, сгенерированных специализированным блоком 1420, которые задействуют блок 1020 BIST, могут также служить для выведения из действия блока 1020 BIST. Такие один или более сигналов могут выводить из действия блок 1020 BIST на основании обнаружения одного или более запускающих событий с помощью запускающего модуля 220 и/или на основании заданной функции, заданной в специализированном блоке 1420. Заданная функция, которую можно сконфигурировать или иным способом запрограммировать во время сеанса тестирования или отладки, может включать в себя функцию таймера, который выводит из действия блок 1020 BIST в заданный период времени после его задействования. Тем не менее, понятно, что сигнал, который выводит из действия блок 1020 BIST, может быть основан практически на любой заданной функции, заданной в специализированном блоке 1420.

Кроме того, понятно, что интегральные схемы 1010 и 1410 могут включать в себя более чем один блок 1020 BIST таким образом, чтобы многочисленные сигнатуры можно было отдельно поддерживать и генерировать во время сеанса тестирования или отладки. На фиг.15 изображена система 1500, имеющая интегральную схему 1510, которая включает в себя многочисленные блоки 1020 и 1020' BIST, каждый из которых принимает один или более сигналов из встроенного логического анализатора 902. В частности, каждый блок 1020, 1020' BIST может принимать отличающийся набор из одного или более сигналов из или связан со встроенным логическим анализатором 902, таких как сигналы, возникающие на выходе модуля 210 межсоединений. Выход каждого блока 1020, 1020' BIST можно соединить со встроенным логическим анализатором 902 для выборки и хранения в нем. Например, выход данных каждого блока 1020, 1020' BIST можно соединить с входом встроенного логического анализатора 902, как показано на фиг.15.

Каждый блок 1020, 1020' BIST можно по отдельности задействовать и выводить из действия для генерации сигнатуры. В частности, разрешающий/запрещающий вход каждого блока 1020 и 1020' BIST можно соединить с входом другого специализированного блока 1420 и 1420', соответственно. Каждый специализированный блок 1420, 1420' может принимать на своем входе один или более сигналов из запускающего модуля 220. Один или более сигналов, принятых из запускающего модуля 220 с помощью каждого специализированного блока 1420, 1420', можно отличить от одного или более сигналов, принятых с помощью другого специализированного блока 1420, 1420'. Кроме этого, каждый специализированный блок 1420, 1420' можно по отдельности запрограммировать и/или сконфигурировать с помощью хост-устройства с использованием интерфейса 906. В результате, специализированные блоки 1420 и 1420' способны по отдельности независимо задействовать и вывести из действия свой соответствующий блок 1020 и 1020' BIST, соответственно. Понятно, что система 1500 может включать в себя более чем двух блоков 1020 и 1020' BIST в зависимости от системных модулей М.

Работа систем 1400 и 1500 будет описана со ссылкой на фиг.16а и 16b. Во время выполнения сеанса тестирования или отладки, запускающие события задают на этапе 1610 для конфигурирования запускающих событий, которые запускающий модуль 200 должен обнаружить во время сеанса. Приблизительно в это же время, функции, выполняемые специализированными блоками 1420 и 1420' задают на этапе 1620 таким образом, чтобы специализированные блоки 1420 и 1420' генерировали разрешающие сигналы для блоков 1020 и 1020' BIST, соответственно, согласно требуемым функциям, основанных на тестируемых и отлаживаемых конкретных системных модулях М. Это можно выполнить путем программирования программируемой схемы в специализированных блоках 1420 и 1420'. В случае, когда специализированные блоки 1420 и 1420' включают в себя процессор, это задание можно выполнить путем загрузки кода в память, доступ к которой осуществляет процессор, для исполнения. Понятно, что задание функций, которые будут выполнять специализированные блоки 1420 и 1420', зависит от конкретной реализации таких блоков.

Кроме того, во время работы каждый из блоков 1020 и 1020' BIST можно установить в свое известное, заданное состояние на этапе 1630 с использованием интерфейса 906. Далее, во время сеанса тестирования или отладки системы, на этапе 1640 встроенный логический анализатор 902 может принимать сигналы из одного или более системных модулей М. В течение этого периода времени встроенный логический анализатор 902 может выбирать на этапе 1650 определенные сигналы из принятых сигналов в качестве сигналов-кандидатов. Этот выбор можно выполнить с помощью модуля 210 межсоединений. Один или более из выбранных сигналов-кандидатов можно использовать с помощью запускающего модуля 220 для обнаружения возникновения ранее заданного запускающего события, тогда как другие сигналы-кандидаты могут быть доступны для захвата сигнала в ответ на такое обнаружение.

Далее, на этапе 1660 можно с помощью запускающего модуля 220 выполнить определение, возникли ли одно или более ранее заданных запущенных событий. После утвердительного определения того, что появилось запускающее событие, один или более сигналов-кандидатов можно захватить с помощью контроллера 240 памяти и сохранить в памяти 250. В дополнение или в качестве альтернативы, обнаружение запускающего события с помощью запускающего модуля 220 может побудить по меньшей мере частично по меньшей мере один из специализированных блоков 1420 и 1420' генерировать разрешающий сигнал на этапе 1670 для задействования соответствующего блока 1020 и 1020' BIST, соответственно, в зависимости от функции, ранее заданной на этапе 1620. В случае, когда специализированный блок 1420 задействует свой соответствующий блок 1020 BIST по меньшей мере частично в ответ на обнаружение запускающего события, на этапе 1680 генерируют новую сигнатуру при каждом тактовом импульсе на основании ранее поддерживаемой сигнатуры и на основании сигналов, появляющихся на входе данных блока 1020 BIST.

В некоторый момент в сеансе тестирования или отладки вслед за обнаружением запускающего события на этапе 1660, на этапе 1685 может произойти другое запускающее событие для выведения из действия ранее задействованного блока 1020 BIST. Это запускающее событие можно обнаружить, например, с помощью запускающего модуля 220 на основании одного или более сигналов-кандидатов, выбранных на этапе 1650. Альтернативно, такое запускающее событие может быть основано на истечении предопределенного периода времени после задействования блока 1020 BIST или после обнаружения запускающего события на этапе 1660 при контроле запускающим модулем 220 и специализированным блоком 1420. После обнаружения запускающего события на этапе 1685, блок 1020 BIST можно вывести из действия, что, таким образом, запрещает дополнительную генерацию сигнатуры. В этот момент сигнатуру, сгенерированную с помощью блока 1020 BIST можно подать во встроенный логический анализатор 902 на этапе 1690 для выборки и сохранения или для запуска события в нем. Сигнатуру можно также подавать для анализа через интерфейс 906.

Если сеанс тестирования или отладки не завершен, то операция может возобновиться на этапе 1660 для определения того, возникло ли другое запускающее событие, или на этапе 1650 для выбора другой группы сигналов для использования в качестве сигналов-кандидатов.

Сгенерированную сигнатуру можно подать на этапе 1690 во встроенный логический анализатор 902 для инициирования запускающего события или для захвата сигнала контроллером 240 памяти для сохранения в памяти 250. Это может произойти в результате того, что блок 1020 BIST больше не задействуется. В случае, когда сгенерированная сигнатура захвачена и сохранена в памяти 250, сигнатуру можно извлечь после этого для анализа. Такой анализ может включать в себя сравнение извлеченной сигнатуры с ожидаемым значением сигнатуры, идентифицированным путем моделирования системы и определения того, что система работает правильно, если извлеченная сигнатуру совпадает с ожидаемым значением сигнатуры.

Понятно, что любой один или более блоков 1020 и 1020' BIST и специализированные блоки 1420 и 1420' можно включить в логический анализатор 902. Кроме того, понятно, что интегральные схемы, 1010, 1410 и 1510 можно использовать практически в любой системе, которая может получить преимущество от встроенного механизма для облегчения эффективного тестирования и отладки системы и их системных модулей М. Например, принтер, печатающее устройство "все в одном" или многофункциональный принтер может включать в себя интегральную схему 900.

Механизм для тестирования отладки системы может включать в себя помимо специализированных блоков 904 и 920 программное обеспечение для поддержания связи со встроенным логическим анализатором 902 и специализированными блоками 904 и 920. Программное обеспечение обеспечивает пользователю возможность выбора внутрисистемных возможностей для таких блоков и управление или иным способом программирование их после того, как система была синтезирована и/или собрана, как во время сеанса тестирования или отладки системы. Программное обеспечение, включающее в себя пользовательский интерфейс, обеспечивает связь со встроенным логическим анализатором 902 и блоками 904 и 920 через интерфейс 906. Программное обеспечение можно использовать для приема в удаленном устройстве данных, выборочных и сохраненных с помощью встроенного логического анализатора 902 и отображения сигналов удаленному пользователю удаленного устройства.

В настоящем изобретении специалистам в данной области техники будет ясно, что в настоящем изобретении можно выполнить различные модификации и изменения без отклонения от сущности и объема настоящего изобретения. Например, понятно, что встроенный логический анализатор 902 может включать в себя выходной модуль 930 и контроллер 270, расположенный во встроенном логическом анализаторе 200 (фиг.2). В дополнение или в качестве альтернативы интегральные схемы 900, 910, 940 могут включать в себя ЦПУ 500 и носитель 510 данных, соединенные со встроенным логическим анализатором 902, как показано на фиг.5 и 6. Интегральные схемы 900, 910, 940 могут также включать в себя процессор 710, соединенный с запускающим модулем 220, как показано на фиг.7. Таким образом, подразумевается, что настоящее изобретение охватывает модификации и изменения настоящего изобретения при условии, что они находятся в пределах объема прилагаемой формулы изобретения и их эквивалентов.

Изобретение относится к встроенному логическому анализатору и, в частности, к программируемому встроенному логическому анализатору для анализа электронной схемы. Устройство для тестирования и отладки электронной схемы, содержащее логический анализатор, имеющий первый вход, принимающий множество сигналов, и выход для обеспечения индикации обнаружения, с помощью логического анализатора, по меньшей мере одного запускающего события; и блок со встроенным самотестированием (BIST), имеющий первый вход для приема одного или более сигналов, появляющихся на первом входе логического анализатора, второй вход, соединенный с выходом логического анализатора для избирательного задействования блока BIST, причем блок BIST генерирует и поддерживает сигнатуру на основании первого и второго его входов. Технический результат заключается в расширении функциональных возможностей. 3 н. и 16 з.п. ф-лы, 17 ил.

1. Устройство для тестирования и отладки электронной схемы, содержащее:

интегральную схему, содержащую:

логический анализатор, имеющий первый вход, принимающий множество сигналов, и выход для обеспечения индикации обнаружения, с помощью логического анализатора, по меньшей мере одного запускающего события; и

блок со встроенным самотестированием (BIST), имеющий первый вход для приема одного или более сигналов, появляющихся на первом входе логического анализатора, второй вход, соединенный с выходом логического анализатора для избирательного задействования блока BIST, причем блок BIST генерирует и поддерживает сигнатуру на основании первого и второго его входов.

2. Устройство по п.1, в котором блок BIST включает в себя выход для обеспечения поддерживаемой сигнатуры, причем упомянутый выход соединен с логическим анализатором для выборки и хранения в нем.

3. Устройство по п.1, в котором логический анализатор включает в себя блок мультиплексора, имеющий вход, соединенный с первым входом логического анализатора, и первый вход блока BIST соединен с выходом схемы мультиплексора.

4. Устройство по п.1, в котором логический анализатор содержит блок мультиплексора, имеющий вход, соединенный с первым входом логического анализатора, и блок контроллера памяти, имеющий первый вход, соединенный с выходом блока мультиплексора, и второй вход, соединенный с выходом блока BIST.

5. Устройство по п.1, в котором блок BIST содержит сдвиговый регистр с многочисленными входами, и сигнатура, поддерживаемая в блоке BIST, поддерживается в сдвиговом регистре с многочисленными входами.

6. Устройство по п.1, в котором блок BIST включает в себя тактовый вход таким образом, чтобы, когда блок BIST задействован с помощью логического анализатора, блок BIST генерировал новую сигнатуру после каждого возникновения запускающего фронта сигнала, появляющегося на тактовом входе блока BIST.

7. Устройство по п.1, дополнительно содержащее блок действия, имеющий вход, соединенный с логическим анализатором для приема индикации обнаружения по меньшей мере одного запускающего события, и выход, соединенный со вторым входом блока BIST, причем блок действий генерирует на своем выходе сигнал, который основан на входном сигнале блока действий, согласно заданной функции, причем заданная функция является конфигурируемой.

8. Устройство по п.1, дополнительно содержащее множество блоков BIST, причем каждый блок BIST имеет первый вход для приема одного или более сигналов, связанных с логическим анализатором, второй вход, связанный с логическим анализатором, для задействования блока BIST, и выход, связанный с логическим анализатором, причем каждый блок BIST отдельно и независимо генерирует и поддерживает сигнатуру, основанную частично на его первом и втором входах.

9. Интегральная схема для тестирования и отладки электронной схемы, содержащая:

логический анализатор, имеющий первый вход для приема множества сигналов, и первый выход для обеспечения выбранных выборок сигналов, появляющихся на первом входе; и

генератор сигнатур, имеющий первый вход, соединенный с логическим анализатором для приема одного или более сигналов, появляющихся на его первом входе, и выход, соединенный с логическим анализатором для подачи в него сигнатуры.

10. Интегральная схема по п.9, в которой логический анализатор включает в себя генерацию сигнала события, показывающего обнаружение события, контролируемого с помощью логического анализатора, причем генератор сигнатур включает в себя разрешающий вход для разрешения генератору сигнатуры генерировать новую сигнатуру, и сигнал события соединен с разрешающим входом генератора сигнатуры.

11. Интегральная схема по п.10, дополнительно содержащая блок действий, имеющий вход, соединенный с логическим анализатором для приема сигнала события, и выходной сигнал, соединенный с разрешающим входом генератора сигнатур, причем блок действий генерирует выходной сигнал, на основании по меньшей мере частично его входного сигнала, согласно заданной функции.

12. Интегральная схема по п.11, в которой заданная функция является программируемой.

13. Интегральная схема по п.9, в которой логический анализатор включает в себя схему мультиплексора, имеющую вход, соединенный с первым входом логического анализатора, и схему управления памятью, имеющую первый вход, соединенный с выходом блока мультиплексора, и второй вход, соединенный с генератором сигнатур для приема от него сигнатуры.

14. Интегральная схема по п.9, в которой генератор сигнатур принимает тактовый сигнал и при задействовании генерирует новую сигнатуру в ответ на каждый запускающий фронт тактового сигнала.

15. Интегральная схема по п.10, в которой генератор сигнатур избирательно задействуется с помощью логического анализатора.

16. Система для тестирования и отладки электронной схемы, содержащая:

один или более системных модулей; и

интегральную схему, содержащую:

блок встроенного логического анализатора, имеющий вход для приема множества сигналов из одного или более системных модулей; и

блок тестирования, имеющий вход, соединенный с блоком встроенного логического анализатора для приема по меньшей мере одного из множества сигналов из одного или более системных модулей, причем блок тестирования поддерживает в нем значение сигнатуры, блок тестирования избирательно генерирует и поддерживает новую сигнатуру при задействовании на основании поддерживаемой сигнатуры и на основании входа блока тестирования.

17. Система по п.16, в которой блок тестирования включает в себя выход, соединенный с блоком встроенного логического анализатора для подачи в него новой сигнатуры.

18. Система по п.16, в которой блок тестирования задействуется и выводится из действия на основании по меньшей мере частично встроенного логического анализатора.

19. Система по п.16, дополнительно содержащая специализированный блок, генерирующий по меньшей мере один выходной сигнал, согласно по меньшей мере одной заданной функции, причем блок тестирования задействуется и выводится из действия на основании по меньшей мере частично по меньшей мере одной заданной функции, при этом по меньшей мере одна заданная функция является программируемой.

| US 6564347 B1, 13.05.2003 | |||

| US 2002194543 A1, 19.12.2002 | |||

| US 2004216061 A1, 28.10.2004 | |||

| US 2004003332 A1, 01.01.2004. |

Авторы

Даты

2016-04-10—Публикация

2011-09-08—Подача