Область техники, к которой относится изобретение

Варианты осуществления изобретения в общем, относятся к связи между устройствами и более конкретно к управлению колебаниями инициатора связи между устройствами.

Уведомление об авторском праве/разрешении

Части раскрытия данного патентного документа могут содержать материал, который защищен авторским правом. Владелец авторского права не возражает против воспроизведения любого из патентного документа или патентного раскрытия в том виде, как они представлены в файле ведомства по патентам и товарным знакам или в записях, но в остальном сохраняет все авторские права. Уведомление о защите авторских прав относится ко всем данным, описанным ниже, и к приложенным к ним чертежам, а также к любому программному обеспечению, описанному ниже: Copyright © 2013, Intel Corporation, All Rights Reserved.

Уровень техники

Связь между компонентами на хост платформе необходима для работы электронного устройства. Однако связь включает в себя использование выходной линии или инициаторов линии передачи, потребляющих существенное количество общей энергии, используемой в электронных устройствах. Например, связь между процессором и памятью, между контроллером памяти и процессором, между контроллером памяти и запоминающим устройством, между периферийным контроллером и процессором или подсистемой памяти, или другая связь, потребляет существенное количество энергии. Обычно связь между разными компонентами может называться вводом-выводом (I/O) и часто управляется стандартами (например, между компонентами подсистемы памяти). Стандарты I/O могут относиться к рабочим характеристикам в отношении энергии питания I/O, задержки I/O и частоты I/O. Стандарты или номинальные значения рабочих установок I/O установлены на значения, которые могут быть достигнуты в разных системах для совместимости и обеспечения возможности взаимодействия.

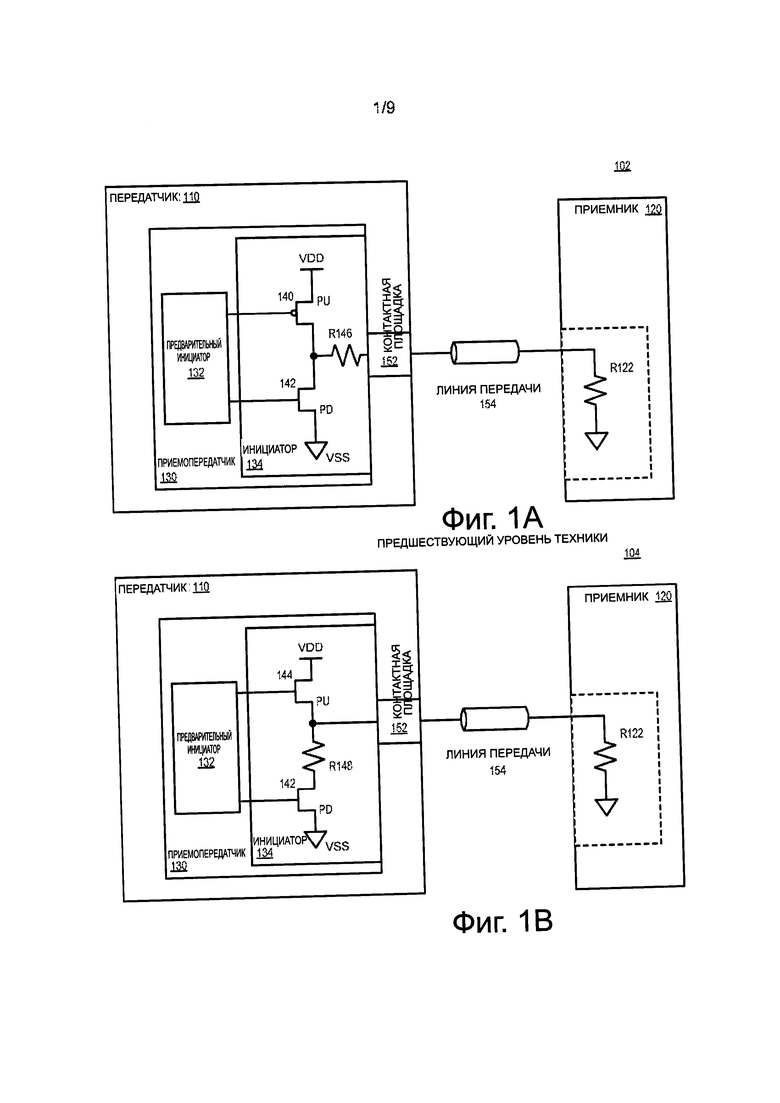

На фиг. 1А показана блок-схема известного выходного инициатора CMOS. Известный выходной инициатор 134 CMOS (комплементарный металлооксидный полупроводник) представляет собой обычную конструкцию для систем I/O. Система 102 включает в себя передатчик 110, осуществляющий связь с приемником 120. Следует понимать, что передатчик 10 представляет собой приемное устройство, когда приемник 120 запускает связь с передатчиком 110. Таким образом, роли устройства передачи и устройства приема могут стать обратными, и выходной инициатор 134 представлен как часть приемопередатчика 130. Однако с целью представленного здесь описания основное внимание направлено, скорее, на передачу сигнала, чем на прием сигнала. С целью передачи сигнала от передатчика 110 в приемник 120 приемник 120 может быть смоделирован как импеданс R122 нагрузки. Передатчик 110 инициирует линию 154 передачи для приемника 120 для приема путем подъема напряжения в линии 154 передачи до уровня VDD через элемент 140 подъема (PU) и опускания напряжения в линии 154 передачи вниз до VSS через элемент 142 опускания (PD). Выходной импеданс R146 обычно согласован с импедансом контактной площадки 152 и линии 154 передачи, как это выглядит для инициатора 134. Предварительный инициатор 132 обеспечивает передачу сигналов и управление для инициатора 134, для вывода сигнала по линии 154 передачи. Контактная площадка 152 формирует интерфейс между устройством 110 передатчика и линией 154 передачи.

Пример использования системы 102 представлен для инициатора в LPDDR3 (малой мощности с двойной скоростью передачи данных версия 3, исходная спецификация, опубликованная в мае 2012 компанией JEDEC). Система 102 обеспечивает полное колебание выходного напряжения для возбуждения выходного сигнала. Другие компоненты, кроме подсистем памяти, также могут использовать инициатор, который обеспечивает полное колебание выходного напряжения. Для полного колебания выходного напряжения используется существенная энергия для I/O (ввода/вывода) или взаимодействия между компонентами.

Краткое описание чертежей

Следующее описание включает в себя раскрытие чертежей, содержащих иллюстрации, приведенные в качестве примера воплощения вариантов осуществления изобретения. Чертежи следует понимать как пример, а не как ограничение. Используемые здесь ссылки на один или больше "вариантов осуществления" следует понимать, как описывающие конкретные свойства, структуры и/или характеристики, включенные, по меньшей мере, в одно воплощение изобретения. Таким образом, такие фразы как "в одном варианте осуществления" или "в альтернативном варианте осуществления", появляющиеся здесь, описывают различные варианты осуществления и воплощения изобретения и не обязательно все относятся к одному и тому же варианту осуществления. Однако они не обязательно являются взаимно исключающими.

На фиг. 1А показана блок-схема известного выходного инициатора CMOS.

На фиг. 1В показана блок-схема выходного инициатора с двойным NMOS.

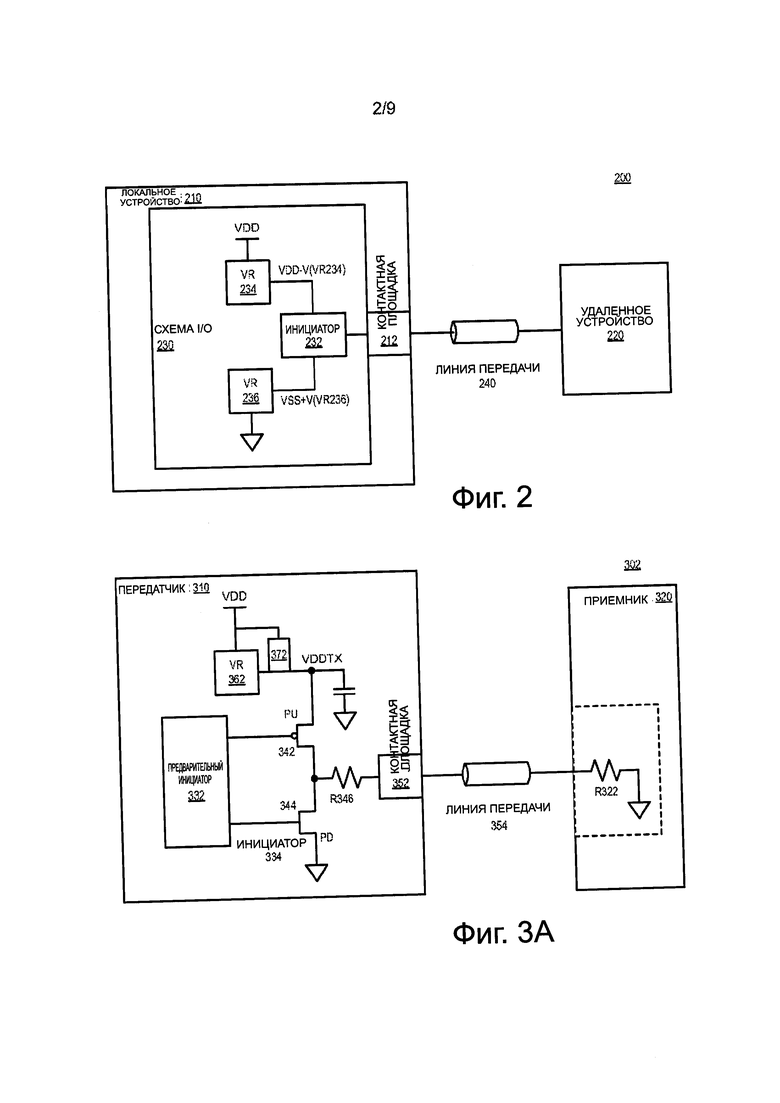

На фиг. 2 показана блок-схема варианта осуществления системы, имеющей регулятор напряжения, для уменьшения колебаний напряжения при передаче.

На фиг. 3А показана блок-схема варианта осуществления системы, имеющей регулятор напряжения, включенный для уменьшения колебаний напряжения относительно высокого опорного напряжения выходного сигнала.

На фиг. 3В показана блок-схема варианта осуществления системы, имеющей регулятор напряжения, включенный для уменьшения колебаний напряжения относительно низкого опорного напряжения выходного сигнала.

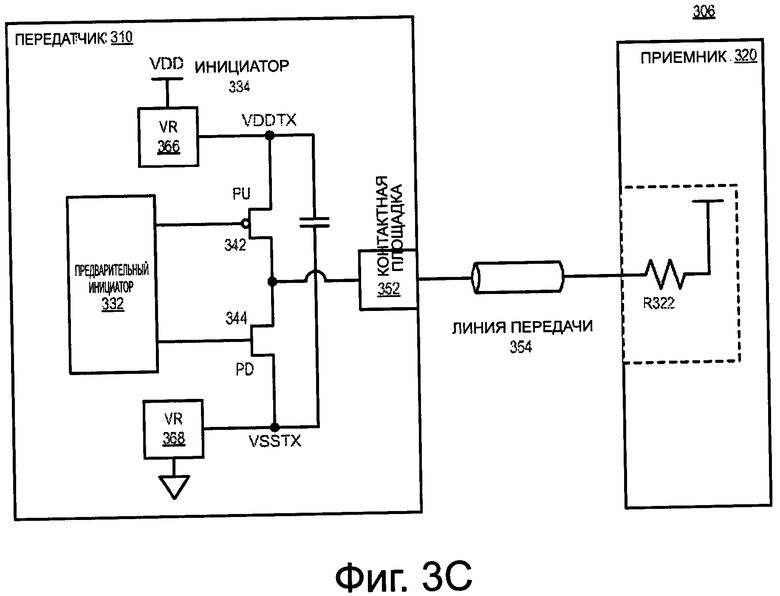

На фиг. 3С показана блок-схема варианта осуществления системы, имеющей регуляторы напряжения, включенные для уменьшения колебаний напряжения, как относительно низкого опорного напряжения, так и относительно высокого опорного напряжения выходного сигнала.

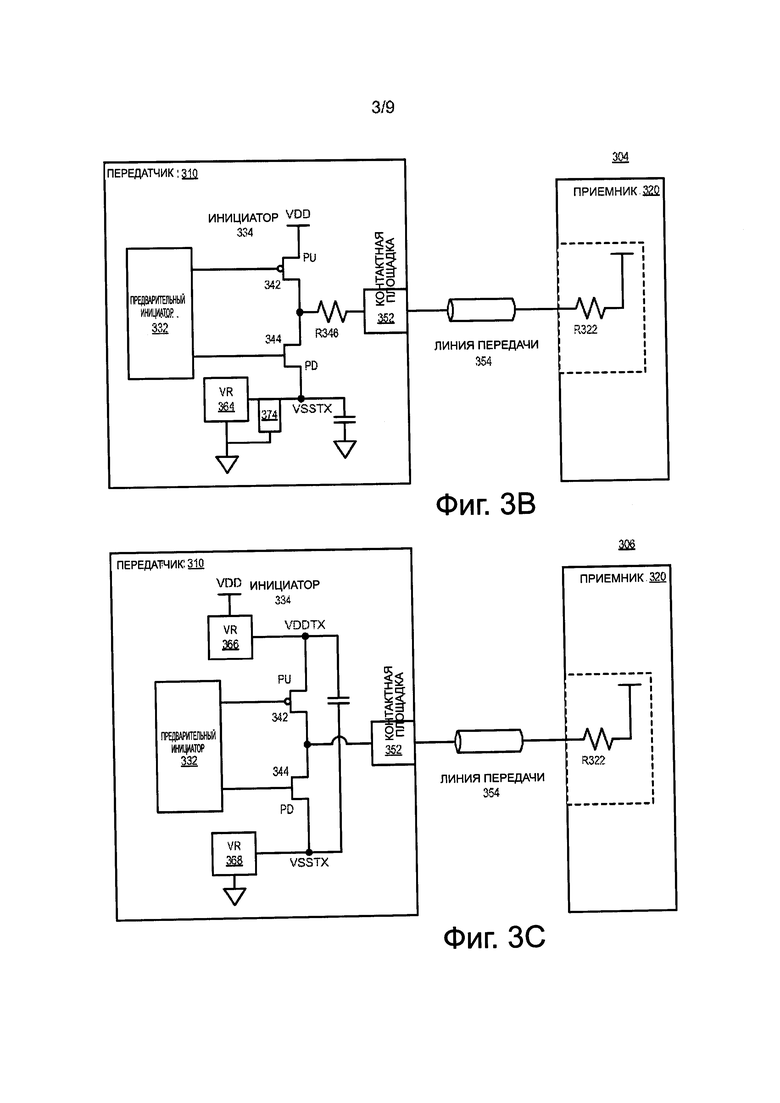

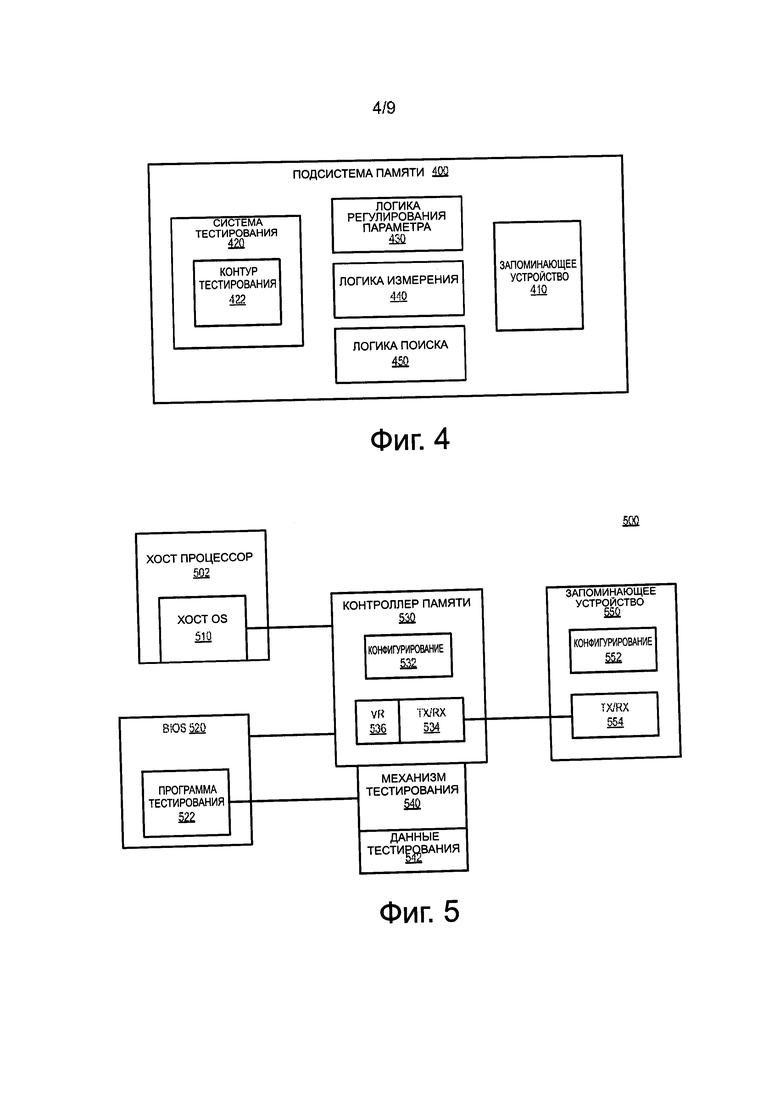

На фиг. 4 показана блок-схема варианта осуществления подсистемы памяти, имеющей систему тестирования, обеспечивающую тестирование в системе для управления колебаниями выходного напряжения.

На фиг. 5 показана блок-схема варианта осуществления контроллера памяти и подсистемы связи запоминающего устройства с регулировкой напряжения для управления колебаниями напряжения сигнала.

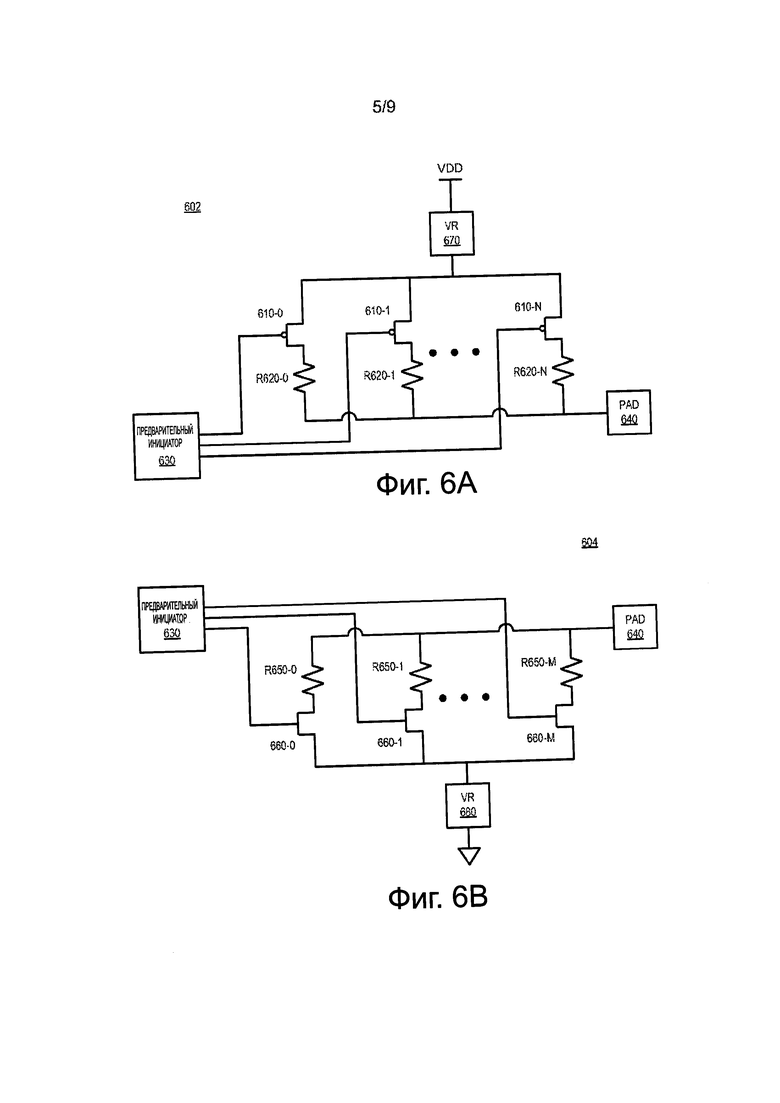

На фиг. 6А показана блок-схема варианта осуществления схемы импеданса с множеством выводов для подъема напряжения.

На фиг. 6В показана блок-схема варианта осуществления схемы импеданса с множеством выводов для опускания напряжения.

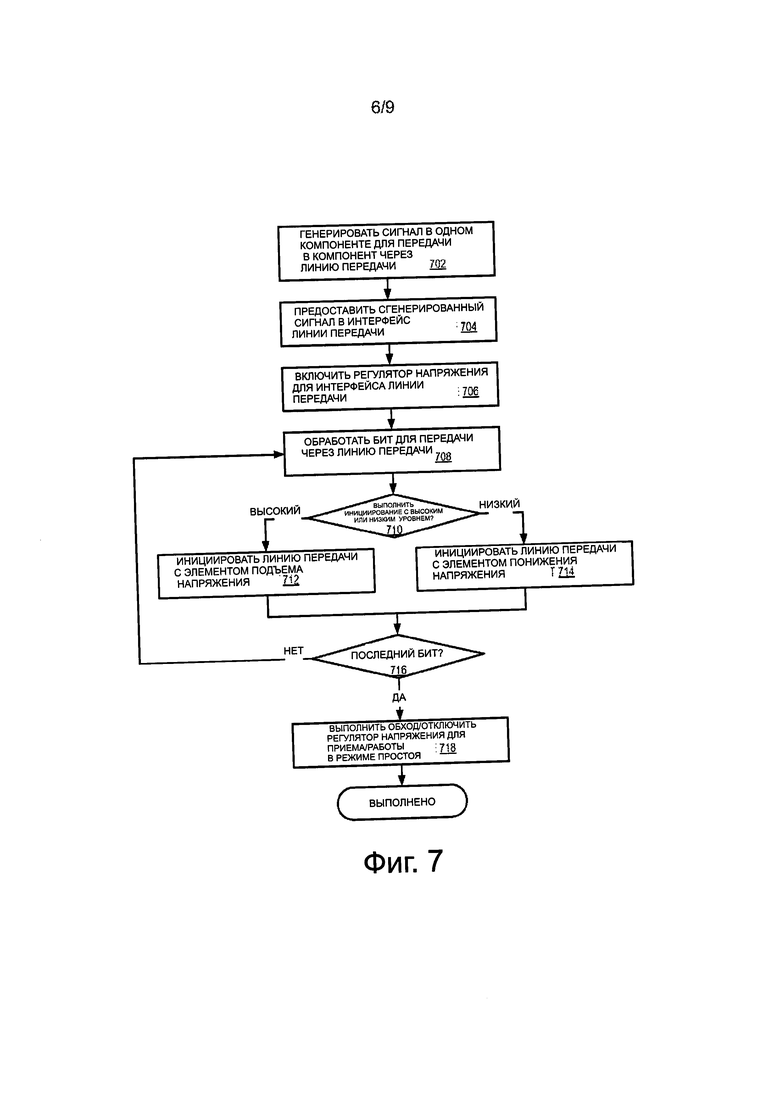

На фиг. 7 показана блок-схема последовательности операций варианта осуществления обработки для вывода сигнала с уменьшенными колебаниями напряжения.

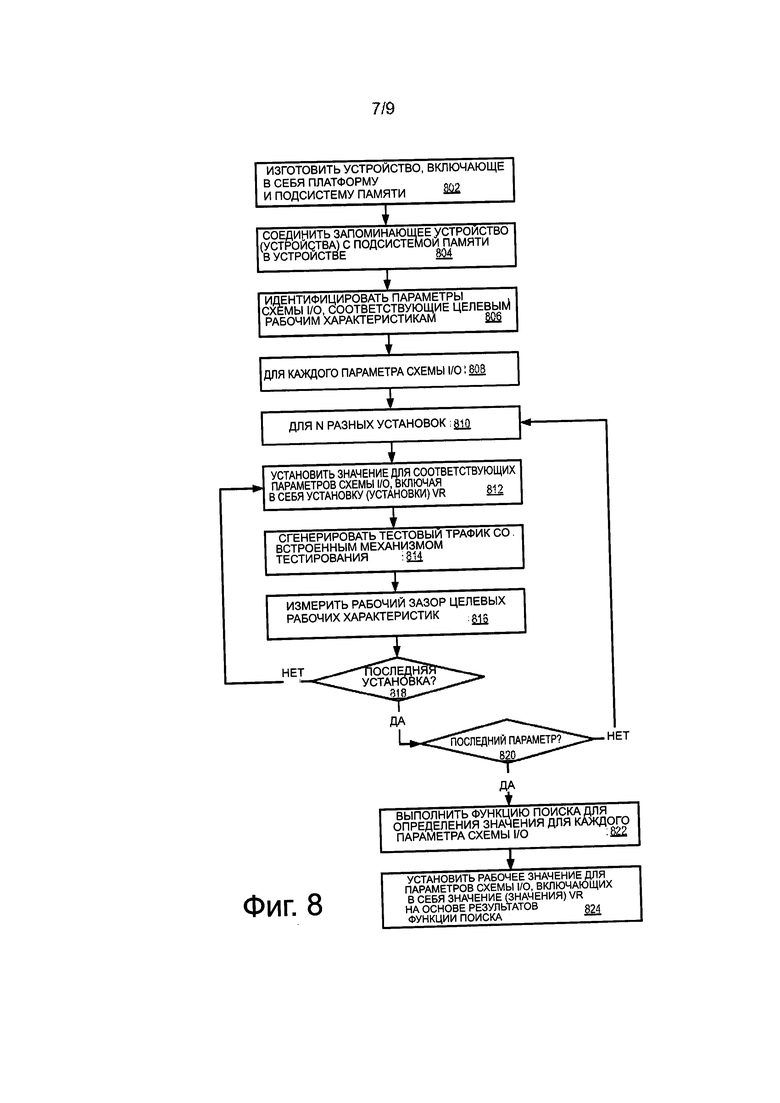

На фиг. 8 показана блок-схема последовательности операций варианта осуществления обработки для эмпирического тестирования и определения установки передачи данных с использованием исчерпывающего поиска возможных значений.

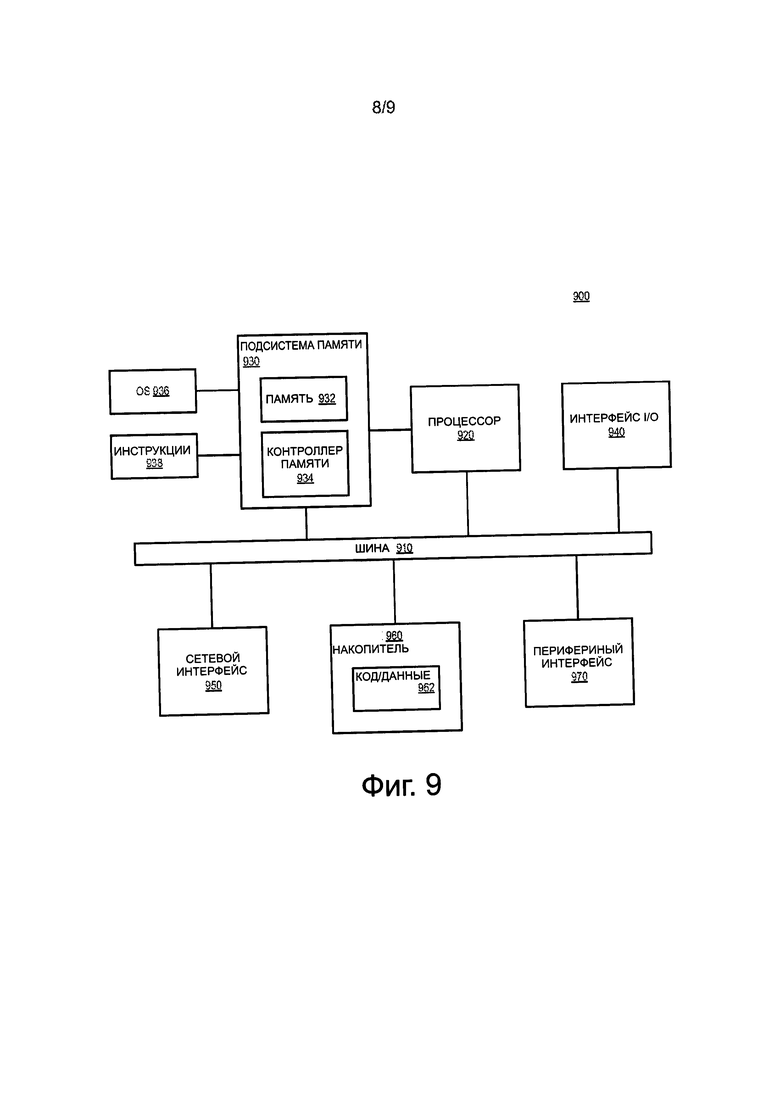

На фиг. 9 показана блок-схема варианта осуществления вычислительной системы, в которой может быть выполнено управление колебаниями напряжения.

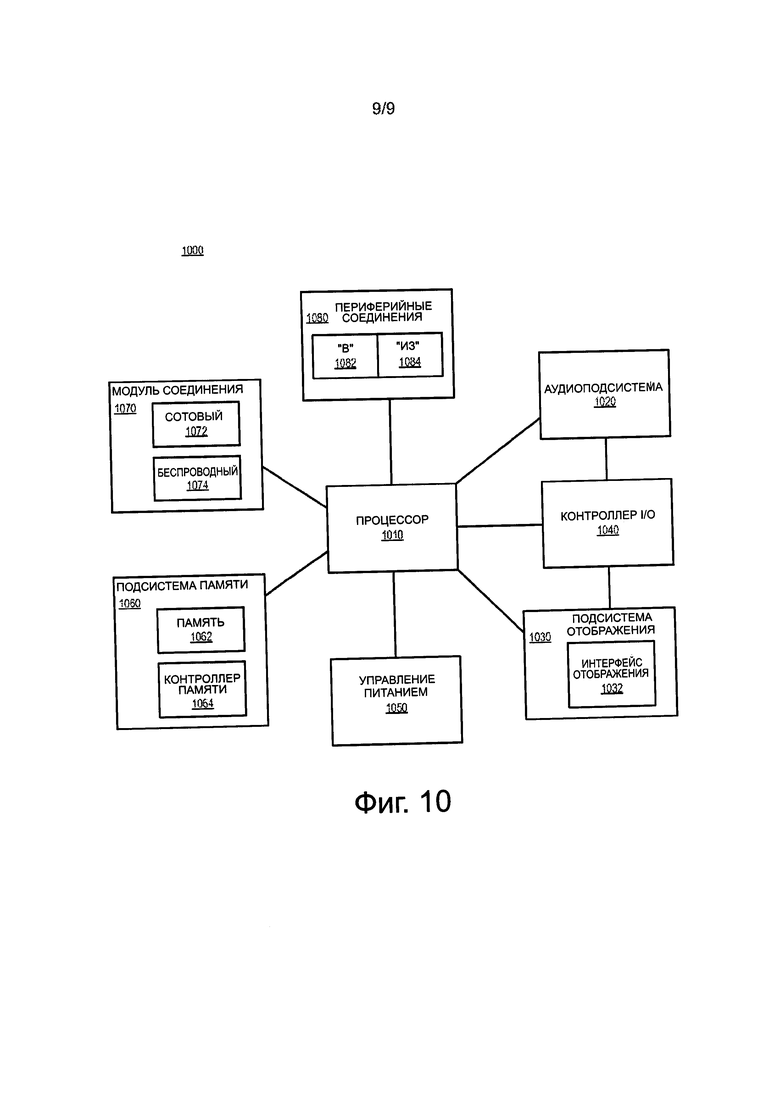

На фиг. 10 показана блок-схема варианта осуществления мобильного устройства, в котором может быть выполнено управление размахом напряжения.

Описания определенных деталей и воплощений представлены ниже, включая в себя описание чертежей, на которых могут быть представлены некоторые или все варианты осуществления, описанные ниже, а также описание других потенциальных вариантов осуществления или вариантов осуществления представленных здесь изобретательских концепций.

Осуществление изобретения

Как описано ниже, регулятор напряжения управляет колебаниями напряжения схемы интерфейса линии передачи для передачи сигналов. Схема интерфейса линии передачи представляет собой или составляет часть инициатора, который инициирует линию передачи. Схема интерфейса линии передачи включает в себя комплементарные элементы инициирования, включающие в себя элемент инициирования р-типа для подъема напряжения в линии передачи в ответ на высокий логический уровень и элемент инициирования n-типа для опускания напряжения в линии передачи в ответ на низкий логический уровень. Регулятор напряжения соединен между одним из элементов инициирования и соответствующим опорным напряжением для уменьшения колебаний напряжения в схеме интерфейса линии передачи. В одном варианте осуществления регуляторы напряжения используются как в ответвлении, поднимающем напряжение, так и в ответвлении, опускающем напряжение, в схеме интерфейса линии передачи. Таким образом, первый регулятор напряжения может быть размещен между источником высокого напряжения (VDD) и элементом подъема напряжения и второй регулятор напряжения может быть размещен между источником низкого напряжения или землей (VSS) и элементом опускания напряжения. Уменьшенный размах колебаний напряжения может быть выполнен так, чтобы он соответствовал стандартам интерфейса I/O (ввода/вывода) при уменьшении количества энергии, используемой в системах для передачи I/O.

В одном варианте осуществления операции схемой интерфейса линии передачи можно дополнительно управлять путем использования эмпирического тестирования. Система эмпирически может тестировать параметры рабочих характеристик I/O (ввода/вывода) устройства для конкретного устройства. На основе эмпирического тестирования через систему тестирования система может устанавливать рабочие параметры, специфичные для системы или устройства, в котором происходит обмен данными между устройствами. Для каждой из множества различных установок для множества разных параметров схемы I/O система тестирования устанавливает значение для каждого параметра схемы I/O, генерирует тестовый трафик для нагрузочных испытаний при передаче данных со значением (значениями) параметра и измеряет рабочий запас для рабочих характеристик I/O. Параметры цепи могут включать в себя Vref, Ron, максимальную скорость нарастания выходного напряжения, нагрузочный резистор на кристалле (ODT), выходное напряжение регулятора и/или другие параметры. Тестовая система дополнительно выполняет функцию поиска для определения значений для каждого параметра цепи I/O, при которых рабочий запас удовлетворяет минимальному пороговому значению, и рабочие характеристики, по меньшей мере, одного из параметров цепи I/O увеличиваются. В одном варианте осуществления система устанавливает значения во время работы для параметров цепи I/O на основе функции поиска. Настройки могут динамически изменяться для конкретных компонентов определенных систем на основе тестирования.

В одном варианте осуществления описанная тестовая система или тестовый механизм может использоваться для тестирования подсистем памяти, и более конкретно, для обмена данными между компонентами платформы (например, процессором, контроллером памяти) и запоминающим устройством. Любая подсистема памяти, в которой используется контроллер памяти с планировщиком или эквивалентной логикой, может воплощать, по меньшей мере, один вариант осуществления тестового механизма. Ссылка здесь может быть сделана на запоминающие устройства, которые могут включать в себя разные типы памяти. Например, в подсистемах памяти обычно используется DRAM, которое представляет собой один пример запоминающего устройства, как описано здесь. Таким образом, тестовый механизм, описанный здесь, совместимым с любой одной из многих технологий памяти, таких как DDR3 (двойная скорость передачи данных, версия 3, оригинальный выпуск JEDEC (Объединенный инженерный совет по электронным устройствам) 27 июня 2007 г., в настоящее время выпуск 21), DDR4 (DDR версии 4, исходная спецификация, опубликованная в сентябре 2012 г. JEDEC), LPDDR4 (двойная скорость передачи данных с низким потреблением энергии, версия 4, спецификация разрабатывается JEDEC на момент подачи данной заявки), WIDEIO (спецификация, развиваемая JEDEC на момент подачи данной заявки), и/или другие, и технологии на основе производных или расширений таких спецификаций.

На фиг. 1В показана блок-схема известного выходного инициатора двойного NMOS. Система 104 аналогична системе 102 на фиг. 1А, но с элементом 144 подъема напряжения n-типа и с элементом 142 опускания напряжения n-типа. Колебания выходных сигналов ниже в системе 104, чем в системе 102, поскольку элемент подъема напряжения n-типа или устройство имеет пороговое напряжение, необходимое для включения элемента 144, что уменьшает выходные колебания в результате использования комплементарной конструкции инициатора. Элементы 110, 120, R122, 130, 132, 134, 152 и 154 являются такими же, как и в системе 104, за исключением упомянутого. Выходной импеданс R148 обычно устанавливают так, чтобы он соответствовал импедансу контактной площадки 152 и линии 154 передачи, как это выглядит для инициатора 134.

Пример использования системы 104 предназначен для инициатора, для LPDDR4, в котором предложена система 104 аналогичной конструкции. Система 102 позволяет получить полное колебание выходного напряжения для возбуждения выходного сигнала, при этом используется больше энергии, чем в системе 104. Однако система 104 увеличивает padcap (емкость контактной площадки) и требует другого управления скоростью нарастания выходного напряжения, чем используется в системе 102. Таким образом, в системе интерфейса невозможно просто подключать инициатор LPDDR3 для поддержки наследуемых устройств на той же контактной площадке, соединенной с инициатором LPDDR4. Кроме того, конструкция системы 104 приводит к таким значениям подъема напряжения Ron (выходной импеданс), которое не очень хорошо управляется через PVT (обработка, напряжение и температура). Кроме того, поднятое напряжение и Ron трудно компенсировать в системе 104.

На фиг. 2 показана блок-схема варианта осуществления системы, имеющей регулятор напряжения для уменьшения колебания напряжения при передаче I/O. Система 200 включает в себя локальное устройство 210, которое связывается с удаленным устройством 220. Основное внимание в описании системы 200 направлено на передачу сигнала из локального устройства 210 в удаленное устройство 220. Локальное устройство 210 является "локальным" для схемы интерфейса линии передачи, которая возбуждает линию 240 передачи при передаче. Таким образом, при передаче из устройства 210 в устройство 220 удаленное устройство 220 является удаленным относительно схемы интерфейса линии передачи. Следует понимать, что роли двух устройств, как передатчика и приемника, могут быть обратными. Схема инициатора передачи устройств 210 и 220 не обязательно одинакова.

Локальное устройство 210 включает в себя схему 230 I/O, которая составляет интерфейсы для линий 240 передачи через контактную площадку 212. Схема 230 включает в себя инициатор 232, который управляет линией 240 передачи для связи с удаленным устройством 220. В одном варианте осуществления линия 240 передачи представляет собой сигнальную линию (например, дорожку), соединяющую выводы I/O локального устройства 210 с удаленным устройством 220. Линия 240 передачи, в качестве альтернативы, может представлять собой провод или другое взаимное соединение.

В одном варианте осуществления инициатор 232 представляет собой структуру CMOS (комплементарный металло-оксидный полупроводник) со схемой, эквивалентной элементу подъема напряжения и элементу опускания напряжения. Любой один или оба из ответвлений подъема напряжения и опускания напряжения инициатора 232 может быть соединен с соответствующим опорным напряжением через регулятор напряжения. В одном варианте осуществления регулятор напряжения предусмотрен в ответвлении подъема напряжения. В одном варианте осуществления регулятор напряжения предусмотрен в ответвлении опускания напряжения. В одном варианте осуществления регуляторы напряжения предусмотрены в обоих ответвлениях подъема и опускания напряжения. Например, ответвление подъема натяжения может быть соединено с VDD через регулятор (VR) 234 напряжения, и ответвление опускания напряжения может быть соединено с VSS через VR 236. Таким образом, эффективное логическое высокое напряжение для передачи локальным устройством 210 может составлять VDD-Vvr 234 или VDD минус величина опускания напряжения, предусмотренная в VR 234. Эффективное логически низкое значение для передачи локальным устройством 210 может составлять VSS+Vvr 236 или VSS плюс величина подъема напряжения, обеспечиваемая VR 236. Следует понимать, что изменение напряжения, предусмотренное VR 234 и VR 236, не обязательно является одинаковым. В обоих случаях колебания напряжения могли бы быть уменьшены посредством эквивалентной схемы без регулятора напряжения.

Уменьшение колебаний выходного напряжения может обеспечить экономию энергии для схемы 230 по сравнению с конструкцией, в которой колебания происходят от одной шины питания до другой шины питания. Предположим, что VR 234 включен в схему 230, обеспечивая выходное напряжение VDD-Vvr234. Если VR 234 представляет собой линейный регулятор напряжения, тогда конструкция системы 200 будет уменьшать мощность передачи в линейной зависимости относительно уменьшения напряжения, обеспечиваемого Vvr234. Если VR 234 разработан как переключающийся регулятор напряжения или переключающий схему регулятор (например, регулятор с переключением конденсаторов, регулятор с переключаемой индуктивностью), конструкция системы 200 может уменьшать мощность передачи приблизительно в квадратичной взаимосвязи с уменьшением напряжения, обеспечиваемым Vvr234. В одном варианте осуществления, как описано более подробно ниже со ссылкой на фиг. 4 и 5, точное целевое значение размаха напряжения для одного или обоих регуляторов напряжения может быть оптимизировано после изготовления фактического физического устройства, используя тренировочный поток из системы тестирования, которая позволяет выполнить поиск для уменьшения общей энергии, при поддержании определенных значений высоты и/или ширины глазковой диаграммы.

В одном варианте осуществления один или оба регулятора 234 и 236 напряжения могут быть локально интегрированы на одном и том же полупроводниковом кристалле или в интегральной схеме, как схема 230, занимая очень мало площади поверхности. Например, конструкция устройства часто имеет достаточно пустых мест для размещения варианта осуществления регулятора напряжения в схеме 230. Известны технологии для разработки линейных регуляторов, которые позволяют получить низкие затраты энергии, не требуя существенной величины уменьшения связи емкости на кристалле. В одном варианте осуществления один или оба регулятора 234 и 236 напряжения воплощены в том же корпусе или на той же плате, что и схема 230, без размещения на той же полупроводниковой подложке. Размещение регуляторов напряжения за пределами кристалла может привести к более высоким издержкам при конструировании и/или затратам при воплощении.

В одном варианте осуществления (который явно не показан) один или оба регулятора 234 и 236 напряжения можно избирательно обойти через путь обхода. Путь обхода может избирательно активироваться для переключения соединения на опорное напряжение через регулятор напряжения или соединение непосредственно с опорным напряжением. Таким образом, например, вход в регулятор и выход из регулятора могут быть соединены через избирательный (например, переключаемый) путь с низким импедансом, который позволяет выполнить обход регулятора, когда он активирован. Такая конструкция может использоваться для формирования интерфейса с разными типами систем (например, интерфейса как с LPDDR3 (с обходом для полного колебания напряжения), так и LPDDR4 (активированный регулятор для малого колебания напряжения)). Кроме того, регулятор напряжения можно отключать, если он не требуется, таким образом, чтобы принять сигнал вместо возбуждения передачи сигнала. Таким образом, при низких состояниях напряжения регулятор напряжения может удваивать энергию как затвор для энергии, и может отключать энергию для инициатора, когда он не используется, что позволяет уменьшить утечку по цепи.

На фиг. 3А показана блок-схема варианта осуществления системы, имеющей регулятор напряжения, подключенный для уменьшения размаха колебаний в отношении опорного высокого напряжения выходного сигнала. Система 302 может представлять собой один пример варианта осуществления системы 200. Передатчик 310 представляет собой локальное устройство, и приемник 320 представляет собой удаленное устройство. Для передачи приемник 320 представлен в системе 302, как импеданс R2322 нагрузки. Передатчик 310 включает в себя предварительный инициатор 332 для обеспечения управления и передачи сигналов в инициатор 334, для возбуждения и вывода сигнала передачи по линии 354 передачи через контактную площадку 352.

Инициатор 334 включает в себя элемент 342 подъема напряжения и элемент 344 опускания напряжения. Элемент 344 представляет собой элемент n-типа (например, NMOS), который опускает напряжение в линии 354 передачи для генерирования логически низкого сигнала. Элемент 342 представляет собой элемент р-типа (например, PMOS), который поднимает напряжение в линии 354 передачи для генерирования логически высокого сигнала. Следует понимать, что "логически низкий" и "логически высокий" относится к уровням напряжения, а не к протоколу связи или сигналам, используемым между устройствами 310 и 320. Например, в одной схеме передачи сигналов логически низкое напряжение может соответствовать передаче "нуля", и логически высокое напряжение может соответствовать передаче "единицы". Однако схема передачи сигналов может быть построена на обратном представлении, где логически высокое напряжение может соответствовать передаче нуля, и логически низкое напряжение может соответствовать передаче единицы.

Передатчик 310 включает в себя регулятор 362 напряжения для уменьшения уровня высокого напряжения передачи от VDD до VDDTX, которое представляет собой VDD минус падение напряжения на регуляторе 362 напряжения. В одном варианте осуществления передатчик 310 включает в себя обходной путь 372, который позволяет обходить регулятор 362 напряжения. Сглаживающий конденсатор может быть размещен между VDDTX и VSS для фильтрации шумов, которые могут быть введены регулятором 362 напряжения. Инициатор 334 включает в себя выходной импеданс, Ron, R346, включенный между комплементарными выходными элементами 342 и 344, и контактной площадкой 352. Конструкция системы 302 обеспечивает хорошо управляемые уровни Ron и выходного напряжения. Кроме того, уровни выходного напряжения могут быть настраиваемыми путем регулирования выхода регулятора 362 напряжения.

Система 302 может использоваться как воплощение схемы нагрузки VSS для низкого размаха колебания LPDDR4. Кроме того, система 302 может быть воплощена как для LPDDR3, так и для LPDDR4, например, путем избирательного обхода регулятора 362 напряжения. Таким образом, система 302 поддерживает конструкцию, представляющую комбинацию LPDDR3/4 с высокими рабочими характеристиками. В одном варианте осуществления обходной путь 372 составляет часть или воплощение регулятора 362 напряжения, что обеспечивает для регулятора возможность короткого замыкания VDD в VDDTX. Для специалиста в данной области техники будет понятно, что конструкция системы 302 не будет сильно влиять на padcap или общие характеристики передатчика 310.

Использование буфера CMOS обеспечивает присущие ему преимущества целостности сигнала, благодаря представлению постоянного импеданса Ron для контактной площадки 352. Таким образом, передатчик 310 может соответствовать характерному импедансу линии 354 передачи и может поглощать любую избыточную энергию в результате отражения. Однако путем регулирования целевого напряжения регулятора 362 напряжения, система 302 может регулировать размах колебаний, представленный приемником 320, для достижения требуемого размаха колебаний или напряжения общего режима. В результате система 302 обеспечивает независимое регулирование над размахом колебаний буфера I/O и Ron.

На фиг. 3В показана блок-схема варианта осуществления системы, имеющей регулятор напряжения, включенный для уменьшения размаха колебаний относительно низкого опорного напряжения выходного сигнала. Система 304 может представлять собой один пример варианта осуществления системы 200. Передатчик 310 представляет собой локальное устройство, и приемник 320 представляет собой удаленное устройство. С целью передачи приемник 320 представлен в системе 304 как импеданс R322 нагрузки, который может представлять собой нагрузочный резистор на кристалле VDD, напряжение общего назначения или заземление, в зависимости от конкретного воплощения. Передатчик 310 включает в себя предварительный инициатор 332 для обеспечения управления и передачи сигнала, для инициатора 334, для возбуждения и вывода или передачи сигнала по линии 354 передачи через контактную площадку 352. Инициатор 334 включает в себя элемент 342 подъема напряжения и элемент 344 опускания напряжения. Элемент 344 представляет собой элемент n-типа (например, NMOS), элемент, который выполняет опускание напряжения в линии 354 передачи для генерирования логически низкого сигнала. Элемент 342 представляет собой элемент р-типа (например, PMOS), который выполняет подъем напряжения в линии 354 передачи, для генерирования логически высокого сигнала.

Передатчик 310 включает в себя регулятор 364 напряжения для подъема передаваемого уровня низкого напряжения от VSS до VSSTX, который представляет собой VSS плюс напряжение регулятора 364 напряжения. В одном варианте осуществления передатчик 310 включает в себя обходной путь 374, который позволяет выполнять обход регулятора 364 напряжения. Сглаживающий конденсатор может быть включен от VSSTX до VSS (или от VDD, в зависимости от окружающей среды), для фильтрации шумов, которые могут быть введены регулятором 364 напряжения. Инициатор 334 включает в себя выходной импеданс, Ron, R346, включенный между комплементарными выходными элементами 342 и 344 и контактной площадкой 352. Конструкция системы 304 обеспечивает хорошо управляемые уровни Ron и выходного напряжения. Кроме того, уровни выходного напряжения можно настраивать путем регулирования выхода регулятора 364 напряжения.

На фиг. 3С показана блок-схема варианта осуществления системы, имеющая регуляторы напряжения, соединенные для уменьшения колебаний напряжения, как в отношении низкого опорного напряжения, так и в отношении высокого опорного напряжения выходного сигнала. Система 306 может представлять собой один пример варианта осуществления системы 200. Передатчик 310 представляет собой локальное устройство, и приемник 320 представляет собой удаленное устройство. Для передачи приемник 320 представлен в системе 306, как импеданс R322 нагрузки, который может составлять нагрузку для напряжения общего режима или VDD. Передатчик 310 включает в себя предварительный инициатор 332 для обеспечения управления и подачи сигналов для инициатора 334, для возбуждения и вывода сигнала передачи по линии 354 передачи через контактную площадку 352. Инициатор 334 включает в себя элемент 342 подъема напряжения и элемент 344 опускания напряжения. Элемент 344 представляет собой элемент n-типа (например, NMOS), который опускает напряжение в линии 354 передачи для генерирования низкого логического сигнала. Элемент 342 представляет собой элемент р-типа (например, PMOS), который поднимает напряжение в линии 354 передачи для генерирования высокого логического сигнала.

Передатчик 310 включает в себя регулятор 366 напряжения для понижения передаваемого напряжения высокого уровня от VDD до VDDTX, который представляет собой VDD минус падение напряжения на регуляторе 366 напряжения. В одном варианте осуществления передатчик 310 включает в себя обходной путь для обхода регулятора 366 напряжения (не представлен в явном виде). Передатчик 310 также включает в себя регулятор 368 напряжения для повышения низкого уровня напряжения передачи от VSS до VSSTX, который представляет собой VSS плюс напряжение регулятора 368 напряжения. В одном варианте осуществления передатчик 310 включает в себя обходной путь для обхода регулятора 368 напряжения (не показан в явном виде). Конденсатор может быть включен между VDDTX и VSSTX для фильтрации шумов выходного сигнала. Инициатор 334 не представлен в явном виде, как включающий в себя выходной импеданс, но выходной импеданс может быть предусмотрен. Уровни выходного напряжения инициатора 334 могут быть отрегулированы как в отношении высокого напряжения, так и в отношении низкого напряжения.

Система 306 может использоваться как вариант осуществления выходного инициатора WIDEIO, а также выходного инициатора LPDDR3 и применима для любого I/O, где колебание напряжения достигает VDD/2. Используя WIDEIO, известные конструкции генерируют на контактной площадке 352 напряжение, достигающее уровней напряжения питания (от VSS до VDD). При использовании LPDDR3 приемник ожидает общий режим VDD/2. Инициатор потребляет энергию, равную CVF (где С представляет собой емкость, V представляет напряжение и F представляет собой частоту сигнала). Стандарты JEDEC, такие как спецификация для LPDDR3 и предложенная спецификация для WIDEIO, разрешают колебания напряжения на контактной площадке от приблизительно 0,2*VDD до 0,8*VDD, так чтобы оно находилось в пределах допустимых требований. Однако в известных конструкциях напряжение достигает полного напряжения питания. Если регуляторы 366 и 368 напряжения будут установлены на 20% VDD, тогда выходное колебание напряжения все еще будет соответствовать стандартам, при уменьшении потребления энергии на 40% по сравнению с колебанием от 0 до VDD. В качестве альтернативы, регуляторы 366 и 368 напряжения могли бы быть установлены на разные значения, и не обязательно требуется устанавливать для получения равного шага напряжения. Следует понимать, что регуляторы 366 и 368 напряжения могут быть выполнены с возможностью работы симметрично (например, регулируя колебание напряжения на равные величины) для сохранения общего режима VDD/2 для приемника 320.

В варианте осуществления для WIDEIO схема приемника обычно воплощена как простой инвертор. Таким образом, потребление энергии за счет утечки увеличивается экспоненциально, когда колебания на контактной площадке 352 напряжения не достигают полного напряжения питания. Использование обходных путей для подъема напряжения на контактной площадке 352 до опорного напряжения питания (VDD или VSS) во время периодов простоя может уменьшить потребление энергии за счет утечки. Во время периодов высокой активности, когда преобладает мощность CVF, система 306 может регулировать размах выходного напряжения, уменьшая его для экономии энергии. Во время периодов простоя, когда преобладает энергии утечки, система 306 может выполнять обход регуляторов напряжения, чтобы обеспечить размах напряжения на контактной площадке 352 до полного напряжения питания, что позволяет уменьшить или устранить утечку. В одном варианте осуществления обходные пути могут быть воплощены как слабые пути подъема/понижения напряжения, для подъема напряжения на контактной площадке 352 до VDD/VSS во время периодов простоя. Обычно обходной путь может быть воплощен либо как путь с малым импедансом для обеспечения равенства выходного напряжения опорному напряжению вместо смещения регулятора напряжения, или как путь с высоким импедансом (например, силовой вентиль).

В любом варианте осуществления на любой из фиг. 3А, 3В или 3С система тестирования может дополнительно быть добавлена для программирования размаха выходного напряжения на основе конкретного изготовленного устройства (например, регулируя операцию устройства на месте установки). Таким образом, точные целевые значения VSSTX и/или VDDTx могут быть настроены системой тестирования на основе оценки высоты и/или ширины глазковой диаграммы для мощности. Несимметричное значение VSSTX и VDDTX могло бы обеспечить для системы возможность выравнивания запасов напряжения на высокой и низкой стороне, дополнительно уменьшая энергию. Такие технологии дополнительно описаны ниже.

На фиг. 4 показана блок-схема варианта осуществления подсистемы памяти, имеющей систему тестирования, которая обеспечивает тестирование в системе для управления размахом выходного напряжения. Конкретный размах выходного напряжения может быть рассчитан для определенного устройства во время работы, для определения компромиссов между высотой и/или шириной глазковой диаграммы в общей мощности. В то время как, в частности, представлена подсистема 400 памяти, следует понимать, что другая подсистема электронного устройства, в которой используется передача данных между устройствами, в равной степени может использоваться. Подсистема 400 памяти может включать в себя запоминающее устройство 410, систему 420 тестирования, логику 430 регулирования параметра, логику 440 измерения и логику 450 поиска. Такая функциональная логика может относиться к аппаратным средствам, программному обеспечению, встроенному программному обеспечению или их комбинации. Функциональная логика также может быть воплощена непосредственно в SoC (система на кристалле) или может быть удаленной и может связываться через отдельный интерфейс I/O.

Запоминающее устройство 410 представляет одно или больше устройств накопителя в подсистеме памяти. Система 420 тестирования обеспечивает тестирование передачи данных с запоминающим устройством 410 для определения, как установить рабочие параметры I/O в отношении связи с запоминающим устройством 410. Помимо других рабочих параметров I/O система 420 тестирования может определять специфичные установки регулятора напряжения для уменьшения колебания напряжения на выходе конкретного запоминающего устройства 410 (или другого приемного устройства из устройства передачи). В одном варианте осуществления система 420 тестирования включает в себя контур 422 тестирования, который представляет контур для выполнения тестирования. В частности, в одном варианте осуществления тестирование и измерение выполняются итеративно в контуре 422 для определения, как запоминающее устройство 410 работает в различных условиях. В одном варианте осуществления система 420 тестирования включает в себя логику экстраполяции (не представлена в явном виде), которая может использоваться для экстраполяции рабочей характеристики (например, рабочей характеристики в наихудшем случае) запоминающего устройства 410 на основе множества измерений для разных установок параметров. В одном варианте осуществления система 420 тестирования включает в себя логику корреляции (не показана, в частности), которая может использоваться для коррелирования множества результатов тестов друг с другом, для уменьшения или компенсации шумов в результатах тестов.

Логика 430 регулирования параметра представляет логику для изменения параметра рабочих характеристик. В одном варианте осуществления логика 430 представляет логику, которая регулирует значение регулятора напряжения или регулирует опорное напряжение для запоминающего устройства 410. Регуляторы напряжения могут включать в себя схемы переменного выхода для обеспечения переменного напряжения, для регулирования колебания выходного напряжения в ответ на логику управления. В одном варианте осуществления логика 430 представляет логику, которая регулирует один или более скрытых параметров. Например, логика 430 может регулировать электрические параметры, такие как Ron (выходной импеданс), Rodt (импеданс завершения на кристалле), скорость нарастания выходного напряжения, выравнивание, центровка по времени между стробами данных, частота или другие электрические параметры. В одном варианте осуществления логика 430 представляет логику, которая регулирует один или более параметров частоты. Например, логика 430 может регулировать параметры, относящиеся к любому из скрытых параметров, описанных выше, или к другим временным параметрам, время на отправку и возвращение или другие параметры I/O. Задержка и/или частота могут влиять на установку для регулятора напряжения.

В одном варианте осуществления логика 430 регулирования параметра составляет часть контроллера памяти, и влияет на установки конфигурации в контроллере памяти, которые управляют задержкой. В одном варианте осуществления логика 430 существует за пределами контроллера памяти, например в механизме тестирования, рядом с контроллером памяти. В одном варианте осуществления логика 430 обеспечивает регулировку контроллером памяти установок в самом запоминающем устройстве, такую как варианты конфигурации установок. В одном варианте осуществления логика 430 регулировки параметра может регулировать частоту, на которой работает подсистема памяти с мелким размером шага гранулярности. Система 420 тестирования определяет рабочие установки, специфичные для подсистемы 400 памяти на основе тестирования. В подсистеме 400 памяти выходные инициаторы существуют в контроллере памяти и включают в себя регулятор (регуляторы) напряжения для регулировки размаха напряжения, в соответствии с любым вариантом осуществления, описанным здесь.

Логика 440 измерения представляет логику, которая измеряет один или более индикаторов рабочих характеристик. Например, логика 440 может измерять ширину глазковой диаграммы сигнала, высоту глазковой диаграммы сигнала или оба эти параметра. В одном варианте осуществления логика 440 измеряет двумерную версию ширины/высоты глазковой диаграммы путем измерения других углов, чем 0 или 90 градусов. В одном варианте осуществления логика 440 измеряет потребление энергии подсистемой 400 памяти. Следует понимать, что установки регулируются логикой 430 регулирования параметра в соответствии с гранулярностью измерений для логики 440 измерений (то есть изменения установки параметра достаточны для того, чтобы получить обнаруживаемую разность). Логика 450 поиска представляет логику, которая определяет по измеренным значениям, какие установки следует использовать для I/O с запоминающим устройством 410. В одном варианте осуществления логика 440 измерения используется для генерирования одной или более представительных кривых рабочих характеристик для конкретной подсистемы 400 памяти, проходящей испытание. На основе представительных кривых логика 450 поиска может выполнять функцию поиска для определения, какие установки следует использовать для удовлетворения лучших рабочих характеристик, по меньшей мере, для одного параметра, в то время, как, по меньшей мере, поддерживается требуемая (стандартом или конфигурацией) рабочая характеристика для других. Логика 450 поиска может включать в себя любую из N-мерной логики поиска, 1-мерной логики поиска (для выполнения n 1-мерных поисков), логику поиска линейного совпадения, логику поиска квадратичного совпадения, логику поиска со скорейшим спуском, логику поиска с совпадением кривой или другие. Следует понимать, что n представляет целое число, обозначающее количество независимых параметров для поиска. Логика 450 поиска может также комбинировать множество измерений вместе, для того чтобы либо уменьшить шумы повторяемости или экстраполировать до условий наихудшего случая. В одном варианте осуществления администратор может определять, какие условия (мощность I/O, частота I/O, или задержка I/O) представляют собой наиболее существенную характеристику для развертывания системы для подсистемы 400 памяти, и может запускать тестовые операции для улучшения этой конкретной целевой характеристики.

Мощность I/O относится к мощности, используемой для передачи данных между устройствами, и составляет существенное количество энергии, потребляемой во многих электронных устройствах. Задержка I/O влияет на длительность, требуемую для доступа к запоминающему устройству, для транзакции доступа. Малая задержка I/O может привести к более быстрому доступу, и, таким образом, к улучшенным рабочим характеристикам в системе, в результате более быстрого получения данных. Частота I/O влияет на длительность, требуемую для доступа к запоминающему устройству для транзакции доступа. Более высокая частота I/O может привести к более широкой полосе пропускания и, таким образом, к улучшенным рабочим характеристикам в системе, в результате более быстрого получения данных. Более широкая полоса пропускания позволяет выполнить больше операций в течение заданного периода времени, что позволяет для системы с ограниченными данными работать с более высокими характеристиками. Это также позволяет уменьшить потребляемую энергию путем уменьшения количества времени, в течение которого I/O является активным, и увеличить количества времени, в течение которого I/O находится в состоянии низкой мощности.

В настоящее время рабочей характеристикой устройства в отношении мощности I/O, с задержки I/O и частоты I/O управляют фиксированными установками значения, которые обеспечивают функциональность на определенном уровне DPM (дефект на миллион), но не достигают самой низкой возможной рабочей задержки I/O для индивидуального, определенного устройства. В одном варианте осуществления, как описано здесь, система тестирования эмпирически тестирует и определяет установки, которые могут устанавливать рабочую мощность, задержку и/или частоту для определенного устройства, все еще поддерживая цели DPM. Каждая установка может влиять на или на нее может влиять уровень, на который должен быть установлен регулятор напряжения для обеспечения уменьшенного колебания выходного напряжения. Система 420 тестирования эмпирически может тестировать, какие установки следует использовать для регулятора напряжения, во время достижения требуемой рабочей характеристики для разных результатов измерения при осуществлении связи.

Для любой целевой рабочей характеристики I/O (например, мощность I/O, задержка I/O, частота I/O) система тестирования может регулировать любое количество параметров цепи I/O, которые влияют на целевые рабочие характеристики. Система тестирования может регулировать частоту, например, используя делитель N-фракционала в схеме PLL (с фазовой автоподстройкой частоты), который может регулировать частоту только для подсистемы памяти, вместо вычислительного устройства в целом. Другие способы для регулировки частоты подсистемы памяти также будут понятны для специалиста в области систем повышения тактовой частоты процессора. Система тестирования затем измеряет один или более рабочих запасов (например, временные характеристики, максимальную частоту и/или напряжение) для каждой установки. Система тестирования выполняет поиск на основе измеренных значений для идентификации установок, которые поддерживают минимальные требования (например, установок, которые позволяют устройству удовлетворять требованиям DPM) при улучшении рабочих характеристик для целевых рабочих характеристик. Операции системы тестирования, можно сказать, "оптимизируют" систему. Следует понимать, что "оптимизация" не обязательно относится к абсолютным наилучшим возможным рабочим характеристикам. Оптимизация может, вместо этого, относиться к улучшению или обеспечению максимальных рабочих характеристик в отношении определенных условий, или в определенных обстоятельствах, или в пределах определенных ограничений.

Тестирование создает напряженные условия для запоминающего устройства, учитывая один или больше рабочих параметров, представляющих интерес, как представлено описанными выше примерами. Следует понимать, что другие рабочие параметры могут быть оценены системой тестирования. С одной перспективы, запоминающее устройство и подсистема памяти (или другие подсистемы), в частности, тестируют в системе для определения, может ли подсистема работать за пределами спецификации или стандарта, применимого для подсистемы памяти и запоминающего устройства в отношении I/O. Тестирование может быть выполнено на основе только самой системы, без необходимости использования внешнего тестового оборудования.

Что касается тестирования, система тестирования, как упомянуто здесь, включает в себя аппаратные элементы, расположенные в и/или рядом с контроллером памяти (например, на совместно используемом пространстве кристалла, на SoC (система на кристалле)) или в другом целевом устройстве, характеристиками I/O которого требуется управлять, используя регуляторы напряжения, для уменьшения выходного колебания напряжения. Система тестирования может создать точные комбинации ввода/вывода (ввод-вывод), которые создают точные комбинации I/O (входа-выхода), в результате которых возникают индуцированные I/O шумы источника питания, взаимная помеха межу символами (ISI), поперечные помехи сигнала и/или другие состояния. Любые из этих эффектов могут быть сформированы путем точного управления данными на каждой из дорожек I/O, структурой каждой из дорожек команды, и/или как сигналы данных выравниваются друг с другом на дорожках.

На фиг. 5 показана блок-схема варианта осуществления контроллера памяти и подсистемы связи запоминающего устройства с регулировкой напряжения для управления размахом напряжения сигнала. В одном варианте осуществления система 500 включает в себя подсистему памяти, включающую в себя контроллер 530 памяти и запоминающее устройство 550. Система 500 представляет производственную систему или систему, в которой запоминающее устройство 550 установлено для использования потребителем. Система 500 включает в себя аппаратную платформу (не показана в явном виде), на которой расположен хост процессор 502, а также подсистему памяти, включающую в себя контроллер 530 памяти и запоминающее устройство 550. BIOS (базовая система ввода/вывода) 520 или эквивалентное встроенное программное обеспечение, для инициализации системы, включая в себя подсистему памяти, также находится на аппаратной платформе.

Хост процессор 502 выполняет, помимо прочего, хост операционную систему (OS) 510. Хост OS 510, в общем, обеспечивает управление операциями системы 500 во время работы. Хост OS 510 предоставляет программное обеспечение для аппаратных средств и аппаратных средств для программных интерфейсов, чтобы обеспечить для пользователя возможность взаимодействовать с системой 500. BIOS 520 обеспечивает управление запуском в системе 500, до тех пор пока не будет загружено хост устройство OS 510.

Хост OS 510 обеспечивает запросы доступа к памяти для контроллера 530 памяти, для доступа к запоминающему устройству 550, для считывания и/или записи данных. Аналогично, BIOS 520 может обеспечивать запросы доступа к памяти для контроллера 530 памяти. Контроллер 530 памяти обращается к запоминающему устройству 550, в ответ на запросы доступа к данным. В одном варианте осуществления тестовый механизм 540 генерирует запросы доступа к данным и/или транзакции доступа для контроллера 530 памяти для передачи в запоминающее устройство 550. В одном варианте осуществления тестовый механизм 540 может непосредственно предоставлять тестовые данные в запоминающее устройство 550.

В одном варианте осуществления BIOS 520 инициирует тест через тестовую программу 522 и обращается к тестовому механизму 540 для генерирования тестовых данных 542 для обеспечения возможности связи теста с запоминающим устройством 550 через контроллеры 530 памяти. В одном варианте осуществления тестовые данные 542 представляют данные, сохраненные во время мониторинга тестируемого запоминающего устройства 550, такие как данные, которые используются для идентификации рабочих характеристик запоминающего устройства 550 при разных установках параметров. В ответ на идентификацию рабочих характеристик запоминающее устройство 500 может динамически устанавливать рабочие параметры для I/O с запоминающим устройством 550. Динамическая установка рабочих параметров позволяет системе устанавливать рабочую характеристику в соответствии с определенным устройством, вместо использования стандартных или принятых по умолчанию установок, обычно применяемых для всех устройств. Таким образом, конкретная система не ограничена рабочей характеристикой возможной системы наихудшего случая.

В одном варианте осуществления конфигурация 552 представляет механизм в запоминающем устройстве 550, такой как регистр или другой механизм конфигурации, который содержит I/O установки для TX/RX 554. TX/RX 554 представляет схемы передачи и приема запоминающего устройства 550, которые управляют характеристиками I/O запоминающего устройства 550. VR 536 представляет один или больше регуляторов напряжения, используемых для управления выходным колебанием напряжения TX/RX 554. В одном варианте осуществления конфигурация 532 представляет механизм в контроллере 530 памяти, который содержит I/O установки для TX/RX 534. TX/RX 534 представляет схему передачи и приема контроллера 530 памяти, который управляет характеристиками I/O для запоминающего устройства 550. Конфигурация 532 также может сохранять установки для VR 536 для регулирования выходного колебания напряжения TX/RX 534. Следует понимать, что другие компоненты также могут быть соединены с запоминающим устройством 550 через схемы TX/RX и могли бы иметь аналогичные механизмы конфигурации.

Конфигурация 532 и 522 может включать в себя установки для функции передачи и приема.

Например, различные установки могут применяться для управления временными характеристиками, мощностью, уровнями выходного напряжения, уровнями регулятора напряжения, выходным импедансом, скоростью нарастания выходного напряжения или другими параметрами передачи. На стороне приема нагрузочным резистором на кристалле (ODT), усилением усилителя, выравниванием и другими параметрами приемника можно управлять через различные установки. Механизм 540 тестирования может выполнять тесты при разнообразных установках параметров передачи и приема, может выполнять измерения и определять рабочие запасы для системы (например, как система работает по сравнению с требуемыми рабочими характеристиками). Рабочие запасы могут быть определены, например, путем установления минимального порогового значения (которое в одном варианте осуществления включает в себя защитную полосу частот) для разных рабочих характеристик. Таким образом, определение рабочих запасов может включать в себя определение фактических рабочих характеристик по сравнению с пороговыми значениями. Пороговое значение может быть рассчитано динамически на основе множества измерений при разных рабочих напряжениях, температурах или при разном тестировании, и может быть экстраполировано для условий наихудшего случая. Кроме того, одно или больше пороговых значений могут быть разными для каждого из разных рабочих запасов, которые тестируют.

В одном варианте осуществления система 500 сконфигурирована для уменьшения мощности I/O, и в этом случае конфигурации 532 и 522 включают в себя, по меньшей мере, возможность изменять параметры схемы I/O, которые влияют на использование энергии I/O. Примеры параметров включают в себя, но не ограничены этим, значения нагрузки, смещение, скорость нарастания выходного напряжения, колебание напряжения инициатора, импеданс инициатора и рабочее напряжение (включая в себя установку для VR 536). В таком варианте осуществления механизм 540 тестирования генерирует содержание теста, которое стимулирует I/O с чем-то имеющим известную корреляцию со стимулом наихудшего случая. Механизм 540 тестирования измеряет рабочее напряжение и/или запас временных характеристик для различных установок схемы. Механизм 540 тестирования затем анализирует измеряемые данные запаса параметра схемы (например, через функцию поиска, как описано здесь) и определяет самую низкую рабочую мощность I/O, которая все еще поддерживает установленное требование продукта DPM для тестированных и измеренных параметров и установок.

В одном варианте осуществления система 500 выполнена с возможностью повышения частоты I/O, и в этом случае конфигурация 532 и 522 включает в себя, по меньшей мере, возможность изменения параметров схемы I/O, которые влияют на частоту I/O. Примеры параметров включают в себя, но не ограничены этим значения нагрузки, смещение, скорость на расстоянии выходного напряжения, инициаторы текущего режима, и рабочее напряжение (включая в себя установку для VR 536). На параметры частоты могут влиять компоненты, которые могут включать в себя, но не ограничены этим DLL (замкнутые контуры задержки), PLL (замкнутые контуры по фазе) и/или микросхемы тактовой частоты. В таком варианте осуществления механизм 540 тестирования генерирует содержание тестирования, которое стимулирует I/O с чем-то имеющим известную корреляцию со стимулом наихудшего случая. Механизм 540 тестирования измеряет рабочее напряжение, рабочую частоту и/или запасы временных характеристик для различных установок схемы. Механизм 540 тестирования затем анализирует измеренные данные запаса параметра схемы (например, через функцию поиска) и определяет самую высокую рабочую частоту I/O, которая все еще поддерживает установленные требования DPM продукта для тестируемых и измеренных параметров и установок.

В одном варианте осуществления система 500 выполнена с возможностью уменьшения задержки I/O, и в этом случае конфигурация 532 и 522 включает в себя, по меньшей мере, возможность изменения параметров схемы I/O, которые влияют на задержку I/O. Примеры параметров включают в себя, но не ограничены ими, значения оборота указателя FIFO (буфер первым прибыл - первым выведен), счетчиков задержки на прохождение сигналов в прямом и обратном направлении, значения нагрузки, смещение, скорость нарастания выходного напряжения и/или инициаторы текущего режима. В таком варианте осуществления механизм 540 тестирования генерирует содержание теста, которое стимулирует I/O с чем-то имеющим известную корреляцию со стимулом наихудшего случая. Механизм 540 тестирования измеряет рабочее напряжение и/или запас по времени для различных установок схемы. Механизм 540 тестирования затем анализирует измеренные данные запаса параметра схемы (например, через функцию поиска, как описано здесь) и определяет самую малую рабочую задержку I/O, которая все еще поддерживает установленные требования продукта DPM для тестированных и измеренных параметров и установок.

Следует понимать, что исторически множество или все рабочие параметры установлены как статические значения для операции. В отличие от этого, как описано здесь, механизм 540 тестирования тестирует и измеряет установки параметров, которые повышают рабочие характеристики системы 500. Механизм 540 тестирования выполняет функцию поиска, которая может включать в себя любую или множество известных технологий поиска. Например, могут использоваться квадратичное совпадение, линейное совпадение, N-мерный поиск, n 1-мерных поисков, генетический поиск, скорейший спуск, совпадение кривой, или другие технологии, или некоторые комбинации. Размеры поиска зависят от манипуляций установками параметров. В одном варианте осуществления n измерений поиска включают в себя N параметров, которые влияют как на операцию передачи, так и на операцию приема. В одном варианте осуществления n измерений включают в себя X параметров передачи на Y параметров приема, где N равно комбинации уникальных параметров X и Y для тестирования. Механизм 540 тестирования может запускать тест, измерять рабочий запас, надежность теста, регулировать параметры и повторять.

На фиг. 6А показана блок-схема варианта осуществления схемы импеданса подъема напряжения с множеством выводов. В одном варианте осуществления выходной инициатор обеспечивает получение разного импеданса подъема напряжения, используя переключение по-разному выводов схемы подъема напряжения или схемы опускания напряжения. Схема 602 подъема напряжения включает в себя N переключателей, 610-0 - 610-N и соответствующее количество резисторов R620-0 - R620-N. Каждая комбинация переключателя 610-n и резистора R620-n представляет ножку схемы 602 подъема напряжения. Предварительный инициатор 630 может выбирать количество ножек для подключения, для формирования требуемого импеданса. В одном варианте осуществления каждый резистор имеет приблизительно эквивалентные размеры (например, одинаковые, за исключением вариации при обработке), и требуемое количество резисторов включают параллельно, чтобы получить требуемый импеданс. В альтернативном варианте осуществления один или больше из резисторов имеет другое значение, которое можно избирательно комбинировать для регулирования, для получения требуемого выходного импеданса. Следует понимать, что все поднимающие напряжение ножки соединены параллельно с контактной площадкой 640, которая представляет выходную точку для схемы 602 подъема напряжения. Как представлено, все ножки подъема напряжения могут быть соединены с VDD через VR 670, который представляет собой компоненты регулировки напряжения для регулировки максимального выходного напряжения, начиная от VDD до более низкого значения. VR 670 может быть переменным, чтобы обеспечить возможность регулировки выхода, специфичного для определенного устройства, в котором интегрирована схема 602.

На фиг. 6В показана блок-схема варианта осуществления схемы импеданса с множеством ножек для подъема напряжения. В одном варианте осуществления выходной инициатор обеспечивает получение разного импеданса опускания напряжения, используя переключение разного количества ножек схемы опускания напряжения или системы опускания напряжения. Схема 604 опускания напряжения включает в себя М переключателей 660-0 - 660-m и соответствующее количество резисторов R650-0 - R650-m. Каждая комбинация переключателя 660-m и резистора R650-n представляет собой ножку схемы 604 опускания напряжения. В одном варианте осуществления М представляет собой такое же число, как и N. В одном варианте осуществления существует разное количество ножек подъема напряжения и ножек опускания напряжения. Как представлено, все ножки опускания напряжения могут быть соединены с VSS через VR 680, которые представляют собой компоненты регулировки напряжения, для регулировки минимального выходного напряжения, начиная от VSS до более высокого значения. VR 680 может быть переменным для обеспечения возможности регулировки выхода, специфичного для определенного устройства, в котором интегрирована схема 604.

Предварительный инициатор 630 может выбирать количество ножек для подключения для формирования требуемого импеданса. В одном варианте осуществления каждый резистор имеет приблизительно эквивалентный размер (например, одинаковый, за исключением образующегося при обработке), и требуемое количество резисторов включают параллельно для получения требуемого импеданса. В альтернативном варианте осуществления один или больше из резисторов имеет другое значение, которое можно избирательно комбинировать для регулировки, для получения требуемого выходного импеданса. Отдельные резисторы опускания напряжения, могут иметь или могут не иметь одинаковое значение, как и отдельные резисторы подъема напряжения. Следует понимать, что все ножки, опускающие напряжение, подключены параллельно к контактной площадке 640, которая представляет выходную точку для схемы 604 опускания напряжения.

Следует также понимать, что схема 602 подъема напряжения, и схема 604 опускания напряжения соединены с контактной площадкой 640. Традиционные способы достижения разных импедансов, в которых используется добавление большего количества ножек для одной из или для обеих из схемы 604 опускания напряжения или схемы 602, подъема напряжения. Однако добавление большего количества ножек увеличивает емкость контактной площадки (обычно называется PAD САР или Cpad). Увеличение паразитного значения PAD САР может отрицательно влиять на временные характеристики и характеристики полосы пропускания. Кроме того, добавление большего количества ножек требует больше схем/логики в предварительном инициаторе 630, что требует больше энергии. Вместо добавления большего количества ножек или ножек опускания напряжения предварительный инициатор 630 может избирательно включать пропорцию верхних и нижних ножек для достижения требуемого выходного импеданса. Таким образом, разные конфигурации выходного импеданса могут быть получены без увеличения количества ножек в системе, что означает, что PAD САР остается без изменений и временные характеристики могут поддерживаться.

Следует понимать, что количество ножек подъема напряжения и/или ножек опускания напряжения, которые должны быть включены, зависит от конструкции системы, а также от требуемого выходного импеданса. Количество включаемых ножек подъема напряжения разное для логически низкого напряжения и логически высокого напряжения. В одном варианте осуществления множество ножек подъема напряжения может быть включено и они могут быть оставлены включенными постоянно, пока инициатор выполняет возбуждение линии передачи, и при этом только другие верхние ножки и нижние ножки остаются включенными и выключенными для того, чтобы различать между единицей и нулем, или логически высоким уровнем и логически низким уровнем. Таким образом, предварительный инициатор может включать определенную пропорцию верхних и нижних ножек для генерирования эффективного выходного импеданса. В одном варианте осуществления выбранная пропорция представляет собой пропорцию, которая обеспечивает то, что эффективный выходной импеданс для логически низкого напряжения будет таким же, как и эффективный выходной импеданс для логически высокого напряжения. Конкретный эффективный выходной импеданс может влиять на значение, используемое в VR 670 и/или VR 680 для установки выходных пороговых значений колебания выходного напряжения.

На фиг. 7 показана блок-схема последовательности операций варианта осуществления обработки для вывода сигнал с уменьшенным размахом напряжения. В одном варианте осуществления компонент хост платформы генерирует сигнал для передачи в другой компонент через линию передачи, 702. Компоненты составляют интерфейс через линию передачи, такую как дорожка или провод. Компонент, который имеет сигнал для передачи, представляет собой передатчик, предназначенный для обмена сигналом, и компонент, в который он передает сигнал, представляет собой приемник, предназначенный для обмена сигналами. В одном варианте осуществления передатчик предоставляет сгенерированный сигнал на свой последовательный выходной участок или приемопередатчик, который может составлять или может включать в себя схему интерфейса линии электропередачи, 704. Интерфейс линии передачи включает в себя инициатор для возбуждения сигнала в линии передачи. Инициатор возбуждает линию передачи до логически высокого и логически низкого уровня для передачи сигнала в приемник.

Схема интерфейса линии передачи включает в себя регулятор напряжения на ножке подъема напряжения, или на ножке опускания напряжения, или на обеих ножках опускания и подъема напряжения. В одном варианте осуществления регулятор (регуляторы) напряжения включают избирательно, например включают только для возбуждения выхода инициатора. Если регулятор (регуляторы) напряжения должен быть включен, схема интерфейса линии передачи включает регулятор (регуляторы) напряжения, 706.

Схема интерфейса линии передачи обрабатывает сигнал для определения бита для передачи в приемник через линию передачи, 708. Если инициатор должен возбуждать логически высокий уровень, 710 ответвление ВЫСОКИЙ, схема интерфейса линии передачи повышает напряжение в линии передачи, используя элемент подъема напряжения до максимального напряжения передачи, 712. Максимальное напряжение передачи обычно представляет собой VDD в традиционных схемах, и может быть уменьшено регулятором напряжения между элементом подъема напряжения и VDD. Если инициатор должен возбуждать логически низкий сигнал, 710 ответвление НИЗКИЙ, схема интерфейса линии передачи уменьшает напряжение в линии передачи с элементом, понижающим напряжение до минимального напряжения передачи, 714. Минимальное напряжение передачи обычно представляет собой VSS в традиционных схемах, и его можно регулировать с помощью регулятора напряжения между элементом опускания напряжения и VSS.

Независимо от логически высокого и логически низкого уровня после возбуждения бита схема интерфейса линии передачи может определять, был ли передан последний бит, 718. Если последний бит не был передан, 716 ответвление НЕТ, схема интерфейса линии передачи обрабатывает следующий бит, 708, и повторяет выходную обработку. Если последний бит был передан, 716 ответвление ДА, схема интерфейса линии электропередачи, в случае необходимости, обходит и/или отключает регулятор напряжения, переводя его в состояние приема или в состояние простоя, 718.

На фиг. 8 показана блок-схема последовательности операций варианта осуществления обработки для эмпирического тестирования и обнаружения установок передачи данных, используя исчерпывающий поиск возможных значений. В то время, как здесь представлен пример подсистемы памяти, следует понимать, что может использоваться другая подсистема, где может использоваться связь с обменом компонентами, вместо подсистемы памяти. Таким образом, подсистема памяти представляет собой просто один пример системы, в которой устройства сообщаются друг с другом, где регулятор напряжения может использоваться для управления выходом или размахом напряжения передачи.

Изготовитель изготовляет устройство, включающее в себя аппаратную платформу хост устройства и подсистему памяти на платформе, 802. Тот же или другой объект (или изготовитель, или конечный пользователь) затем может соединять одно или больше из устройств памяти с подсистемой памяти в устройстве, 804. Один или более компонентов на платформе (например, такой как контроллер памяти) будет выполнять операции I/O с устройством памяти.

Механизм тестирования или система тестирования выполняют программу тестирования для нагрузочных испытаний запоминающего устройства (устройств) в системе для определения, какие установки требуется использовать для схем I/O. Система тестирования идентифицирует параметры схемы I/O, относящиеся к целевым рабочим характеристикам (например, мощность, временные характеристики), 806. Тестирование может быть выполнено в соответствии с любым описанным здесь вариантом осуществления. Механизм тестирования встроен в хост платформу и не требует внешнего тестового оборудования при выполнении тестирования. В одном варианте осуществления BIOS на платформе включает в себя программу тестирования или процедуру тестирования для выполнения, когда память соединяют с подсистемой памяти. Программа или процедура направляет механизм тестирования для выполнения тестирования, включая в себя измерение и анализ, для определения наилучшей установки, для определенной системы в пределах ограничений того, что тестируют. В одном варианте осуществления механизм тестирования инициирует из местоположения, удаленного для устройства, включающего в себя запоминающее устройство (устройства) для тестирования, например, через соединение по сети.

В одном варианте осуществления система тестирования выполняет итерации или выполняет циклические различные операции тестирования через каждый идентифицированный параметр цепи, 808. Система тестирования также может циклически выполнять операции, используя N разных установок любого заданного параметра (где N не обязательно является одинаковым для любого из множества параметров, предназначенных для тестирования), 810. Для каждой итерации тестирования подсистема памяти под управлением программы тестирования и/или системы тестирования, может регулировать или устанавливать одно или больше значений для соответствующих параметров схемы I/O, включая в себя установки регулятора напряжения для управления размахом выходного напряжения, 812.

В одном варианте осуществления система тестирования генерирует трафик теста со встроенным механизмом тестирования, 814. Содержание теста может соответствовать одиночному множеству тестов, которые тестируют разные предельные подходы в конструкции, функционально в одном или множестве состояний окружающей среды, таких как напряжение, температура, частота или другие состояния. В одном варианте осуществления система тестирования затем измеряет один или больше рабочих запасов целевой рабочей характеристики, 816. Система тестирования повторяет тестирование и измерение для каждой из разных установок, пока не будет тестирована последняя установка, 818 ответвление ДА. В одном варианте осуществления система тестирования выполняет итерации через каждый идентифицированный параметр I/O, который может влиять на рабочую характеристику I/O, представляющую интерес, до тех пор пока все параметры не будут тестированы, 820 ответвление ДА. До тех пор пока не будет достигнут последний параметр, 820 ответвление НЕТ, механизм тестирования продолжает итерацию для каждой из разных N установок, 810. Механизм тестирования может использовать разнообразные структуры нагрузочного испытания, как более подробно описано ниже, и эти структуры могут включать в себя LFSR, "жертва-агрессор", перекрестные помехи, IS I, шумы источника питания, напряжение источника питания или другие структуры.

В одном варианте осуществления система тестирования исполняет функцию поиска для определения значения для каждого параметра схемы I/O, для использования при выполнении рабочих операций тестируемой системы, 822.

Определенные значения должны представлять собой значения, при которых каждый параметр схемы I/O удовлетворяет минимальному пороговому значению для определенной системы, и улучшает рабочие характеристики, по меньшей мере, одного из параметров схемы I/O. Система тестирования затем может обеспечивать установку для системы, проходящей тестирование, рабочих значений для параметров схемы I/O, на основе результатов функции поиска, 824. Рабочие установки могут быть, в частности, определены с помощью функции поиска, или функция поиска может идентифицировать значение, и система может устанавливать рабочие установки несколько выше определенного значения. В одном варианте осуществления функция поиска добавляет явно выраженную защитную полосу. В одном варианте осуществления функция поиска может экстраполировать один или больше результатов измерений на основе множества тестов или условий окружающей среды для условий наихудшего случая, для минимизации какой-либо защитной полосы.

На фиг. 9 показана блок-схема варианта осуществления компьютерной системы, в которой может быть воплощено управление размахом напряжения. Система 900 представляет собой компьютерное устройство в соответствии с любым вариантом осуществления, описанным здесь, и может представлять собой переносной компьютер, настольный компьютер, сервер, игровую или развлекательную систему управления, сканер, копировальное устройство, принтер, устройство маршрутизации или коммутации или другое электронное устройство. Система 900 включает в себя процессор 920, который обеспечивает обработку, администрирование операциями и исполнение инструкций для системы 900. Процессор 920 может включать в себя любой тип микропроцессора, центральное процессорное устройство (CPU), ядро обработки или другие аппаратные средства обработки для обеспечения обработки для системы 900. Процессор 920 управляет общей работой системы 900 и может представлять собой или может включать в себя один или больше программируемых общего назначения или специального назначения микропроцессоров, цифровые сигнальные процессоры (DSP), программируемые контроллеры, специализированные интегральные схемы (ASIC), программируемые логические устройства (PLD) и т.п. или комбинацию таких устройств.

Подсистема 930 памяти представляет основную память системы 900 и обеспечивает временное сохранение кода, который должен быть выполнен процессором 920, или значений данных, которые должны использоваться при исполнении процедуры. Подсистема 930 памяти может включать в себя одно или больше запоминающих устройств, таких как постоянное запоминающее устройство (ROM), память типа флэш, одну или больше разновидностей оперативного запоминающего устройства (RAM), или другие запоминающие устройства, или комбинацию таких устройств. Подсистема 930 памяти содержит и принимает, помимо прочего, операционную систему (OS) 936 для обеспечения программной платформы для исполнения инструкций в системе 900. Кроме того, другие инструкции 938 сохранены и исполняются из подсистемы 930 памяти для обеспечения логики и обработки системы 900. OS 936 и инструкции 938 исполняются процессором 920.

Подсистема 930 памяти включает в себя устройство 932 памяти, при этом оно содержит данные, инструкции, программы или другие элементы. В одном варианте осуществления подсистема памяти включает в себя контроллер 934 памяти, который представляет собой контроллер памяти, в соответствии с любым вариантом осуществления, описанным здесь, и который включает в себя планировщик для генерирования и выработки команд в запоминающее устройство 932.

В одном варианте осуществления один или больше компонентов системы 900 включают в себя один или больше регуляторов напряжения, используемых для управления выходным напряжением интерфейса линии электропередачи. Регулятор (регуляторы) напряжения может включаться избирательно, и позволяет регулировать выход или колебание напряжения передачи. В одном варианте осуществления система 900 включает в себя механизм тестирования (не показан в частности), который может эмпирически тестировать передачу данных в системе, включая в себя тестирование установок значения для регулятора напряжения.

Процессор 920 и подсистема 930 памяти соединены с системой 910 шина/шина. Шина 910 представляет абстракцию, которая представляет собой одну или больше отдельных физических шин, линий/интерфейсов связи, и/или соединений из точки в точку, соединенных соответствующими мостиками, адаптерами и/или контроллерами. Поэтому, шина 910 может включать в себя, например, одну или больше из системной шины, шины межсоединения периферийных компонентов (PCI), шины HyperTransport или промышленной стандартной архитектуры (ISA), шины интерфейса малых компьютерных систем (SCSI), универсальной последовательной шины (USB) или шины по стандарту 1394 Института инженеров по электротехнике и радиотехнике (IEЕЕ) (обычно называется "Firewire"). Шина или шины 910 также могут соответствовать интерфейсам в сетевом интерфейсе 950.

Система 900 также включает в себя один или больше интерфейс (интерфейсов) 940 I/O (ввода/вывода), сетевой интерфейс 950, одно или больше внутреннее устройство (устройства) 960 накопителя большого объема, и периферийный интерфейс 970, соединенный с шиной 910. Интерфейс 940 I/O может включать в себя один или больше компонентов интерфейса, через которые пользователь взаимодействует с системой 900 (например, видео, аудио и/или алфавитно-цифровой интерфейс). Сетевой интерфейс 950 обеспечивает для системы 900 возможность обмена данными с удаленными устройствами (например, серверами, другими вычислительными устройствами) одной или больше сетей. Сетевой интерфейс 950 может включать в себя адаптер Ethernet, компоненты беспроводного взаимного соединения, USB (универсальную последовательную шину), или другие основанные на проводных или на беспроводных стандартах или частные интерфейсы.

Накопитель 960 может представлять собой или включать в себя любой обычный носитель для сохранения большого количества данных энергонезависимым способом, такой как один или больше магнитных, твердотельных или оптических дисков или их комбинации. Накопитель 960 содержит код или инструкции и данные 962 в постоянном состоянии (то есть, значение поддерживается, несмотря на перерыв питания в системе 900). Накопитель 960, можно, в общем, рассматривать, как "память", хотя память 930 представляет собой исполнительную или оперативную память для предоставления инструкции для процессора 920. В то время, как накопитель 960 является энергонезависимым, память 930 может включать в себя энергозависимую память (то есть, значение или состояние данных становится неопределенным, если происходит перерыв питания в системе 900).

Периферийный интерфейс 970 может включать в себя любой аппаратный интерфейс, не обязательно, в частности, упомянутый выше. Периферийное устройство, в общем, относится к устройствам, которые подключаются в зависимом состоянии от системы 900. Зависимое подключение представляет собой подключение, в котором система 900 обеспечивает программное обеспечение и/или аппаратную платформу, в которой исполняется операция, и с которой взаимодействует пользователь.

На фиг. 10 показана блок-схема варианта осуществления мобильного устройства, в котором может быть осуществлено управление колебанием напряжения. Устройство 1000 представляет собой мобильное вычислительное устройство, такое как компьютерное планшетное устройство, мобильный телефон или смартфон, электронный считыватель с возможностью беспроводной передачи или другое мобильное устройство. Следует понимать, что некоторые компоненты представлены в обобщенном виде, и не все компоненты такого устройства представлены в устройстве 1000.

Устройство 1000 включает в себя процессор 1010, который выполняет основные операции по обработке устройства 1000. Процессор 1010 может включать в себя одно или больше физических устройств, таких как микропроцессоры, процессоры приложения, микроконтроллеры, программируемые логические устройства или другое средство обработки. В одном варианте осуществления процессор 1010 включает в себя компоненты оптического интерфейса в дополнение к кристаллу процессора. Таким образом, кристалл процессора и фотонные компоненты находятся в одном и том же корпусе. Такой корпус процессора может составлять оптический интерфейс с оптическим разъемом в соответствии с любым описанным здесь вариантом осуществления.

Операции по обработке, выполняемые процессором 1010, включают в себя исполнение операционной платформы или операционной системы, в которой исполняются приложения и/или функции устройства. Операции по обработке включают в себя операции, относящиеся к I/O (вводу/выводу) с пользователем - человеком или с другими устройствами, операции, относящиеся к управлению питанием, и/или операции, относящиеся к подключению устройства 1000 к другому устройству. Операции по обработке также могут включать в себя операции, относящиеся к аудио I/O и/или I/O устройства отображения.

В одном варианте осуществления устройство 1000 включает в себя аудио подсистему 1020, которая представляет аппаратные средства (например, аудио аппаратные средства и аудио схемы) и программные компоненты (например, инициаторы, кодеки), ассоциированные с предоставлением аудиофункций для компьютерного устройства. Аудиофункций могут включать в себя вывод в громкоговоритель и/или головные телефоны, а также вход через микрофон. Устройства для таких функций могут быть интегрированы в устройство 1000 или могут быть подключены к устройству 1000. В одном варианте осуществления пользователь взаимодействует с устройством 1000 путем предоставления аудиокоманд, которые принимают и которые обрабатывает процессор 1010.

Подсистема 1030 отображения представляет аппаратные средства (например, устройства отображения) и программные компоненты (например, инициаторы), которые обеспечивают визуальное и/или тактильное отображение для пользователя, для взаимодействия с компьютерным устройством. Подсистема 1030 отображения включает в себя интерфейс 1032 отображения, который включает в себя определенный экран или аппаратное устройство, используемое для предоставления отображения для пользователя. В одном варианте осуществления интерфейс 1032 отображения включает в себя логику, отдельную от процессора 1010 для выполнения, по меньшей мере, некоторой обработки, относящейся к отображению. В одном варианте осуществления подсистема 1030 отображения включает в себя устройство с сенсорным экраном, которое обеспечивает как выход, так и вход для пользователя.

I/O контроллер 1040 представляет аппаратные устройства и программные компоненты, относящиеся к взаимодействию с пользователем. I/O контроллер 1040 может работать для администрирования аппаратными средствами, которые составляют часть аудиоподсистемы 1020 и/или подсистемы 1030 отображения. Кроме того, I/O контроллер 1040 иллюстрирует точку соединения для дополнительных устройств, которые соединяются с устройством 1000, через которые пользователь может взаимодействовать с системой. Например, устройства, которые могут быть присоединены к устройству 1000, могут включать в себя устройства микрофона, громкоговоритель или стереосистемы, видеосистемы или другое устройство отображения, клавиатуру или устройства кнопочной панели, или другие I/O устройства для использования с определенными приложениями, такими как считыватели карт или другие устройства.