Перекрестная ссылка на родственную заявку

Согласно 37 C.F.R. § 1.78, данная заявка является заявкой-частичным продолжением и притязает на приоритет ранее поданной заявки № 12/542976, поданной 18 августа 2009 г., под названием “An Integrated Circuit Including a Programmable Logic Analyzer with Enhanced Analyzing and Debugging Capabilities and a Method Therefor”, содержание которой, таким образом, включено посредством ссылки в полном объеме.

Область техники

[0001] Изобретение относится, в целом, к встроенному логическому анализатору и, в частности, к программируемому встроенному логическому анализатору для анализа электронной схемы.

Уровень техники

[0002] Логический анализатор - это электронный прибор, который используется для захвата и отображения сигналов данных электронной схемы. В общем случае логический анализатор захватывает сигналы данных, которые слишком быстры для наблюдения пользователем. Пользователь наблюдает сигналы данных, захваченные логическим анализатором, для эффективного анализа электронной схемы и для совершения упреждающих действий или для отладки на основании анализа.

[0003] Логические анализаторы можно, в широком смысле, разделить на внешние логические анализаторы и встроенные логические анализаторы. Встроенный логический анализатор в общем случае входит в состав программируемого логического устройства или интегральной схемы (ИС), например, комплексного программируемого логического устройства (CPLD), программируемой пользователем вентильной матрицы (FPGA), специализированной интегральной схемы (ASIC) и т.д. Встроенный логический анализатор обладает способностью захватывать большие объемы высокоскоростных сигналов данных в ИС.

[0004] Встроенный логический анализатор может включать в себя память для хранения захваченных сигналов данных. Обычно встроенный логический анализатор имеет возможность программирования для захвата и сохранения сигналов данных, указанных пользователем. Сигналы данных, сохраненные встроенным логическим анализатором, можно переносить на компьютер для дополнительного анализа. Сигналы данных, в общем случае, переносятся на компьютер через интерфейс, обеспеченный на ИС.

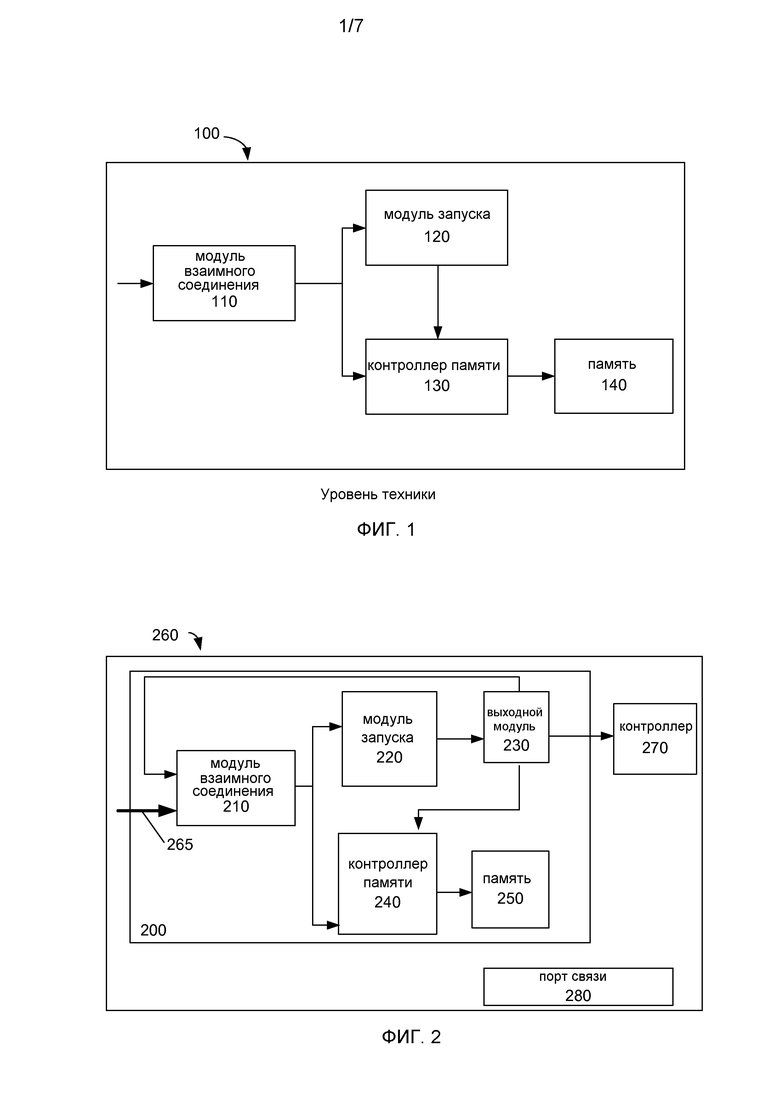

[0005] На фиг. 1 показана блок-схема традиционного встроенного логического анализатора (ELA) 100, входящего в состав интегральной схемы (не показан). ELA 100 включает в себя модуль 110 взаимного соединения для приема множества сигналов данных в интегральной схеме. Модуль 110 взаимного соединения имеет возможность программирования для выбора множества сигналов, подлежащих выборке, и по меньшей мере одного запускающего сигнала для задействования выборки из множества принятых сигналов. По меньшей мере один запускающий сигнал переносится в модуль 120 запуска. Модуль 120 запуска имеет возможность программирования для задания условия запуска и для определения, удовлетворяет ли по меньшей мере один запускающий сигнал условию запуска. В случае удовлетворения условия запуска, модуль 120 запуска инициирует процесс выборки. После инициирования процесса выборки, контроллер 130 памяти начинает производить выборку множества сигналов, подлежащих выборке, из модуля 110 взаимного соединения. Выборочные сигналы могут храниться в памяти 140 для дополнительного анализа. Таким образом, ELA 100 выполняет общий код, приведенный ниже:

IF (<условие запуска>) THEN (выполнять выборку сигналов(X)),

[0006] в котором условие запуска представляет собой любую логическую операцию или последовательность логических операций, и сигналы(X) представляют собой множество сигналов, подлежащих выборке, из модуля 110 взаимного соединения. Согласно коду, исполняемому ELA 100, в случае удовлетворения условия запуска, ELA 100 совершает выборку по меньшей мере одного выборочного сигнала и сохраняет выборочный сигнал в памяти 140.

[0007] Однако традиционные ELA ограничены тем, что совершают выборку в случае удовлетворения условия запуска. Кроме того, традиционные ELA не выполняют захват, анализ и/или отладку программных данных или сигналов данных программно-аппаратного обеспечения в ИС, и для анализа этих типов данных может потребоваться дополнительный(е) инструмент(ы). Дополнительно, для программирования ELA или для анализа данных, хранящихся в ELA, пользователю необходимо присутствовать на рабочей станции, где установлен ELA.

[0008] Таким образом, для устранения вышеупомянутых проблем, желательно обеспечить ELA с расширенными возможностями анализа и отладки.

Сущность изобретения

[0009] Примерные варианты осуществления настоящего изобретения преодолевают недостатки известных логических анализаторов и, таким образом, удовлетворяют значительную потребность в механизме для эффективного тестирования и отладки системы. В соответствии с примерным вариантом осуществления, раскрыта интегральная схема, включающая в себя логический анализатор, имеющий первый вход, принимающий множество сигналов и первый выход для обеспечения выбранных выборок сигналов, поступающих на первый вход; и первый блок, имеющий первый вход, подключенный к логическому анализатору для приема одного или более сигналов, поступающих на его первый вход, и выход, подключенный к логическому анализатору для непосредственной подачи на него отдельного набора из одного или более сигналов, который основан на одном или более сигналах на первом входе первого блока, согласно заранее определенной функции, причем заранее определенная функция является конфигурируемой. За счет подачи на логический анализатор отдельного набора сигналов, который основан на одном или более сигналах поступающих на первый вход логического анализатора, первый блок обеспечивает дополнительную гибкость, позволяя эффективно осуществлять операции тестирования и отладки, как на уровне системы, так и на уровне подсистем.

[0010] Согласно другому примерному варианту осуществления, раскрыта система, включающая в себя интегральную схему, имеющую встроенный блок логического анализатора с входом для приема множества сигналов и блоком запускающих событий для обнаружения наступления события, частично на основании множества сигналов; и блок, подключенный к встроенному логическому анализатору и имеющий выходной сигнал, который основан на обнаружении наступления события, причем выходной сигнал поступает на встроенный логический анализатор для выборки или сохранения на нем. За счет подачи на встроенный логический анализатор выходного сигнала для выборки или сохранения который основан на обнаружении или наступлении события, блок преимущественно обеспечивает более эффективный механизм для выборки и сохранения системных данных.

[0011] Дополнительные признаки и преимущества изобретения будут изложены в нижеследующем подробном описании, и частично будут очевидны специалистам в данной области техники из этого описания или будут поняты благодаря практическому применению описанного здесь изобретения, включающего в себя нижеследующее подробное описание, формулу изобретения, а также прилагаемые чертежи.

[0012] Следует понимать, что вышеизложенное общее описание и нижеследующее подробное описание настоящих вариантов осуществления изобретения призваны обеспечивать обзор или основные положения для понимания природы и характера изобретения, заявленного, как есть. Прилагаемые чертежи включены для обеспечения дополнительного понимания изобретения, и включены в состав и составляют часть этого описания изобретения. Чертежи иллюстрируют различные варианты осуществления изобретения и, совместно с описанием, служат для пояснения принципов и действия изобретения.

Краткое описание чертежей

[0013] Вышеупомянутые и другие признаки и преимущества различных вариантов осуществления изобретения, и пути их достижения, будут более очевидны и более понятны, если обратиться к прилагаемым чертежам, на которых:

фиг. 1 - блок-схема традиционного встроенного логического анализатора;

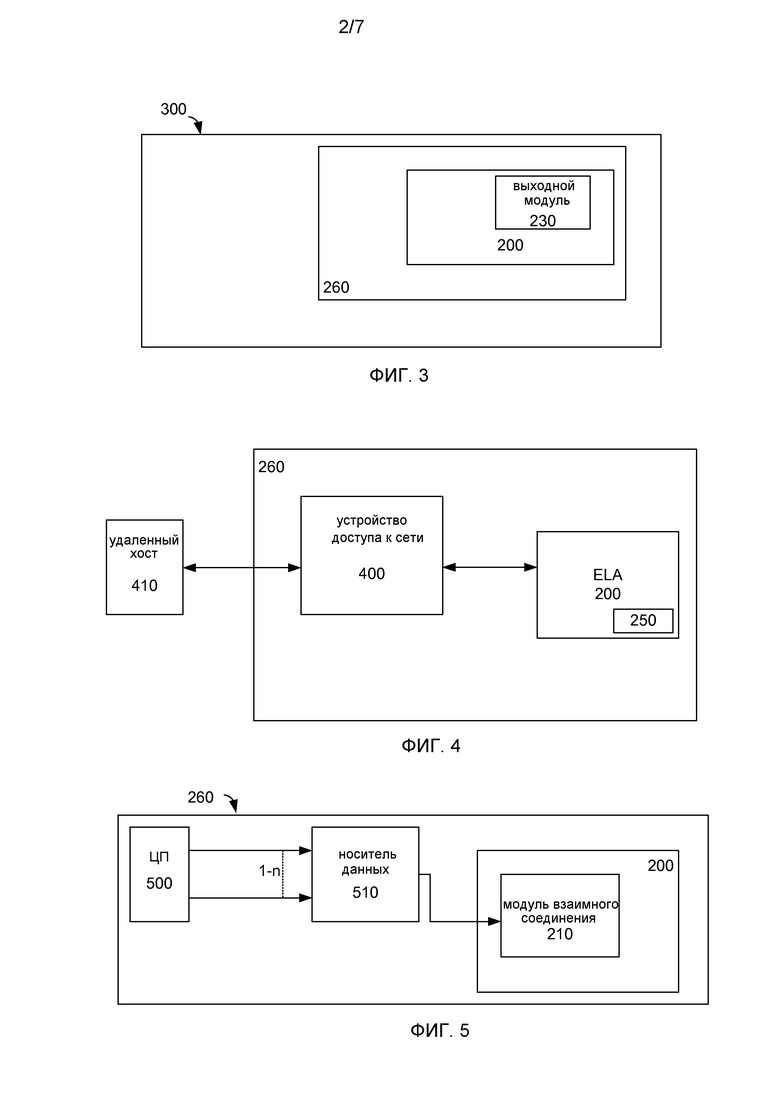

фиг. 2 - блок-схема одного варианта осуществления интегральной схемы, включающей в себя логический анализатор согласно настоящему изобретению;

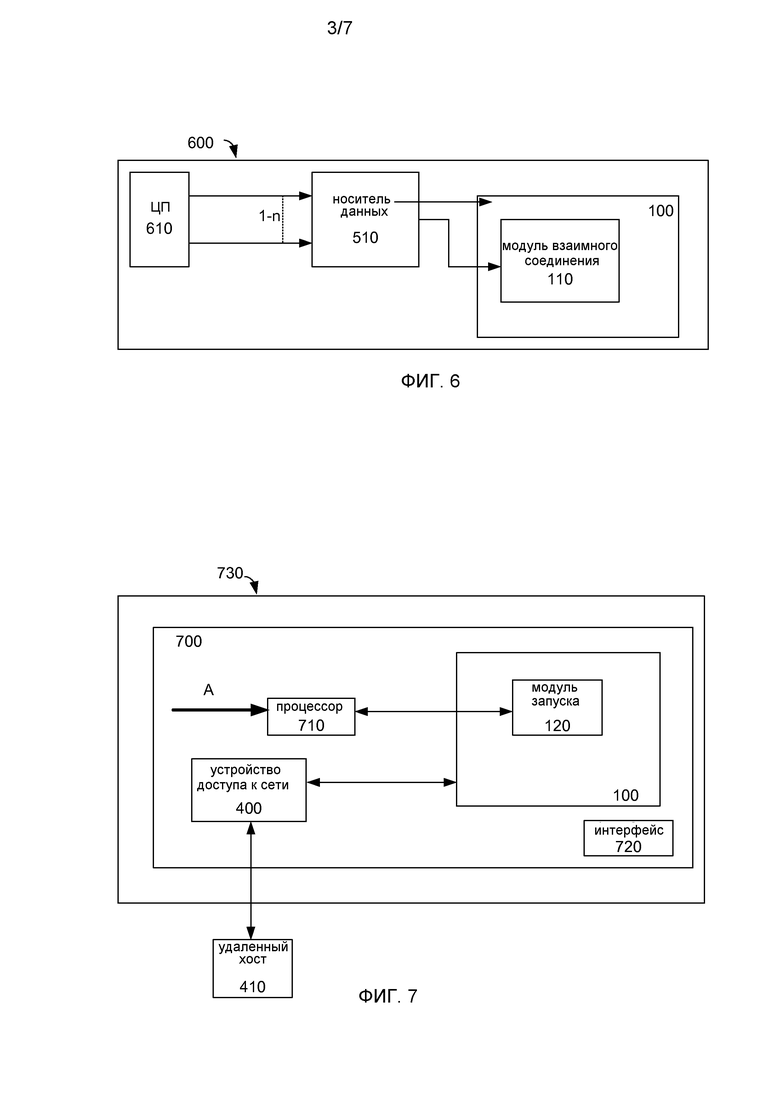

фиг. 3 - блок-схема устройства, включающего в себя интегральную схему, показанную на фиг. 2;

фиг. 4 - блок-схема, иллюстрирующая устройство доступа к сети, подключающее удаленный хост к интегральной схеме, показанной на фиг. 2;

фиг. 5 - блок-схема, иллюстрирующая интерфейс для подачи программных сигналов на логический анализатор, входящий в состав интегральной схемы, показанной на фиг. 2;

фиг. 6 - блок-схема, иллюстрирующая интерфейс, сконфигурированный для подачи программных сигналов на логический анализатор, показанный на фиг. 1, согласно настоящему изобретению;

фиг. 7 - блок-схема, демонстрирующая процессор, соединенный с логическим анализатором входящий в состав интегральной схемы, показанной на фиг. 2;

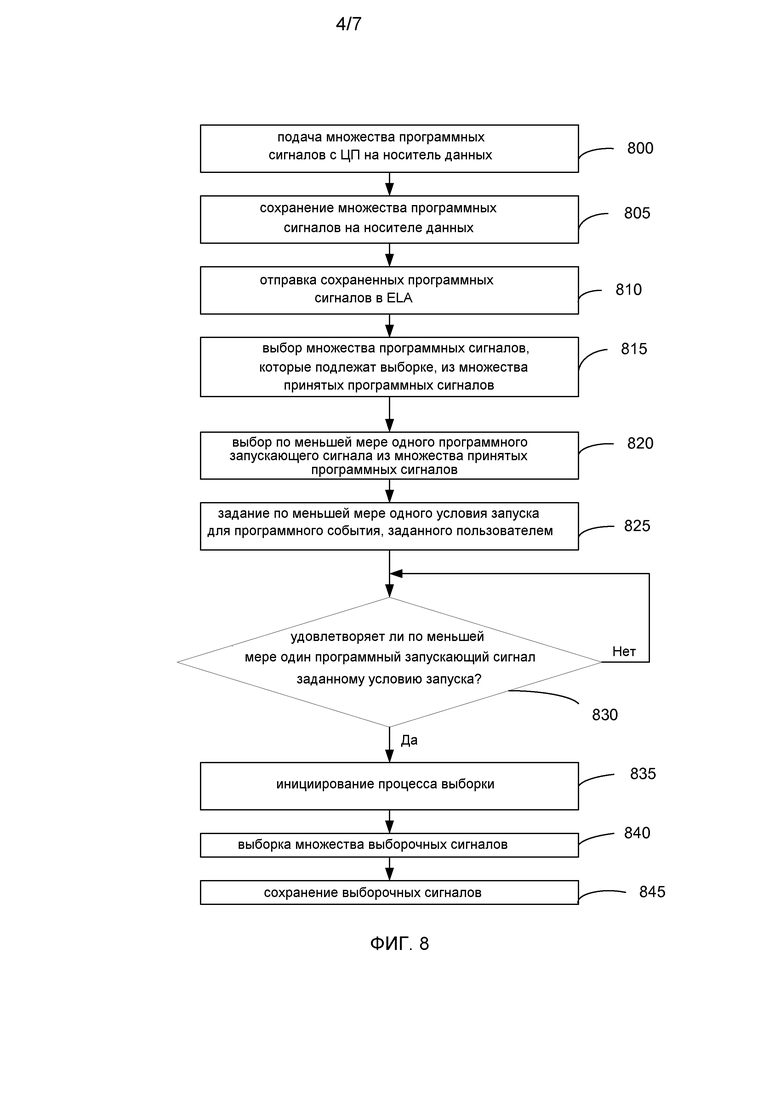

фиг. 8 - блок-схема операций, демонстрирующая действия, осуществляемые для захвата программных сигналов в интегральной схеме, показанной на фиг. 2, согласно настоящему изобретению;

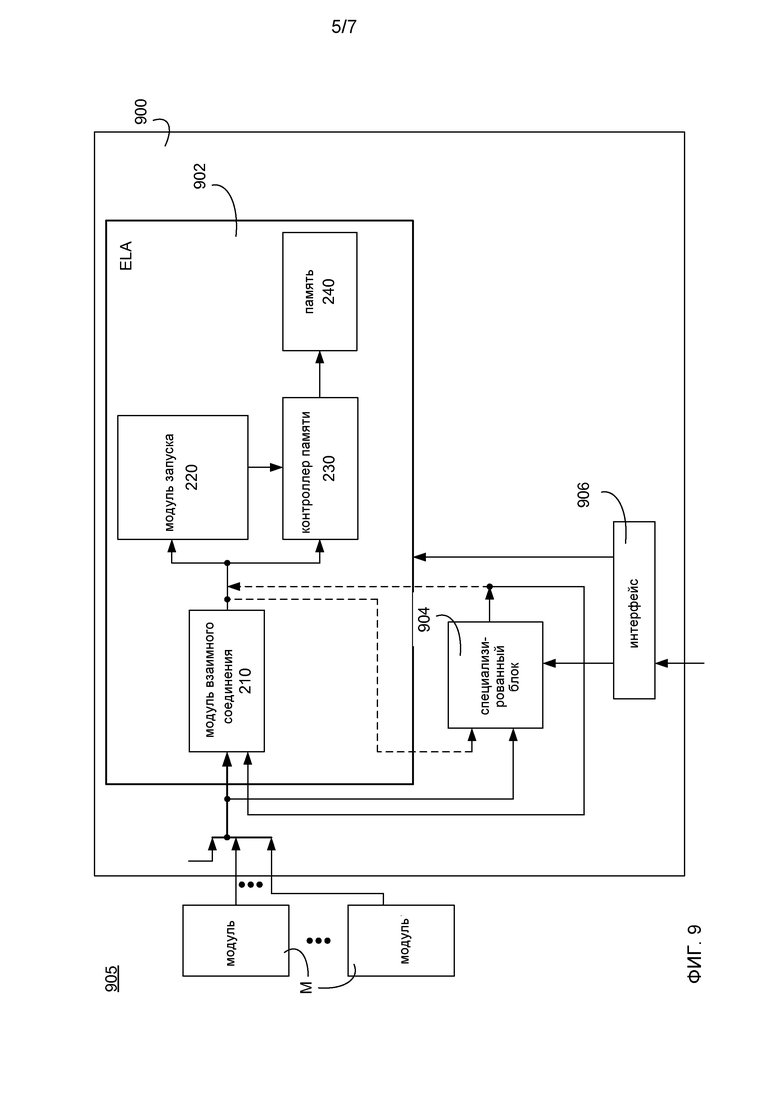

фиг. 9 - блок-схема, иллюстрирующая систему, имеющую интегральную схему согласно примерному варианту осуществления настоящего изобретения;

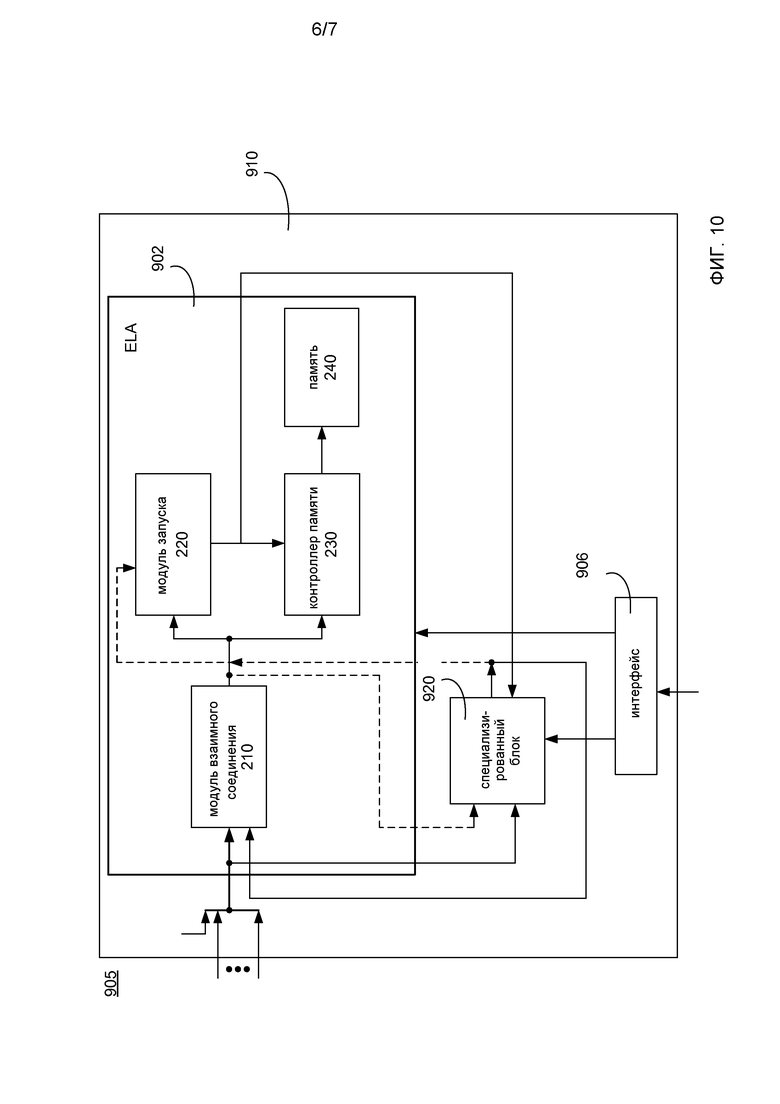

фиг. 10 - блок-схема, иллюстрирующая систему, имеющую интегральную схему согласно примерному варианту осуществления настоящего изобретения;

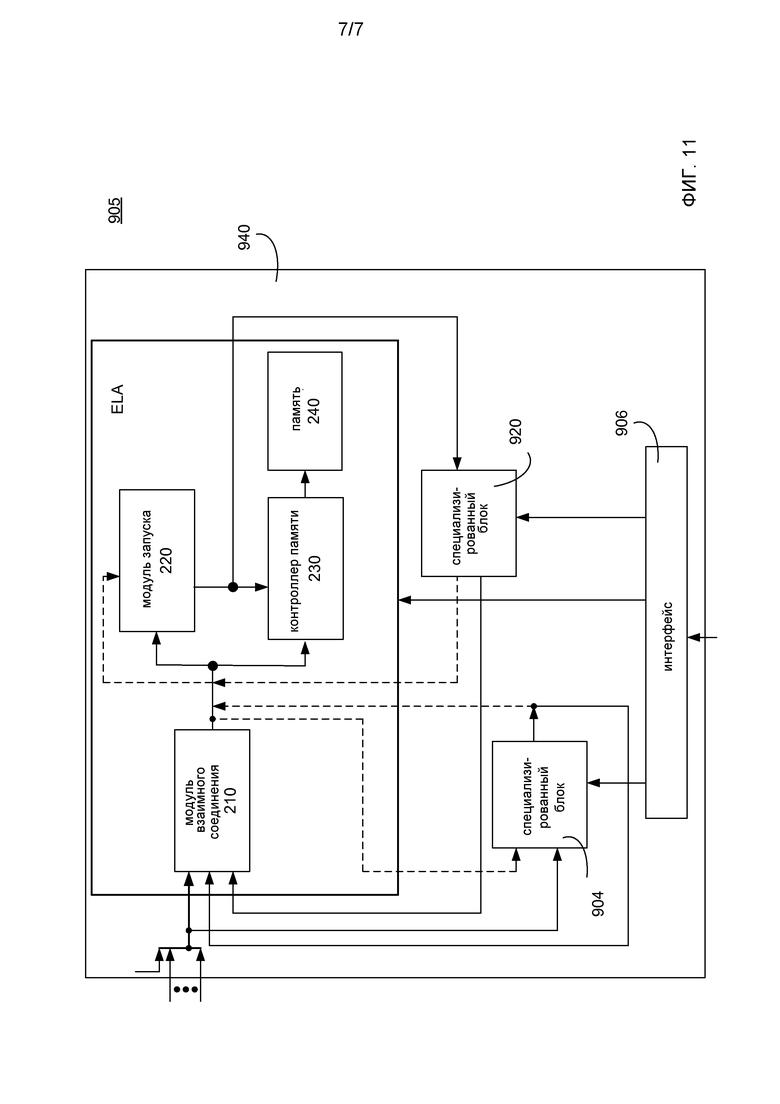

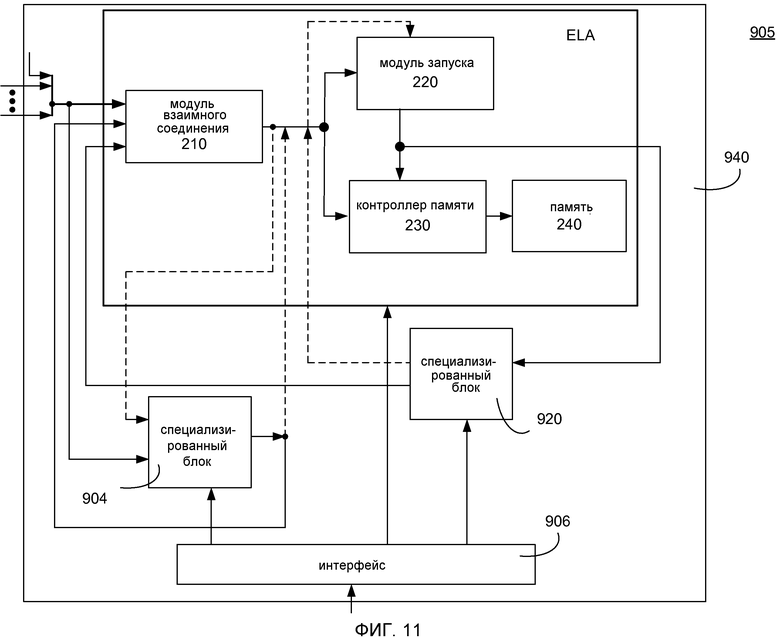

фиг. 11 - блок-схема, иллюстрирующая систему, имеющую интегральную схему согласно примерному варианту осуществления настоящего изобретения.

Подробное описание

[0014] Ниже будет подробно рассмотрен примерный(е) вариант(ы) осуществления изобретения, проиллюстрированный(е) в прилагаемых чертежах. По мере возможности, одинаковые ссылочные позиции будут использоваться на протяжении чертежей для обозначения одинаковых или сходных частей.

[0015] Настоящее изобретение относится к программируемому встроенному логическому анализатору, входящему в состав интегральной схемы, имеющей расширенные возможности анализа и отладки. Фиг. 2 иллюстрирует один вариант осуществления встроенного логического анализатора (ELA) 200, расположенного в интегральной схеме (ИС) 260. ELA 200 включает в себя модуль 210 взаимного соединения, который имеет возможность программирования для выбора по меньшей мере одного из множества сигналов-кандидатов в ИС 260. Множество сигналов-кандидатов, выбранных модулем 210 взаимного соединения, может включать в себя по меньшей мере один запускающий сигнал и/или по меньшей мере один сигнал, подлежащий выборке (т.е. выборочный сигнал). Модуль 210 взаимного соединения направляет по меньшей мере один запускающий сигнал в модуль 220 запуска. Модуль 220 запуска определяет, удовлетворяет ли по меньшей мере один запускающий сигнал по меньшей мере одному условию запуска, указанному пользователем. В случае удовлетворения условия запуска, выходной модуль 230 выполняет по меньшей мере одно задание. Например, выходной модуль 230 может изменять по меньшей мере один сигнал в ИС 260.

[0016] ИС 260 включает в себя множество шин 265, которые переносят множество сигналов-кандидатов. Множество сигналов включает в себя по меньшей мере один выборочный сигнал и по меньшей мере один запускающий сигнал. Модуль 210 взаимного соединения принимает множество сигналов от множества шин 265. Модуль 210 взаимного соединения имеет возможность программирования для выбора по меньшей мере одного выборочного сигнала и/или по меньшей мере одного запускающего сигнала из множества принятых сигналов. По существу, модуль 210 взаимного соединения выбирает выборочный(е) сигнал(ы) и/или запускающий(е) сигнал(ы), указанные пользователем. В одном варианте осуществления, модуль 210 взаимного соединения может быть мультиплексором.

[0017] Модуль 210 взаимного соединения направляет запускающий сигнал в модуль 220 запуска. Модуль 220 запуска имеет возможность программирования для задания условия запуска. Условием запуска может быть единичная логическая операция (например, простое событие) или последовательность логических операций (например, сложная последовательность событий, осуществляемых конечным автоматом). Модуль 220 запуска определяет, удовлетворяет ли запускающий сигнал по меньшей мере одному условию запуска. В случае удовлетворения условия запуска, модуль 220 запуска предоставляет информацию выходному модулю 230.

[0018] Выходной модуль 230 выполняет по меньшей мере одно задание из группы заданий на основании, в ответ на, или в результате удовлетворения по меньшей мере одного условия запуска. Группа заданий может включать в себя изменение по меньшей мере одного сигнала из множества принятых сигналов, изменение по меньшей мере одного условия запуска и инициирование процесса выборки. В одном варианте осуществления, выходной модуль 230 является программируемой пользователем вентильной матрицей.

[0019] Если выходной модуль 230 инициирует процесс выборки, контроллер 240 выборки начинает производить выборку выборочного сигнала из модуля 210 взаимного соединения. Выборочный сигнал, подвергнутый выборке контроллером 240 выборки, может храниться в памяти 250. Сигналы, хранящиеся в памяти 250, можно переносить на компьютер (не показан) для анализа. Такой перенос сигнала на компьютер может происходить через порт 280 связи, например порт USB. Затем сигналы, переносимые на компьютер, могут анализироваться пользователем.

[0020] Хотя на фиг. 2 показано, что память 250 находится в ELA 200, специалисту в данной области техники очевидно, что память может быть отдельным компонентом интегральной схемы 260 в другом варианте осуществления. В еще одном варианте осуществления, память может располагаться отдельно от интегральной схемы 260, при условии, что она остается подключенной с возможностью передачи данных в ELA. После анализа сигналов, по меньшей мере одно действие в устройстве 300, включающем в себя ИС 260, как показано на фиг. 3, может осуществляться путем конфигурирования или программирования выходного модуля 230 для осуществления конкретного задания на основании анализа. Например, пользователь может выполнять отладку для устранения ошибки или сбоя или для корректировки действия компонента устройства 300. Таким образом, устройство 300 можно диагностировать более эффективно, чтобы гарантировать правильное функционирование устройства 300. В одном варианте осуществления, устройство 300 может представлять собой устройство формирования изображения, например принтер, сканер, или многофункциональное устройство, которое обладает способностью печатать, сканировать, осуществлять факсимильную связь и/или копировать.

[0021] Выходной модуль 230 можно программировать или конфигурировать для изменения по меньшей мере одного сигнала на основании, в ответ на, или в результате удовлетворения условия запуска. Если удовлетворенное условие запуска указывает ошибку, выходной модуль 230 может изменять по меньшей мере один сигнал из множества сигналов, принятых ELA 200, для исправления указанной ошибки. Например, если значение сигнала 'X' должно быть равно 30 для безошибочной работы устройства 300 или если условие запуска X≠30 выполняется, то выходной модуль 230 изменяет значение сигнала X для придания сигналу значения 30 для безошибочной работы устройства 300.

[0022] Выходной модуль 230 также может предписывать контроллеру 270 (показанному на фиг. 2) изменять по меньшей мере один сигнал из множества сигналов, принятых ELA 200, для исправления указанной ошибки. Например, выходной модуль 230 может предписывать контроллеру 270 отключать широтно-импульсный модулятор (ШИМ), если обнаружено, что ШИМ, который регулирует обороты двигателя, завис, таким образом, предотвращая повреждение двигателя. Выходной модуль 230 также может быть способен останавливать операцию прямого доступа к памяти (DMA). Кроме того, выходной модуль 230, при необходимости, может изменять условие запуска. Эти возможности выходного модуля 230 значительно расширяют отладочные возможности ELA 200. Таким образом, ELA 200, в общем случае, выполняет нижеприведенный код:

IF (<условие>) THEN (<действие(S)>),

где действие(S) является по меньшей мере любым из вышеупомянутых действий, осуществляемых выходным модулем или контроллером, и условие является условием запуска, заданным пользователем.

[0023] В одном варианте осуществления, как показано на фиг. 4, ИС 260 включает в себя устройство 400 доступа к сети. Устройство 400 доступа к сети подключено с возможностью передачи данных в ELA 200 и подключено к удаленному хосту 410 непосредственно или через сеть. Соединение может включать в себя проводное соединение и/или беспроводное соединение, и сеть может представлять собой интернет, локальную сеть, глобальную сеть или городскую сеть. Удаленный хост 410 способен программировать ELA 200 в ИС 260. Удаленный хост 410 также способен анализировать выборочные сигналы, хранящиеся в памяти. Удаленный хост 410 осуществляет доступ к ELA 200 через устройство 400 доступа к сети.

[0024] ELA 200 можно программировать для автоматической и периодической отправки сохраненных выборочных сигналов на удаленный хост 410 для анализа. Например, ELA 200, встроенный в принтер, можно программировать для автоматической и периодической отправки сигнала кодера на удаленный хост 410. Сигнал кодера указывает движение двигателя в принтере. Если определено, что сигналы кодера спадают или переходят в плохое состояние, удаленный пользователь может выдать инструкцию на обслуживание принтера. В одном варианте осуществления, ELA 200 имеет возможность программирования для переноса сохраненных сигналов данных на удаленный хост 410 в случае приема такой инструкции или команды от удаленного хоста 410.

[0025] В другом варианте осуществления, согласно фиг. 5, ИС 260 включает в себя центральный процессор (ЦП) 500. ЦП 500 выдает множество сигналов данных на ELA 200. Сигналы данных могут быть аппаратными, программными или программно-аппаратными сигналами. Сигналы данных поступают от ЦП 500 на ELA 200 через интерфейс. Интерфейс подключен с возможностью передачи данных к ЦП 500 и ELA 200. Интерфейс включает в себя носитель 510 данных и множество линий связи (1-n). Множество линий связи связано с возможностью передачи данных с ЦП 500 и носителем 510 данных. Множество линий связи (1-n) сконфигурированы для подачи множества сигналов данных от ЦП 500 на носитель 510 данных. Носитель 510 данных сконфигурирован для хранения множества сигналов данных.

[0026] Каждый сигнал данных из множества сигналов данных связан с полем данных и полем адреса. Поле данных обеспечивает значение сигнала данных, подлежащее сохранению, и поле адреса указывает место на носителе 510 данных, где сохраняется сигнал данных. Носитель 510 данных включает в себя множество ячеек памяти. Каждая из множества ячеек памяти имеет уникальный адрес. Множество сигналов данных, хранящихся на носителе 510 данных, поступает в модуль 210 взаимного соединения через множество шин на ИС 260. По существу, носитель 510 данных находится в электрической связи с множеством шин на ИС 260 для подачи сохраненных сигналов данных в модуль 210 взаимного соединения.

[0027] Сохраненные сигналы данных, поступающие в модуль 210 взаимного соединения, включают в себя аппаратные, программные и/или программно-аппаратные сигналы данных. Сигналы данных включают в себя множество выборочных сигналов и по меньшей мере один запускающий сигнал. Модуль 210 взаимного соединения выбирает множество выборочных сигналов и по меньшей мере один запускающий сигнал из множества принятых сигналов данных. Запускающий сигнал поступает в модуль 220 запуска. Модуль 220 запуска определяет, удовлетворяет ли запускающий сигнал по меньшей мере одному условию запуска. В случае удовлетворения условия запуска, контроллер 240 выборки производит выборку множества выборочных сигналов из модуля 210 взаимного соединения. Множество выборочных сигналов сохраняется в памяти 250. Множество сохраненных сигналов совместно с другими сохраненными сигналами переносится на компьютер для анализа. Таким образом, аппаратные, программные и/или программно-аппаратные сигналы можно одновременно анализировать на компьютере.

[0028] В другом варианте осуществления, согласно фиг. 6, интерфейс, т.е. множество линий связи (1-n) и носитель 510 данных располагаются на ИС 600. ИС 600 включает в себя ELA 100, показанный на фиг. 1, и ЦП 610. ЦП 610 подает множество сигналов данных на ELA 100. Множество сигналов данных включает в себя по меньшей мере один из программного или программно-аппаратного сигнала данных. Множество сигналов данных поступают от ЦП 610 на ELA 100 через множество линий связи (1-n) и носитель 510 данных. Множество линий связи (1-n) сконфигурировано для подачи множества сигналов данных от ЦП 610 на носитель 510 данных. Носитель 510 данных сконфигурирован для хранения множества сигналов данных. Сигналы данных, хранящиеся на носителе 510 данных, поступают в модуль 110 взаимного соединения через множество шин на ИС 600. По существу, носитель 510 данных находится в электрической связи с множеством шин на ИС 600 для подачи сохраненных сигналов данных в модуль 110 взаимного соединения.

[0029] В еще одном варианте осуществления, согласно фиг. 7, ELA 100 располагается на ИС 700, которая включает в себя процессор 710. Процессор 710 принимает множество сигналов из множества шин на ИС 700. Такие сигналы могут представлять собой любую комбинацию аппаратных, программных и/или программно-аппаратных сигналов (указанных стрелкой A) в ИС 700. Процессор 710 подключен с возможностью передачи данных к ELA 100, расположенному на ИС 700. В частности, процессор 710 может быть подключен с возможностью передачи данных к модулю 120 запуска ELA 100.

[0030] В альтернативном варианте осуществления, ИС 700 может быть подключена с возможностью передачи данных к ELA 200, показанному на фиг. 2. В этом варианте осуществления, процессор 710 принимает по меньшей мере один запускающий сигнал от модуля 220 запуска для определения, выполняется ли по меньшей мере одно условие запуска. Если по меньшей мере одно условие запуска выполняется, то процессор 710 изменяет по меньшей мере один сигнал из множества сигналов данных, принятых процессором 710. Процессор 710 также допускает программирование для изменения по меньшей мере одного условия запуска в модуле 220 запуска, в случае удовлетворения по меньшей мере одного условия запуска. Процессор 710 имеет возможность программирования через интерфейс 720, обеспеченный на ИС 700.

[0031] ИС 700 может включать в себя устройство 400 доступа к сети. Устройство 400 доступа к сети подключает с возможностью передачи данных ИС 700 к удаленному хосту 410. Удаленный хост 410 может программировать ELA 10, расположенный на ИС 700. Удаленный хост 410 также может анализировать выборочные сигналы, хранящиеся в ELA 100. Таким образом, удаленный хост 410 может диагностировать устройство 730, включающее в себя ELA 100 и устройство 400 доступа к сети.

[0032] На фиг. 8 показана блок-схема операций, демонстрирующая способ захвата программных сигналов или событий в ИС 260. ЦП 500, расположенный на ИС 260, подает множество программных сигналов на носитель 510 данных на блоке 800. Носитель данных сконфигурирован для хранения множества программных сигналов (блок 805). Носитель 510 данных отправляет сохраненные программные сигналы в модуль 210 взаимного соединения ELA 200 в блоке 810. Модуль 210 взаимного соединения запрограммирован для выбора множества программных сигналов, которые подлежат выборке, из множества принятых программных сигналов (блок 815). Модуль 210 взаимного соединения также запрограммирован для выбора по меньшей мере одного программного запускающего сигнала из множества принятых программных сигналов (блок 820). Пользователь задает в модуле 220 запуска по меньшей мере одно условие запуска для программного события (блок 825). Модуль 220 запуска определяет, удовлетворяет ли по меньшей мере один программный запускающий сигнал заданному условию запуска (блок 830). В случае удовлетворения условия запуска, модуль 220 запуска инициирует процесс выборки в блоке 835. В противном случае, модуль запуска повторяет проверку выполнения заданного условия запуска.

[0033] После инициирования процесса выборки, контроллер 240 выборки производит выборку множества программных сигналов, которые подлежат выборке, из модуля 210 взаимного соединения (блок 840). Выборочные программные сигналы затем могут сохраняться в памяти 250 в блоке 845. Сохраненные программные сигналы также могут переноситься на компьютер для анализа программой, выполняющейся на компьютере, или пользователем.

[0034] Специалисту в данной области техники очевидно, что настоящее изобретение не ограничивается программными сигналами. Вместо программных сигналов и/или совместно с ними, можно захватывать другие сигналы, например, аппаратные и программно-аппаратные.

[0035] Фиг. 9 иллюстрирует системную интегральную схему 900 согласно другому варианту осуществления настоящего изобретения. Интегральная схема 900 может располагаться в системе 905, имеющей множество модулей M. Интегральная схема 900 может включать в себя встроенный логический анализатор 902, имеющий вышеописанные модуль 210 взаимного соединения, модуль 220 запуска, контроллер 240 памяти и память 250. Встроенный логический анализатор 902 может быть соединен с системными модулями M, чтобы встроенный логический анализатор 902 можно было использовать для эффективного тестирования или отладки системы 905, где он располагается.

[0036] Следует также понимать, что термины “тестирование” и “отладка” призваны включать в себя операции, обычно осуществляемые в ходе разработки, тестирования, отладки, системного анализа и контроля и обслуживания в условиях эксплуатации системы и ее системных модулей M, и не подлежат ограничению только одной фазой или периодом времени работы системы от проектирования на протяжении периода эксплуатации системы.

[0037] Интегральная схема 900 также может включать в себя специализированный блок 904, который принимает один или более сигналов, связанных со встроенным логическим анализатором 902. В частности, специализированный блок 904 может принимать в качестве входного сигнала один или более сигналов, поступающих на встроенный логический анализатор 902 от других модулей M системы. Такие сигналы могут включать в себя сигналы, которые применимы для осуществления выборки или запуска событий встроенным логическим анализатором 902. Специализированный блок 904 может генерировать на своем выходе один или более выходных сигналов, которые основаны на одном или более принятых входных сигналах и которые возвращаются на встроенный логический анализатор 902 для выборки или запуска. За счет подачи на встроенный логический анализатор 902 одного или более дополнительных сигналов для осуществления выборки и/или запуска событий, которые основаны на сигналах, связанных со встроенным логическим анализатором 902, встроенный логический анализатор 902 может более эффективно отлаживать систему, в которой располагается интегральная схема 900.

[0038] Специализированный блок 904 может включать в себя схему, специфичную для конкретной системы и/или системных модулей M, которые доступны для тестирования и/или отладки с использованием встроенного логического анализатора 902. В примерном варианте осуществления настоящего изобретения, специализированный блок 904 выполнен с возможностью конфигурирования таким образом, чтобы сигналы, генерируемые таким образом, можно было конфигурировать. Возможность конфигурирования специализированного блока 904 преимущественно обеспечивает существенную гибкость для тестирования и/или отладки разнообразных системных модулей M и системных сигналов, генерируемых таким образом. Специализированный блок 904 можно реализовать в виде FPGA или CPLD. Альтернативно, специализированный блок 904 можно реализовать с помощью процессора, к которому подключена память для хранения кода, подлежащего выполнению процессором. Благодаря тому, что в память можно загружать разный код, специализированный блок 904 может обеспечивать достаточную гибкость для тестирования и/или отладки, по существу, большого количества разных системных модулей M. Согласно еще одной альтернативе, специализированный блок 904 может включать в себя схему конечного автомата, которая имеет возможность программирования частично путем программирования и/или сохранения информации в регистрах, которые располагаются в конечном автомате или связаны с ним. Следует понимать, что специализированный блок 904 можно реализовать по-разному для обеспечения конфигурируемой функциональности и генерации сигналов.

[0039] Как показано на фиг. 9, специализированный блок 904 может принимать один или более сигналов, поступающих на встроенный логический анализатор 902. Такие сигналы, поступающие на встроенный логический анализатор 902, могут приниматься специализированным блоком 904 за счет непосредственного подключения одного или более входов специализированного блока 904 к одному или более входам встроенного логического анализатора 902. Дополнительно или альтернативно, такие сигналы, поступающие на встроенный логический анализатор, могут приниматься специализированным блоком 904 за счет непосредственной подачи на один или более входов специализированного блока 904 одного или более выходных сигналов модуля 210 взаимного соединения, которые предназначены для запуска события и/или подлежат выборке, как показано пунктирными линиями на фиг. 9. Как дополнительно показано на фиг. 9, с выхода специализированного блока 904 на встроенный логический анализатор 902 может поступать один или более выходных сигналов для запуска событий или осуществления выборки. Такие один или более выходных сигналов могут поступать на встроенный логический анализатор 902 за счет непосредственного подключения выхода специализированного блока 904 к входу встроенного логического анализатора 902. Дополнительно или альтернативно, такие один или более выходных сигналов могут поступать на встроенный логический анализатор 902 за счет непосредственного подключения выхода специализированного блока 904 к входу модуля 220 запуска и/или входу контроллера 240 памяти, как показано пунктирными линиями на фиг. 9.

[0040] Интегральная схема 900 может дополнительно включать в себя интерфейс 906, который можно использовать для осуществления доступа к специализированному блоку 904 и встроенному логическому анализатору 902. В частности, интерфейс 906 может обеспечивать проводное или беспроводное соединение с сетевым устройством в сети, например удаленным хостом (не показан). Интерфейс 906 может обеспечивать необходимый интерфейс между сетевым устройством и различными блоками в интегральной схеме 900, в том числе встроенным логическим анализатором 902 и специализированным блоком 904. Встроенный логический анализатор 902 и, в частности, модуль 210 взаимного соединения и модуль 220 запуска может управляться конфигурироваться и/или программироваться с использованием интерфейса 906. Кроме того, данные, подвергнутые выборке встроенным логическим анализатором 902, могут загружаться на сетевое устройство для анализа через интерфейс 906.

[0041] Как упомянуто выше, доступ к специализированному блоку 904 можно осуществлять с использованием интерфейса 906. Например, в случае когда специализированный блок 904 допускает реконфигурирование и/или программирование, специализированный блок 904 может конфигурироваться сетевым устройством с использованием интерфейса 906 для генерации одного или более выходных сигналов, адаптированных к конкретным системным модулям M, подлежащим тестированию или отладке. Дополнительно или альтернативно, специализированный блок 904 может управляться удаленным хостом в ходе тестирования или отладки системы с использованием интерфейса 906. В результате, специализированный блок 904 может конфигурироваться в ходе сеанса тестирования или отладки на уровне системы.

[0042] На фиг. 9 показан специализированный блок 904, отделенный от встроенного логического анализатора 902 в интегральной схеме 900. Следует понимать, что, альтернативно, специализированный блок 904 может находиться внутри встроенного логического анализатора 902 в интегральной схеме 900 и быть подключенным к модулю 100 взаимного соединения, модулю 220 запуска и контроллеру 240 памяти, как описано выше.

[0043] Фиг. 10 иллюстрирует интегральную схему 910 системы 905 согласно другому примерному варианту осуществления настоящего изобретения. Интегральная схема 910 может включать в себя встроенный логический анализатор 902, как описано выше со ссылкой на фиг. 9, имеющий модуль 210 взаимного соединения, модуль 220 запуска, контроллер 240 памяти и память 250. Интегральная схема 910 также может включать в себя специализированный блок 920 для генерации одного или более сигналов для осуществления выборки или запуска событий встроенным логическим анализатором 902, на основании сигналов, подаваемых на встроенный логический анализатор 902 и/или генерируемых в нем.

[0044] Аналогично специализированному блоку 904 на фиг. 9, специализированный блок 920 подключен к встроенному логическому анализатору 902 для приема в качестве входного сигнала одного или более сигналов, поступающих на встроенный логический анализатор 902. Специализированный блок 920, наподобие специализированного блока 904, может генерировать один или более выходных сигналов на основании одного или более принятых входных сигналов, которые поступают на встроенный логический анализатор 902, модуль 220 запуска (для запуска событий) и/или контроллер 240 памяти (для избирательной выборки). По аналогии со специализированным блоком 904, специализированный блок 920 может включать в себя схему, специфичную для системных модулей M, которые можно тестировать или отлаживать с помощью встроенного логического анализатора 902. В одном варианте осуществления, функции, осуществляемые специализированным блоком 920 при генерации одного или более выходных сигналов, можно конфигурировать и/или программировать с использованием FPGA или схемы CPLD, процессора, исполняющего загруженный код тестирования/отладки, схемы конечного автомата и т.д. Интерфейс 906 может быть подключен к специализированному блоку 920 для обеспечения доступа к нему, для обеспечения управления, конфигурирования и/или программирования специализированного блока с использованием сетевого устройства, например, устройства-хоста.

[0045] Кроме того, специализированный блок 920 может принимать в качестве входного сигнала один или более сигналов, генерируемых модулем 220 запуска. В частности, один или более запускающих сигналов, генерируемых модулем 220 запуска, которые указывают обнаружение по меньшей мере одного события, могут поступать, в качестве входных сигналов, на специализированный блок 920. Один или более выходных сигналов, генерируемых специализированным блоком 920, могут основываться на одном или более запускающих сигналах, генерируемых модулем 220 запуска. Таким образом, выходной сигнал, генерируемый специализированным блоком 920, можно задавать на основании сигналов, генерируемых системными модулями M в ходе тестирования и отладки, а также действий, которые задаются и выполняются в ходе сеанса тестирования или отладки.

[0046] Например, запускающий сигнал, генерируемый модулем 220 запуска встроенного логического анализатора 902 и поступающий на специализированный блок 920, можно использовать для включения схемы генерации сигнала в специализированном блоке 920. В одной реализации специализированный блок 920 может конфигурироваться или иным образом программироваться как накопитель для отсчета количества событий, например, количества слов, считанных из памяти системным модулем прямого доступа к памяти (DMA). После тестирования или отладки система выбирает модуль DMA для мониторинга и соответственно управляет, программирует и/или конфигурирует модуль 220 запуска с использованием интерфейса 906. Запускающая программа, посредством которой сконфигурирован модуль 220 запуска, может включать в себя действие для запуска накопления. После обнаружения условия одного или более сигналов, поступающих в модуль 220 запуска, запускающий сигнал, генерируемый модулем 220 запуска, указывает обнаружение условия и разрешает накопителю, сконфигурированному в специализированном блоке 920, начать накопление.

[0047] Модуль 220 запуска также может, либо через тот же запускающий сигнал, который используется для включения специализированного блока 920, либо через другой запускающий сигнал, отключать специализированный блок 920 после его включения. Сигнал, используемый для отключения, может вырабатываться схемой, которая выполнена с возможностью конфигурирования и/или программирования и обнаруживает наступление по меньшей мере одного запускающего события, относящегося к одному или более сигналам, принятым модулем 220 запуска. В случае когда специализированный блок 920 сконфигурирован как накопитель, после отключения, выходной сигнал накопителя поступает на вход встроенного логического анализатора 902 для осуществления избирательной выборки контроллером 240 памяти или запуска событий модулем 220 запуска. Благодаря управлению функцией накопления в специализированном блоке 920 для осуществления накопления только по наступлении запускающего события, указанного пользователем и передачи накопленного результата на встроенный логический анализатор 902, для хранения выборок выходного сигнала накопительной функции требуется существенно меньше памяти, чем в противном случае потребовалось бы для отсчета количество слов, считанных системным модулем DMA.

[0048] Частные примеры запускающего события для управления, включения и/или отключения специализированного блока 902 можно конфигурировать или программировать в ходе сеанса тестирования или отладки, наподобие любого другого запускающего события, отслеживаемого модулем 220 запуска. Запускающее событие для отключения специализированного блока 920, может, например, частично основываться на заранее определенном периоде времени, прошедшем после его включения, причем заранее определенный период времени конфигурируется или иным образом программируется в ходе работы. Следует понимать, что, запускающее событие, вероятно, может основываться на любой из разнообразных функций или операций, заданных в модуле 220 запуска, и на одном или более сигналах, принятых таким образом.

[0049] Следует понимать, что специализированные блоки 904 и 920 можно использовать в одном и том же кристалле интегральной схемы. Фиг. 11 иллюстрирует такую интегральную схему 940 системы 905 согласно примерному варианту осуществления настоящего изобретения, включающую в себя оба специализированных блока 904 и 920. Следует также понимать, что интегральная схема может включать в себя более чем один специализированный блок 904 и/или более чем один специализированный блок 920. В отношении включения более одного специализированного блока 920 в единый кристалл интегральной схемы, каждый специализированный блок 920 может принимать на своем входе один или более сигналов от модуля 220 запуска. Один или более сигналов, принятых от модуля 220 запуска каждым специализированным блоком 920, могут отличаться от одного или более сигналов, принятых другим специализированным блоком 920. Кроме того, каждый специализированный блок 920 может отдельно программироваться и/или конфигурироваться устройством-хостом с использованием интерфейса 906.

[0050] Следует понимать, что интегральные схемы 900, 910 и 940 можно использовать практически в любой системе, которая может пользоваться встроенным механизмом, для облегчения эффективного тестирования и отладки системы и ее системных модулей M. Например, принтер, полнофункциональное печатающее устройство или многофункциональный принтер может включать в себя интегральную схему 900.

[0051] Было показано, что использование специализированных блоков 904 и 920 существенно снижает объем памяти, необходимый для хранения сигналов, подвергнутых выборке встроенным логическим анализатором 902. Например, принтер или другое устройство формирования изображения может включать в себя последовательный интерфейс для подачи на печатающую головку принтера данных печати для всего задания печати, для чего может потребоваться гигабайтное хранилище. Если желательно знать, сколько раз срабатывает конкретное сопло в печатающей головке, специализированный блок 904 или 920 можно сконфигурировать для приема сигнала из последовательного интерфейса и генерации сигнала, указывающего срабатывание конкретного сопла, без какой-либо другой информации, относящейся к любому другому соплу печатающей головки. Генерируемый сигнал может поступать в качестве входного сигнала на встроенный логический анализатор 902 для осуществления избирательной выборки в ходе сеанса тестирования/отладки. Установлено, что для выборки и сохранения в памяти специализированного генерируемого сигнала требуются лишь килобайты памяти, что существенно меньше, чем объем памяти, необходимый для выборки и сохранения всего последовательного интерфейса.

[0052] Механизм для тестирования и отладки системы может включать в себя, помимо специализированных блоков 904 и 920, программное обеспечение для осуществления связи со встроенным логическим анализатором 902 и специализированными блоками 904 и 920. Программное обеспечение дает пользователю возможность выбора системных возможностей для таких блоков и управления ими или иного их программирования после синтеза и/или сборки системы, например, в ходе сеанса тестирования или отладки системы. Программное обеспечение, включающее в себя пользовательский интерфейс, обеспечивает связь со встроенным логическим анализатором 902 и блоками 904 и 920 через интерфейс 906. Программное обеспечение можно использовать для приема на удаленном устройстве данных, подвергнутых выборке и сохраненных встроенным логическим анализатором 902 и отображения сигналов пользователю удаленного устройства.

[0053] Специалисты в данной области техники могут предложить различные модификации и вариации настоящего изобретения, не выходя за рамки сущности и объема изобретения. Например, следует понимать, что встроенный логический анализатор 902 может включать в себя выходной модуль 230 и контроллер 270, присутствующие во встроенном логическом анализаторе 200, показанном на фиг. 2. Дополнительно или альтернативно, интегральные схемы 900, 910 и 940 могут включать в себя ЦП 500 и носитель 510 данных, подключенные к встроенному логическому анализатору 902, как показано на фиг. 5 и 6. Интегральные схемы 900, 910 и 940 также могут включать в себя процессор 710, подключенный к модулю 220 запуска, как показано на фиг. 7. Таким образом, настоящее изобретение призвано охватывать модификации и вариации этого изобретения при условии, что они согласуются с объемом нижеследующей формулы изобретения и ее эквивалентов.

| название | год | авторы | номер документа |

|---|---|---|---|

| ИНТЕГРАЛЬНАЯ СХЕМА С ПРОГРАММИРУЕМЫМ ЛОГИЧЕСКИМ АНАЛИЗАТОРОМ С РАСШИРЕННЫМИ ВОЗМОЖНОСТЯМИ АНАЛИЗА И ОТЛАДКИ И СПОСОБ | 2011 |

|

RU2579814C2 |

| СПОСОБ ДИАГНОСТИКИ СБОЯ ЭЛЕКТРОПИТАНИЯ В УСТРОЙСТВЕ БЕСПРОВОДНОЙ СВЯЗИ | 2014 |

|

RU2653336C1 |

| СИСТЕМА И СПОСОБ УПРАВЛЕНИЯ СЕНСОРНЫМ ЭКРАНОМ С ПОМОЩЬЮ ДВУХ КОСТЯШЕК ПАЛЬЦЕВ | 2016 |

|

RU2689430C1 |

| ПЛАВНЫЕ ПЕРЕХОДЫ МЕЖДУ АНИМАЦИЯМИ | 2006 |

|

RU2420806C2 |

| Способ, устройство и компьютерная программа для обработки данных датчика активности | 2014 |

|

RU2606880C2 |

| МАСШТАБИРУЕМЫЕ ПУЛЫ ХРАНЕНИЯ ДАННЫХ | 2015 |

|

RU2702268C2 |

| КОНФИГУРАЦИЯ УСТРОЙСТВА НА ОСНОВЕ СЕАНСОВ СВЯЗИ | 2015 |

|

RU2689194C2 |

| ОСУЩЕСТВЛЕНИЕ ДОСТУПА К РЕГИСТРАМ УСТРОЙСТВ ВЫБРОСА ТЕКУЧЕЙ СРЕДЫ | 2019 |

|

RU2776431C1 |

| СПОСОБЫ И УСТРОЙСТВО ДЛЯ САМОСТОЯТЕЛЬНОГО КОНФИГУРИРОВАНИЯ СЕТЕВЫХ СВЯЗЕЙ | 2008 |

|

RU2461984C2 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ОТЛАДКИ МНОГОЯДЕРНОЙ СИСТЕМЫ | 2007 |

|

RU2405192C2 |

Изобретение относится к анализаторам электронных схем. Устройство содержит интегральную схему, содержащую: схему логического анализатора, имеющую первый вход, принимающий множество сигналов, и первый выход для обеспечения выбранных выборок сигналов, поступающих на первый вход, и первый блок, имеющий первый вход, подключенный к схеме логического анализатора для приема одного или более сигналов, поступающих на его первый вход, и выход, подключенный к схеме логического анализатора для непосредственной подачи на него отдельного набора из одного или более сигналов, которые основаны на одном или более сигналах на первом входе первого блока, согласно заранее определенной функции, причем заранее определенная функция является конфигурируемой. Технический результат заключается в повышении отладочных возможностей и расширении функциональных возможностей. 3 н. и 14 з.п. ф-лы, 11 ил.

1. Устройство для тестирования и отладки электронной схемы, содержащее:

интегральную схему, содержащую:

схему логического анализатора, имеющую первый вход, принимающий множество сигналов от одного или более участков упомянутого устройства при тестировании, причем упомянутое множество сигналов применимо для схемы логического анализатора для осуществления выборки и запуска событий, и первый выход для обеспечения выбранных выборок сигналов, поступающих на первый вход, и

первый блок, имеющий первый вход, подключенный к схеме логического анализатора для приема одного или более сигналов, поступающих на первый вход схемы логического анализатора, и схему, генерирующую отдельный набор из одного или более тестовых сигналов на основе одного или более сигналов, поступающих на первый вход первого блока, согласно заранее определенной функции, причем заранее определенная функция является конфигурируемой, упомянутый отдельный набор из одного или более тестовых сигналов отличается от множества сигналов, принятых схемой логического анализатора, и от одного или более сигналов, принятых первым блоком, поступает на выход первого блока и подается на схему логического анализатора для по меньшей мере одного из осуществления выборки и запуска событий,

при этом первый вход первого блока связан с первым выходом схемы логического анализатора, так что первый блок принимает одну или более выбранных выборок упомянутого множества сигналов, поступающих на первый вход схемы логического анализатора, и генерирует упомянутый отдельный набор из одного или более тестовых сигналов на основе упомянутых одной или более выбранных выборок упомянутого множества сигналов, поступающих на первый вход схемы логического анализатора.

2. Устройство по п. 1, в котором схема логического анализатора включает в себя второй выход для обеспечения индикации обнаружения схемой логического анализатора по меньшей мере одного запускающего события, причем первый блок включает в себя второй вход, подключенный ко второму выходу схемы логического анализатора, и упомянутый отдельный набор из одного или более тестовых сигналов избирательно основан на сигналах, принятых на первом и втором входах первого блока.

3. Устройство по п. 2, в котором первый блок выполнен с возможностью конфигурирования в качестве накопителя, причем накопитель включается с помощью второго выхода схемы логического анализатора.

4. Устройство по п. 2, в котором упомянутая заранее определенная функция задействуется с помощью второго выхода схемы логического анализатора.

5. Устройство по п. 1, в котором схема логического анализатора содержит блок мультиплексора, подключенный к первому входу схемы логического анализатора для выбора по меньшей мере одного из множества сигналов, поступающих на первый вход схемы логического анализатора для осуществления выборки или запуска событий посредством этого, и блок запускающих событий, подключенный к выходу блока мультиплексора для обнаружения по меньшей мере одного запускающего события, причем отдельный набор из одного или более тестовых сигналов подан на вход блока запускающих событий.

6. Устройство по п. 1, в котором схема логического анализатора содержит блок управления выводом для осуществления избирательной выборки сигналов, поступающих на первый вход схемы логического анализатора и на выход первого блока.

7. Устройство по п. 1, в котором схема первого блока содержит программируемую пользователем схему.

8. Устройство по п. 1, в котором схема логического анализатора содержит блок входного мультиплексора, имеющий первый вход, подключенный к первому входу схемы логического анализатора, и второй вход, подключенный к выходу первого блока.

9. Интегральная схема для тестирования и отладки электронной схемы, содержащая:

схему логического анализатора, имеющую первый вход, принимающий множество сигналов, причем упомянутое множество сигналов применимо для схемы логического анализатора для осуществления выборки и запуска событий, второй вход, первый выход для обеспечения выбранных выборок сигналов, поступающих на первый вход, и второй выход для обеспечения индикации обнаружения схемой логического анализатора по меньшей мере одного запускающего события, и

первый блок, имеющий первый вход, подключенный к схеме логического анализатора для приема одного или более сигналов, поступающих на его первый вход, и схему для генерирования отдельного набора из одного или более тестовых сигналов на основе одного или более сигналов, поступающих на первый вход первого блока, согласно заранее определенной функции, причем заранее определенная функция является конфигурируемой, и выход, подключенный ко второму входу схемы логического анализатора для непосредственной подачи сгенерированного отдельного набора из одного или более тестовых сигналов в схему логического анализатора в качестве дополнительных тестовых сигналов для по меньшей мере одного из осуществления выборки и запуска событий,

при этом первый блок включает в себя второй вход, подключенный ко второму выходу схемы логического анализатора, и первый блок выполнен с возможностью конфигурирования в качестве накопителя для накопления на основе второго выхода схемы логического анализатора.

10. Интегральная схема по п. 9, в которой накопитель задействуется с помощью второго выхода схемы логического анализатора.

11. Интегральная схема по п. 9, в которой схема первого блока содержит программируемую пользователем схему.

12. Интегральная схема по п. 9, дополнительно содержащая интерфейс для конфигурирования заранее определенной функции первого блока.

13. Интегральная схема по п. 9, в которой схема логического анализатора содержит блок мультиплексора, подключенный к первому входу схемы логического анализатора, и блок запускающих событий, подключенный к выходу блока входного мультиплексора для обнаружения по меньшей мере одного запускающего события, причем отдельный набор из одного или более тестовых сигналов поступает на вход блока запускающих событий.

14. Интегральная схема по п. 9, в которой схема логического анализатора содержит блок управления выводом для осуществления избирательной выборки сигналов, поступающих на первый вход схемы логического анализатора и на выход первого блока.

15. Система для тестирования и отладки электронной схемы, содержащая:

интегральную схему, содержащую:

встроенный блок логического анализатора, имеющий вход для приема множества сигналов от одного или более участков упомянутой системы при тестировании для осуществления выборки и запуска событий, и блок запускающих событий для обнаружения наступления события частично на основании упомянутого множества сигналов,

блок, имеющий первый вход, подключенный к встроенному блоку логического анализатора для приема одного или более из упомянутого множества сигналов, второй вход, подключенный к блоку запускающих событий для приема от него сигнала, указывающего обнаружение наступления события, схему для генерирования отдельного набора из одного или более сигналов на основе упомянутого сигнала, указывающего обнаружение наступления события, причем упомянутый отдельный набор из одного или более сигналов отличается от упомянутого множества сигналов, поступающих на вход встроенного блока логического анализатора, и от одного или более из упомянутого множества сигналов, принятых на первом входе упомянутого блока, и имеющий выход, обеспечивающий сгенерированный отдельный набор из одного или более сигналов во встроенный блок логического анализатора для осуществления выборки или запуска событий,

при этом упомянутый блок выполнен с возможностью конфигурирования в качестве накопителя для накопления и начинать накопление при приеме упомянутого сигнала, указывающего обнаружение наступления события.

16. Система по п. 15, в которой упомянутый блок выполнен с возможностью конфигурирования для осуществления функции, которая задействуется частично на основании обнаружения наступления события.

17. Система по п. 15, в которой упомянутый отдельный набор из одного или более сигналов частично основан на по меньшей мере одном из множества сигналов, поступающих на вход встроенного блока логического анализатора.

| US 6389558 B1, 14.05.2002 | |||

| DE 4042262 A1, 02.07.1992 | |||

| US 6564347 B1, 13.05.2003 | |||

| US 6286114 B1, 04.09.2001. |

Авторы

Даты

2016-10-10—Публикация

2011-09-08—Подача