Изобретение относится к электрическим машинам, а именно к устройствам регулирования напряжения генераторов трехфазного переменного тока автономных источников электрической энергии.

Известны системы регулирования возбуждения синхронных генераторов, содержащие регуляторы напряжения (угольные, импульсные, вибрационные) /1/.

Недостатком этих систем является невысокое быстродействие, так как они производят регулирование по отклонению напряжения.

Известны системы регулирования возбуждения синхронных генераторов, содержащие элементы компаундирования (резисторы, автотрансформаторы, суммирующие трансформаторы) /2/.

Недостатком этих систем является невысокая точность, так как они производят регулирование по главному возмущающему фактору, не учитывая остальные возмущения.

Известны комбинированные цифровые системы регулирования возбуждения синхронных генераторов, содержащие суммирующий трансформатор, осуществляющий фазовое компаундирование, корректор напряжения, осуществляющий управление компаундированием и электронную схему осуществляющую управление форсировкой возбуждения /3/.

Недостатком этих устройств является невозможность сохранения удовлетворительного коэффициента небаланса фазных напряжений при работе на несимметричную нагрузку, поскольку регулирование возбуждения производится для генератора в целом, а не для отдельных фаз.

Наиболее близким по технической сущности к изобретению является устройство, содержащее генератор переменного напряжения с системой регулирования возбуждения, в цепь которого последовательно включена переменная неоднородная несимметричная нагрузка /4/.

Недостатком устройства является наличие небаланса фазных напряжений при работе на переменную неоднородную несимметричную нагрузку.

Цель изобретения - снижение небаланса фазных напряжений при работе на переменную неоднородную несимметричную нагрузку.

Цель изобретения достигается тем, что устройство коррекции небаланса фазных напряжений, содержащее трехфазный генератор переменного тока с системой регулирования возбуждения и переменной неоднородной несимметричной нагрузкой, отличающееся тем, что снабжено задающим регистром, тремя вариаторами, тремя числовыми компараторами, девятью логическими элементами И, тремя логическими элементами ИЛИ, логическим элементом И-НЕ, тремя измерителями амплитуд фазных напряжений, входы которых подключены на напряжения нагрузки соответствующих фаз, а разряды первого выхода первого измерителя амплитуд соединены с соответствующими разрядами первого входа первого числового компаратора и второго входа третьего числового компаратора, разряды первого выхода второго измерителя амплитуд соединены с соответствующими разрядами первого входа второго числового компаратора и второго входа первого числового компаратора, разряды первого выхода третьего измерителя амплитуд соединены с соответствующими разрядами первого входа третьего числового компаратора и второго входа второго числового компаратора, первый выход которого подключен к второму входу четвертого логического элемента И и второму входу девятого логического элемента И, выход которого связан с первым входом третьего вариатора, а первый вход - с третьим, а через диод и со вторым выходом третьего числового компаратора, первым входом пятого логического элемента И, первым входом второго логического элемента И и вторым входом первого логического элемента И, выход которого соединен с первым входом первого логического элемента ИЛИ, а первый вход - с вторым входом шестого логического элемента И, первым входом седьмого логического элемента И и первым выходом первого числового компаратора, третий, а через диод и второй выход которого подключены к второму входу второго логического элемента И, первому входу третьего логического элемента И, первому входу четвертого логического элемента И и второму входу восьмого логического элемента И, выход которого соединен с вторым входом третьего логического элемента ИЛИ, который связан выходом с вторым входом третьего вариатора, а первым входом - с выходом седьмого логического элемента И, второй вход которого соединен с первым выходом третьего числового компаратора, вторым входом третьего логического элемента И, первым входом шестого логического элемента И и первым входом восьмого логического элемента И, третий вход которого соединен с третьим выходом, а через диод и со вторым выходом второго числового компаратора, третьим входом второго логического элемента И и вторым входом пятого логического элемента И, выход которого подключен к первому входу второго логического элемента ИЛИ, второй вход которого связан с выходом шестого логического элемента И, а выход - с первым входом второго вариатора, второй вход которого соединен с выходом четвертого логического элемента И, разряды его пятого входа - с соответствующими разрядами выхода задающего регистра и разрядами пятых входов первого и третьего вариатора, его третий вход - с третьими входами первого и третьего вариатора и шиной ПУСК, его четвертый вход - с вторым выходом второго измерителя амплитуд, при этом второй выход третьего измерителя амплитуд связан с четвертым входом третьего вариатора, а второй выход первого измерителя амплитуд связан с четвертым входом первого вариатора, первый вход которого подключен к выходу третьего логического элемента И, а второй вход - к выходу первого логического элемента ИЛИ, связанного вторым входом с выходом второго логического элемента И, причем каждый измеритель амплитуд имеет измерительный трансформатор, первичная обмотка, зажимы которой являются входом измерителя, подключена на соответствующее фазное напряжение нагрузки, а вторичная обмотка через диод соединена с входом аналого-цифрового преобразователя, разряды выхода которого связаны с соответствующими разрядами первого входа числового компаратора и разрядами информационного входа регистра памяти, вход записи которого через первый формирователь коротких импульсов подключен к первому выходу числового компаратора, сбросовый вход регистра подключен к второму выходу числового компаратора через последовательно включенные элемент задержки и второй формирователь коротких импульсов, а разряды выхода регистра соединены с соответствующими разрядами второго входа числового компаратора и разрядами входа выходного регистра, выход которого является первым выходом измерителя, вторым выходом которого служит выход электронного ключа, вход которого соединен с выходом второго формирователя коротких импульсов и входом записи выходного регистра, причем управляющий электрод электронного ключа подключен к выходу логического элемента И-НЕ, входы которого связаны со вторыми выходами первого, второго и третьего компараторов, кроме того, каждый вариатор содержит N параллельных ветвей, включенных последовательно с нагрузкой соответствующей фазы и содержащих последовательно соединенные резистор и электронный ключ, управляющие электроды которых подключены к соответствующим разрядам выхода реверсивного счетчика, вход исходного числа которого служит пятым входом вариатора, а вход записи исходного числа - третьим входом вариатора, первым и вторым входами которого соответственно служат первые входы первого и второго логического элемента И вариатора, при этом их вторые входы соединены и являются четвертым входом вариатора при этом выход первого логического элемента И подключен к суммирующему входу реверсивного счетчика, а выход второго логического элемента И - к вычитающему входу счетчика, причем сопротивление резистора в i-й ветви определяется соотношением Ri=R121-i, где R1 - сопротивление резистора первой ветви.

Измерители амплитуд фазных напряжений и входящие в них элементы обеспечивают измерение напряжений фаз нагрузки для последующего анализа. Первый, второй и третий числовые компараторы, девять логических элементов И и три логических элемента ИЛИ производят анализ фазных напряжений и выявляют фазы с наибольшим и наименьшим напряжением. Вариаторы и входящие в них элементы обеспечивают коррекцию напряжения в фазах до приведения их к среднему уровню. Шина ПУСК и задающий регистр предназначены для перевода схемы в рабочее состояние. Логический Элемент И-НЕ и его связи исключают флуктуацию фазных напряжений после достижения баланса напряжений.

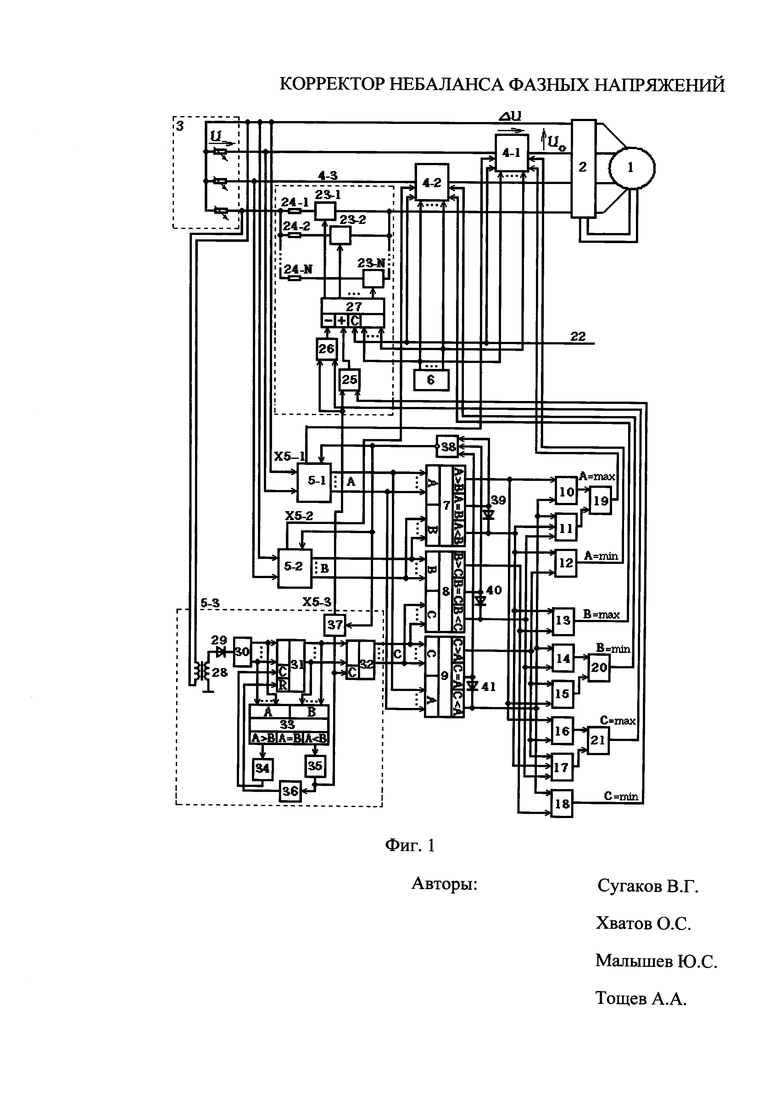

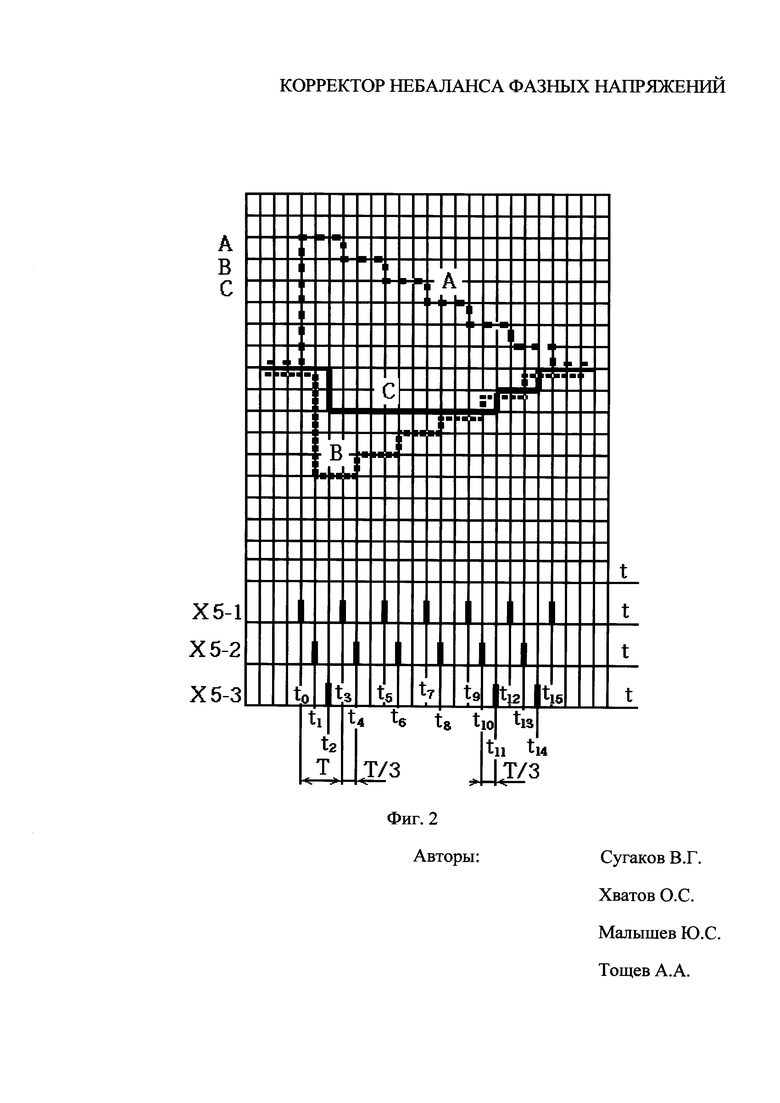

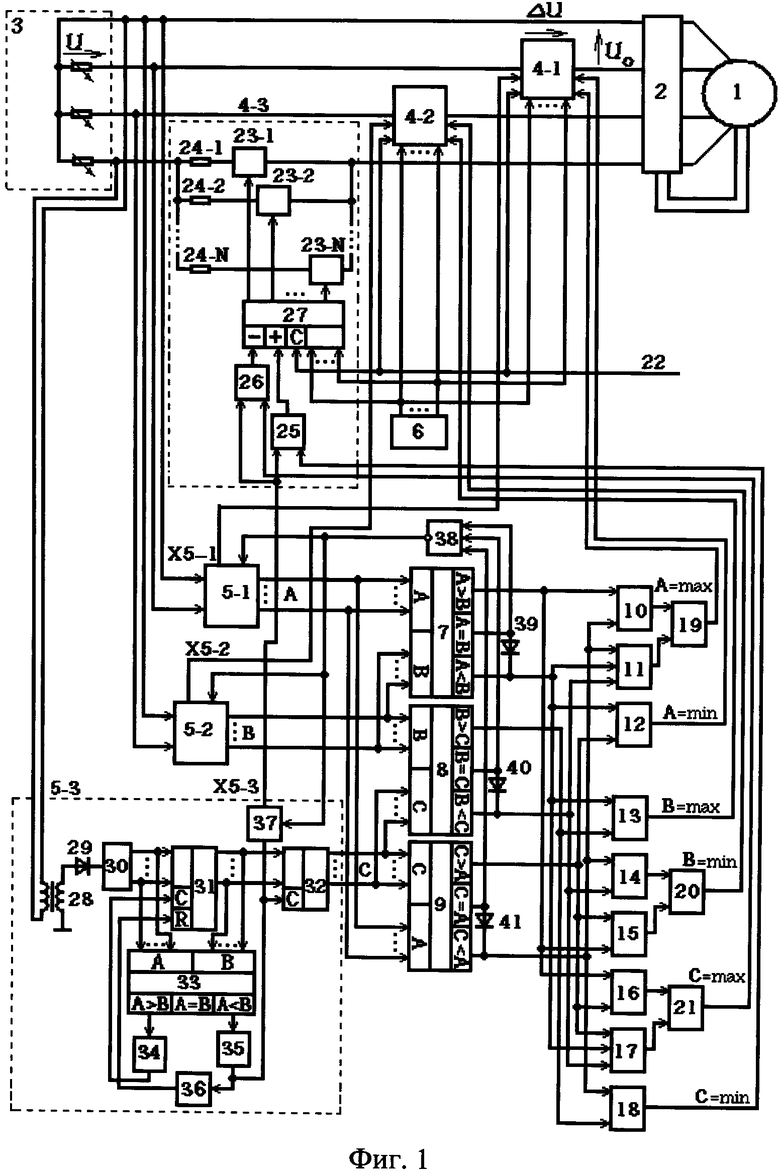

На фиг. 1 представлена схема устройства коррекции небаланса фазных напряжений, на фиг. 2 - эпюры сигналов на основных элементах схемы.

Схема содержит трехфазный генератор 1 переменного тока с системой автоматического регулирования возбуждения 2. В фазные провода последовательно с нагрузкой 3 включены соответственно вариаторы 4-1, 4-2 и 4-3. На фазные напряжения нагрузки 3 подключены измерители 5-1, 5-2 и 5-3 амплитуд соответствующих напряжений. Задающий регистр 6 подключен к информационным входам вариаторов 4-1, 4-2 и 4-3. Выходы измерителей амплитуды 5-1, 5-2 и 5-3 соединены с первым 7, вторым 8 и третьим 9 числовыми компараторами. Их выходы связаны с первым 10, вторым 11, третьим 12, четвертым 13, пятым 14, шестым 15, седьмым 16, восьмым 17 и девятым 18 логическими элементами И и через них с первым 19, вторым 20 и третьим 21 логическими элементами ИЛИ. Шина ПУСК 22 соединена с третьими входами вариаторов 4-1, 4-2 и 4-3, каждый из которых содержит с первого 23-1 по N-й 23-N электронные ключи, включенные последовательно с соответствующими с первого 24-1 по N-й 24-N резисторами, сопротивления R24-i i-го из которых определяется соотношением

R24-i=R24-121-i,

где R24-1 - сопротивление первого резистора 24-1. Кроме того, в каждый вариатор 4-1, 4-2 и 4-3 входят первый 25 и второй 26 логические элементы И и реверсивный счетчик 27. Измерители амплитуды 5-1, 5-2 и 5-3 имеют одинаковую структуру, которая включает измерительный трансформатор 28, диод 29, аналого-цифровой преобразователь (АЦП) 30, регистр памяти 31, выходной регистр 32, числовой компаратор 33, первый 34 и второй 35 формирователь коротких импульсов и элемент задержки 36, блокирующий электронный ключ 37. Входы логического элемента И-НЕ 38 подключены к вторым выходам числовых компараторов 7, 8, 9, и развязаны диодами 39, 40 и 41 с третьими выходами компараторов 7, 8 и 9.

Схема работает следующим образом.

В задающем регистре 6 устанавливается код, обеспечивающий среднюю по величине проводимость вариаторов 4-1, 4-2 и 4-3. При подаче сигнала на шину 22 этот код заносится в счетчики 27 вариаторов 4-1, 4-2 и 4-3. С разрядов выхода счетчика 27 на управляющие электроды соответствующих электронных ключей 23 поступают сигналы, которые открывают ключи, включая соответствующие резисторы 24. Системе регулирования возбуждения 2 задается уровень регулирования, обеспечивающий номинальное напряжение на нагрузке при симметричной нагрузке. При появлении на нагрузке 3 напряжения оно поступает на первичную обмотку измерительного трансформатора 28 измерителей 5-1, 5-2 и 5-3 амплитуд фазных напряжений. Положительная полуволна напряжения с вторичной обмотки трансформатора 28 через диод 29 поступает на вход АЦП 30, на выходе которого формируется код мгновенного значения фазного напряжения. Этот код подается на вход регистра памяти 31 и на первый вход числового компаратора 33. Если код на втором входе компаратора 33 меньше чем на первом входе, то появляется сигнал на первом выходе компаратора 33, по фронту которого формирователь 34 выдает короткий импульс на вход записи регистра 31, в который записывается код мгновенного значение фазного напряжения. Коды на входах компаратора 33 выравниваются, и сигнал на первом выходе исчезает. По мере роста фазного напряжения увеличивается код на выходе АЦП 30 и первом входе компаратора 33, который оказывается больше кода на втором входе компаратора 33. Вновь появляется сигнал на первом выходе компаратора 33 и в регистр 31 записывается код нового мгновенного значения напряжения. Процесс перезаписи в регистр 31 продолжается до момента записи кода амплитуды напряжения. После этого код на первом входе компаратора 33 оказывается меньше кода на втором входе и появляется сигнал на втором выходе компаратора 33, по фронту которого формирователь 35 вырабатывает импульс. Этим импульсом в регистр 32 заносится код амплитуды фазного напряжения. Одновременно импульс с выхода формирователя 35 поступает на элемент задержки 36, импульсом с выхода которого обнуляется регистр 31 и подготавливаются измерители 5 к измерению амплитуды очередной положительной полуволны фазного напряжения. Таким образом, на выходе регистра 32 измерителей 5-1, 5-2 и 5-3 устанавливаются и постоянно обновляются коды А, В и С амплитуды напряжения соответственно первой, второй и третьей фазы. С выхода измерителей 5-1, 5-2 и 5-3 коды А, В и С поступают на входы числовых компараторов 7, 8 и 9.

Если, например, к моменту времени t0 (фиг. 2) возникает разбалансировка фазных напряжений, то в момент времени t0 формируется код А амплитуды напряжения первой фазы. Через треть периода Т/3 в момент времени t1 (фиг. 2) формируется код В амплитуды напряжения второй фазы, еще через треть периода в момент времени t2 - код С амплитуды напряжения третьей фазы. Если, например, имеет место соотношение А>С>В, то к моменту времени t3 (фиг. 2) появится сигнал на первом выходе числового компаратора 7, подготавливающий элемент И 10 по первому входу, и сигнал на третьем выходе компаратора 9, подготавливающий элемент И 10 по второму входу. Элемент И 10 открывается, подавая сигнал на первый вход элемента ИЛИ 19. Сигнал с выхода элемента ИЛИ 19 поступает на второй вход вариатора 4-1 и далее на первый вход элемента И 26. В момент времени t3 (фиг. 2), когда завершается формирование очередного кода А, появляется импульс на выходе формирователя 35 измерителя 5-1, который через открытый электронный ключ 37 поступает на четвертый вход вариатора 4-1 и далее на второй вход элемента И 26. Через элемент И 26 на вычитающий вход счетчика 27 поступает импульс, уменьшая на единицу код на выходе счетчика 27. От этого кода зависит проводимость вариатора 4-1. При единичном коде на выходе счетчика 27 на управляющие электроды всех ключей 23-1…23-N поступают сигналы и они, открываясь, вводят в работу все резисторы 24-1…24-N, обеспечивая максимальную проводимость и минимальное сопротивление вариатора 4-1. При нулевом коде на выходе счетчика 27 на управляющих электродах всех ключей 23-1…23-N сигнал отсутствует и они закрыты. Все резисторы 24-1…24-N выведены из работы, поэтому проводимость вариатора стремится к нулю, а сопротивление - к бесконечности. Уменьшение на единицу кода на выходе счетчика 27 приводит к уменьшению проводимости вариатора 4-1 на одну ступень, равную проводимости резистора 24-1. Снижение проводимости вариатора 4-1 вызывает увеличение его сопротивления и падения напряжения Δu на нем, при этом на ступень снижается напряжение u=uo-Δu первой фазы нагрузки, амплитуда которого максимальна.

К моменту времени t4 (фиг. 2) присутствует сигнал на третьем выходе компаратора 8, которым по второму входу подготавливается элемент И 14, и сигнал на третьим выходе компаратора 9, который подготавливает элемент И 14 по первому входу. Элемент И 14 открывается и подает сигнал на первый вход элемента ИЛИ 20. С его выхода подается сигнал на первый вход вариатора 4-2 и далее на первый вход элемента И 25. В момент времени t4 (фиг. 2), когда в измерителе 5-2 завершается формирование кода В амплитуды второй фазы, появляется импульс на выходе формирователя 35 Х5-1 (фиг. 2), который через ключ 37 поступает четвертый вход вариатора 4-2 и далее на второй вход элемента И 25. Элемент И 25 пропускает импульс на суммирующий вход счетчика 27. Код на выходе счетчика 27 увеличивается на единицу. Проводимость вариатора 4-2 возрастает на одну ступень, падение напряжения на нем уменьшается. Напряжение второй фазы нагрузки, амплитуда которого минимальна, возрастает на ступень.

Если за счет однократной коррекции напряжения первой и второй фазы баланс не наступает, продолжается, как описано выше, сближение уровней напряжений путем ступенчатого снижения напряжения первой фазы в моменты времени t5, t7, t9 (фиг. 2) и увеличения напряжения второй фазы в моменты времени t6 и t8 (фиг. 2).

К моменту времени t10 (фиг. 2) складывается соотношение кодов амплитуд напряжений фаз А>В=С, и появляются сигналы на втором выходе компаратора 8 и третьем выходе компаратора 9, которые открывают элемент И14. Через элемент ИЛИ 20 проходит сигнал на первый вход вариатора 4-2, что вызывает увеличение на ступень напряжения второй фазы и приводит к соотношению кодов А>В>С. Поэтому к моменту времени t11 (фиг. 2) появляются сигналы на первом выходе компаратора 8 и третьем выходе компаратора 9, которыми открывается элемент И 18, подающий сигнал на первый вход вариатора 4-3. В момент времени t11 (фиг. 2) с приходом с выхода измерителя 5-3 импульса Х5-3 (фиг. 2) на четвертый вход вариатора 4-3 код на выходе счетчика 27 возрастает на единицу. При этом возрастает проводимость вариатора 4-3, а сопротивление его и падение напряжения Δu на нем уменьшаются. Напряжение u=uo-Δu третьей фазы нагрузки возрастает на ступень вместе с кодом С, что приводит к соотношению кодов А>В=С. К моменту времени t12 (фиг. 2) присутствуют сигналы на первом выходе компаратора 7 и третьем выходе компаратора 9, которые, поступая на входы элемента И 10, открывают его. Через элемент ИЛИ 19 проходит сигнал на второй вход вариатора 4-1. В момент времени t12 (фиг. 2) на четвертый вход вариатора 4-1 приходит сигнал Х5-1 (фиг. 2) с выхода измерителя 5-1, что вызывает очередное снижение напряжения первой фазы нагрузки.

В момент времени t13 (фиг. 2) происходит увеличение на ступень напряжения второй фазы нагрузки, как в момент времени t10, в момент времени t13 - увеличение на ступень напряжения третьей фазы нагрузки, как в момент времени t14, а в момент времени t15 - уменьшение на ступень напряжения первой фазы нагрузки, как в момент времени t12. При этом в момент времени t15 наступает баланс фазных напряжений нагрузки и равенство кодов А=В=С. Одновременно на вторых входах компараторов 7, 8 и 9 присутствуют сигналы, поступающие на входы элемента И-НЕ 38. Сигнал на выходе элемента И-НЕ 38 исчезает, и закрываются блокирующие ключи 37 измерителей 5-1, 5-2 и 5-3, что исключает изменение параметров вариаторов 4-1, 4-2 и 4-3 и флуктуацию фазных напряжений в условиях их фактического баланса.

При возникновении небаланса фазных напряжений при других соотношениях кодов А, В и С схема работает аналогично описанному выше. В любом случае, если наибольшее напряжение в первой фазе, то появляется сигнал на выходе логического элемента ИЛИ 19, если во второй, - то сигнал появляется на выходе логического элемента И 13, если в третьей, - то на выходе элемента ИЛИ 21. Эти сигналы поступают соответственно на вторые входы вариаторов 4-1, 4-2 и 4-3, что приводит к снижению соответствующего фазного напряжения. Если же наименьшее напряжение наблюдается в первой фазе, то сигнал появляется на выходе логического элемента И 12, если - во второй фазе, то - на выходе элемента ИЛИ 20, если - в третьей фазе, то - на выходе элемента И 18. Сигналы поступают соответственно на первые входы вариаторов 4-1, 4-2 и 4-3, и напряжение соответствующих фаз увеличивается.

Во всех случаях происходит последовательное ступенчатое уменьшение наибольшего из фазных напряжений и увеличение наименьшего из напряжений до наступления баланса на уровне среднего значения.

Точность обеспечения баланса напряжений определяется шагом квантования АЦП 30 и разрядностью элементов схемы. При N=10 погрешность и коэффициент небаланса не превышают 0,1%.

Источники информации

1. Полянский В.Ф, Попов А.В. Электрооборудование судов и предприятий: Учебник для вузов. - М.: Транспорт, 1989, с. 233-236.

2. Сугаков В.Г. Системы автоматического регулирования параметров электрической энергии судовых электростанций. Ч. 2. Автоматическое регулирование напряжения судовых источников электрической энергии: учеб. пособие / В.Г. Сугаков, О.С. Хватов. - Н. Новгород: Изд-во ФГОУ ВПО «ВГАВТ», 2011. С. 47-57.

3. Патент на изобретение RU №2510698, кл. Н02Р 9/14, 2014.

4. Патент на изобретение RU №2523005, кл. Н02Р 9/14, 2014.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОРРЕКТОР КАЧЕСТВА НАПРЯЖЕНИЯ | 2016 |

|

RU2643155C1 |

| КОРРЕКТОР НАПРЯЖЕНИЯ | 2016 |

|

RU2631862C1 |

| УСТРОЙСТВО КОРРЕКЦИИ НАПРЯЖЕНИЯ | 2016 |

|

RU2625351C1 |

| ТРЕХФАЗНЫЙ БЕСТРАНСФОРМАТОРНЫЙ НЕПОСРЕДСТВЕННЫЙ ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ | 2020 |

|

RU2758443C1 |

| БЕСТРАНСФОРМАТОРНЫЙ НЕПОСРЕДСТВЕННЫЙ ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ | 2018 |

|

RU2691968C1 |

| НЕПОСРЕДСТВЕННЫЙ ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ БЕСТРАНСФОРМАТОРНЫЙ | 2022 |

|

RU2787121C1 |

| НЕПОСРЕДСТВЕННЫЙ ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ И НАПРЯЖЕНИЯ | 2021 |

|

RU2784879C1 |

| СИСТЕМА ВОЗБУЖДЕНИЯ СИНХРОННОГО ГЕНЕРАТОРА | 2024 |

|

RU2822126C1 |

| Регулируемая реактивная нагрузка | 1989 |

|

SU1682983A1 |

| ВОЛНОВАЯ ГИДРОЭЛЕКТРОСТАНЦИЯ | 1993 |

|

RU2074328C1 |

Изобретение относится к области электротехники и может быть использовано для регулирования напряжения генераторов трехфазного переменного тока автономных источников электрической энергии. Технический результат - снижение небаланса фазных напряжений при работе на переменную неоднородную несимметричную нагрузку. Корректор небаланса фазных напряжений содержит трехфазный генератор (1) переменного тока с системой автоматического регулирования возбуждения (2), нагрузку (3), вариаторы (4-1, 4-2 и 4-3), измерители (5-1, 5-2 и 5-3) амплитуд напряжений, задающий регистр (6), числовые компараторы (7, 8 и 9), логические элементы И (10…18), логические элементы ИЛИ (19, 20 и 21), шину ПУСК (22). Каждый вариатор (4-1, 4-2 и 4-3) содержит с первого (23-1 по 23-N) электронные ключи, с первого (24-1 по 24-N) резисторы, причем сопротивление резистора в i-й ветви определяется соотношением Ri=R1·21-i, где R1 - сопротивление резистора первой ветви, логические элементы (И 25 и 26) и реверсивный счетчик (27). Измерители амплитуды (5-1, 5-2 и 5-3) имеют одинаковую структуру, которая включает измерительный трансформатор (28), диод (29), аналого-цифровой преобразователь (30), регистр памяти (31), выходной регистр (32), числовой компаратор (33), формирователи коротких импульсов (34 и 35) и элемент задержки (36), электронный ключ (37). В схему входят логический элемент И-НЕ (38) и диоды (39, 40 и 41). Устройство с высокой точностью обеспечивает баланс фазных напряжений нагрузки. 2 ил.

Корректор небаланса фазных напряжений, содержащий трехфазный генератор переменного тока с системой регулирования возбуждения и переменной неоднородной несимметричной нагрузкой, отличающийся тем, что, с целью снижения небаланса фазных напряжений при работе на переменную неоднородную несимметричную нагрузку, снабжен задающим регистром, тремя вариаторами, тремя числовыми компараторами, девятью логическими элементами И, тремя логическими элементами ИЛИ, логическим элементом И-НЕ, тремя измерителями амплитуд фазных напряжений, входы которых подключены на напряжения нагрузки соответствующих фаз, а разряды первого выхода первого измерителя амплитуд соединены с соответствующими разрядами первого входа первого числового компаратора и второго входа третьего числового компаратора, разряды первого выхода второго измерителя амплитуд соединены с соответствующими разрядами первого входа второго числового компаратора и второго входа первого числового компаратора, разряды первого выхода третьего измерителя амплитуд соединены с соответствующими разрядами первого входа третьего числового компаратора и второго входа второго числового компаратора, первый выход которого подключен к второму входу четвертого логического элемента И и второму входу девятого логического элемента И, выход которого связан с первым входом третьего вариатора, а первый вход - с третьим, а через диод и со вторым выходом третьего числового компаратора, первым входом пятого логического элемента И, первым входом второго логического элемента И и вторым входом первого логического элемента И, выход которого соединен с первым входом первого логического элемента ИЛИ, а первый вход - с вторым входом шестого логического элемента И, первым входом седьмого логического элемента И и первым выходом первого числового компаратора, третий, а через диод и второй выход которого подключены к второму входу второго логического элемента И, первому входу третьего логического элемента И, первому входу четвертого логического элемента И и второму входу восьмого логического элемента И, выход которого соединен с вторым входом третьего логического элемента ИЛИ, который связан выходом с вторым входом третьего вариатора, а первым входом - с выходом седьмого логического элемента И, второй вход которого соединен с первым выходом третьего числового компаратора, вторым входом третьего логического элемента И, первым входом шестого логического элемента И и первым входом восьмого логического элемента И, третий вход которого соединен с третьим выходом, а через диод и со вторым выходом второго числового компаратора, третьим входом второго логического элемента И и вторым входом пятого логического элемента И, выход которого подключен к первому входу второго логического элемента ИЛИ, второй вход которого связан с выходом шестого логического элемента И, а выход - с первым входом второго вариатора, второй вход которого соединен с выходом четвертого логического элемента И, разряды его пятого входа - с соответствующими разрядами выхода задающего регистра и разрядами пятых входов первого и третьего вариатора, его третий вход - с третьими входами первого и третьего вариатора и шиной ПУСК, его четвертый вход - с вторым выходом второго измерителя амплитуд, при этом второй выход третьего измерителя амплитуд связан с четвертым входом третьего вариатора, а второй выход первого измерителя амплитуд связан с четвертым входом первого вариатора, первый вход которого подключен к выходу третьего логического элемента И, а второй вход - к выходу первого логического элемента ИЛИ, связанного вторым входом с выходом второго логического элемента И, причем каждый измеритель амплитуд имеет измерительный трансформатор, первичная обмотка, зажимы которой являются входом измерителя, подключена на соответствующее фазное напряжение нагрузки, а вторичная обмотка через диод соединена с входом аналого-цифрового преобразователя, разряды выхода которого связаны с соответствующими разрядами первого входа числового компаратора и разрядами информационного входа регистра памяти, вход записи которого через первый формирователь коротких импульсов подключен к первому выходу числового компаратора, сбросовый вход регистра подключен к второму выходу числового компаратора через последовательно включенные элемент задержки и второй формирователь коротких импульсов, а разряды выхода регистра соединены с соответствующими разрядами второго входа числового компаратора и разрядами входа выходного регистра, выход которого является первым выходом измерителя, вторым выходом которого служит выход электронного ключа, вход которого соединен с выходом второго формирователя коротких импульсов и входом записи выходного регистра, причем управляющий электрод электронного ключа подключен к выходу логического элемента И-НЕ, входы которого связаны со вторыми выходами первого, второго и третьего компараторов, кроме того, каждый вариатор содержит N параллельных ветвей, включенных последовательно с нагрузкой соответствующей фазы и содержащих последовательно соединенные резистор и электронный ключ, управляющие электроды которых подключены к соответствующим разрядам выхода реверсивного счетчика, вход исходного числа которого служит пятым входом вариатора, а вход записи исходного числа - третьим входом вариатора, первым и вторым входами которого соответственно служат первые входы первого и второго логического элемента И вариатора, при этом их вторые входы соединены и являются четвертым входом вариатора, при этом выход первого логического элемента И подключен к суммирующему входу реверсивного счетчика, а выход второго логического элемента И - к вычитающему входу счетчика, причем сопротивление резистора в i-й ветви определяется соотношением

Ri=R1·2l-i, где R1 - сопротивление резистора первой ветви.

| СИСТЕМА ВОЗБУЖДЕНИЯ СИНХРОННОГО ГЕНЕРАТОРА С УПРАВЛЯЕМОЙ ВНЕШНЕЙ ФОРСИРОВКОЙ | 2013 |

|

RU2523005C1 |

| СИСТЕМА ВОЗДУЖДЕНИЯ СИНХРОННОГО ГЕНЕРАТОРА С ВНЕШНЕЙ ФОРСИРОВКОЙ | 2012 |

|

RU2510698C1 |

| Устройство для защиты асинхронного трехфазного электродвигателя от аварийного режима | 1984 |

|

SU1358033A1 |

| DE 102006013201 A1, 28.09.2006 | |||

| JPS 52125708 A, 21.10.1977 | |||

| US 8581558 B2, 12.11.2013 | |||

| Устройство разделения полос к ножницам продольной резки | 1984 |

|

SU1191207A1 |

Авторы

Даты

2016-04-10—Публикация

2014-12-22—Подача