Изобретение относится к преобразовательной технике и может быть использовано для питания частотноуправляемых электроприводов переменного тока и электроприводов постоянного тока.

Известен непосредственный преобразователь частоты (НПЧ), подключаемый к трем фазам питающей сети и имеющий шесть пар встречно параллельно включенных тиристоров [1].

Его недостатком является невысокое качество выходного напряжения, которое формируется из шести синусоид, а также зависимость выходного напряжения от вариации параметров напряжения питающей сети.

Известен НЧП содержащий, трансформатор, двадцать электронных ключей, распределитель импульсов, логический элемент НЕ, восемь логических элементов И, шесть логических элементов ИЛИ, задающий генератор, два делителя частоты, компаратор и узел развязки и усиления [2].

Недостатком данного НПЧ является зависимость параметров выходного напряжения от вариации параметров питающего напряжения.

Наиболее близким по технической сущности к изобретению является бестрансформаторный непосредственный преобразователь частоты, содержащий коммутатор, имеющий с первого по двадцать восьмой электронный ключ и распределитель импульсов, с первого по двенадцатый логические элементы И, логический элемент ИЛИ, задающие регистры частоты и амплитуды выходного напряжения, генератор стабильных импульсов, блок памяти, счетчик импульсов, числовой компаратор, с первого по одиннадцатый блок выбора наименьшего напряжения (БВНН), с первого по двенадцатый вычитатель, с первого по двенадцатый аналого-цифровой преобразователь, входы которых подключены к соответствующим напряжениям питающей сети, RS-триггер коммутатора, единичный вход которого подключен к первому выходу распределителя, а сбросовый вход - ко второму, причем каждый БВНН имеет числовой компаратор, первый вход которого является первым входом БВНН и его соответствующие разряды подключены к соответствующим разрядам входа первого n-разрядного электронного ключа, разряды выхода которого связаны с соответствующими разрядами регистра памяти, выход которого является третьим выходом БВНН, а вход записи соединен с выходом логического элемента ИЛИ, первый вход которого связан с выходом первого формирователя коротких импульсов, управляющим входом второго n-разрядного электронного ключа и сбросовым входом RS-триггера, прямой выход которого является первым выходом БВНН, а инверсный - вторым выходом БВНН, кроме того единичный вход RS-триггера связан со вторым входом логического элемента ИЛИ, управляющим входом первого n-разрядного электронного ключа и выходом второго формирователя коротких импульсов, вход которого соединен с выходами РАВНО и МЕНЬШЕ числового компаратора, выход БОЛЬШЕ которого подключен к входу первого формирователя коротких импульсов, а второй вход компаратора является вторым входом БВНН и его разряды соединены с соответствующими разрядами входа второго n-разрядного электронного ключа, разряды выхода которого связаны с соответствующими разрядами входа регистра памяти, причем выход генератора импульсов подключен к счетному входу счетчика, сбросовый вход которого соединен с выходом логического элемента ИЛИ, первый вход которого связан с шиной ПУСК, второй с - входом распределителя импульсов и выходом РАВНО числового компаратора, первый вход которого соединен с выходом счетчика и входом третьего адреса блока памяти, а второй вход компаратора - с выходом задающего регистра частоты и входом второго адреса блока памяти, вход первого адреса которого подключен к выходу задающего регистра амплитуды выходного напряжения, а соответствующие разряды выхода - к соответствующим разрядам вторых входов с первого по двенадцатый вычитатель, первые входы которых подключены к выходам с первого по двенадцатый аналого-цифрового преобразователя соответственно, а разряды выхода первого вычитателя соединены с соответствующими разрядами первого входа первого БВНН, второй вход которого связан с разрядами выхода второго вычитателя, первый выход - с первым входом первого элемента И, второй выход - с первым входом второго элемента И, разряды третьего выхода - с соответствующими разрядами первого входа четвертого БВНН, первый выход которого связан со вторыми входами первого и второго элемента И, второй выход - со вторыми входами третьего и четвертого элемента И, разряды третьего выхода - с соответствующими разрядами первого входа пятого БВНН, разряды второго входа - с соответствующими разрядами третьего выхода второго БВНН, первый выход которого соединен с первым входом третьего элемента И, второй выход - с первым входом четвертого элемента И, разряды первого входа - с соответствующими разрядами выхода третьего вычитателя, разряды второго входа - с соответствующими разрядами выхода четвертого вычитателя, а разряды выхода пятого вычитателя подключены к соответствующим разрядам первого входа третьего БВНН, разряды второго входа которого связаны с соответствующими разрядами выхода шестого вычитателя, первый выход - с первым входом пятого элемента И, второй выход - с первым входом шестого элемента И, разряды третьего выхода - с соответствующими разрядами второго входа пятого БВНН, первый выход которого подключен к третьему входу первого элемента И, второй выход - к вторым входам пятого и шестого элемента И, разряды третьего выхода - к соответствующим разрядом первого входа одиннадцатого БВНН, первый выход которого соединен с третьими входами пятого и шестого элемента И и четвертыми входами первого, второго, третьего и четвертого элемента И, второй выход - с третьими входами одиннадцатого и двенадцатого элемента И и четвертыми входами седьмого, восьмого, девятого и десятого элемента И, разряды второго входа - с соответствующими разрядами выхода десятого БВНН, разряды второго входа которого связаны с соответствующими разрядами третьего выхода восьмого БВНН, первый выход - с третьими входами седьмого, восьмого, девятого и десятого элемента И, второй выход - со вторыми входами одиннадцатого и двенадцатого элемента И, разряды первого входа - с соответствующими разрядами третьего выхода девятого БВНН, первый выход которого подключен к вторым входам седьмого и восьмого элемента И, второй выход - к вторым входам девятого и десятого элемента И, разряды второго входа - к соответствующим разрядам третьего выхода седьмого БВНН, разряды первого входа - к соответствующим разрядам третьего выхода шестого БВНН, первый выход которого соединен с первым входом седьмого элемента И, второй выход - с первым входом восьмого элемента И, разряды первого входа - с соответствующими разрядами выхода седьмого вычитателя, разряды второго входа - с соответствующими разрядами выхода восьмого вычитателя, а разряды выхода девятого вычитателя подключены к соответствующим разрядам первого входа седьмого БВНН, с разрядами второго входа которого связаны соответствующие разряды выхода десятого вычитателя, первый выход - с первым входом девятого элемента И, второй выход - с первым входом десятого элемента И, а разряды выхода одиннадцатого вычитателя подключены к соответствующим разрядам первого входа восьмого БВНН, разряды второго входа которого связаны с соответствующими разрядами выхода двенадцатого вычитателя, первый выход - с первым входом одиннадцатого элемента И, второй выход - с первым входом двенадцатого элемента И, выход которого подключен к управляющему входу двадцать третьего и двадцать четвертого ключа, а выход одиннадцатого элемента И подключен к управляющему входу двадцать первого и двадцать второго ключа, выход десятого элемента И - к управляющему входу девятнадцатого и двадцатого ключа, выход девятого элемента И - к управляющему входу семнадцатого и восемнадцатого ключа, выход восьмого элемента И - к управляющему входу пятнадцатого и шестнадцатого ключа, выход седьмого элемента И - к управляющему входу тринадцатого и четырнадцатого ключа, выход шестого элемента И - к управляющему входу одиннадцатого и двенадцатого ключа, выход пятого элемента И - к управляющему входу девятого и десятого ключа, выход четвертого элемента И - к управляющему входу седьмого и восьмого ключа, выход третьего элемента И - к управляющему входу пятого и шестого ключа, выход второго элемента И - к управляющему входу третьего и четвертого ключа, выход первого элемента И - к управляющему входу первого и второго ключа, кроме того выходы ключей с нечетными номерами с первого по двадцать третий подключены к входу двадцать пятого и двадцать восьмого ключа, а выходы ключей с четными номерами со второго по двадцать четвертый подключены к входу двадцать шестого и двадцать седьмого ключа, выход которого связан с выходом двадцать пятого ключа и первым зажимом нагрузки, а управляющий вход соединен с инверсным выходом RS-триггера и управляющим входом двадцать восьмого ключа, выход которого связан с выходом двадцать шестого ключа и вторым зажимом нагрузки, а управляющий вход - с прямым выходом RS-триггера и управляющим входом двадцать пятого ключа, причем к первой фазе питающей сети подключены входы первого, третьего, двенадцатого, четырнадцатого, шестнадцатого и двадцать третьего ключей, к второй фазе - входы седьмого, девятого, одиннадцатого, двадцатого, двадцать второго и двадцать четвертого ключа, к третий фазе - входы четвертого, шестого, восьмого, пятнадцатого, семнадцатого и девятнадцатого ключа, а к нейтрали питающей сети - входы второго, пятого, десятого, тринадцатого, восемнадцатого и двадцать первого ключа [3].

Недостатком данного преобразователя является невозможность формирования постоянного напряжения заданной величины.

Цель изобретения расширение функциональных возможностей за счет возможности формирования постоянного напряжения заданной величины и полярности.

Цель изобретения достигается тем, непосредственный преобразователь частоты и напряжения, содержащий коммутатор, имеющий RS-триггер коммутатора, с первого по двадцать восьмой электронный ключ и распределитель импульсов, с первого по двенадцатый логические элементы И, логический элемент ИЛИ, задающие регистры частоты и амплитуды выходного напряжения, генератор стабильных импульсов, блок памяти, счетчик импульсов, числовой компаратор, с первого по одиннадцатый блок выбора наименьшего напряжения (БВНН), с первого по двенадцатый вычитатель, с первого по двенадцатый аналого-цифровой преобразователь, входы которых подключены к соответствующим напряжениям питающей сети, причем каждый БВНН имеет числовой компаратор, первый вход которого является первым входом БВНН и его соответствующие разряды подключены к соответствующим разрядам входа первого n-разрядного электронного ключа, разряды выхода которого связаны с соответствующими разрядами регистра памяти, выход которого является третьим выходом БВНН, а вход записи соединен с выходом логического элемента ИЛИ, первый вход которого связан с выходом первого формирователя коротких импульсов, управляющим входом второго n-разрядного электронного ключа и сбросовым входом RS-триггера, прямой выход которого является первым выходом БВНН, а инверсный - вторым выходом БВНН, кроме того единичный вход RS-триггера связан со вторым входом логического элемента ИЛИ, управляющим входом первого n-разрядного электронного ключа и выходом второго формирователя коротких импульсов, вход которого соединен с выходами РАВНО и МЕНЬШЕ числового компаратора, выход БОЛЬШЕ которого подключен к входу первого формирователя коротких импульсов, а второй вход компаратора является вторым входом БВНН и его разряды соединены с соответствующими разрядами входа второго n-разрядного электронного ключа, разряды выхода которого связаны с соответствующими разрядами входа регистра памяти, причем выход генератора импульсов подключен к счетному входу счетчика, сбросовый вход которого соединен с выходом логического элемента ИЛИ, первый вход которого связан с шиной ПУСК, второй с - первым входом распределителя импульсов и выходом РАВНО числового компаратора, первый вход которого соединен с выходом счетчика и входом третьего адреса блока памяти, а второй вход компаратора - с выходом задающего регистра частоты и входом второго адреса блока памяти, вход первого адреса которого подключен к выходу задающего регистра выходного напряжения, кроме того разряды первого входа с первого по двенадцатого вычитателя подключены к выходам разрядов с первого по двенадцатого аналого-цифрового преобразователя соответственно, а разряды выхода первого вычитателя соединены с соответствующими разрядами первого входа первого БВНН, второй вход которого связан с разрядами выхода второго вычитателя, первый выход - с первым входом первого элемента И, второй выход - с первым входом второго элемента И, разряды третьего выхода - с соответствующими разрядами первого входа четвертого БВНН, первый выход которого связан со вторыми входами первого и второго элемента И, второй выход - со вторыми входами третьего и четвертого элемента И, разряды третьего выхода - с соответствующими разрядами первого входа пятого БВНН, разряды второго входа - с соответствующими разрядами третьего выхода второго БВНН, первый выход которого соединен с первым входом третьего элемента И, второй выход - с первым входом четвертого элемента И, разряды первого входа - с соответствующими разрядами выхода третьего вычитателя, разряды второго входа - с соответствующими разрядами выхода четвертого вычитателя, а разряды выхода пятого вычитателя подключены к соответствующим разрядам первого входа третьего БВНН, разряды второго входа которого связаны с соответствующими разрядами выхода шестого вычитателя, первый выход - с первым входом пятого элемента И, второй выход - с первым входом шестого элемента И, разряды третьего выхода - с соответствующими разрядами второго входа пятого БВНН, первый выход которого подключен к третьему входу первого элемента И, второй выход - к вторым входам пятого и шестого элемента И, разряды третьего выхода - к соответствующим разрядом первого входа одиннадцатого БВНН, первый выход которого соединен с третьими входами пятого и шестого элемента И и четвертыми входами первого, второго, третьего и четвертого элемента И, второй выход - с третьими входами одиннадцатого и двенадцатого элемента И и четвертыми входами седьмого, восьмого, девятого и десятого элемента И, разряды второго входа - с соответствующими разрядами выхода десятого БВНН, разряды второго входа которого связаны с соответствующими разрядами третьего выхода восьмого БВНН, первый выход - с третьими входами седьмого, восьмого, девятого и десятого элемента И, второй выход - со вторыми входами одиннадцатого и двенадцатого элемента И, разряды первого входа - с соответствующими разрядами третьего выхода девятого БВНН, первый выход которого подключен к вторым входам седьмого и восьмого элемента И, второй выход - к вторым входам девятого и десятого элемента И, разряды второго входа - к соответствующим разрядам третьего выхода седьмого БВНН, разряды первого входа - к соответствующим разрядам третьего выхода шестого БВНН, первый выход которого соединен с первым входом седьмого элемента И, второй выход - с первым входом восьмого элемента И, разряды первого входа - с соответствующими разрядами выхода седьмого вычитателя, разряды второго входа - с соответствующими разрядами выхода восьмого вычитателя, а разряды выхода девятого вычитателя подключены к соответствующим разрядам первого входа седьмого БВНН, с разрядами второго входа которого связаны соответствующие разряды выхода десятого вычитателя, первый выход - с первым входом девятого элемента И, второй выход - с первым входом десятого элемента И, а разряды выхода одиннадцатого вычитателя подключены к соответствующим разрядам первого входа восьмого БВНН, разряды второго входа которого связаны с соответствующими разрядами выхода двенадцатого вычитателя, первый выход - с первым входом одиннадцатого элемента И, второй выход - с первым входом двенадцатого элемента И, выход которого подключен к управляющему входу двадцать третьего и двадцать четвертого ключа, а выход одиннадцатого элемента И подключен к управляющему входу двадцать первого и двадцать второго ключа, выход десятого элемента И - к управляющему входу девятнадцатого и двадцатого ключа, выход девятого элемента И - к управляющему входу семнадцатого и восемнадцатого ключа, выход восьмого элемента И - к управляющему входу пятнадцатого и шестнадцатого ключа, выход седьмого элемента И - к управляющему входу тринадцатого и четырнадцатого ключа, выход шестого элемента И - к управляющему входу одиннадцатого и двенадцатого ключа, выход пятого элемента И - к управляющему входу девятого и десятого ключа, выход четвертого элемента И - к управляющему входу седьмого и восьмого ключа, выход третьего элемента И - к управляющему входу пятого и шестого ключа, выход второго элемента И - к управляющему входу третьего и четвертого ключа, выход первого элемента И - к управляющему входу первого и второго ключа, кроме того выходы ключей с нечетными номерами с первого по двадцать третий подключены к входу двадцать пятого и двадцать восьмого ключа, а выходы ключей с четными номерами со второго по двадцать четвертый подключены к входу двадцать шестого и двадцать седьмого ключа, выход которого связан с выходом двадцать пятого ключа и первым зажимом нагрузки, а управляющий вход соединен с инверсным выходом RS-триггера и управляющим входом двадцать восьмого ключа, выход которого связан с выходом двадцать шестого ключа и вторым зажимом нагрузки, а управляющий вход - с прямым выходом RS-триггера и управляющим входом двадцать пятого ключа, причем к первой фазе питающей сети подключены входы первого, третьего, двенадцатого, четырнадцатого, шестнадцатого и двадцать третьего ключей, к второй фазе - входы седьмого, девятого, одиннадцатого, двадцатого, двадцать второго и двадцать четвертого ключа, к третий фазе - входы четвертого, шестого, восьмого, пятнадцатого, семнадцатого и девятнадцатого ключа, а к нейтрали питающей сети - входы второго, пятого, десятого, тринадцатого, восемнадцатого и двадцать первого ключа, снабжен логическим элементом НЕ, третьим и четвертым n-разрядным электронными ключами, двухразрядным электронным ключом, переключателем полярности выходного напряжения, выключателем режима, один зажим которого подключен к шине сигнала единичного уровня, а второй зажим - к управляющим входам двухразрядного электронного ключа и третьего n-разрядного электронного ключа и входу логического элемента НЕ, выход которого связан с входом переключателя полярности выходного напряжения и управляющим входом четвертого n-разрядного электронного ключа, разряды входа которого соединены с соответствующими разрядами выхода блока памяти, а разряды выхода - с соответствующими разрядами выхода третьего n-разрядного электронного ключа и вторыми входами с первого по двенадцатый вычитателей, кроме того первый и второй выходы распределителя соединены с соответствующими входами двухразрядного электронного ключа, первый выход которого связан с единичным входом RS-триггера и первым выходом переключателя полярности выходного напряжения, второй выход которого соединен со сбросовым входом RS-триггера и вторым выходом двухразрядного электронного ключа, а разряды входа третьего n-разрядного электронного ключа подключены к соответствующим разрядам выхода задающий регистр выходного напряжения

Выключатель режима, логический элемент НЕ и их связи обеспечивают перевод НПЧН из режима преобразователя частоты в режим управляемого выпрямителя. Третий и четвертый n-разрядные электронные ключа, двухразрядный электронный ключ и их связи переводят НПЧН в режим управляемого выпрямителя. Переключатель полярности выходного напряжения позволяет изменять полярность выходного напряжения.

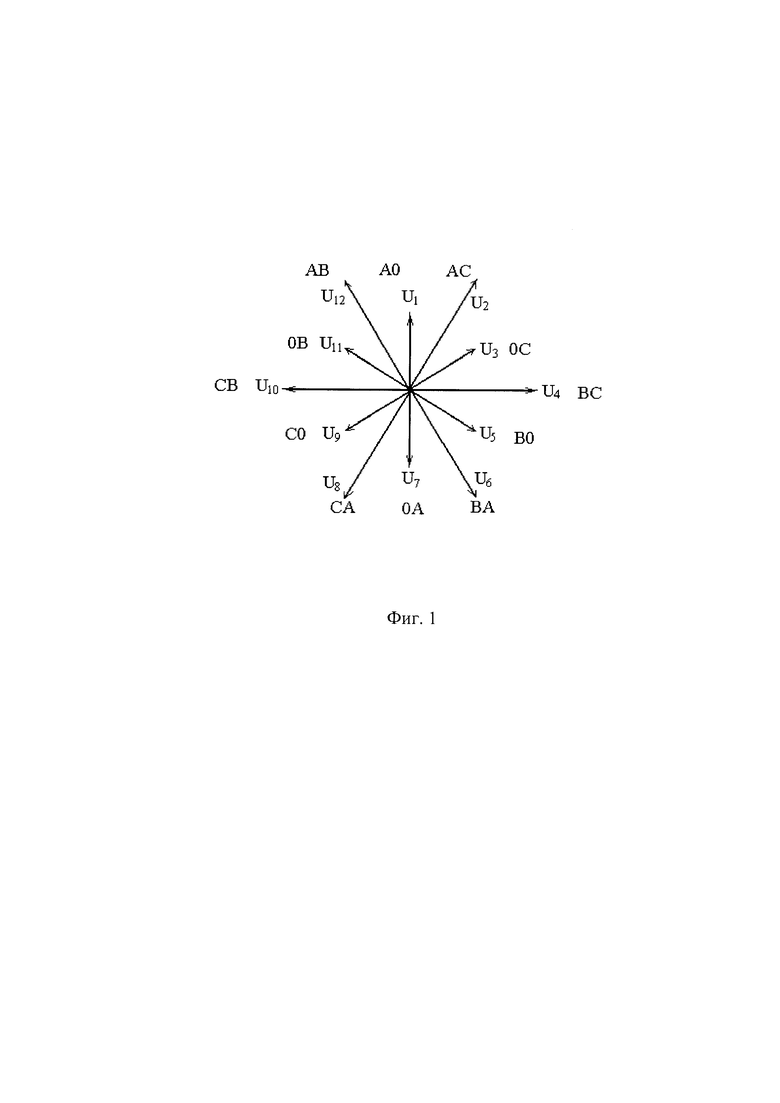

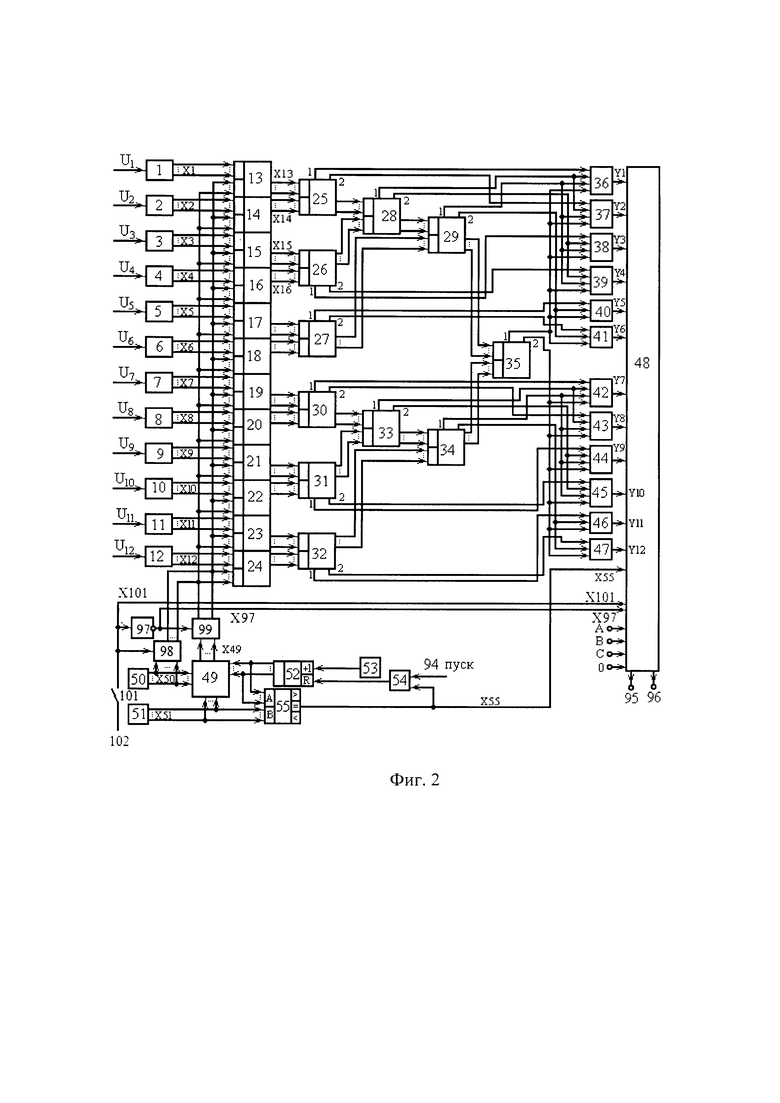

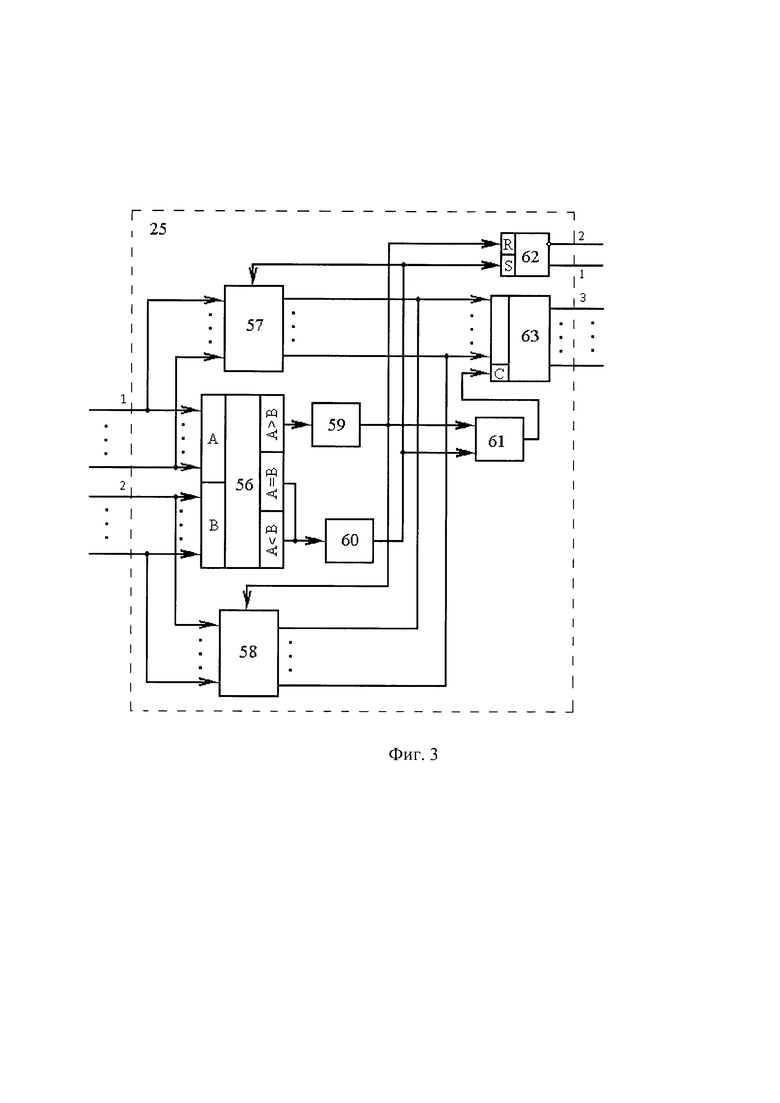

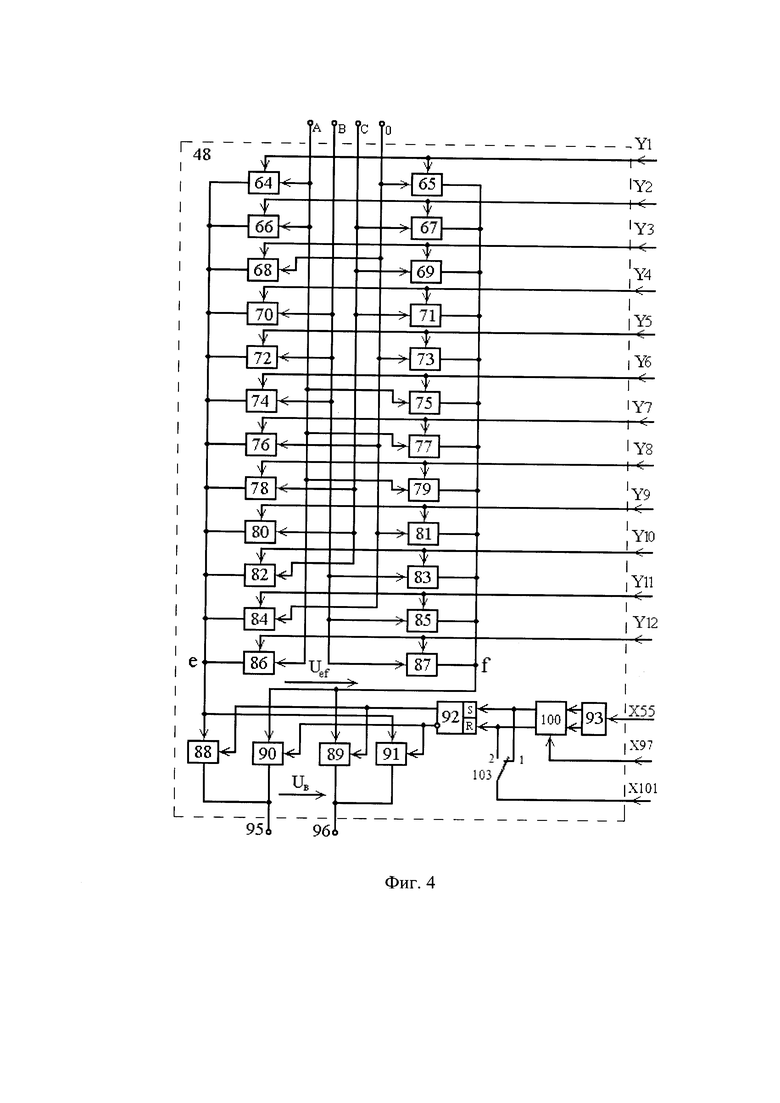

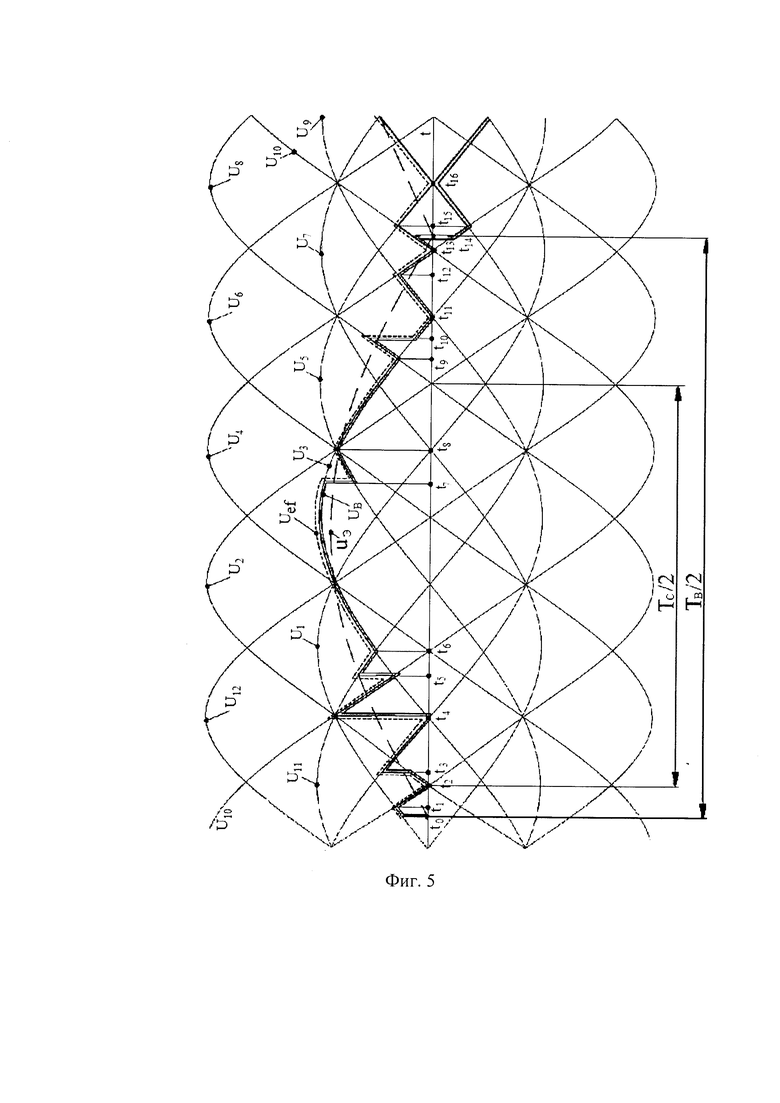

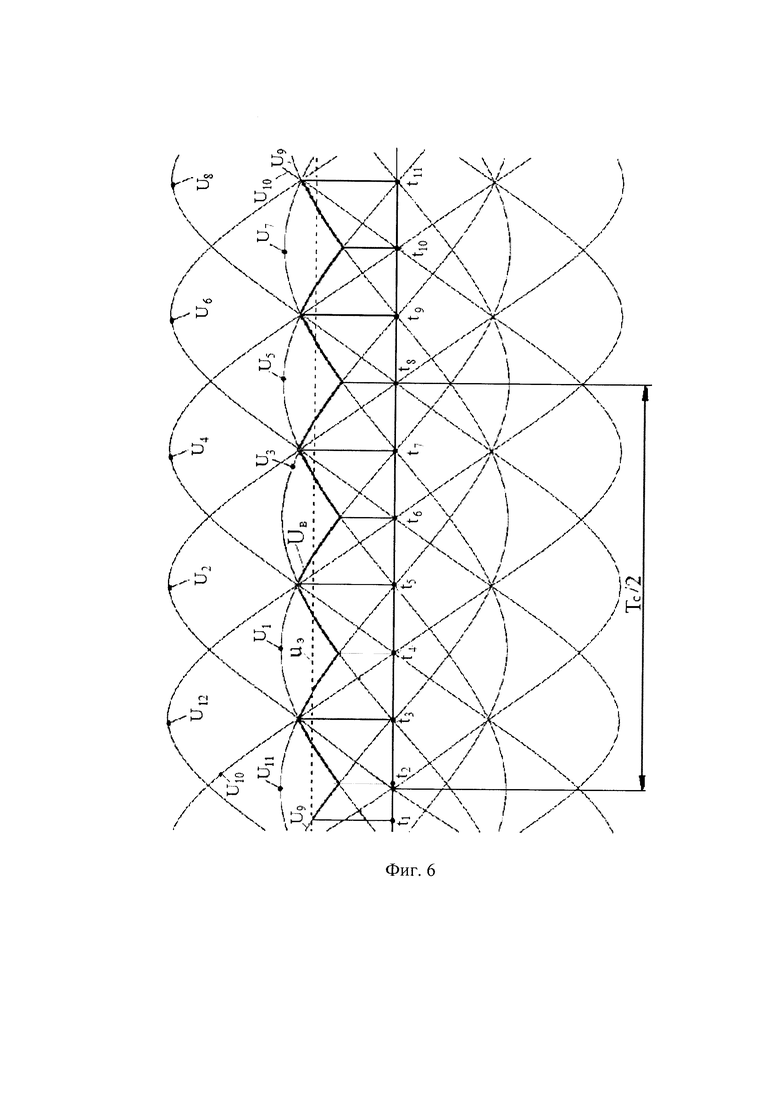

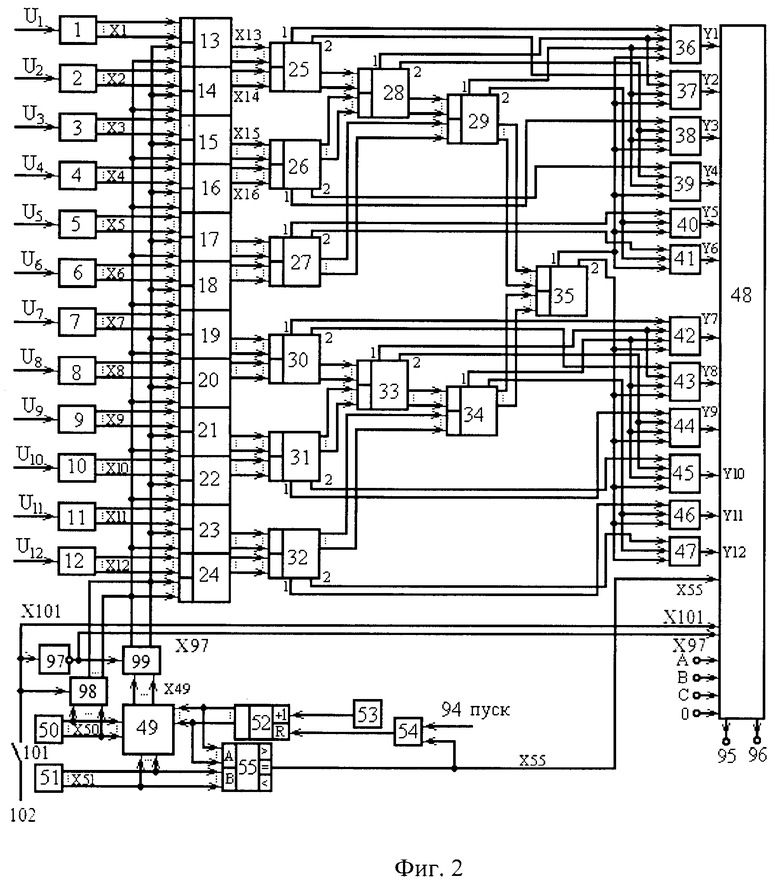

На фиг. 1 представлены векторные диаграммы системы питающего напряжения, на фиг. 2 - схема непосредственного преобразователя частоты и напряжения (НПЧН), на фиг. 3 - схема блока выбора наименьшего напряжения (БВНН), на фиг. 4 - схема коммутатора, на фиг. 5 - временные диаграммы формирования выходного напряжения при работе в режиме преобразователя частоты, на фиг. 6 - временные диаграммы формирования выходного напряжения при работе в режиме управляемого выпрямителя.

Непосредственный преобразователь частоты и напряжения (НПЧН) содержит (см. фиг. 2) с первого по двенадцатый аналого-цифровые преобразователи (АЦП) 1...12, с первого по двенадцатый вычитатели 13…24, с первого по одиннадцатый блоки выбора наименьшего напряжения (БВНН) 25…35, с первого по двенадцатый логические элементы И 36…47, коммутатор 48, блок памяти 49, задающий регистр выходного напряжения 50, задающий регистр частоты 51, суммирующий счетчик 52, генератор стабильных импульсов 53, логический элемент ИЛИ 54, числовой компаратор 55. Блоки выбора наименьшего напряжения (см. фиг. 3) 25…35 имеют одинаковую структуру, включающую числовой компаратор 56, входы которого являются входами БВНН, первый 57 и второй 58 n-разрядные электронные ключи, первый 59 и второй 60 формирователи коротких импульсов, логический элемент ИЛИ 61, RS-триггер 62 прямой выход которого является первым выходом БВНН, инверсный выход - вторым выходом БВНН, а выход регистра памяти 63 служит третьим выходом блока. Коммутатор 48 (см. фиг. 4) подключается к шинам питающего напряжения А, В, С и 0. В его состав входят с первого по двадцать восьмой электронные ключи 64…91, RS-триггер 92, распределитель импульсов 93, шина ПУСК 94, первый 95 и второй 96 выходные зажимы преобразователя, логический элемент НЕ 97, третий 98 и четвертый 99 n-разрядные электронные ключи, двухразрядный электронный ключ 100, выключатель 101 режима, шина 102 сигнала единичного уровня, переключатель 103 полярности выходного напряжения.

В режиме преобразователя частоты устройство работает следующим образом. Режим вводится выключателем 101 (см. фиг. 2) контакты, которого разомкнуты. При этом на входе логического элемента НЕ 97 сигнал X101 отсутствует и ключ 98 закрыт, а ключи 99 и 100 открываются сигналом Х97 с выхода логического элемента НЕ 97. Источник питания для НПЧ имеет трехфазную систему напряжений с выведенной нулевой точкой. Эта система позволяет иметь три прямых фазных напряжения UA0, UB0, UC0 и соответствующие обратные фазные напряжения U0A, U0B, U0C, а также три прямых линейных напряжений UAB, UBC, UCA и соответствующие обратные линейные напряжения UBA, UCB, UAC. Из этих напряжений можно создать систему двенадцати напряжений (см. фиг. 1), имеющих фазовый сдвиг 30°: U1=UA0, U2=UAC, U3=U0C, U4=UBC, U5=UB0, U6=UBA, U7=U0A, U8=UCA, U9=UC0, U10=UCB, U11=U0B, U12=UAB. Напряжения этой системы с нечетными индексами имеют амплитуду равную амплитуде фазного напряжения источника питания Uфм, а напряжения с нечетными индексами - равную амплитуде линейного напряжения Uлм. Напряжения U1, U2…U12 соответственно подаются на входы АЦП 1…12, на выходах которых появляются коды X1, Х2…Х12 этих напряжений, поступающие на первые входы соответственно вычитателей 13…24.

На выходе задающего регистра 50 (см. фиг. 2) устанавливается код амплитуды выходного напряжения Х50, который подается на вход первого адреса блока памяти 49, а на вход второго адреса - код частоты выходного напряжения Х51 (код полупериода) с выхода задающего регистра 51. При подаче питающего напряжения одновременно поступает сигнал на шину 94 ПУСК, который через элемент ИЛИ 54 подается на сбросовый вход счетчика 52, и на выходах разрядов счетчика 52 устанавливается нулевой код. С выхода генератора 53 поступают импульсы на вход счетчика 52, и с каждым импульсом код на выходе счетчика 52 возрастает на единицу. Этот код, характеризующий текущее время, подается на вход третьего адреса блока памяти 49, и на его выходе появляется код Х49 мгновенного значения идеальной кривой выходного напряжения, соответствующего заданной частоте и амплитуде. С ростом кода на выходе счетчика 52 из блока памяти 49 извлекаются коды мгновенных значений за положительный полупериод напряжения. Когда текущее время достигает полупериода, код на выходе счетчика 52 оказывается равным коду Х51 заданной частоты на выходе задатчика 51. При этом оказываются равными коды на входах компаратора 55, и на его выходе РАВНО появляется сигнал, который проходит через элемент ИЛИ 54 и обнуляет счетчик 52, подготавливая его для отсчета времени очередного полупериода. С выхода блока памяти 49 код Х49 мгновенных значений идеальной кривой выходного напряжения поступает через открытый ключ 99 на вторые входы вычитателей 13…24, на первых входах которых присутствуют коды X1, Х2…Х12 соответственно напряжений U1, U2…U12. На выходах вычитателей 13…24, появляются коды модуля отклонения Х13=|Х1-Х49|, Х14=[Х2-Х49|…Х24=|Х12-Х49|, соответствующих мгновенных напряжений U1, U2…U12 питающей системы и кода идеального выходного напряжения Х49, заложенного в блоке памяти 49. Эти коды отклонений X13, X14, … Х24 попарно подаются на входы БВНН 25, 26, 27, 30, 31, 32 для выявления в каждой паре напряжения с наименьшим отклонением, т.е. предпочтительного напряжения для использования в формировании выходного напряжения с заданными параметрами в данный момент времени.

На первый вход БВНН 25 подается код отклонения первого напряжения U1, который поступает на вход электронного ключа 57 и первый вход компаратора 56. На второй вход БВНН 25 подается код отклонения второго напряжения U2, который поступает на вход электронного ключа 58 и второй вход компаратора 56.

Если напряжение U1, связанное с первым входом БВНН, имеет меньшее или равное отклонение в сравнении с напряжением U2, связанным со вторым входом, то появляется сигнал на выходе МЕНЬШЕ или РАВНО компаратора 56, который поступает на вход формирователя 60. Короткий импульс с выхода формирователя 60 открывает электронный ключ 57, который подает на информационный вход регистра памяти 63 код отклонения, поданный на первый вход БВНН. Этот код записывается в регистр 63 импульсом с выхода формирователя 60 и поступает на третий выход БВНН. Одновременно с прямого выхода RS-триггера 62 поступает сигнал на первый выход БВНН.

Если меньшее отклонение имеет напряжение U2, связанное со вторым входом БВНН, то появляется сигнал на выходе БОЛЬШЕ компаратора 56 и импульсом с выхода формирователя 59 RS-триггер 62 переводится в нулевое состояние, обеспечивая подачу с инверсного выхода сигнала на второй выход БВНН. Одновременно этим же импульсом с выхода формирователя 60, проходящем через элемент ИЛИ 61, в регистр 63 через ключ 58, записывается код отклонения, поданный на второй вход БВНН, который поступает на третий выход БВНН.

Таким образом, БВНН осуществляет выбор кода наименьшего отклонения, подавая его на третий выход, а на первом и втором выходах формирует признак напряжения с наименьшим отклонением из двух напряжений связанных с входами БВНН. В результате на третьем выходе блока 25 появляется наименьшее отклонение первого и второго напряжения Min{U1,U2}, блока 26 - третьего и четвертого напряжения Min{U3,U4}, блока 27 - Min{U5,U6}, блока 30 - Min{U7,U8}, блока 31 - Min{U9,U10}, блока 32 - Min{U11,U12}. БВНН 25, 26, 27, 30, 31 и 32 выдают результаты сравнения пары напряжений, а БВНН 28 и 33 четырех напряжений: блок 28 - Min{U1, U2, U3, U4}, а блок 33 - Min {U7, U8, U9, U10}. БВНН 29 и 34 выдают результаты по сравнению шести напряжений: блок 28 - Min{U1, U2, U3, U4, U5, U6}, а блок 34 - Min{U7, U8, U9, U10, U11, U12}. Результат сравнения всех напряжений выдает блок 35 Min{U1, U2, U3, U4, U5, U6, U7, U8, U9, U10, U11, U12}.

Если в процессе сравнения появляются сигналы на первых выходах БВНН 25, 28, 29 и 35, то с выхода элемента И 36 подается сигнал Y1 на управляющие входы электронных ключей 64 и 65 коммутатора 48 (см. фиг. 4), которые к выходному зажиму 95 подключают шину А, а к зажиму 96 - шину 0, т.е. к выходным зажимам подключается напряжение U1, как наиболее подходящее в данный момент времени, для формирования кривой выходного напряжения.

Когда в процессе сравнения появляются сигналы на первых выходах блоков 28, 29, 35 и втором выходе блока 25, то с выхода элемента И 37 подается сигнал Y2 на управляющие входы ключей 66 и 67 коммутатора 48 (см. фиг. 4). К зажиму 96 подключается шина А, а к зажиму 96 - шина С, т.е. к выходным зажимам подключается напряжение U2.

Если в процессе сравнения появляются сигналы на первых выходах блоков 26, 29, 35 и втором выходе блока 28, то с выхода элемента И 38 подается сигнал Y3 на управляющие входы ключей 68 и 69 коммутатора 48 (см. фиг. 4). Ключ 68 подключает шину 0 к зажиму 95, а ключ 69 - шину С к зажиму 96. К выходным зажимам подключается напряжение U3.

Если появляются сигналы на вторых выходах блоков 26, 28 и первых выходах блоков 29, 35, то открывается элемент И 39 и на управляющие входы электронных ключей 70 и 71 поступает сигнал Y4. При этом зажим 95 через ключ 70 подключается к шине В, а зажим 96 - через ключ 71 к шине С, т.е. к выходным зажимам подключается напряжение U4.

Когда появляются сигналы на первых выходах блоков 27, 35 и втором выходе блока 29, открывается элемент И 40 и сигнал Y5 с его выхода включает ключи 72 и 73. Ключ 72 подключает шину В к зажиму 95, а ключ 73 - шину 0 к зажиму 96 и на выходные зажимы подается напряжение U5.

При наличии сигналов на вторых выходах блоков 27, 29 и первом выходе блока 35 появляется сигнал Y6 на выходе элемента И 41, поступающий на входы управления ключей 74 и 75. Открывшиеся ключи 74 и 75 подключают к зажиму 95 шину В, к зажиму 96 шину А, т.е. на выходные зажимы подается напряжение U6.

Если в процессе сравнения появляются сигналы на первых выходах блоков 30, 33, 34 и втором выходе блока 35, то появляется сигнал Y7 на выходе элемента И 42, который открывает ключи 76 и 77. Ключ 76 подключает зажим 95 к шине 0, а ключ 77 - зажим 96 к шине А, подавая на выходные зажимы напряжение U7.

Если одновременно присутствуют сигналы первых выходах блоков 33, 34 и вторых выходах блоков 30, 35, открывается элемент И 43, на выходе которого появляется сигнал Y8, поступающий на управляющие входы ключей 78 и 79. Они открываются и ключ 78 подключает шину С к зажиму 95, а ключ 79 - шину А к зажиму 96, подавая на выходные зажимы напряжение U8.

Когда появляются сигналы на первых выходах блоков 31, 34 и вторых выходах блоков 33, 35 появляется сигнал Y9 на выходе элемента И 44, который подается на управляющие входы электронных ключей 80 и 81. Открывшийся ключ 80 подключает зажим 95 к шине С, а ключ 81 - зажим 96 к шине 0, и на выходных зажимах оказывается напряжение U9.

При наличии сигналов на вторых выходах блоков 31, 33, 35 и на первом выходе блока 34 открывается элемент И 45 и появляется сигнал Y10 на его выходе, поступающий на управляющие входы электронных ключей 82 и 83, которые открываются. Ключ 82 соединяет зажим 95 с шиной С, а ключ 83 - зажим 96 с шиной В, подавая на выходные зажимы напряжение U10.

Если присутствуют сигналы на вторых выходах блоков 34, 35 и первом выходе блока 32, появляется сигнал Y11 на выходе элемента И 46, которым открываются ключи 84 и 85. Ключом 84 зажим 95 подключается к шине 0, а ключом 85 - зажим 96 к шине В, подавая на выходные зажимы напряжение U11.

Когда имеются сигналы на вторых выходах блоков 32, 34 и 35 открывается элемент И 47 и сигналом Y12 с его выхода включаются ключи 86 и 87. Ключ 86 связывает зажим 95 с шиной А, а ключ 87 - зажим 96 с шиной В. При этом на выходные зажимы подается напряжение U12.

Подача соответствующих напряжений U1…U12 на выходные зажимы 95 и 96 при формировании положительной полуволны выходного напряжения происходит, как описано выше. При этом шина е (см. фиг. 4) подключается к зажиму 95 через ключ 88, а шина ƒ - к зажиму 96 через ключ 89. Для формирования отрицательной полуволны меняются связи между шинами e, ƒ и зажимами 95, 96 с помощью ключей 90, 91. Ключ 90 подключает шину ƒ к зажиму 95, а ключ 91 - шину е к зажиму 96. Управление ключами 88, 89 и 90, 91 осуществляется триггером 92.

Одновременно с включением НПЧН подается сигнал на шину ПУСК 94, которым обнуляется счетчик 52. С выхода генератора 53 стабильных импульсов на суммирующий вход счетчика 52 проходят импульсы, и на его выходе формируется возрастающий код Kt текущего времени t, которое связано с кодом выражением

где Т53 - период следования импульсов генератора 53.

Код Kt текущего времени поступает на вход третьего адреса блока памяти 49. На входе второго адреса блока 49 присутствует код КТ половины периода ТВ/2 выходного напряжения, который устанавливается задающим регистром 51. Код КТ половины периода связан с частотой fв выходного напряжения и частотой f53 и импульсов генератора 53 выражением

Задающим регистром 50 на вход первого адреса блока памяти 49 подается код KUm амплитуды выходного напряжения Um в, которые связаны выражением

где ΔU1-12 - ступень квантования АЦП 1…12.

В ячейках блока памяти 49 записаны коды KUO мгновенных значений эталонного напряжения uЭ(Х) с идеально синусоидальной формой, которые связаны выражением

В зависимости от текущего времени t, заданной амплитуды Um в и частоты fв выходного напряжения на выходе блока памяти 49 появляется соответствующий код KUЭ эталонного напряжения, который поступает на вторые входы вычитателей 13…24, которые определяют отклонения напряжений U1…U12 от эталонного.

При включении НПЧН в момент времени t0 (см. фиг. 5) для формирования выходного напряжения Uв, имеющего меньшую частоту и амплитуду, чем питающее напряжение, появляется сигнал Y1, который поступает на управляющие входы электронных ключей 64 и 65 коммутатора 48 (см. фиг. 4). К шинам е и f подключается напряжение U1 и появляется напряжение Uef, которое через открытые ключи 88 и 89 подается на зажимы нагрузки 95 и 96 при этом Uв=Uef, обеспечивая формирование положительной полуволны выходного напряжения.

В момент времени t1 (см. фиг. 5) появляется сигнал Y8, который поступает на управляющие входы электронных ключей 78 и 79 коммутатора 48 (см. фиг. 4) подключающие к выходу напряжение U8.

В момент времени t2 (см. фиг. 5) наиболее подходящим является напряжение U2, которое подключается к выходу коммутатором 48 (см. фиг. 4) по сигналу Y2.

Далее в момент времени 13 (см. фиг. 5) коммутатор 48 (см. фиг. 4) подключает к выходу напряжение U9; в момент времени 14 (см. фиг. 5) - напряжение U10; в момент времени t5 - напряжение U11; в момент времени t6 - напряжение U3; в момент времени t7 - напряжение U10; в момент времени t8 - напряжение U3; в момент времени t9 - напряжение U8; в момент времени t10 - напряжение U3; в момент времени t11 - напряжение U9; в момент времени t12 - напряжение U4; в момент времени t13 - напряжение U10.

В момент времени t14 (см. фиг. 5) завершается формирование положительной полуволны выходного напряжения и на входах компаратора 55 (см. фиг. 2) оказываются равные коды. На выходе РАВНО компаратора 55 появляется сигнал Х55, который через элемент ИЛИ 54 поступает сбросовый вход счетчика 52, запуская очередной цикл генерации кода текущего времени. Одновременно сигнал Х55 с выхода компаратора 55 поступает на распределитель импульсов 93 (см. фиг. 4), а со второго выхода распределителя 93 через ключ 100 - на сбросовый вход триггера 92. Триггер 92 меняет состояние и закрывает ключи 88, 89, а открывает ключи 90, 91. При этом к шине е подключается зажим нагрузки 96, а к шине f - зажим 95 обеспечивая равенство Uв=-Uef. Начинается формирование отрицательной полуволны выходного напряжения. В момент времени t15 (см. фиг. 5) коммутатор 48 (см. фиг. 4) подключает к выходу напряжение U5. В момент времени t16 (см. фиг. 5) к выходным зажимам подключается напряжение U11. В последующем при формировании отрицательной полуволны, как описано выше, происходит подбор наиболее подходящих напряжений из системы напряжений U1…U12. По завершению формирования отрицательной полуволны вновь появляется сигнал Х55 на выходе компаратора 55 (см. фиг. 2), который через распределитель 93 и ключ 100 поступает на счетный вход триггера 92. Триггер меняет состояние и подготавливает схему к формированию очередной полуволны выходного напряжения.

В режиме управляемого выпрямителя НПЧН работает следующим образом. Режим вводится замыканием контактов выключателя 101, который подает сигнал единичного уровня с шины 102 на вход логического элемента НЕ 97. При этом исчезает сигнал Х97 на входе логического элемента НЕ 97 и закрываются ключи 99 и 100. Одновременно выключатель 101 подает сигнал X101 на управляющий вход ключа 98, который открывается. На выходе задающего регистра 50 устанавливают код Х50 заданного напряжения. Этот код Х50 через электронный ключ 98 поступает на вторые входы вычитателей 13…24 и далее происходит подбор наиболее подходящего напряжения из U1…U12, как описано выше.

При включении режима управляемого выпрямителя в момент времени t1 (см. фиг. 6) для формирования выходного напряжения Uв, имеющего заданный уровень uэ, появляется сигнал Y9, который поступает на управляющие входы электронных ключей 80 и 81 коммутатора 48 (см. фиг. 4). К шинам е и f подключается напряжение U9 и появляется напряжение Uef. Потенциал шины е (+) больше потенциала шины f (-). При замкнутом контакте 1 переключателя 103 присутствует сигнал на прямом выходе триггера 92, который поступая на входы управления ключей 88 и 98 открывает их. Напряжение Uef через открытые ключи 88 и 89 подается на зажимы нагрузки 95 и 96 при этом Uв=Uef.

В момент времени t2 (см. фиг. 6) появляется сигнал Y1, который поступает на управляющие входы электронных ключей 64 и 65 коммутатора 48 (см. фиг. 4). К шинам е и f подключается напряжение U1.

В момент времени t3 (см. фиг. 6) наиболее подходящим является напряжение U11, которое подключается к выходу коммутатором 48 (см. фиг. 4) по сигналу Y11 ключами 84 и 85.

В момент времени t4 (см. фиг. 6) появляется сигнал Y3, и электронные ключи 68 и 69 коммутатора 48 (см. фиг. 4) подключают к выходу напряжение U3.

Далее в момент времени t5 (см. фиг. 6) коммутатор 48 (см. фиг. 4) подключает к выходу напряжение U1; в момент времени t6 (см. фиг. 6) - напряжение U5; в момент времени t7 - напряжение U3; в момент времени t8 - напряжение U7; в момент времени t9 - напряжение U5; в момент времени t10 - напряжение U3; в момент времени t9 - напряжение U8; в момент времени t10 - напряжение U9 и т.д.

В результате на зажимах 95 и 96 формируется знакопостоянное напряжение: на зажиме 95 (+), а на зажиме 96 (-). Для изменения полярности выходного напряжения переключатель 103 переводят в положение 2. При этом триггер 92 меняет состояние и на прямом выходе сигнал исчезает, а на инверсном выходе появляется. Электронные ключи 88 и 89 закрываются, а ключи 90 и 91 открываются, поэтому Uв=-Uef и на зажиме 95 оказывается (-), а на зажиме 96 (+).

Таким образом, НПЧН имеет расширенные функциональные возможности и обеспечивает на выходе формирование переменного напряжения с заданной частотой и амплитудой и постоянного напряжения заданного уровня и полярности.

Источники информации

1. Электроника: учеб. пособие / В.И. Лачин, Н.С. Савелов. - Изд. 7-е. - Ростов н/Д: Феникс, 2009, С. 667-669

2. Описание изобретения к авторскому свидетельству №736296, Н02М 5/27, 1980.

3. Описание изобретения к патенту №2691968 РФ, МПК Н02М 5/27, 2019.

| название | год | авторы | номер документа |

|---|---|---|---|

| НЕПОСРЕДСТВЕННЫЙ ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ БЕСТРАНСФОРМАТОРНЫЙ | 2022 |

|

RU2787121C1 |

| БЕСТРАНСФОРМАТОРНЫЙ НЕПОСРЕДСТВЕННЫЙ ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ | 2018 |

|

RU2691968C1 |

| ТРЕХФАЗНЫЙ БЕСТРАНСФОРМАТОРНЫЙ НЕПОСРЕДСТВЕННЫЙ ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ | 2020 |

|

RU2758443C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ХАРАКТЕРИСТИК СЛУЧАЙНЫХ ПРОЦЕССОВ | 2004 |

|

RU2280278C1 |

| Электронный коммутатор системы зажигания | 1990 |

|

SU1774060A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ХАРАКТЕРИСТИК СЛУЧАЙНЫХ ПРОЦЕССОВ | 2006 |

|

RU2336562C2 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ РТСМ | 2008 |

|

RU2390930C2 |

| КОМПЛЕКС ДЛЯ МОДЕЛИРОВАНИЯ ХИМИКО-ТЕХНОЛОГИЧЕСКИХ ПРОЦЕССОВ | 2017 |

|

RU2657711C1 |

| Кодирующий преобразователь | 1989 |

|

SU1755376A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ СОВМЕСТНО ХРАНИМЫХ ГРАНИЦ ПРИ ИНТЕРВАЛЬНЫХ ВЫЧИСЛЕНИЯХ | 2012 |

|

RU2497179C1 |

Изобретение относится к преобразовательной технике и может быть использовано для питания частотно-управляемых электроприводов переменного тока и электроприводов постоянного тока. Технический результат - расширение функциональных возможностей за счет возможности формирования постоянного напряжения заданной величины и полярности. Преобразователь содержит с первого по двенадцатый аналого-цифровые преобразователи (АЦП) 1…12, с первого по двенадцатый вычитатели 13…24, с первого по одиннадцатый блоки выбора наименьшего напряжения (БВНН) 25…35, с первого по двенадцатый логические элементы И 36…47, коммутатор 48, блок памяти 49, задающий регистр амплитуды напряжения 50, задающий регистр частоты 51, суммирующий счетчик 52, генератор стабильных импульсов 53, логический элемент ИЛИ 54, числовой компаратор 55. Блоки выбора наименьшего напряжения 25…35 имеют одинаковую структуру, включающую числовой компаратор 56, первый 57 и второй 58 n-разрядные электронные ключи, первый 59 и второй 60 формирователи коротких импульсов, логический элемент ИЛИ 61, RS-триггер 62, регистр памяти 63. Коммутатор 48 подключается к шинам питающего напряжения А, В, С и 0. В его состав входят с первого по двадцать восьмой электронные ключи 64…91, RS-триггер 92, распределитель импульсов 93, шина ПУСК 94, первый 95 и второй 96 выходные зажимы преобразователя, логический элемент НЕ 97. Кроме того, в преобразователь входят третий 98 и четвертый 99 n-разрядные электронные ключи, двухразрядный электронный ключ 100, выключатель 101 режима, шина 102 сигнала единичного уровня, переключатель 103 полярности выходного напряжения. Устройство позволяет формировать переменное напряжение заданной частоты и постоянное напряжение заданной величины и полярности. 6 ил.

Непосредственный преобразователь частоты и напряжения, содержащий коммутатор, имеющий RS-триггер коммутатора, с первого по двадцать восьмой электронные ключи и распределитель импульсов, с первого по двенадцатый логические элементы И, логический элемент ИЛИ, задающие регистры частоты и амплитуды выходного напряжения, генератор стабильных импульсов, блок памяти, счетчик импульсов, числовой компаратор, с первого по одиннадцатый блоки выбора наименьшего напряжения (БВНН), с первого по двенадцатый вычитатели, с первого по двенадцатый аналого-цифровые преобразователи, входы которых подключены к соответствующим напряжениям питающей сети, причем каждый БВНН имеет числовой компаратор, первый вход которого является первым входом БВНН, и его соответствующие разряды подключены к соответствующим разрядам входа первого n-разрядного электронного ключа, разряды выхода которого связаны с соответствующими разрядами регистра памяти, выход которого является третьим выходом БВНН, а вход записи соединен с выходом логического элемента ИЛИ, первый вход которого связан с выходом первого формирователя коротких импульсов, управляющим входом второго n-разрядного электронного ключа и сбросовым входом RS-триггера, прямой выход которого является первым выходом БВНН, а инверсный - вторым выходом БВНН, кроме того, единичный вход RS-триггера связан со вторым входом логического элемента ИЛИ, управляющим входом первого n-разрядного электронного ключа и выходом второго формирователя коротких импульсов, вход которого соединен с выходами РАВНО и МЕНЬШЕ числового компаратора, выход БОЛЬШЕ которого подключен к входу первого формирователя коротких импульсов, а второй вход компаратора является вторым входом БВНН, и его разряды соединены с соответствующими разрядами входа второго n-разрядного электронного ключа, разряды выхода которого связаны с соответствующими разрядами входа регистра памяти, причем выход генератора импульсов подключен к счетному входу счетчика, сбросовый вход которого соединен с выходом логического элемента ИЛИ, первый вход которого связан с шиной ПУСК, второй - с первым входом распределителя импульсов и выходом РАВНО числового компаратора, первый вход которого соединен с выходом счетчика и входом третьего адреса блока памяти, а второй вход компаратора - с выходом задающего регистра частоты и входом второго адреса блока памяти, вход первого адреса которого подключен к выходу задающего регистра выходного напряжения, кроме того, разряды первого входа с первого по двенадцатый вычитателей подключены к выходам разрядов с первого по двенадцатый аналого-цифровых преобразователей соответственно, а разряды выхода первого вычитателя соединены с соответствующими разрядами первого входа первого БВНН, второй вход которого связан с разрядами выхода второго вычитателя, первый выход - с первым входом первого элемента И, второй выход - с первым входом второго элемента И, разряды третьего выхода - с соответствующими разрядами первого входа четвертого БВНН, первый выход которого связан со вторыми входами первого и второго элементов И, второй выход - со вторыми входами третьего и четвертого элементов И, разряды третьего выхода - с соответствующими разрядами первого входа пятого БВНН, разряды второго входа - с соответствующими разрядами третьего выхода второго БВНН, первый выход которого соединен с первым входом третьего элемента И, второй выход - с первым входом четвертого элемента И, разряды первого входа - с соответствующими разрядами выхода третьего вычитателя, разряды второго входа - с соответствующими разрядами выхода четвертого вычитателя, а разряды выхода пятого вычитателя подключены к соответствующим разрядам первого входа третьего БВНН, разряды второго входа которого связаны с соответствующими разрядами выхода шестого вычитателя, первый выход - с первым входом пятого элемента И, второй выход - с первым входом шестого элемента И, разряды третьего выхода - с соответствующими разрядами второго входа пятого БВНН, первый выход которого подключен к третьему входу первого элемента И, второй выход - к вторым входам пятого и шестого элементов И, разряды третьего выхода - к соответствующим разрядом первого входа одиннадцатого БВНН, первый выход которого соединен с третьими входами пятого и шестого элементов И и четвертыми входами первого, второго, третьего и четвертого элементов И, второй выход - с третьими входами одиннадцатого и двенадцатого элементов И и четвертыми входами седьмого, восьмого, девятого и десятого элементов И, разряды второго входа - с соответствующими разрядами выхода десятого БВНН, разряды второго входа которого связаны с соответствующими разрядами третьего выхода восьмого БВНН, первый выход - с третьими входами седьмого, восьмого, девятого и десятого элементов И, второй выход - со вторыми входами одиннадцатого и двенадцатого элементов И, разряды первого входа - с соответствующими разрядами третьего выхода девятого БВНН, первый выход которого подключен к вторым входам седьмого и восьмого элементов И, второй выход - к вторым входам девятого и десятого элементов И, разряды второго входа - к соответствующим разрядам третьего выхода седьмого БВНН, разряды первого входа - к соответствующим разрядам третьего выхода шестого БВНН, первый выход которого соединен с первым входом седьмого элемента И, второй выход - с первым входом восьмого элемента И, разряды первого входа - с соответствующими разрядами выхода седьмого вычитателя, разряды второго входа - с соответствующими разрядами выхода восьмого вычитателя, а разряды выхода девятого вычитателя подключены к соответствующим разрядам первого входа седьмого БВНН, с разрядами второго входа которого связаны соответствующие разряды выхода десятого вычитателя, первый выход - с первым входом девятого элемента И, второй выход - с первым входом десятого элемента И, а разряды выхода одиннадцатого вычитателя подключены к соответствующим разрядам первого входа восьмого БВНН, разряды второго входа которого связаны с соответствующими разрядами выхода двенадцатого вычитателя, первый выход - с первым входом одиннадцатого элемента И, второй выход - с первым входом двенадцатого элемента И, выход которого подключен к управляющему входу двадцать третьего и двадцать четвертого ключей, а выход одиннадцатого элемента И подключен к управляющему входу двадцать первого и двадцать второго ключей, выход десятого элемента И - к управляющему входу девятнадцатого и двадцатого ключей, выход девятого элемента И - к управляющему входу семнадцатого и восемнадцатого ключей, выход восьмого элемента И - к управляющему входу пятнадцатого и шестнадцатого ключей, выход седьмого элемента И - к управляющему входу тринадцатого и четырнадцатого ключей, выход шестого элемента И - к управляющему входу одиннадцатого и двенадцатого ключей, выход пятого элемента И - к управляющему входу девятого и десятого ключей, выход четвертого элемента И - к управляющему входу седьмого и восьмого ключей, выход третьего элемента И - к управляющему входу пятого и шестого ключей, выход второго элемента И - к управляющему входу третьего и четвертого ключей, выход первого элемента И - к управляющему входу первого и второго ключей, кроме того, выходы ключей с нечетными номерами с первого по двадцать третий подключены к входу двадцать пятого и двадцать восьмого ключей, а выходы ключей с четными номерами со второго по двадцать четвертый подключены к входу двадцать шестого и двадцать седьмого ключей, выход которого связан с выходом двадцать пятого ключа и первым зажимом нагрузки, а управляющий вход соединен с инверсным выходом RS-триггера и управляющим входом двадцать восьмого ключа, выход которого связан с выходом двадцать шестого ключа и вторым зажимом нагрузки, а управляющий вход - с прямым выходом RS-триггера и управляющим входом двадцать пятого ключа, причем к первой фазе питающей сети подключены входы первого, третьего, двенадцатого, четырнадцатого, шестнадцатого и двадцать третьего ключей, к второй фазе - входы седьмого, девятого, одиннадцатого, двадцатого, двадцать второго и двадцать четвертого ключей, к третий фазе - входы четвертого, шестого, восьмого, пятнадцатого, семнадцатого и девятнадцатого ключей, а к нейтрали питающей сети - входы второго, пятого, десятого, тринадцатого, восемнадцатого и двадцать первого ключей, отличающийся тем, что с целью расширения функциональных возможностей снабжен логическим элементом НЕ, третьим и четвертым n-разрядными электронными ключами, двухразрядным электронным ключом, переключателем полярности выходного напряжения, выключателем режима, один зажим которого подключен к шине сигнала единичного уровня, а второй зажим - к управляющим входам двухразрядного электронного ключа и третьего n-разрядного электронного ключа и входу логического элемента НЕ, выход которого связан с входом переключателя полярности выходного напряжения и управляющим входом четвертого n-разрядного электронного ключа, разряды входа которого соединены с соответствующими разрядами выхода блока памяти, а разряды выхода - с соответствующими разрядами выхода третьего n-разрядного электронного ключа и вторыми входами с первого по двенадцатый вычитателей, кроме того, первый и второй выходы распределителя соединены с соответствующими входами двухразрядного электронного ключа, первый выход которого связан с единичным входом RS-триггера и первым выходом переключателя полярности выходного напряжения, второй выход которого соединен со сбросовым входом RS-триггера и вторым выходом двухразрядного электронного ключа, а разряды входа третьего n-разрядного электронного ключа подключены к соответствующим разрядам выхода задающего регистра выходного напряжения.

| БЕСТРАНСФОРМАТОРНЫЙ НЕПОСРЕДСТВЕННЫЙ ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ | 2018 |

|

RU2691968C1 |

| Трехфазно- -фазный непосредственный преобразователь частоты | 1977 |

|

SU736296A1 |

| ТРЁХФАЗНО-ТРЁХФАЗНЫЙ ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ | 2015 |

|

RU2582654C1 |

| WO 2015086416 A1, 18.06.2015 | |||

| WO 2006000111 A1, 05.01.2006. | |||

Авторы

Даты

2022-11-30—Публикация

2021-11-26—Подача