Изобретение относится к полупроводниковой микроэлектронике и наноэлектронике и может быть использовано при создании логических интегральных схем с элементами нанометровых размеров.

Известна комплементарная биполярная схема ИЛИ-НЕ, содержащая подложку первого типа проводимости, в которой расположена общая коллекторная область второго типа проводимости переключательных n-p-n транзисторов, совмещенная с базой нагрузочного многоколлекторного p-n-p транзистора, в которой расположены базовые области первого типа проводимости переключательных n-p-n транзисторов, совмещенные с коллекторами нагрузочного многоколлекторного p-n-p транзистора, разделенные глубокой изолирующей областью двуокиси кремния, содержащие высоколегированные эмиттерные области второго типа проводимости переключательных n-p-n транзисторов (Патент РФ №2094911, МПК H01L 27/04, опубл. 25.05.2002).

Недостатками известного устройства являются:

- низкое быстродействие, из-за реализации схемы с помощью эпитаксиально-планарной технологии, предполагающей при технологической реализации наличие внутренних коллекторных и эмиттерных переходов для реализации транзисторных эффектов;

- низкая информационная плотность, из-за формирования транзисторных эффектов в поверхностном слое полупроводникового кристалла;

- повышенная мощность потребления вследствие использования переходов диффузионного типа, имеющих большую площадь поверхности, чем поверхностные переходы, что приводит к потреблению дополнительной мощности;

Техническая задача, на решение которой направлено заявляемое изобретение, состоит в создании интегрального логического элемента ИЛИ-НЕ на основе однослойной трехмерной наноструктуры, обладающего повышенным быстродействием, информационной плотностью и сниженной потребляемой мощностью.

Поставленная техническая задача решается тем, что в интегральном логическом элементе ИЛИ-НЕ на основе однослойной трехмерной наноструктуры, содержащем первый и второй логические транзисторы и подложку, согласно предложенному изобретению логическая структура элемента ИЛИ-НЕ выполнена наноразмерной, область I типа проводимости, которая является анодом нагрузочного диода, сформирована в виде нанослоя высотой не менее 3 нм на изолирующей подложке высотой не менее 3 нм, область II типа проводимости, которая является катодом нагрузочного диода и коллектором первого логического транзистора, и коллектором второго логического транзистора, сформирована в виде нанослоя высотой не менее 3 нм на изолирующей подложке и имеет непосредственный контакт с областью I типа проводимости, область I типа проводимости, которая является базой первого логического транзистора, сформирована в виде нанослоя высотой не менее 3 нм на изолирующей подложке и имеет непосредственный контакт с областью II типа проводимости, которая является общим эмиттером первого и второго логических транзисторов, область I типа проводимости, которая является базой второго логического транзистора, сформирована в виде нанослоя высотой не менее 3 нм на изолирующей подложке и имеет непосредственный контакт с областью II типа проводимости, которая является эмиттером первого логического транзистора и эмиттером второго логического транзистора, область II типа проводимости, которая является эмиттером первого логического транзистора и эмиттером второго логического транзистора, сформирована в виде нанослоя высотой не менее 3 нм на изолирующей подложке.

Технический результат, достижение которого обеспечивается реализацией всей заявленной совокупности существенных признаков, состоит в том, что создан новый тонкослойный интегральный логический элемент ИЛИ-НЕ на основе однослойной трехмерной наноструктуры с вертикально ориентированными слоями, в котором рабочими переходами «база-эмиттер» и «база-коллектор» являются поверхностные переходы, которые обладают низкой мощностью потребления и наименьшими поверхностями переходов, что обеспечивает снижение потребляемой мощности и повышение быстродействия из-за снижения паразитных емкостей переходов.

Сущность заявляемого изобретения поясняется рисунками, где:

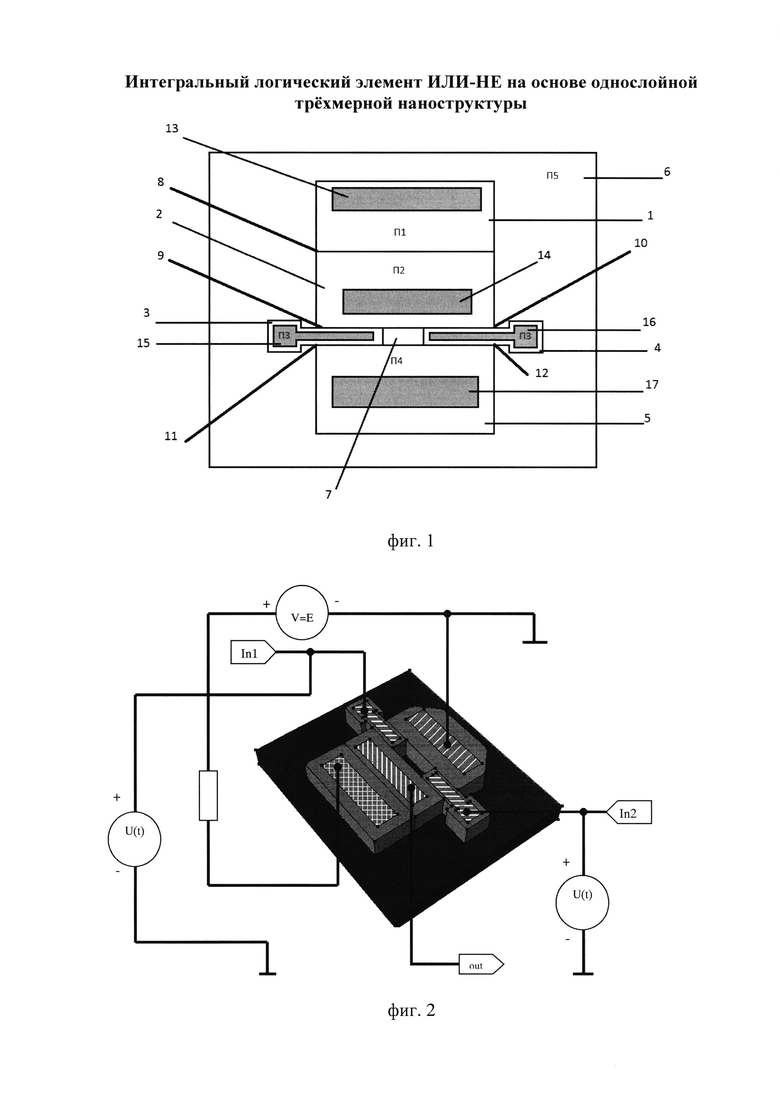

на фиг. 1 приведена принципиальная обобщенная схема заявляемого интегрального логического элемента ИЛИ-НЕ на основе однослойной трехмерной наноструктуры (вид сверху),

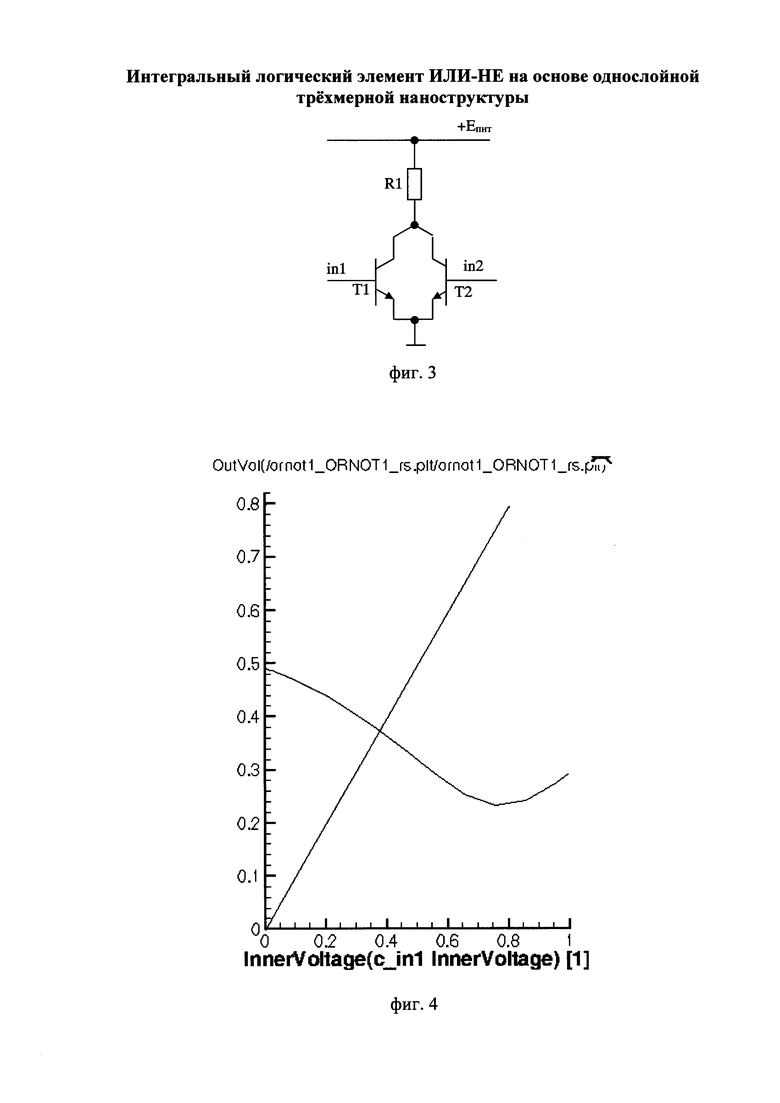

на фиг. 2 приведена схема, поясняющая работу устройства,

на фиг. 3 представлена эквивалентная транзисторная схема, поясняющая работу устройства,

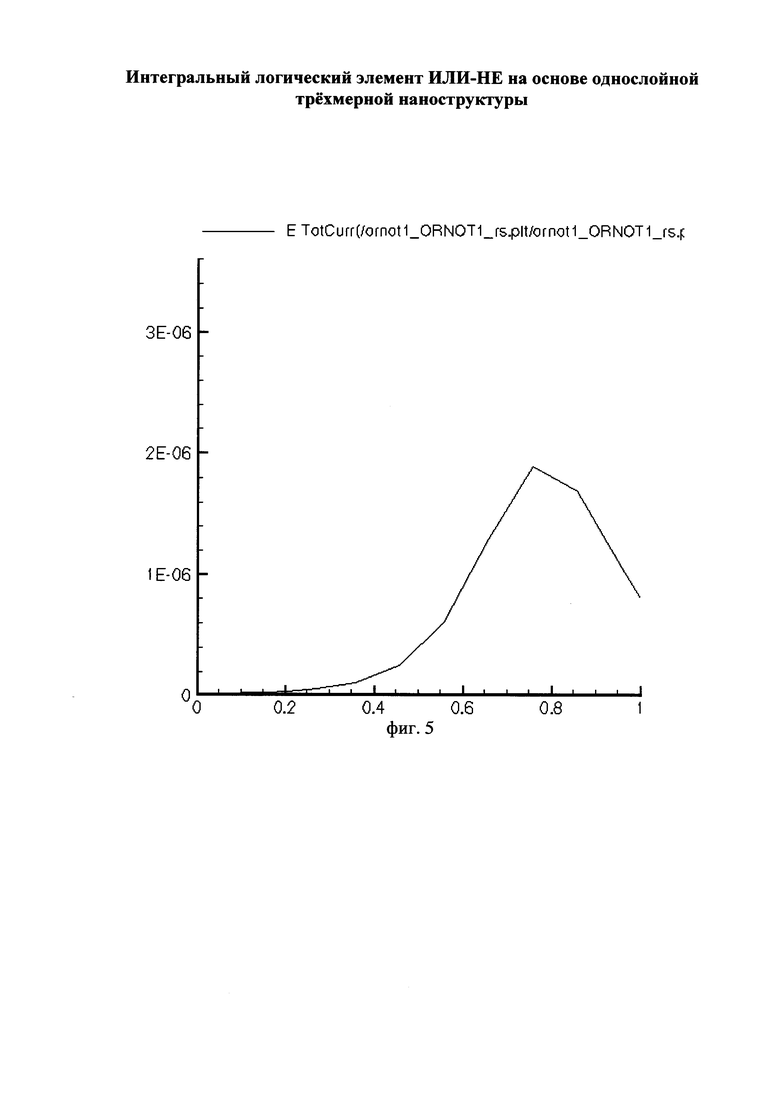

на фиг. 4 приведена передаточная характеристика интегрального логического элемента ИЛИ-НЕ на основе однослойной трехмерной наноструктуры (1), при изменении входного напряжения (2), которая демонстрирует выполнение наноструктурой, включенной по схеме (фиг. 5, 6, 7), реализации функции инверсии, что говорит о ее работоспособности.

на фиг. 5 предоставлен график общего тока через контакт питания Е,

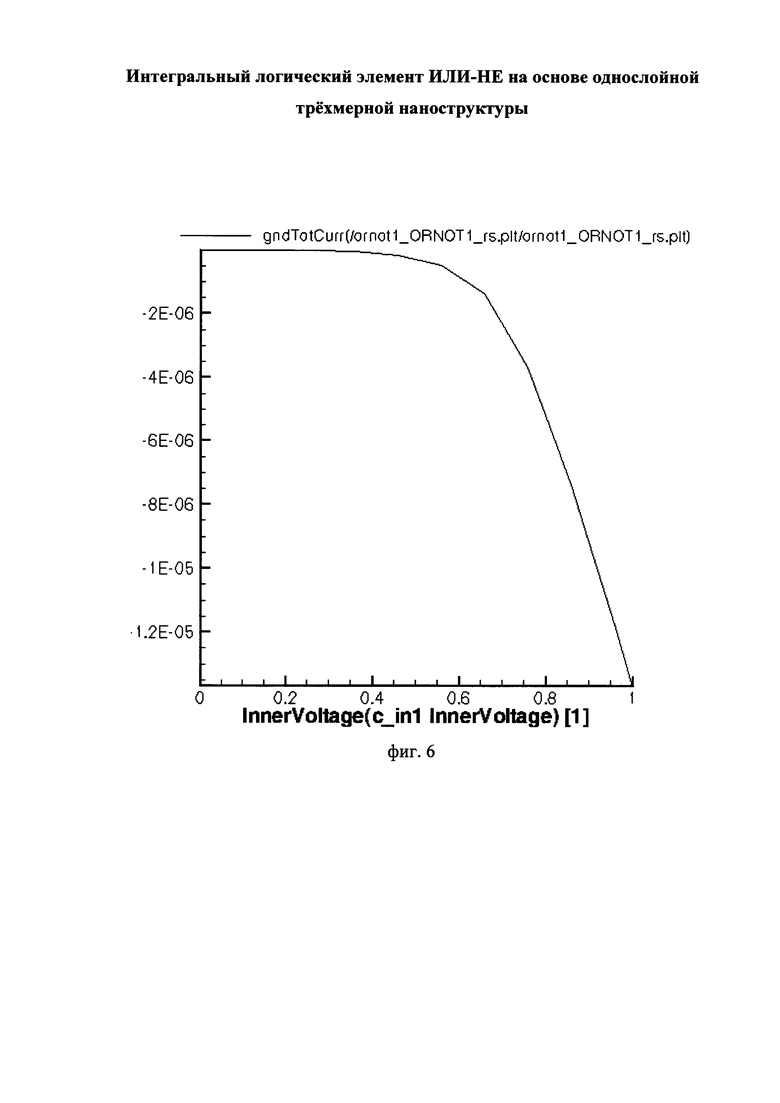

на фиг. 6 предоставлен график общего тока через контакт нулевого потенциала,

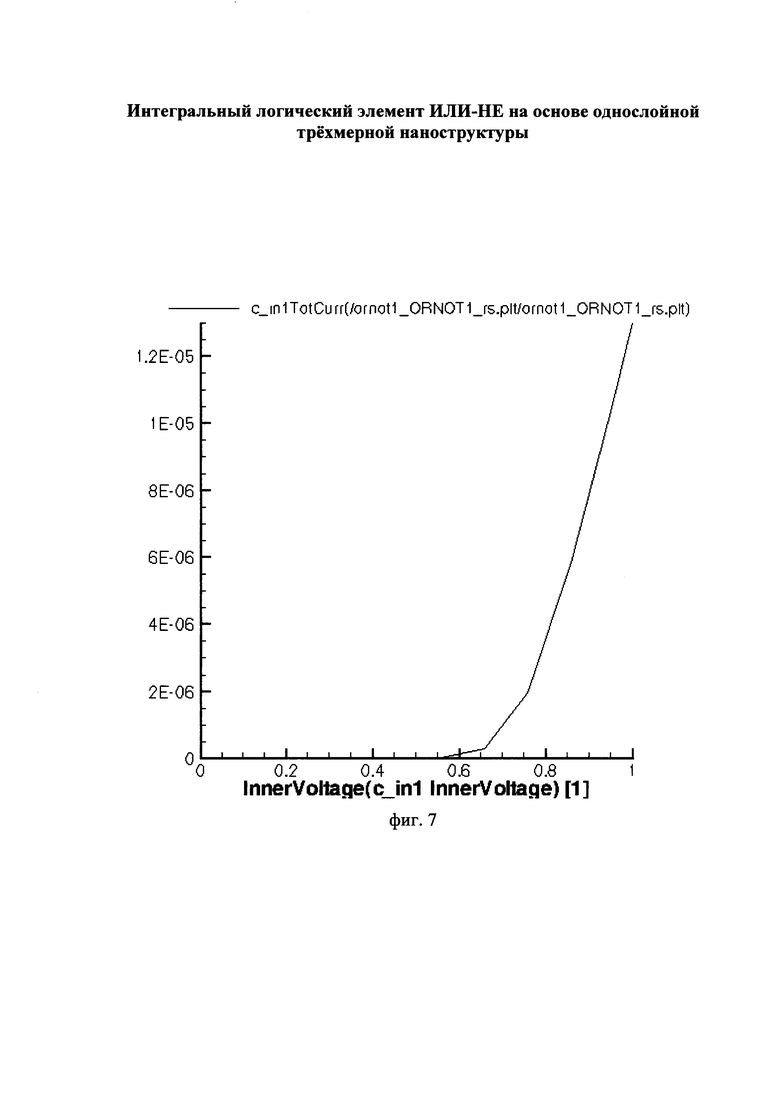

на фиг. 7 предоставлен график общего тока через контакт первого входа,

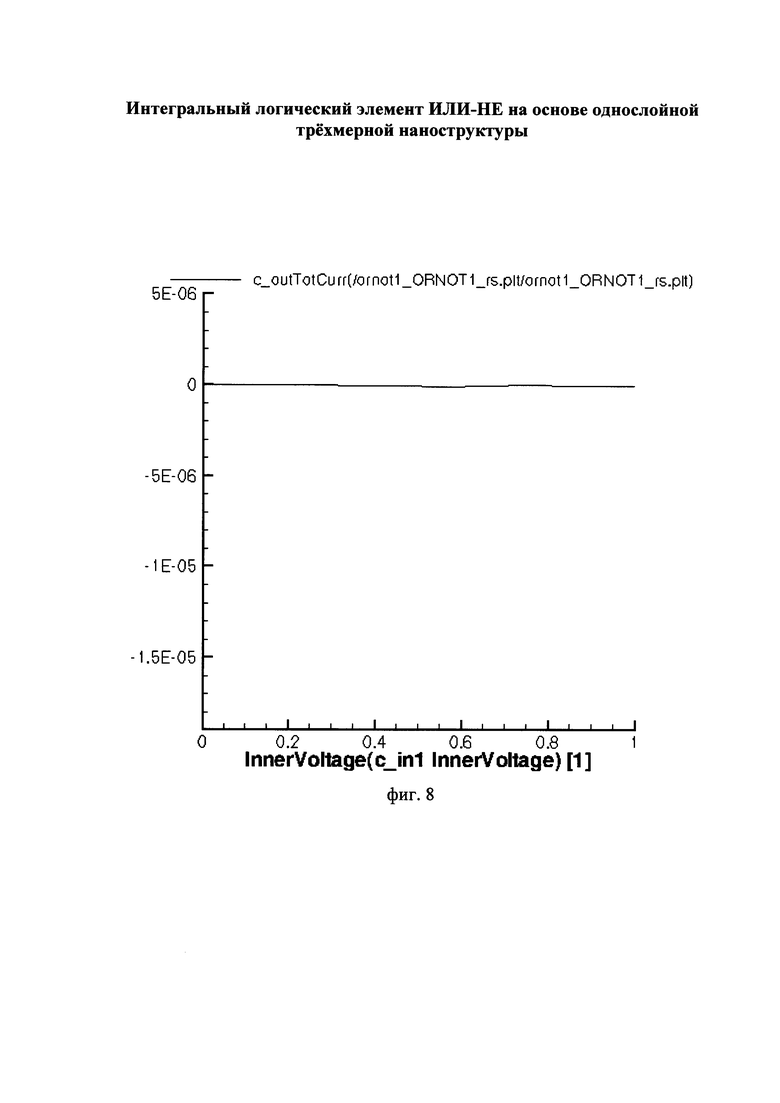

на фиг. 8 предоставлен график общего тока через выходной контакт,

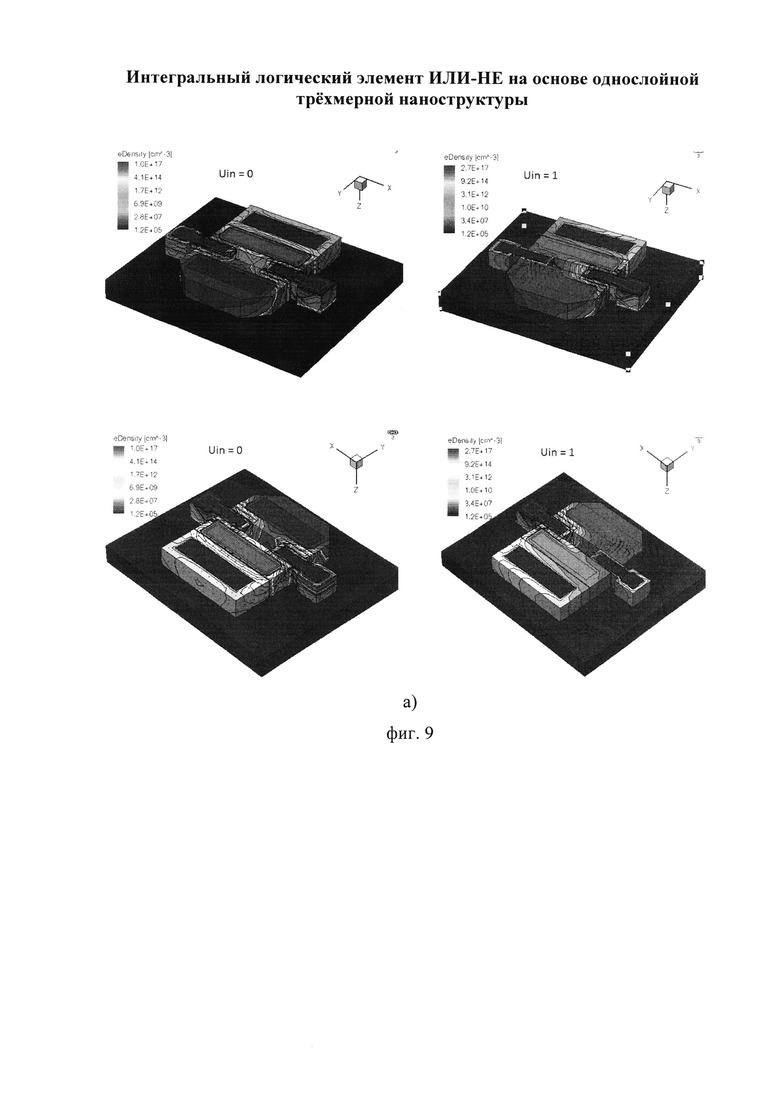

на фиг.9 приведены результаты работы интегрального логического элемента ИЛИ-НЕ на основе однослойной трехмерной наноструктуры, включенного по схеме (фиг. 2, 3) в двух режимах: когда на вход подается напряжение логического нуля (uin=u0) и когда на вход подается напряжение логической единицы (uin=u1) для следующего параметра:

а) распределение плотности электронов;

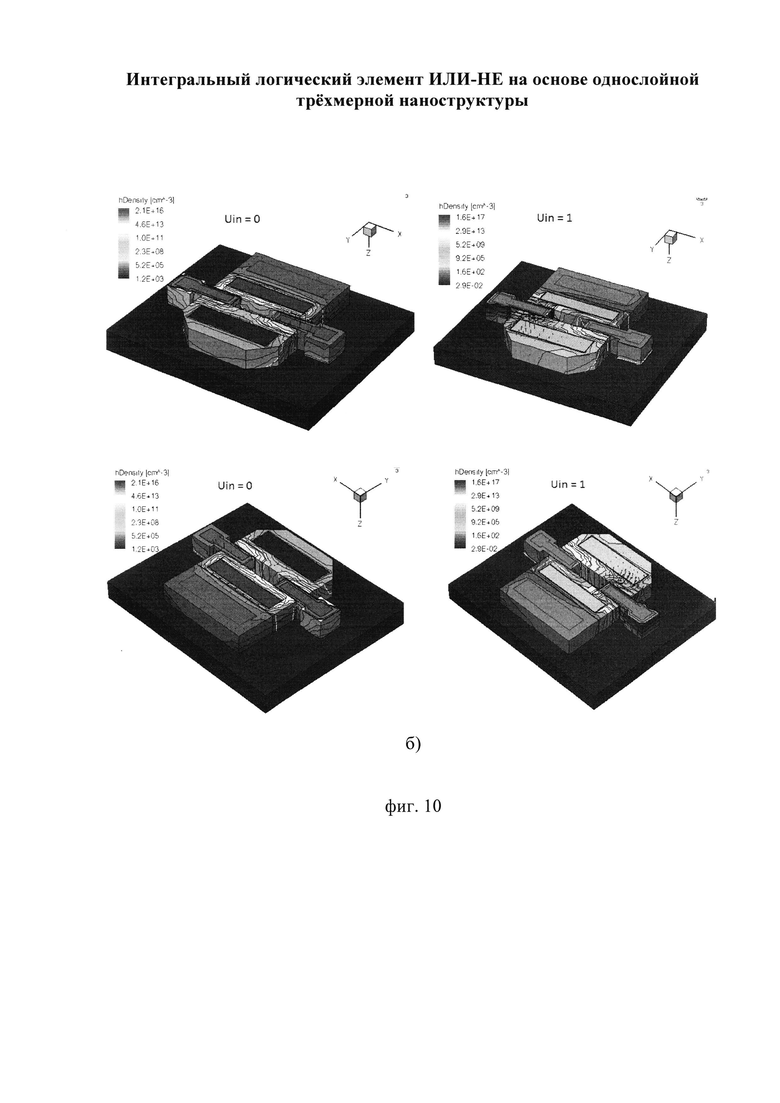

на фиг. 10 приведены результаты работы интегрального логического элемента ИЛИ-НЕ на основе однослойной трехмерной наноструктуры, включенного по схеме (фиг. 2, 3) в двух режимах: когда на вход подается напряжение логического нуля (uin=u0) и когда на вход подается напряжение логической единицы (uin=u1) для следующего параметра:

б) распределение плотности дырок;

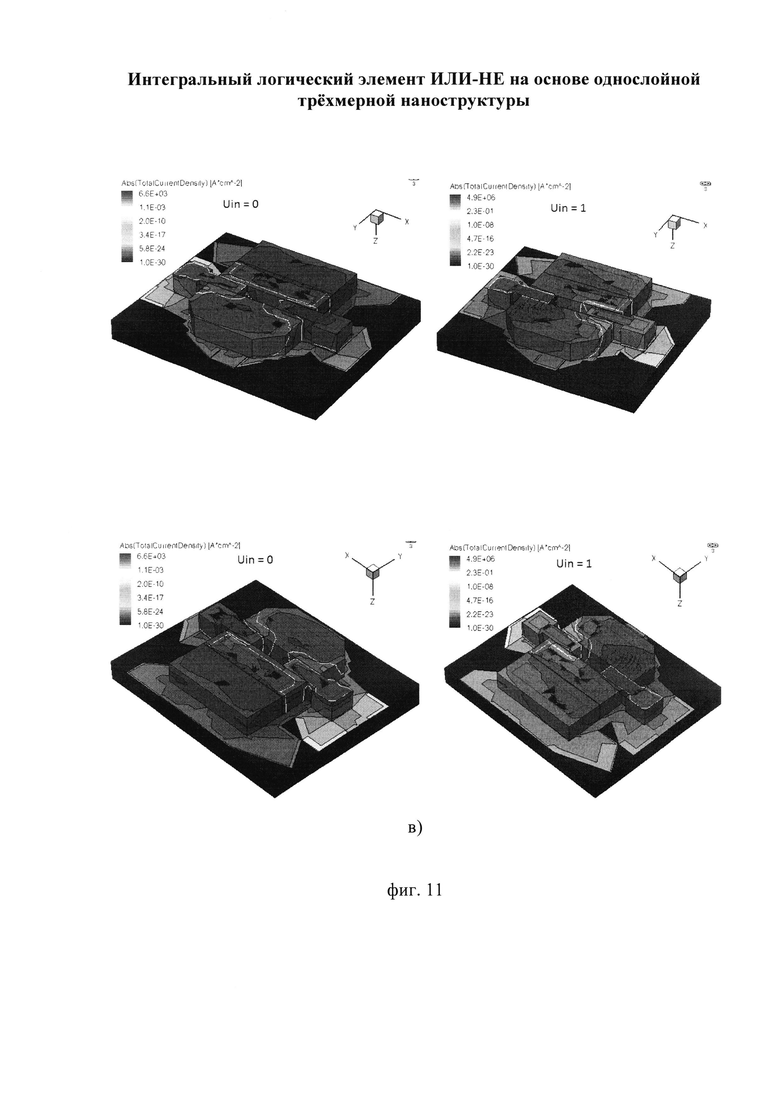

на фиг. 11 приведены результаты работы интегрального логического элемента ИЛИ-НЕ на основе однослойной трехмерной наноструктуры, включенного по схеме (фиг. 2, 3) в двух режимах: когда на вход подается напряжение логического нуля (uin=u0) и когда на вход подается напряжение логической единицы (uin=u1) для следующего параметра:

в) абсолютное значение общего тока в наноструктуре;

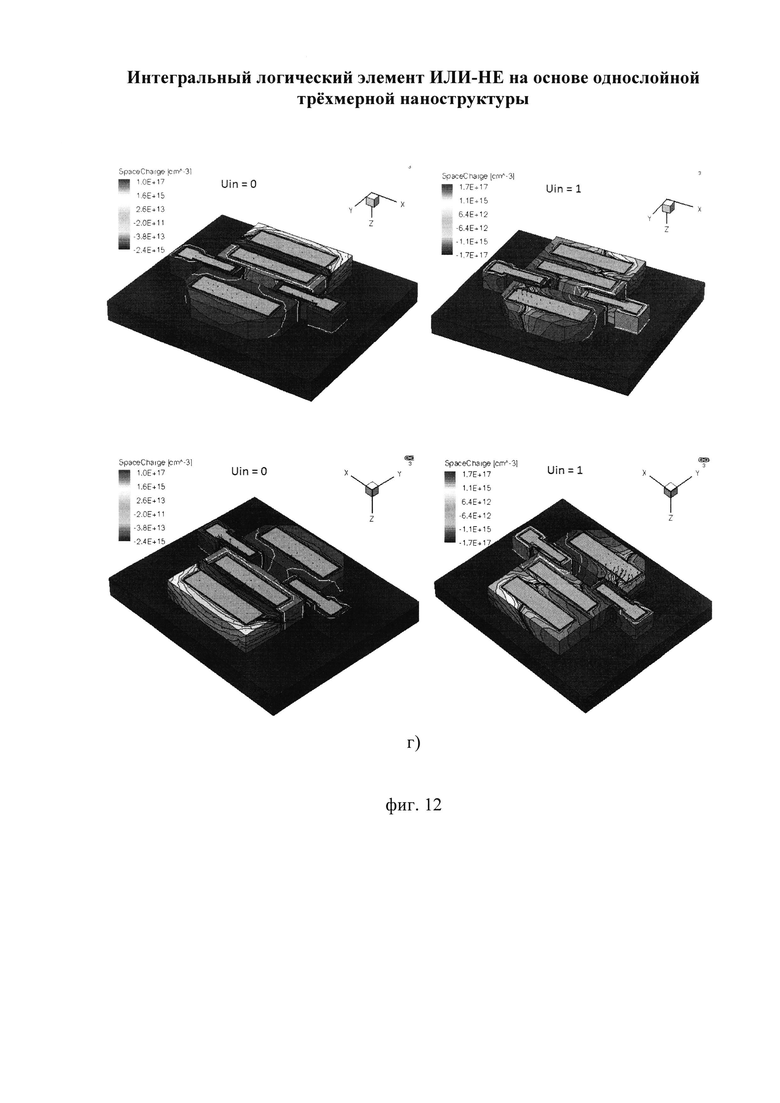

на фиг. 12 приведены результаты работы интегрального логического элемента ИЛИ-НЕ на основе однослойной трехмерной наноструктуры, включенного по схеме (фиг. 2, 3) в двух режимах: когда на вход подается напряжение логического нуля (uin=u0) и когда на вход подается напряжение логической единицы (uin=u1) для следующего параметра:

г) распределение пространственного заряда;

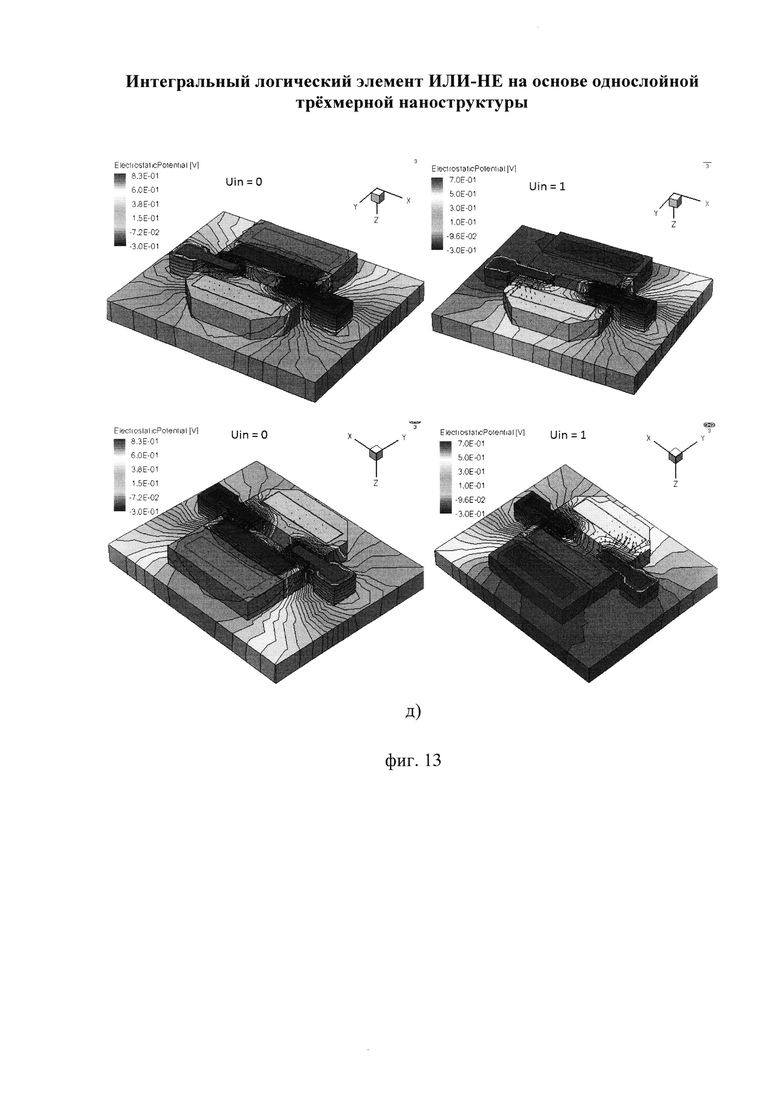

на фиг. 13 приведены результаты работы интегрального логического элемента ИЛИ-НЕ на основе однослойной трехмерной наноструктуры, включенного по схеме (фиг. 2, 3) в двух режимах: когда на вход подается напряжение логического нуля (uin=u0) и когда на вход подается напряжение логической единицы (uin=u1) для следующего параметра:

д) электростатический потенциал.

На фигуре 1, иллюстрирующей описание полезной модели, представлены следующие позиции:

1 - область первого типа проводимости, которая является катодом нагрузочного диода;

2 - область второго типа проводимости, которая является анодом нагрузочного диода, коллектором первого и второго транзистора;

3 - область первого типа проводимости, которая является базой первого транзистора;

4 - область первого типа проводимости, которая является базой второго транзистора;

5 - область второго типа проводимости, которая является эмиттером первого и второго транзистора;

6 - подложка первого типа проводимости;

7 - диэлектрическая изоляция между транзисторами;

8 - поверхностный переход между областью, которая является катодом нагрузочного диода, и областью, которая является анодом нагрузочного диода и коллектором первого и второго транзистора;

9 - поверхностный переход между областью, которая является анодом нагрузочного диода и коллектором первого и второго транзистора, и областью, которая является базой первого транзистора;

10 - поверхностный переход между областью, которая является анодом нагрузочного диода и коллектором первого и второго транзистора, и областью, которая является базой второго транзистора;

11 - поверхностный переход между областью, которая является базой первого транзистора, и областью, которая является эмиттером первого и второго транзистора;

12 - поверхностный переход между областью, которая является базой второго транзистора, и областью, которая является эмиттером первого и второго транзистора;

13 - контакт области, которая является катодом нагрузочного диода (питание);

14 - контакт области, которая является анодом нагрузочного диода и коллектором первого и второго транзистора (выход);

15 - контакт области, которая является базой первого транзистора (вход 1);

16 - контакт области, которая является базой второго транзистора (вход 2);

17 - контакт области, которая является эмиттером первого и второго транзистора (земля).

Интегральный логический элемент ИЛИ-НЕ на основе однослойной трехмерной наноструктуры (фиг. 1) содержит: подложка (6) первого типа проводимости (П5), область первого типа проводимости (П1), которая является катодом нагрузочного диода (1), область второго типа проводимости (П2), которая является анодом нагрузочного диода и коллектором первого и второго транзистора (2), между которыми расположен поверхностный переход (8), который образует нагрузочный диод, область первого типа проводимости (П3), которая является базой первого транзистора (3), между которыми расположен поверхностный переход (9), который образует переход между коллектором и базой первого транзистора, область первого типа проводимости (П3), которая является базой второго транзистора (4), между которыми расположен поверхностный переход (10), который образует переход между коллектором и базой второго транзистора, область второго типа проводимости (П4), которая является эмиттером первого и второго транзистора (5), между которыми расположены поверхностные переходы (11,12), которые образуют переход между базой и эмиттером первого транзистора (11) и между базой и эмиттером второго транзистора (12). На области первого типа проводимости (1) расположен контакт (13), на который подается питание схемы, на области второго типа проводимости (2) расположен контакт (14), с которого снимается выходной сигнал, на области первого типа проводимости (3) расположен контакт (15), на который подается входной сигнал 1, на области первого типа проводимости (4) расположен контакт (16), на который подается входной сигнал 2, на области второго типа проводимости (5) расположен контакт (17), на который подключается земля.

Интегральный логический элемент ИЛИ-НЕ на основе однослойной трехмерной наноструктуры выполнен наноразмерным со ступенчатым профилем.

Область I типа проводимости, которая является катодом нагрузочного диода, сформирована в виде нанослоя высотой не менее 3 нм на изолирующей подложке.

Область II типа проводимости, которая является анодом нагрузочного диода и коллектором первого и второго транзистора, сформирована в виде нанослоя высотой не менее 3 нм, имеют непосредственный контакт с областью I типа проводимости, которая является катодом нагрузочного диода, на изолирующей подложке.

Области I типа проводимости, которые являются базами первого и второго транзистора, сформированы в виде нанослоя высотой не менее 3 нм, имеют непосредственный контакт с областью II типа проводимости, которая является анодом нагрузочного диода и коллектором первого и второго транзистора, на изолирующей подложке, между областями баз транзисторов находится диэлектрическая изоляция.

Область II типа проводимости, которая является эмиттером первого и второго транзистора, сформирована в виде нанослоя высотой не менее 3 нм, имеет непосредственные контакты с областями I типа проводимости, которые являются базами первого и второго транзистора, на изолирующей подложке.

Контакты представляют собой контактные площадки.

Нанослои могут быть сформированы с использованием любой известной технологии формирования поверхностных полупроводниковых нанослоев, например молекулярного выращивания.

Предлагаемая схема может использоваться в качестве элемента, выполняющего функцию ИЛИ-НЕ.

Для n-p-n-транзистора для устранения влияния паразитного транзистора, образованного p-подложкой, p-подложку можно заменить на изолирующую, например, из технического сапфира.

Работа предлагаемой схемы поясняется на примере работы схемы ИЛИ-НЕ, включающей:

область (1), которая является катодом нагрузочного диода, сформирована в виде нанослоя p-типа (Si p-типа) высотой не менее 3 нм на подложке (6) p-типа (Si p-типа) высотой не менее 15 нм,

- область (2), которая является анодом нагрузочного диода и коллектором первого и второго транзистора, сформирована в виде нанослоя n-типа (Si n-типа) высотой не менее 3 нм на подложке (6) p-типа (Si p-типа) высотой не менее 15 нм,

- область (3), которая является базой первого транзистора, сформирована в виде нанослоя р-типа (Si p-типа) высотой не менее 3 нм на подложке (6) p-типа (Si p-типа) высотой не менее 15 нм,

- область (4), которая является базой второго транзистора, сформирована в виде нанослоя р-типа (Si р-типа) высотой не менее 3 нм на подложке (6) р-типа (Si р-типа) высотой не менее 15 нм,

- область (5), которая является эмиттером первого и второго транзистора, сформирована в виде нанослоя n-типа (Si n-типа) высотой не менее 3 нм на подложке (6) p-типа (Si p-типа) высотой не менее 15 нм.

Устройство работает следующим образом.

Для проверки работы наноструктуры ИЛИ-НЕ включаем ее так, как показано на фиг. 2.

На первый вход (контакт (15)) подается линейно меняющееся входное напряжение от 0 В до 1 В. На второй вход (контакт (16)) подается напряжение 0,01 В.

На выходе (контакт (14)) получается передаточная характеристика (фиг. 4) с двумя устойчивыми состояниями, которые соответствуют двум режимам работы схемы:

- режим 1 - когда на первом входе (контакт (15)) напряжение логического нуля и 0 (низкий уровень напряжения (0,1-0,2 В)), а на втором (контакт (16)) напряжение логического нуля u0(0,1-0,2 В),

- режим 2 - когда на первом входе (контакт (15)) напряжение логической единицы u1 (высокий уровень напряжения (0,9 В)) и на втором (контакт (16)) напряжение логического нуля u0 (0,1-0,2 В).

Рассмотрим работу интегрального логического элемента ИЛИ-НЕ на основе однослойной трехмерной наноструктуры для обоих режимов.

Режим 1. При подаче на первый вход и второй вход (контакт (15, 16)) напряжения логического нуля u0 поверхностные переходы «база-эмиттер» (11, 12) первого и второго транзистора наноструктуры закрыты. На выходе (контакт (14)) напряжение логической единицы.

Режим 2. При подаче на первый вход (контакт (15)) логической единицы u1, поверхностный переход (11) «база-эмиттер» открыт, ток из области инжектора (область (5)) поступает в базовую область (область (3)). В результате на выходной области (область (2)), являющейся коллектором первого и второго транзистора, низкий уровень напряжения.

Анализ работы наноструктуры ИЛИ-НЕ, сформированного нанослоями 1, 2, 3, 4, 5, 6 доказывает ее работоспособность и выполнение функции ИЛИ-НЕ.

Предлагаемый интегральный логический элемент ИЛИ-НЕ на основе однослойной трехмерной наноструктуры обеспечивает высокую информационную плотность (за счет использования наноразмеров, однослойной структуры (поверхностные p-n переходы) и трехмерной реализации элемента) и улучшенное быстродействие (за счет минимизации паразитных емкостей вследствие трехмерности элемента и использования поверхностных переходов) при низкой мощности потребления (за счет использования поверхностных переходов).

| название | год | авторы | номер документа |

|---|---|---|---|

| ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ И-НЕ НА ОСНОВЕ СЛОИСТОЙ ТРЕХМЕРНОЙ НАНОСТРУКТУРЫ | 2010 |

|

RU2452058C2 |

| ПОЛУПРОВОДНИКОВАЯ СТРУКТУРА ЛОГИЧЕСКОГО ЭЛЕМЕНТА И-НЕ | 2010 |

|

RU2444086C2 |

| Бистабильная ячейка памяти на базе однослойной наноструктуры | 2015 |

|

RU2611094C1 |

| ЯЧЕЙКА ПАМЯТИ НА БАЗЕ ТОНКОСЛОЙНОЙ НАНОСТРУКТУРЫ | 2010 |

|

RU2444806C2 |

| НАНОРАЗМЕРНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2020 |

|

RU2743510C1 |

| НИЗКОВОЛЬТНЫЙ БЫСТРОДЕЙСТВУЮЩИЙ БИПОЛЯРНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА КОМПЛЕМЕНТАРНЫХ СТРУКТУРАХ | 1999 |

|

RU2173915C2 |

| НАНОРАЗМЕРНЫЙ ЛОГИЧЕСКИЙ ИНВЕРТОР ДЛЯ ЦИФРОВЫХ УСТРОЙСТВ | 2020 |

|

RU2744161C1 |

| ВЫСОКОВОЛЬТНЫЙ САМОСОВМЕЩЕННЫЙ ИНТЕГРАЛЬНЫЙ ДИОД | 2012 |

|

RU2492552C1 |

| КОМПЛЕМЕНТАРНЫЙ ЭЛЕМЕНТ ИЛИ - НЕ И ЕГО ЭЛЕКТРИЧЕСКАЯ СХЕМА | 1994 |

|

RU2094911C1 |

| ИНТЕГРАЛЬНЫЙ ТОКОМАГНИТНЫЙ ДАТЧИК НА ОСНОВЕ БИПОЛЯРНОГО МАГНИТОТРАНЗИСТОРА | 2008 |

|

RU2387046C1 |

Изобретение относится к полупроводниковой микроэлектронике и наноэлектронике и может быть использовано при создании логических интегральных схем с элементами нанометровых размеров. В интегральном логическом элементе ИЛИ-НЕ на основе однослойной трехмерной наноструктуры, содержащем первый и второй логические транзисторы, нагрузочный резистор и подложку, логическая структура выполнена наноразмерной со ступенчатым профилем. Технический результат, достижение которого обеспечивается реализацией всей заявленной совокупности существенных признаков, состоит в том, что создан новый тонкослойный интегральный логический элемент ИЛИ-НЕ на основе слоистой трехмерной наноструктуры с вертикально ориентированными слоями, в котором рабочими переходами «база-эмиттер» и «база-коллектор» являются поверхностные переходы, которые обладают низкой мощностью потребления и наименьшими поверхностями переходов, что обеспечивает снижение потребляемой мощности и повышение быстродействия из-за снижения паразитных емкостей переходов. 13 ил.

Интегральный логический элемент ИЛИ-НЕ на основе однослойной трехмерной наноструктуры, содержащий первый и второй логические транзисторы и подложку, отличающийся тем, что логическая структура элемента ИЛИ-НЕ выполнена наноразмерной, область I типа проводимости, которая является анодом нагрузочного диода, сформирована в виде нанослоя высотой не менее 3 нм на изолирующей подложке высотой не менее 3 нм, область II типа проводимости, которая является катодом нагрузочного диода, коллектором первого логического транзистора и коллектором второго логического транзистора, сформирована в виде нанослоя высотой не менее 3 нм на изолирующей подложке и имеет непосредственный контакт с областью I типа проводимости, область I типа проводимости, которая является базой первого логического транзистора, сформирована в виде нанослоя высотой не менее 3 нм на изолирующей подложке и имеет непосредственный контакт с областью II типа проводимости, которая является общим эмиттером первого и второго логических транзисторов, область I типа проводимости, которая является базой второго логического транзистора, сформирована в виде нанослоя высотой не менее 3 нм на изолирующей подложке и имеет непосредственный контакт с областью II типа проводимости, которая является эмиттером первого логического транзистора и эмиттером второго логического транзистора, область II типа проводимости, которая является эмиттером первого логического транзистора и эмиттером второго логического транзистора, сформирована в виде нанослоя высотой не менее 3 нм на изолирующей подложке.

| КОМПЛЕМЕНТАРНЫЙ ЭЛЕМЕНТ ИЛИ - НЕ И ЕГО ЭЛЕКТРИЧЕСКАЯ СХЕМА | 1994 |

|

RU2094911C1 |

| ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ "ИЛИ-НЕ" НА КВАНТОВЫХ ЭФФЕКТАХ | 2004 |

|

RU2278445C1 |

| ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ И-НЕ НА ОСНОВЕ СЛОИСТОЙ ТРЕХМЕРНОЙ НАНОСТРУКТУРЫ | 2010 |

|

RU2452058C2 |

| US 5945848 A, 31.08.1999 | |||

| US 5463332 A, 31.10.1995. | |||

Авторы

Даты

2016-07-10—Публикация

2015-03-19—Подача