Полезная модель относится к полупроводниковой микроэлектронике и наноэлектронике и может быть использована при создании интегральных схем памяти с элементами нанометровых размеров.

Известна комплементарная Би-МОП ячейка памяти конденсаторного типа, содержащая биполярный транзистор, нагрузочный МОП-транзистор и конденсатор, сформированный областями вертикального МОП-транзистора (патент США №7199417, МПК H01L 29/76, опубл. 03.04.2007).

Недостатками известного устройства являются низкое быстродействие из-за большого времени рассасывания зарядов из емкости, хранящей информацию, а также пониженная радиационная стойкость из-за тонких окислов МОП-транзистора бистабильной ячейки.

Техническая задача, на решение которой направлена предлагаемая полезная модель, состоит в создании ячейки памяти на базе тонкослойной наноструктуры нанометрового размера, обладающей повышенными быстродействием и радиационной стойкостью.

Поставленная техническая задача решается тем, что в ячейке памяти на базе тонкослойной наноструктуры, содержащей подложку первого типа проводимости, согласно предложенной полезной модели подложка, на которую подается напряжение питания, выполнена наноразмерной высотой не менее 20 нм и является общим анодом нагрузочных диодов, на подложке расположены первая область второго типа проводимости, которая является коллектором первого переключающего транзистора и катодом первого нагрузочного диода, выполненная наноразмерной с высотой не менее 15 нм, к которой подключен контакт, соответствующий прямому выходу ячейки памяти, вторая область второго типа проводимости, которая является коллектором второго переключающего транзистора и катодом второго нагрузочного диода, выполненная наноразмерной с высотой не менее 15 нм, к которой подключен контакт, соответствующий инверсному выходу ячейки памяти, первая и вторая области отделены друг от друга областью с диэлектрическими свойствами шириной не менее 10 нм, на первой области второго типа проводимости расположена первая область первого типа проводимости, являющаяся базой первого переключающего транзистора, выполненная наноразмерной с высотой не менее 3 нм и имеющая потенциальный контакт со второй областью второго типа проводимости, на второй области второго типа проводимости расположена вторая область первого типа проводимости, являющаяся базой второго переключающего транзистора, выполненная наноразмерной с высотой не менее 3 нм и имеющая потенциальный контакт с первой областью второго типа проводимости, первая и вторая области второго типа проводимости разделены областью с диэлектрическими свойствами шириной не менее 10 нм, на первой области первого типа проводимости расположена третья область второго типа проводимости, которая выполнена наноразмерной с высотой не менее 10 нм и является первым эмиттером первого переключающего транзистора, к ней подключена шина записи единицы, на второй области первого типа проводимости расположена четвертая область второго типа проводимости, выполненная наноразмерой с высотой не менее 10 нм, и является первым эмиттером второго переключающего транзистора, к ней подключена шина сброса записи ноль, третья и четвертая области второго типа проводимости разделены областью с диэлектрическими свойствами шириной не менее 10 нм, на первой области первого типа проводимости расположена пятая область второго типа проводимости, которая является вторым эмиттером первого переключающего транзистора, выполненная наноразмерной с высотой не менее 10 нм, к которой подключена шина опорного напряжения, на второй области первого типа проводимости расположена шестая область второго типа проводимости, которая является вторым эмиттером второго переключающего транзистора, выполненная наноразмерной с высотой не менее 10 нм, к которой подключена шина опорного напряжения.

Кроме того, пятая и шестая области второго типа проводимости объединены в одну общую область второго типа проводимости, к которой подключена шина опорного напряжения.

Кроме того, в качестве диэлектрика для области с диэлектрическими свойствами используются окислы или газы.

Технический результат, достижение которого обеспечивается реализацией всей заявленной совокупности существенных признаков, состоит в том, что создана новая ячейка памяти на базе тонкослойной наноструктуры нанометровых размеров с вертикально ориентированными слоями, в котором рабочими переходами «база-эмиттер», «база-коллектор» и нагрузочный диод являются поверхностные переходы, которые обладают низкой мощностью потребления и наименьшими поверхностями переходов, что обеспечивает снижение потребляемой мощности и повышение быстродействия из-за снижения паразитных емкостей рабочих переходов.

Сущность заявляемой полезной модели поясняется рисунками, где

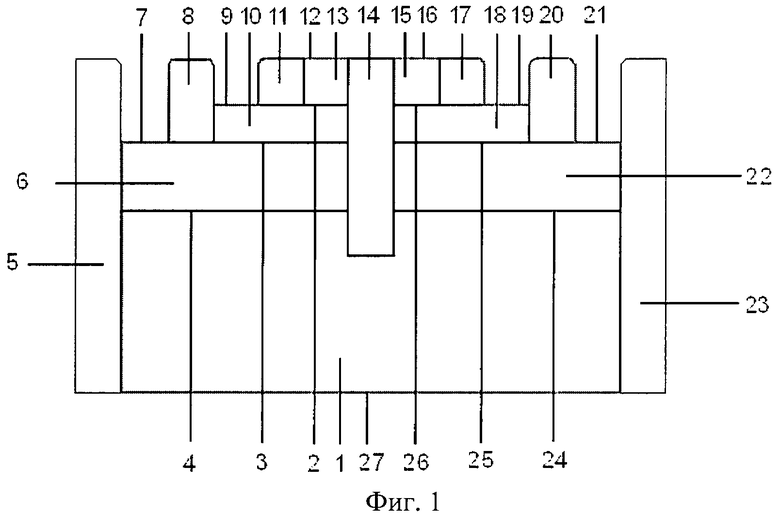

на фиг.1 приведена принципиальная обобщенная схема заявляемой бистабильной ячейки памяти;

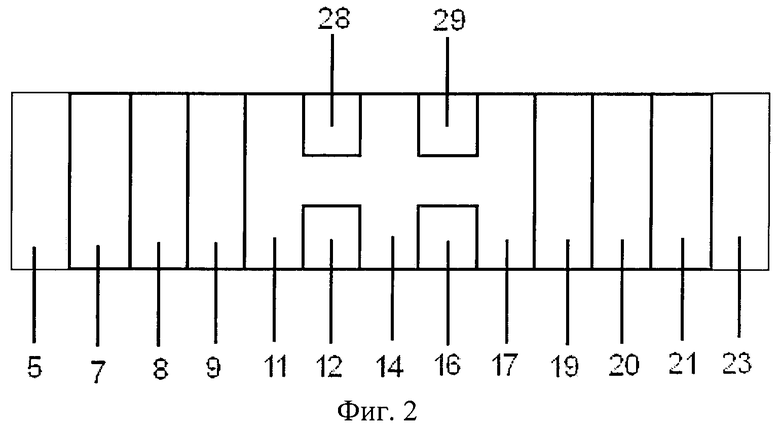

на фиг.2 приведен вид сверху схемы заявляемой ячейки памяти на базе тонкослойной наноструктуры фиг.1;

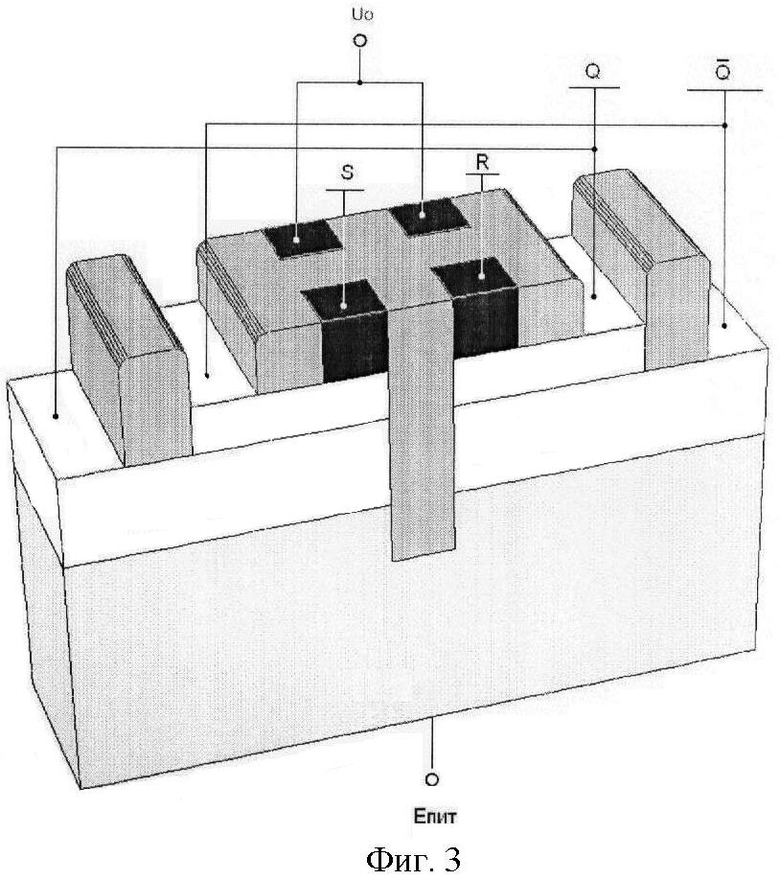

на фиг.3 приведена схема, поясняющая работу устройства;

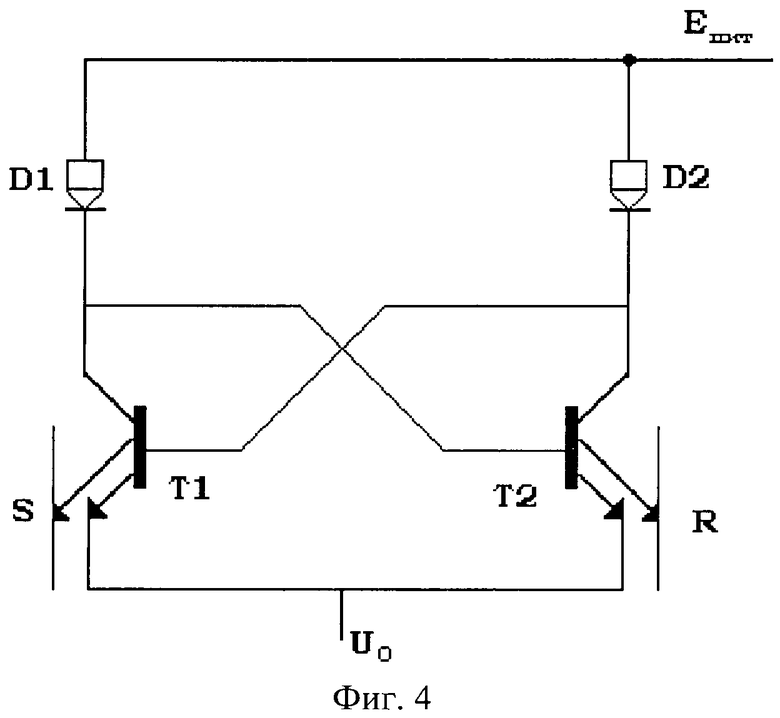

на фиг.4 приведена эквивалентная транзисторная схема;

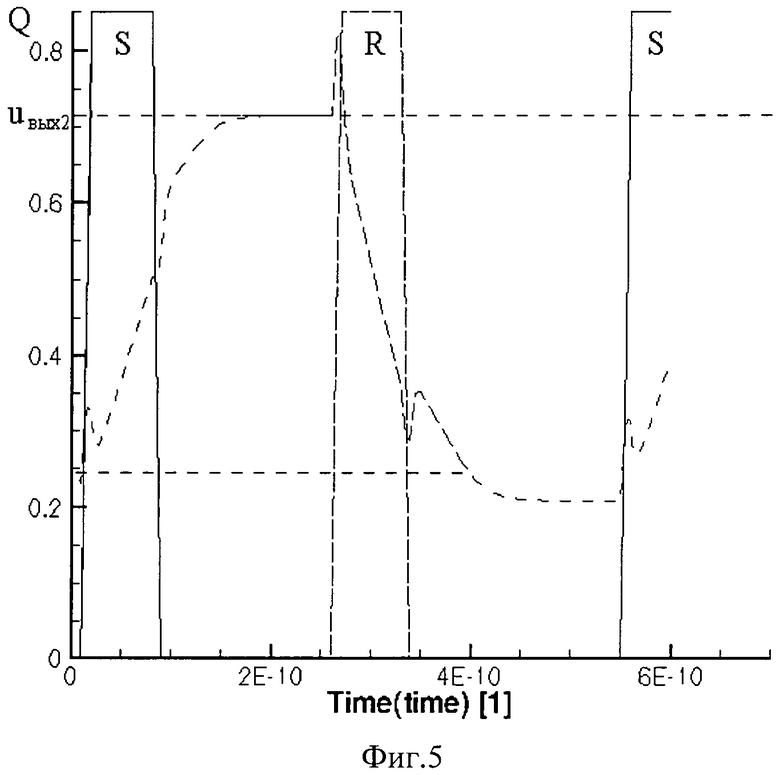

на фиг.5 приведена переходная характеристика наноструктуры бистабильной ячейки памяти, которая демонстрирует выполнение наноструктурой, включенной по схеме (фиг.2) реализации функции установки в единицу и сброса состояния, что говорит о ее работоспособности;

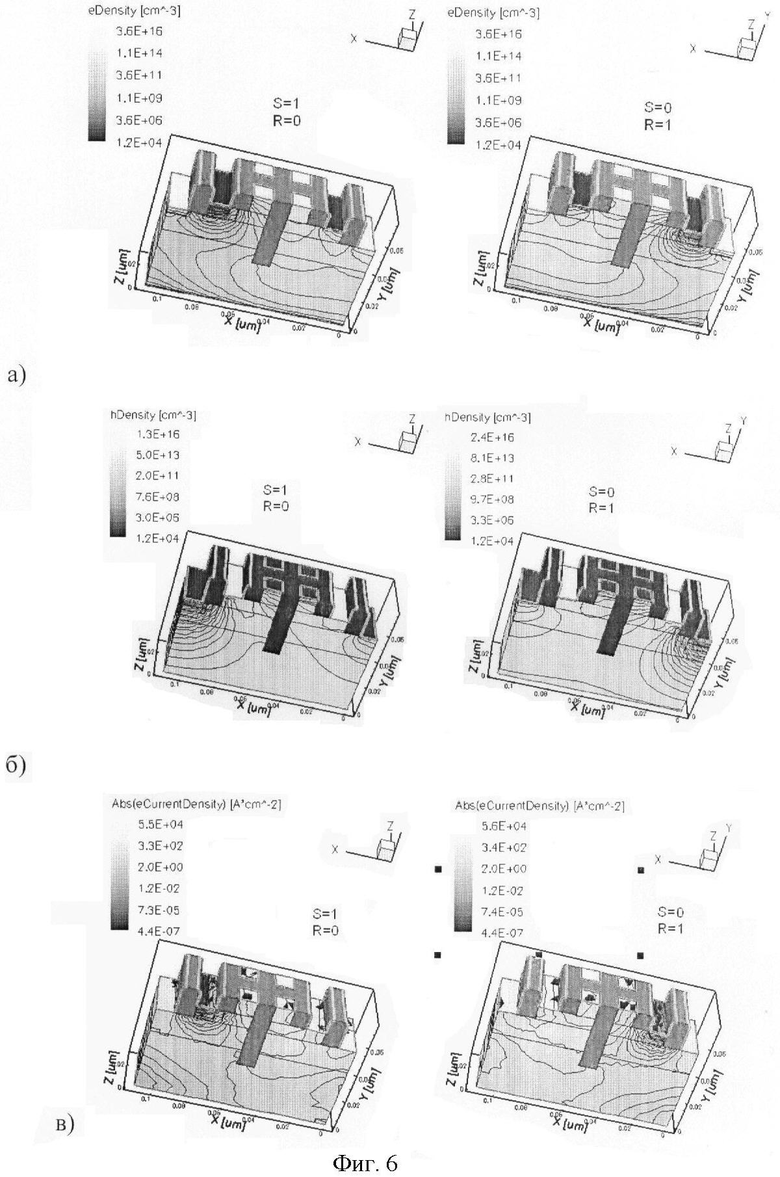

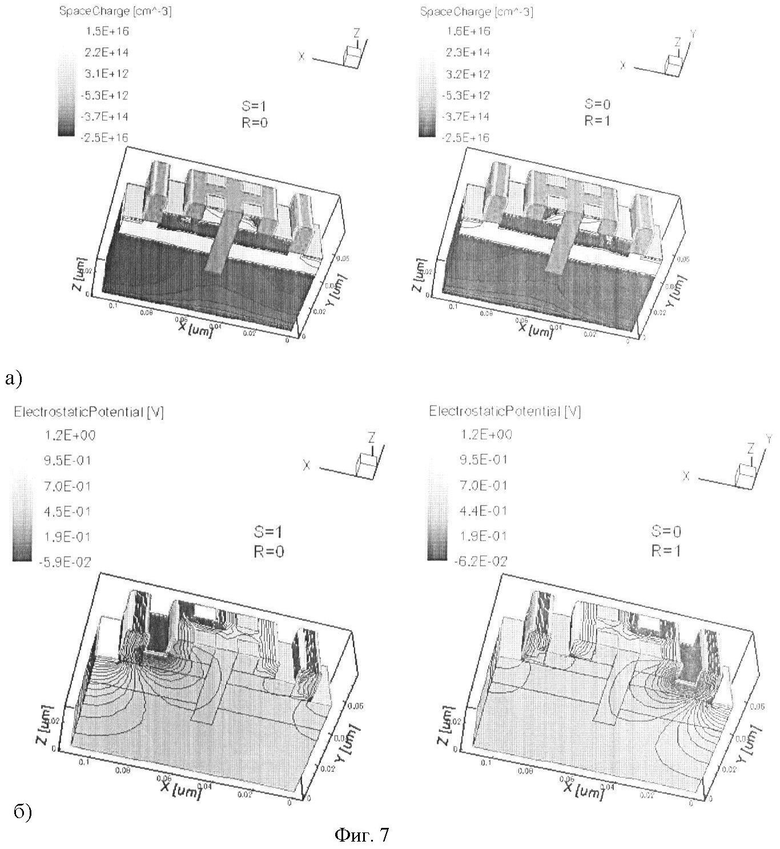

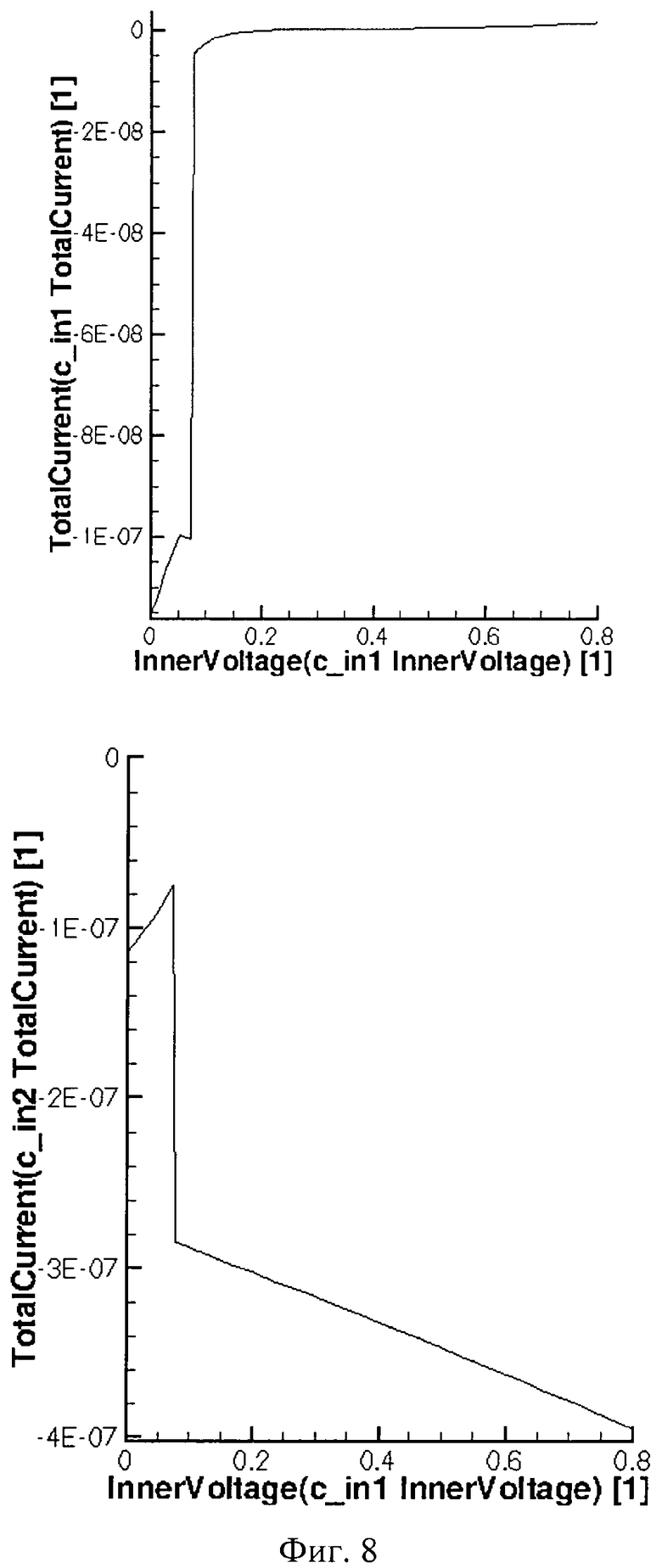

на фиг.6, фиг.7 и фиг.8 приведены результаты работы наноструктуры бистабильной ячейки памяти, включенной по схеме (фиг.3) в двух режимах: когда на вход S подается напряжение логической единицы и когда на вход R подается напряжение логического нуля для следующих параметров:

фиг.6 - а) распределение плотности электронов; б) распределение плотности дырок; в) абсолютное значение общего тока в наноструктуре бистабильной ячейки памяти;

фиг.7 - а) распределение пространственного заряда; б) распределение электростатического потенциала;

фиг.8 - а) график общего ток через контакт, подключенный к шине записи единицы (12); б) график общего ток через контакт, подключенный к шине сброса единицы (16); в) ток через контакт подложки (27).

На фиг.1 и 2, иллюстрирующих описание полезной модели, представлены следующие позиции:

1 - подложка первого типа проводимости,

2 - поверхностный переход «база-эмиттер»,

3 - поверхностный переход «база-коллектор»,

4 - поверхностный переход «подложка-коллектор»,

5 - диэлектрическая изоляция между ячейками памяти,

6 - первая область второго типа проводимости,

7 - контакт, соответствующий прямому выходу ячейки памяти,

8 - диэлектрическая изоляция между контактом, соответствующим прямому выходу ячейки памяти и областью первого типа проводимости,

9 - контакт для подключения ко второй области второго типа проводимости,

10 - первая область первого типа проводимости,

11 - диэлектрическая изоляция между контактом для подключения ко второй области второго типа проводимости и третьей областью второго типа проводимости,

12 - контакт, подключенный к шине записи единицы,

13 - третья область второго типа проводимости,

14 - диэлектрическая изоляция между двумя транзисторами,

15 - четвертая область второго типа проводимости,

16 - контакт, подключенный к шине записи нуля,

17 - диэлектрическая изоляция между контактом для подключения к первой области второго типа проводимости и четвертой областью второго типа проводимости,

18 - вторая область первого типа проводимости,

19 - контакт для подключения к первой области второго типа проводимости,

20 - диэлектрическая изоляция между контактом, соответствующим инверсному выходу ячейки памяти, и областью первого типа проводимости,

21 - контакт, соответствующий инверсному выходу ячейки памяти,

22 - вторая область второго типа проводимости,

23 - диэлектрическая изоляция между ячейками памяти,

24 - поверхностный переход «подложка-коллектор»,

25 - поверхностный переход «база-коллектор»,

26 - поверхностный переход «база-коллектор»,

27 - контакт, подключенный к питанию,

28 - контакт опорного напряжения,

29 - контакт опорного напряжения.

Ячейка памяти на базе тонкослойной наноструктуры (фиг.1 и фиг.2) содержит подложку (1) (первого или второго типа проводимости), контакт, подключенный к питанию (27), диэлектрическую изоляцию между ячейками памяти(5, 23), области коллекторов (второго типа проводимости) (6, 22), контакты коллекторов (7, 21), диэлектрическую изоляцию между контактами коллекторов и областями баз (8, 20), области баз (первого типа проводимости) (10, 18), контакты баз (9, 19), диэлектрическую изоляцию между контактами базы и областями эмиттеров (11, 17), контакты эмиттеров (12, 16, 28, 29), области эмиттеров (второго типа проводимости) (13, 15), поверхностные переходы «база-эмиттер» (2, 26), поверхностные переходы «база-коллектор» (3, 25), поверхностные переходы «подложка-коллектор» (4, 24). Ячейка памяти на базе тонкослойной наноструктуры выполнена наноразмерной.

Нанослои могут быть сформированы с использованием любой известной технологии формирования поверхностных полупроводниковых нанослоев, например молекулярным выращиванием.

В качестве диэлектрика для области с диэлектрическими свойствами используются окислы, в частности SiO2, или газы, в частности воздух (O2+N+CO2) или гексафторид серы SFe.

Устройство работает следующим образом.

Режим записи единицы: При подаче на контакт 12 высокого уровня напряжения (выше, чем u0), а на контакт 16 низкого уровня напряжения, транзистор Т1 закрывается, а транзистор Т2 открывается, основная часть тока течет через области (1, 15, 18, 22), на коллекторе Т2 низкий потенциал, что соответствует инверсному выходу, низкий потенциал поступает на базу Т1, закрывая транзистор Т1, при этом потенциал на его коллекторе растет до напряжения логической единицы, что соответствует записи логической единицы бистабильной ячейки.

Режим записи нуля: При подаче на контакт 16 высокого уровня напряжения (выше, чем u0), а на контакт 12 низкого уровня напряжения, транзистор Т2 закрывается, а транзистор Т1 открывается, основная часть тока течет через области (1, 6, 10, 13), на коллекторе Т1 низкий потенциал, что соответствует прямому выходу, низкий потенциал поступает на базу Т2, закрывая транзистор Т2, при этом потенциал на его коллекторе растет до напряжения логической единицы, что соответствует сбросу в логической ноль ячейки памяти на базе тонкослойной наноструктуры.

Режим хранения информации: В случае подачи на контакт записи единицы и контакт записи нуля напряжения логического нуля происходит неизменение режима работы схемы. Ячейка памяти сохраняет предыдущее состояние.

Комбинация высоких потенциалов на обеих шинах является запрещенной, как для обычного RS-триггера.

Анализ работы наноструктуры бистабильной ячейки памяти доказывает ее работоспособность и выполнение функции RS-триггера.

Предлагаемая ячейка памяти на базе тонкослойной наноструктуры обеспечивает высокое быстродействие (за счет использования поверхностных переходов биполярного транзистора нагрузочного диода, имеющих наименьшую паразитную емкость), повышение радиационной стойкости достигается за счет использования толстых слоев окислов (в сравнении с тонкими подзатворными окислами МОП-транзистора аналога).

| название | год | авторы | номер документа |

|---|---|---|---|

| Бистабильная ячейка памяти на базе однослойной наноструктуры | 2015 |

|

RU2611094C1 |

| ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ИЛИ-НЕ НА ОСНОВЕ ОДНОСЛОЙНОЙ ТРЁХМЕРНОЙ НАНОСТРУКТУРЫ | 2015 |

|

RU2589512C1 |

| ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ И-НЕ НА ОСНОВЕ СЛОИСТОЙ ТРЕХМЕРНОЙ НАНОСТРУКТУРЫ | 2010 |

|

RU2452058C2 |

| ПОЛУПРОВОДНИКОВАЯ СТРУКТУРА ЛОГИЧЕСКОГО ЭЛЕМЕНТА И-НЕ | 2010 |

|

RU2444086C2 |

| НАНОРАЗМЕРНЫЙ ЛОГИЧЕСКИЙ ИНВЕРТОР ДЛЯ ЦИФРОВЫХ УСТРОЙСТВ | 2020 |

|

RU2744161C1 |

| ЭЛЕМЕНТ ЭНЕРГОНЕЗАВИСИМОЙ ЭЛЕКТРИЧЕСКИ ПЕРЕПРОГРАММИРУЕМОЙ ПАМЯТИ | 2016 |

|

RU2637175C2 |

| НАНОРАЗМЕРНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2020 |

|

RU2743510C1 |

| ОДНОЭЛЕКТРОННЫЙ МЕМРИСТОР (НАНОЯЧЕЙКА) И СПОСОБ ПРИМЕНЕНИЯ | 2023 |

|

RU2823967C1 |

| СВЕРХБЫСТРОДЕЙСТВУЮЩЕЕ СВЕРХИНТЕГРИРОВАННОЕ БИМОП ОЗУ НА ЛАВИННЫХ ТРАНЗИСТОРАХ | 1999 |

|

RU2200351C2 |

| ЯЧЕЙКА ЭНЕРГОНЕЗАВИСИМОЙ ЭЛЕКТРИЧЕСКИ ПЕРЕПРОГРАММИРУЕМОЙ ПАМЯТИ | 2010 |

|

RU2436190C1 |

Изобретение относится к полупроводниковой микроэлектронике и наноэлектронике и может быть использовано при создании интегральных схем памяти с элементами нанометровых размеров. Сущность изобретения заключается в том, что подложка выполнена наноразмерной и является общим анодом нагрузочных диодов, на подложке расположены первая область второго типа проводимости, которая является коллектором первого переключающего транзистора и катодом первого нагрузочного диода, выполненная наноразмерной, вторая область второго типа проводимости, которая является коллектором второго переключающего транзистора и катодом второго нагрузочного диода, выполненная наноразмерной, первая и вторая области отделены друг от друга областью с диэлектрическими свойствами, на первой области второго типа проводимости расположена первая область первого типа проводимости, являющаяся базой первого переключающего транзистора, выполненная наноразмерной, на второй области второго типа проводимости расположена вторая область первого типа проводимости, являющаяся базой второго переключающего транзистора, выполненная наноразмерной, первая и вторая области второго типа проводимости разделены областью с диэлектрическими свойствами, на первой области первого типа проводимости расположена третья область второго типа проводимости, которая выполнена наноразмерной и является первым эмиттером первого переключающего транзистора, на второй области первого типа проводимости расположена четвертая область второго типа проводимости, выполненная наноразмерой, и является первым эмиттером второго переключающего транзистора, третья и четвертая области второго типа проводимости разделены областью с диэлектрическими свойствами, на первой области первого типа проводимости расположена пятая область второго типа проводимости, которая является вторым эмиттером первого переключающего транзистора, выполненная наноразмерной, на второй области первого типа проводимости расположена шестая область второго типа проводимости, которая является вторым эмиттером второго переключающего транзистора, выполненная наноразмерной, к которой подключена шина опорного напряжения. Технический результат - снижение потребляемой мощности и повышение быстродействия устройства. 2 з.п. ф-лы, 8 ил.

1. Ячейка памяти на базе тонкослойной наноструктуры, содержащая подложку первого типа проводимости, отличающаяся тем, что подложка выполнена наноразмерной высотой не менее 20 нм и является общим анодом нагрузочных диодов, на подложке расположены первая область второго типа проводимости, которая является коллектором первого переключающего транзистора и катодом первого нагрузочного диода, выполненная наноразмерной с высотой не менее 15 нм, к которой подключен контакт, соответствующий прямому выходу ячейки памяти, вторая область второго типа проводимости, которая является коллектором второго переключающего транзистора и катодом второго нагрузочного диода, выполненная наноразмерной с высотой не менее 15 нм, к которой подключен контакт, соответствующий инверсному выходу ячейки памяти, первая и вторая области отделены друг от друга областью с диэлектрическими свойствами шириной не менее 10 нм, на первой области второго типа проводимости расположена первая область первого типа проводимости, являющаяся базой первого переключающего транзистора, выполненная наноразмерной с высотой не менее 3 нм и имеющая потенциальный контакт со второй областью второго типа проводимости, на второй области второго типа проводимости расположена вторая область первого типа проводимости, являющаяся базой второго переключающего транзистора, выполненная наноразмерной с высотой не менее 3 нм и имеющая потенциальный контакт с первой областью второго типа проводимости, первая и вторая области второго типа проводимости разделены областью с диэлектрическими свойствами шириной не менее 10 нм, на первой области первого типа проводимости расположена третья область второго типа проводимости, которая выполнена наноразмерной с высотой не менее 10 нм и является первым эмиттером первого переключающего транзистора, к ней подключена шина записи единицы, на второй области первого типа проводимости расположена четвертая область второго типа проводимости, выполненная наноразмерой с высотой не менее 10 нм и является первым эмиттером второго переключающего транзистора, к ней подключена шина сброса записи ноль, третья и четвертая области второго типа проводимости разделены областью с диэлектрическими свойствами шириной не менее 10 нм, на первой области первого типа проводимости расположена пятая область второго типа проводимости, которая является вторым эмиттером первого переключающего транзистора, выполненная наноразмерной с высотой не менее 10 нм, к которой подключена шина опорного напряжения, на второй области первого типа проводимости расположена шестая область второго типа проводимости, которая является вторым эмиттером второго переключающего транзистора, выполненная наноразмерной с высотой не менее 10 нм, к которой подключена шина опорного напряжения.

2. Ячейка памяти на базе тонкослойной наноструктуры по п.1, отличающаяся тем, что пятая и шестая области второго типа проводимости объединены в одну общую область второго типа проводимости, к которой подключена шина опорного напряжения.

3. Ячейка памяти на базе тонкослойной наноструктуры по п.1, отличающаяся тем, что в качестве диэлектрика для области с диэлектрическими свойствами используются окислы или газы.

| US 7199417 В2, 03.04.2007 | |||

| ЯЧЕЙКА ПАМЯТИ ДИНАМИЧЕСКОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 2001 |

|

RU2216795C2 |

| ПОЛУПРОВОДНИКОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1998 |

|

RU2216819C2 |

| JP 9116106 А, 02.05.1997. | |||

Авторы

Даты

2012-03-10—Публикация

2010-05-19—Подача