Предпосылки изобретения

I. Притязание на приоритет

Эта заявка испрашивает приоритет предварительной патентной заявки США № 60/759797, поданной 17 января 2006 г.

II. Область техники

Настоящее раскрытие, в целом, относится к схемам и, в частности, к способу и устройству для отладки многоядерной системы.

III. Уровень техники

Многоядерная система - это система, имеющая множество ядер обработки. Эти ядра обработки могут представлять собой ядра обработки цифрового сигнала (Цифрового сигнального процессора - ЦСП), ядра процессора и/или некоторые другие типы блоков обработки. Ядра ЦСП - это особые процессоры, предназначенные для очень быстрого выполнения математических расчетов. Например, ядро ЦСП может включать в себя один или несколько блоков умножения и накопления (MAC), один или несколько арифметико-логических блоков (АЛУ) и т.д. Ядра процессора это процессоры общего назначения, которые можно программировать на выполнение различных функций.

Многоядерная система обычно проходит стадию конструирования и стадию отладки до изготовления. На стадии конструирования, каждое ядро обработки должно отвечать требованиям для этого ядра. На стадии отладки, ядра обработки в системе тестируются на предмет отыскания дефектов и ошибок конструкции, которые можно исправить до изготовления.

Отладка многоядерной системы представляет собой сложную задачу по разным причинам. Во-первых, каждое ядро обработки может быть сложной системой, которую необходимо отлаживать с использованием сложных инструментов отладки. Во-вторых, ядра обработки в системе обычно взаимодействуют друг с другом поэтому для отладки данного ядра обработки может потребоваться правильная настройка других ядер обработки.

Традиционно, множество отладчиков используется для отладки ядер обработки в многоядерной системе. Каждый отладчик может представлять собой комбинацию оборудования, программно-аппаратного обеспечения и/или программного обеспечения, которое управляет работой соответствующего ядра обработки с целью отладки этого ядра. Каждый отладчик может действовать независимо для отладки соответствующего ядра обработки. Однако в многоядерной системе часто желательно координировать отладку этих ядер обработки для учета их взаимодействий.

Таким образом, в технике существует необходимость в средствах отладки многоядерной системы.

Сущность изобретения

Здесь описаны средства отладки многоядерной системы с возможностями синхронной остановки и синхронного возобновления. Согласно варианту осуществления устройство (например, СИС) включает в себя первое и второе ядра обработки. В ходе отладки, первое или второе ядро обработки принимает программную команду остановки работы и, в ответ, генерирует первый аппаратный сигнал, указывающий остановку работы. Другое ядро обработки принимает первый аппаратный сигнал и останавливает работу. Оба ядра обработки останавливаются приблизительно в одно и то же время на основании первого аппаратного сигнала. Затем первое или второе ядро обработки принимает другую программную команду для возобновления работы и в ответ генерирует второй аппаратный сигнал, указывающий возобновление работы. Другое ядро обработки принимает второй аппаратный сигнал и возобновляет работу. Оба ядра обработки возобновляют работу приблизительно в одно и то же время на основании второго аппаратного сигнала. Первый и второй аппаратные сигналы могут поступать от одного ядра обработки и могут соответствовать двум фронтам (переднему и заднему фронтам) одного физического аппаратного сигнала. Альтернативно, первый и второй аппаратные сигналы могут поступать от разных ядер обработки, благодаря чему одно ядро обработки может синхронно останавливать оба ядра, и другое ядро обработки может синхронно возобновлять работу обоих ядер.

В другом варианте осуществления, устройство включает в себя, по меньшей мере, три ядра обработки и перекрестный коммутатор. Ядра обработки генерируют выходные аппаратные сигналы и принимают входные аппаратные сигналы. Выходной и входной аппаратные сигналы можно использовать для синхронной остановки, синхронного возобновления или синхронных остановки и возобновления ядер обработки в ходе отладки. Перекрестный коммутатор принимает выходные аппаратные сигналы от ядер обработки и выдает входные аппаратные сигналы для ядер обработки. Перекрестный коммутатор может обнаруживать выходной аппаратный сигнал, указывающий остановку работы ядром обработки в ходе отладки, и может выдавать этот выходной аппаратный сигнал в качестве входных аппаратных сигналов для всех ядер обработки. Перекрестный коммутатор также может обнаруживать выходной аппаратный сигнал, указывающий возобновление работы, и может выдавать этот выходной аппаратный сигнал в качестве входных аппаратных сигналов для всех ядер обработки. Одно и то же или разные ядра обработки могут генерировать выходной аппаратный сигнал для остановки и выходной аппаратный сигнал для возобновления.

Ниже приведено более подробное описание различных аспектов и вариантов осуществления изобретения.

Краткое описание чертежей

Признаки и характер настоящего изобретения явствуют из нижеследующего подробного описания, приведенного совместно с чертежами, на которых одинаковые ссылочные позиции обозначают соответствующие элементы на всех чертежах.

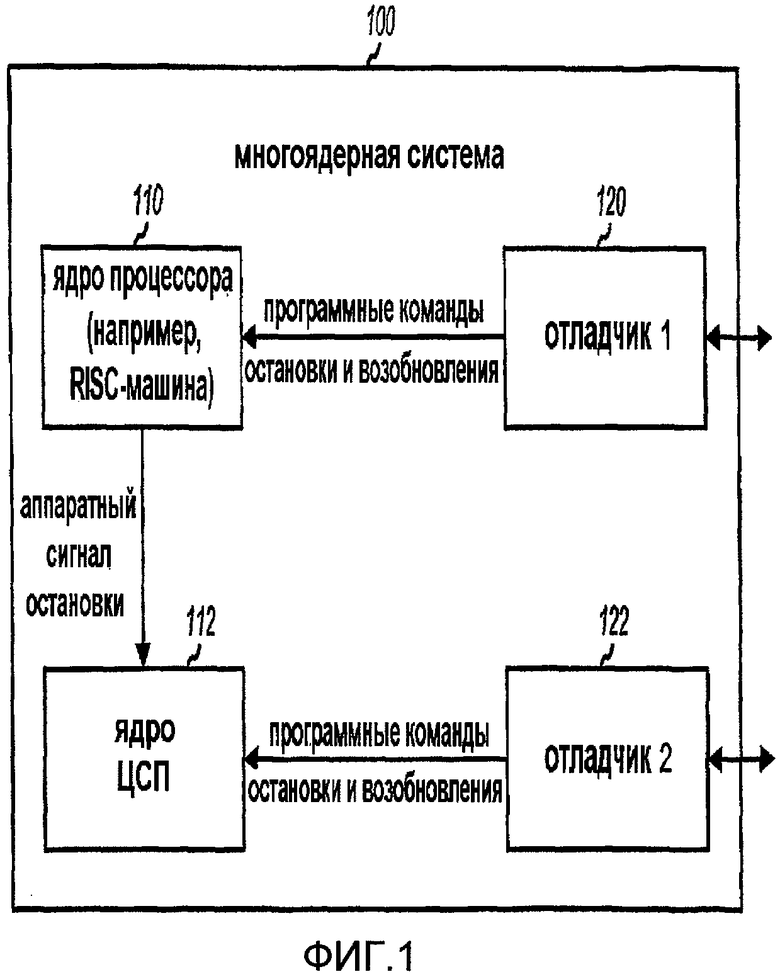

Фиг.1 - многоядерная система с синхронной остановкой для двух ядер обработки.

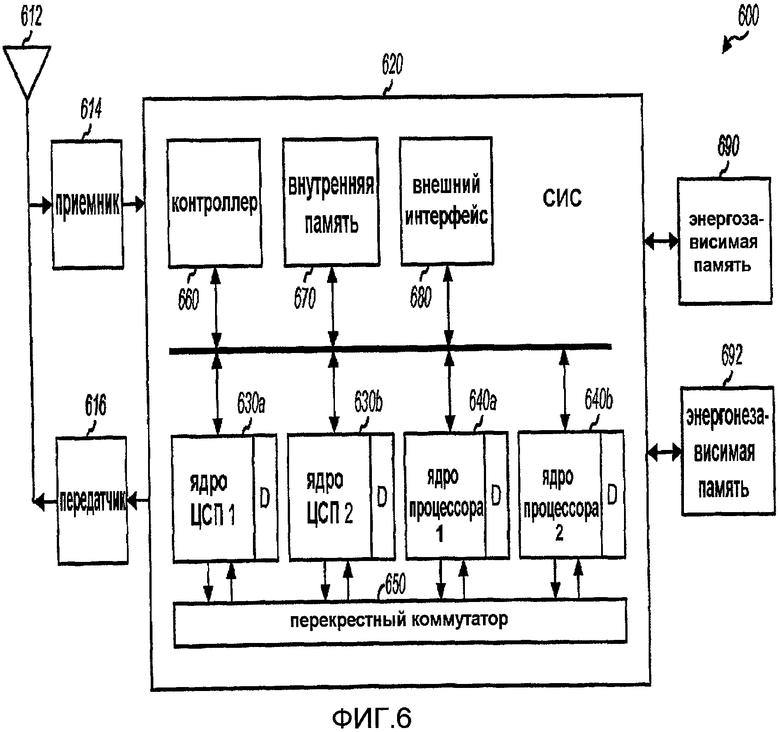

Фиг.2 - многоядерная система с синхронными остановкой и возобновлением для двух ядер обработки.

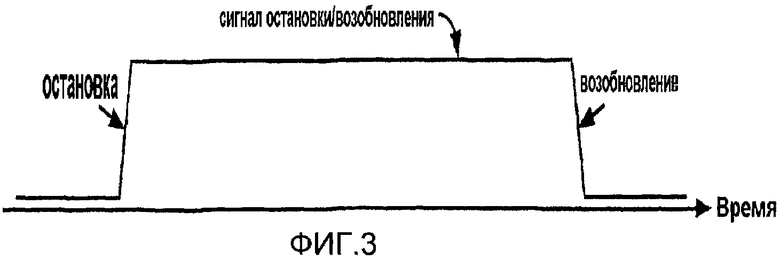

Фиг.3 - иллюстративный аппаратный сигнал остановки/возобновления.

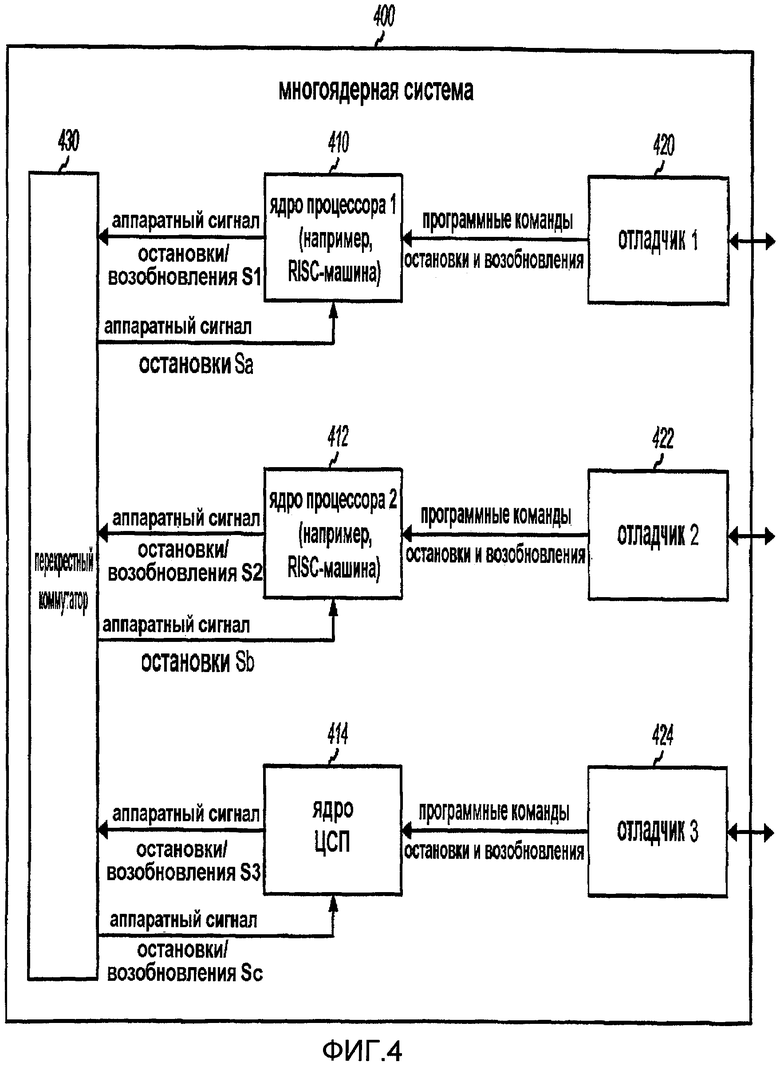

Фиг.4 - многоядерная система с синхронными остановкой и возобновлением для трех ядер обработки.

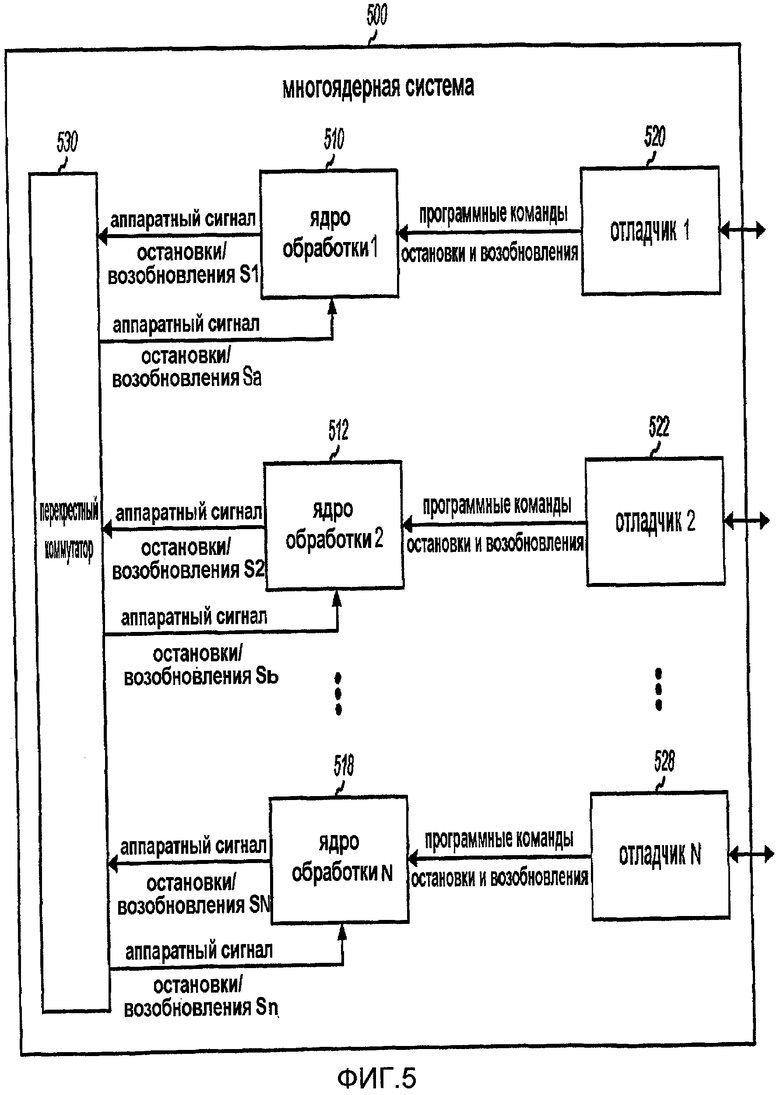

Фиг.5 - многоядерная система с синхронными остановкой и возобновлением для множественных (N) ядер обработки.

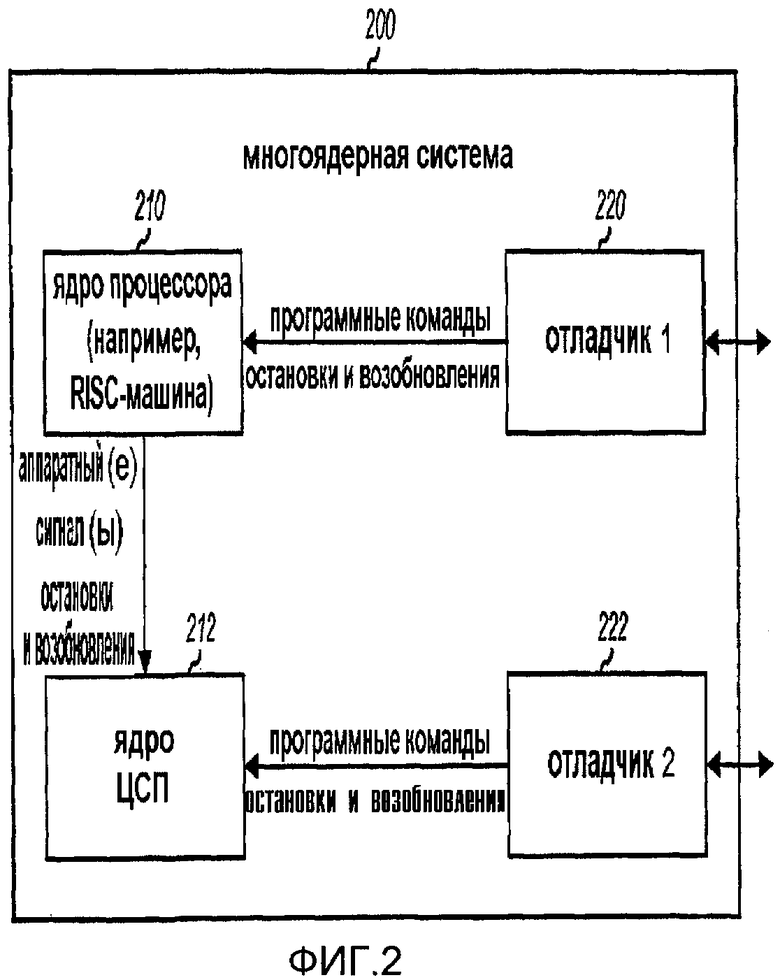

Фиг.6 - блок-схема беспроводного устройства.

Подробное описание

Слово "иллюстративный" используется здесь в смысле "служащий примером, вариантом или иллюстрацией". Любой вариант осуществления или конструкцию, описанный/ую здесь как "иллюстративный/ую", не обязательно рассматривать как предпочтительный/ую или преимущественный/ую над другими вариантами осуществления или конструкциями.

Описанные здесь методы отладки можно использовать для различных многоядерных систем. Многоядерную систему можно реализовать в одной интегральной схеме (ИС), например, специализированной интегральной схеме (СИС), цифровом сигнальном процессоре (ЦСП), устройстве цифровой обработки сигнала (DSPD), программируемом логическом устройстве (ПЛУ), вентильной матрице, программируемой пользователем (FPGA), процессоре, контроллере, микропроцессоре и т.д. Например, многоядерная система может представлять собой систему на микросхеме (SoC), и множественные ядра обработки можно изготавливать на одном или нескольких кристаллах ИС, заключенных в единый корпус. Многоядерную систему также можно реализовать посредством множественных ИС. Многоядерную систему также можно использовать для различных электронных устройств, например устройства беспроводной связи, сотового телефона, карманного персонального компьютера (КПК), бытового электронного устройства, портативного компьютера и т.д.

На фиг.1 показана блок-схема иллюстративной многоядерной системы 100, которая поддерживает синхронную остановку для двух ядер обработки в ходе отладки. Многоядерная система 100 включает в себя ядро 110 процессора, которое осуществляет обработку общего назначения для СИС 100, и ядро 112 ЦСП, которое осуществляет математические расчеты для СИС. Ядро 110 процессора может представлять собой машину типа компьютера с сокращенным набором команд (RISC) или некоторый другой тип процессора. RISC-машина представляет собой процессор общего назначения, который предназначен для очень быстрого выполнения малого набора поддерживаемых инструкций. В общем случае, ядро 110 процессора и ядро 112 ЦСП можно реализовать в различных конструкциях, которые известны в технике. Каждое ядро обработки выполняет последовательность инструкций, которые могут храниться в памяти (например, кэш-памяти) или поступать на ядро иным образом.

Отладчик 120 используется для отладки ядра 110 процессора, и отладчик 122 используется для отладки ядра 112 ЦСП. Каждый отладчик может взаимодействовать, например, через JTAG или некоторый другой тип интерфейса, с помощью внешней хост-системы, которая направляет работу этого отладчика. Например, внешняя хост-система может настраивать отладчик на задание точек прерывания в программе, выполняемой соответствующим ядром обработки, для доступа к ресурсам ядра обработки, для приостановки/остановки и для возобновления работы ядра обработки, и т.д. Каждый отладчик может подавать команды отладки на соответствующее ядро обработки для управления работой этого ядра в ходе отладки. Эти команды отладки можно выбирать из набора программных команд или инструкций, которые может выполнять ядро обработки. Например, команда отладки может задавать точку прерывания (или может являться программной командой остановки), которая останавливает ядро обработки в случае наступления того или иного события. Команда отладки также может представлять собой программную команду возобновления, которая предписывает ядру обработки возобновить работу. Каждое ядро обработки обычно выполняет команды отладки таким же образом, как инструкции для нормальной работы и обычно не знает, что действует в режиме отладки.

В примере, показанном на фиг.1, ядро 110 процессора генерирует аппаратный сигнал остановки всякий раз, когда оно принимает программную команду остановки от отладчика 120. Этот аппаратный сигнал остановки поступает на ядро 112 ЦСП и используется для остановки ядра ЦСП всякий раз, когда ядро процессора останавливается.

Конструкция, показанная на фиг.1, поддерживает синхронную остановку в среде многоядерной отладки. Например, отладчик 120 может задавать точку прерывания на ядре 110 процессора, отладчик 122 может задавать точку прерывания на ядре 112 ЦСП и вне зависимости от того, какая точка прерывания достигается первой, может останавливать оба ядра обработки. Если первой достигается точка прерывания на ядре 110 процессора, то ядро 110 процессора активирует свой аппаратный сигнал остановки, который затем останавливает ядро 112 ЦСП. Напротив, если первой достигается точка прерывания на ядре 112 ЦСП, то ядро 112 ЦСП активирует свой аппаратный сигнал остановки (не показанный на фиг.1), который поступает на ядро 110 процессора и останавливает ядро процессора (также не показанное на фиг.1). Этот признак часто называют многоядерной остановкой. Однако конструкция, показанная на фиг.1. не поддерживает постепенное возобновление работы из многоядерной остановки. По завершении функций отладки, ядра 110 и 112 обработки могут возобновлять работу путем подачи отдельных программных команд возобновления от отладчиков 120 и 122 соответственно. Однако отладчики 120 и 122 обычно не синхронизированы и/или два ядра обработки могут не возобновлять работу в одно и то же время после получения их программных команд возобновления. В этом случае, одно ядро обработки (например, ядро 110 процессора) может действовать в течение многих циклов (например, тысяч циклов) прежде, чем другое ядро обработки (например, ядро 112 ЦСП) возобновит работу. Таким образом, многоядерная система 100 выходит из синхронизма, что нежелательно.

На фиг.2 показана блок-схема варианта осуществления многоядерной системы 200, которая поддерживает синхронные остановку и возобновление для двух ядер обработки в ходе отладки. Многоядерная система 200 может быть реализована посредством СИС или кого-либо другого электронного устройства. Многоядерная система 200 включает в себя ядро 210 процессора, ядро 212 ЦСП и отладчики 220 и 222, которые действуют аналогично ядру 110 процессора, ядру 112 ЦСП и отладчикам 120 и 122 соответственно, показанным на фиг.1.

Согласно варианту осуществления, показанному на фиг.2, ядро 210 процессора активирует аппаратный(е) сигнал(ы) остановки и возобновления, которые могут поступать на ядро 212 ЦСП и использоваться для синхронных остановки и возобновления соответственно в ходе многоядерной отладки. Ядро 210 процессора выдает аппаратный сигнал остановки всякий раз, когда ядро процессора останавливается точкой прерывания или программной командой остановки для отладчика 220. Ядро 210 процессора активирует аппаратный сигнал возобновления всякий раз, когда ядро процессора возобновляет работу согласно программной команде возобновления от отладчика 220. Таким образом, аппаратный(е) сигнал(ы) остановки и возобновления указывают состояние ядра 210 процессора.

На фиг.3 показан вариант осуществления аппаратного сигнала остановки/возобновления, который можно использовать для ядра 210 процессора, показанного на фиг.2. Согласно этому варианту осуществления передний/нарастающий фронт аппаратного сигнала остановки/возобновления указывает остановку работы, а задний/спадающий фронт аппаратного сигнала остановки/возобновления указывает возобновление работы. Также можно использовать противоположную полярность, в результате чего остановку работы может указывать задний/спадающий фронт и возобновление работы может указывать передний/нарастающий фронт.

В другом варианте осуществления, раздельные аппаратные сигналы остановки и возобновления используются для указания остановки и возобновления соответственно. В еще одном варианте осуществления, сигналы остановки и возобновления передаются через аппаратный интерфейс, например шину, интерфейс последовательной шины (SBI), и т.д. В еще одном варианте осуществления, сигналы остановки и возобновления указываются путем задания аппаратных прерываний для ядер обработки. Сигналы остановки и возобновления также можно передавать иным образом, от одного ядра обработки к другому ядру обработки без необходимости опираться на отладчики для этих ядер обработки.

Согласно фиг.2 многоядерная система 200 поддерживает синхронную остановку и возобновление в среде многоядерной отладки. Например, отладчик 220 может задавать точку прерывания на ядре 210 процессора, отладчик 222 может задавать точку прерывания на ядре 212 ЦСП и вне зависимости от того, какая точка прерывания достигается первой, может останавливать оба ядра обработки. По завершении функций отладки, оба ядра обработки могут возобновлять работу согласно программной команде возобновления, переданной от отладчика 220 на ядро 210 процессора. После получения этой программной команды возобновления, ядро 210 процессора возобновляет работу и также активирует аппаратный сигнал возобновления. Ядро 212 ЦСП возобновляет работу после получения аппаратного сигнала возобновления от ядра 210 процессора. Благодаря использованию более быстрого аппаратного сигнала возобновления, ядро 212 ЦСП способно возобновлять работу одновременно с ядром 210 процессора с погрешностью в несколько циклов. Тогда ядро 210 процессора и ядро 212 ЦСП будут синхронизироваться при прерывании отладки.

На фиг.2 показан вариант осуществления, в котором одно ядро обработки (например, ядро 210 процессора) генерирует аппаратный(е) сигнал(ы) остановки и возобновления, и другое ядро обработки (например, ядро 212 ЦСП) принимает аппаратный(е) сигнал(ы) остановки и возобновления и действует на их основании. Согласно этому варианту осуществления синхронного возобновления можно добиться, передавая программную команду возобновления на ядро обработки, которое генерирует аппаратный сигнал возобновления для другого ядра обработки.

Синхронная остановка может быть разрешена все время в ходе отладки или может быть разрешена избирательно. Например, ядро 212 ЦСП может получать команду действовать на основании аппаратного сигнала остановки или игнорировать этот сигнал. Синхронное возобновление также может быть разрешено все время в ходе отладки или может быть разрешено избирательно. Например, ядро 212 ЦСП может получать команду действовать на основании аппаратного сигнала возобновления или игнорировать этот сигнал.

На фиг.4 показана блок-схема варианта осуществления многоядерной системы 400, которая поддерживает синхронные остановку и возобновление для трех ядер обработки в ходе отладки. Многоядерную систему 400 можно реализовать посредством СИС или кого-либо другого электронного устройства. Согласно варианту осуществления, показанному на фиг.4, многоядерная система 400 включает в себя ядра 410 и 412 процессора, ядро 414 ЦСП, перекрестный коммутатор 430 и отладчики 420, 422 и 424. Ядра 410 и 412 процессора могут представлять собой RISC-машины и/или некоторые другие типы процессора и могут предназначаться для поддержки разных приложений и функций. Отладчик 420 используется для отладки ядра 410 процессора, отладчик 422 используется для отладки ядра 412 процессора, отладчик 424 используется для отладки ядра 414 ЦСП. Отладчик 420 также можно использовать для отладки обоих ядер 410 и 412 процессора. Каждый отладчик может подавать команды отладки на соответствующее ядро обработки(а) для управления работой соответствующего(их) ядра(ер) в ходе отладки.

Согласно варианту осуществления, показанному на фиг.4, ядро 410 процессора генерирует и выдает выходной аппаратный сигнал остановки/возобновления S1 на перекрестный коммутатор 430 и дополнительно принимает входной аппаратный сигнал остановки Sa от перекрестного коммутатора. Ядро 412 процессора генерирует и выдает выходной аппаратный сигнал остановки/возобновления S2 на перекрестный коммутатор 430 и дополнительно принимает входной аппаратный сигнал остановки Sb от перекрестного коммутатора. Ядро 414 ЦСП генерирует и выдает выходной аппаратный сигнал остановки/возобновления S3 на перекрестный коммутатор 430 и дополнительно принимает входной аппаратный сигнал остановки/возобновления Sc от перекрестного коммутатора. Каждое ядро обработки может активировать свой выходной аппаратный сигнал остановки/возобновления всякий раз, когда это ядро останавливается (например, согласно программной команде остановки), и может деактивировать свой выходной аппаратный сигнал остановки/возобновления всякий раз, когда это ядро возобновляет работу (например, согласно программной команде возобновления). Выходной аппаратный сигнал остановки/возобновления для каждого ядра обработки может генерироваться согласно фиг.3.

Согласно варианту осуществления, показанному на фиг.4, ядра 410 и 412 процессора останавливаются при активации их входных аппаратных сигналов остановки Sa и Sb соответственно. Ядро 414 ЦСП останавливается при активации своего входного аппаратного сигнала остановки/возобновления Sc и возобновляет работу при деактивации своего аппаратного сигнала остановки/возобновления Sc.

Согласно варианту осуществления перекрестный коммутатор 430 выбирает один из трех выходных аппаратных сигналов остановки/возобновления S1, S2 и S3 и выдает выбранный аппаратный сигнал в качестве входных аппаратных сигналов остановки Sa и Sb и входного аппаратного сигнала остановки/возобновления Sc. Согласно этому варианту осуществления каждое ядро обработки может синхронно останавливать два других ядра обработки, поскольку все три ядра обработки принимают один и тот же аппаратный сигнал остановки. Согласно этому варианту осуществления каждое из ядер 410 и 412 процессора может синхронно возобновлять работу ядра 414 ЦСП, которое также принимает аппаратный сигнал возобновления.

В другом варианте осуществления, перекрестный коммутатор 430 выдает выходной аппаратный сигнал остановки/возобновления S2 или S3 в качестве входного аппаратного сигнала остановки Sa, выдает выходной аппаратный сигнал остановки/возобновления S1 или S3 в качестве входного аппаратного сигнала остановки Sb и выдает выходной аппаратный сигнал остановки/возобновления S1 или S2 в качестве входного аппаратного сигнала остановки/возобновления Sc. Согласно этому варианту осуществления ядро 410 процессора может синхронно останавливаться либо ядром 412 процессора, либо ядром 414 ЦСП, ядро 412 процессора может синхронно останавливаться либо ядром 410 процессора, либо ядром 414 ЦСП, и ядро 414 ЦСП может синхронно останавливаться и повторно запускаться ядром 410 или 412 процессора. Этот вариант осуществления обеспечивает гибкость в принятии решения, какое(ие) ядро(а) обработки может(могут) синхронно останавливать и/или повторно запускать каждое ядро обработки.

Ядра обработки и перекрестный коммутатор также могут действовать иначе, что также входит в объем изобретения. Например, каждое ядро обработки может иметь возможность синхронно останавливать другие ядра обработки, но только одно ядро 410 процессора может иметь возможность синхронно перезапускать ядро 414 ЦСП. Согласно этому варианту осуществления ядро 412 процессора и ядро 414 ЦСП могут выдавать входные аппаратные сигналы остановки вместо выходных аппаратных сигналов остановки/возобновления.

На фиг.5 показана блок-схема варианта осуществления многоядерной системы 500, которая поддерживает синхронные остановку и возобновление для множества (N) ядер 510-518 обработки в ходе отладки. Многоядерную систему 500 можно реализовать посредством СИС или кого-либо другого электронного устройства. Каждое из ядер 510-518 обработки может быть ядром процессора, ядром ЦСП или блоком обработки некоторого другого типа. Отладчики 520-528 используются для отладки ядер 510-518 обработки соответственно. Один отладчик также можно использовать для отладки более одного ядра обработки. Каждый отладчик может подавать команды отладки на соответствующее(ие) ядро(а) обработки для управления работой соответствующего(их) ядра(ер) в ходе отладки.

Согласно варианту осуществления, показанному на фиг.5, каждое из ядер 510-518 обработки генерирует и выдает выходной аппаратный сигнал остановки/возобновления на перекрестный коммутатор 530 и дополнительно принимает входной аппаратный сигнал остановки/возобновления от перекрестного коммутатора. Каждое ядро обработки может активировать свой выходной аппаратный сигнал остановки/возобновления всякий раз, когда это ядро останавливается (например, согласно программной команде остановки) и может деактивировать свой выходной аппаратный сигнал остановки/возобновления всякий раз, когда это ядро возобновляет работу (например, согласно программной команде возобновления). Ядро обработки может активировать свой выходной аппаратный сигнал остановки/возобновления путем назначения сигналу высокого логического уровня и может деактивировать выходной аппаратный сигнал остановки/возобновления путем назначения сигналу низкого логического уровня, как показано на фиг.3. Согласно варианту осуществления каждое ядро обработки останавливается всякий раз при активации его входного аппаратного сигнала остановки/возобновления и возобновляет всякий раз при деактивации его входного аппаратного сигнала остановки/возобновления. Согласно варианту осуществления каждое ядро обработки можно запрограммировать на избирательное действие на основании его входного аппаратного сигнала остановки/возобновления или игнорирование его.

Согласно варианту осуществления перекрестный коммутатор 530 выбирает выходной аппаратный сигнал остановки/возобновления от одного ядра обработки и выдает этот выбранный аппаратный сигнал в качестве входных аппаратных сигналов остановки/возобновления для всех N ядер обработки. Согласно этому варианту осуществления каждое ядро обработки может синхронно останавливать или синхронно перезапускать другие ядра обработки, поскольку все ядра обработки принимают один и тот же аппаратный сигнал остановки/возобновления. Перекрестный коммутатор 530 может выбирать один выходной аппаратный сигнал остановки/возобновления из N выходных аппаратных сигналов остановки/возобновления S1-SN по-разному. В одном варианте осуществления, перекрестный коммутатор 530 отслеживает N выходных аппаратных сигналов остановки/возобновления, выбирает выходной аппаратный сигнал остановки/возобновления, который активируется первым, когда все ядра обработки действуют, и выбирает выходной аппаратный сигнал остановки/возобновления, который деактивируется первым, когда ядра обработки остановлены. В другом варианте осуществления, одно ядро обработки может быть назначено главным ядром обработки, и перекрестный коммутатор 530 может выбирать выходной аппаратный сигнал остановки/возобновления из этого ядра обработки.

В другом варианте осуществления, каждое ядро Cx обработки (для x=a, b,..., n) связано с набором ядер обработки, которые могут останавливать и/или перезапускать это ядро Cx обработки. Согласно этому варианту осуществления перекрестный коммутатор 530 выбирает и выдает выходной аппаратный сигнал остановки/возобновления с одного из ядер обработки в наборе в качестве входного аппаратного сигнала остановки/возобновления для ядра Cx обработки. Этот вариант осуществления обеспечивает гибкость в принятии решения, какое(ие) ядро(а) обработки может(могут) синхронно останавливать и/или повторно запускать ядро Cx обработки. Ядра обработки и перекрестный коммутатор также могут действовать иначе, что также входит в объем изобретения.

Как отмечено выше, методы отладки можно использовать для многоядерных систем, используемых в различных электронных устройствах. Ниже описано иллюстративное применение методов отладки для беспроводных устройств.

На фиг.6 показана блок-схема беспроводного устройства 600, которое может иметь возможность отслеживать и/или поддерживать связи с одной или несколькими системами беспроводной связи. В приемном тракте, антенна 612 принимает сигналы, передаваемые базовыми станциями и/или спутниками, и выдает принятый сигнал на приемник (RCVR) 614. Приемник 614 обрабатывает (например, фильтрует, усиливает, понижает частоту и цифрует) принятый сигнал и выдает дискретизированный сигнал на СИС 620 для дальнейшей обработки. В передающем тракте, СИС 620 обрабатывает данные, подлежащие передаче, и выдает чипы данных на передатчик (TMTR) 616. Передатчик 616 обрабатывает (например, преобразует к аналоговому виду, фильтрует, усиливает и повышает частоту) чипы данных и генерирует модулированный сигнал, который передается через антенну 612.

СИС 620 включает в себя различные блоки обработки, которые поддерживают мониторинг и/или связь с одной или несколькими системами связи. Согласно варианту осуществления, показанному на фиг.6, СИС 620 включает в себя ядра 630a и 630b ЦСП, ядра 640a и 640b процессора, перекрестный коммутатор 650, контроллер 660, внутреннюю память 670 и блок внешнего интерфейса 680. Ядра 630a и 630b ЦСП осуществляют обработку (например, демодуляцию и декодирование) для приемного тракта, обработку (например, кодирование и модуляцию) для передающего тракта и/или обработку для других приложений и функций. Ядра 640a и 640b процессора поддерживают различные функции, например, видео, аудио, графику, игры и т.д. Каждое ядро процессора может представлять собой RISC-машину, микропроцессор или некоторый другой тип процессора. Контроллер 660 управляет работой блоков обработки в СИС 620. Во внутренней памяти 670 хранятся данные и программные коды, используемые блоками обработки в СИС 620. Блок внешнего интерфейса 680 взаимодействует с другими блоками, внешними по отношению к СИС 620. В общем случае, СИС 620 может включать в себя меньше, больше и/или другие блоки обработки, чем показано на фиг.6. Количество блоков обработки и типы блоков обработки, включенных в СИС 620, обычно зависят от различных факторов, например, систем связи, приложений и функций, поддерживаемых беспроводным устройством 600.

Согласно варианту осуществления, показанному на фиг.6, каждое ядро обработки включает в себя аппаратный отладчик (D), который поддерживает отладку этого ядра. Отладчики для ядер 630a и 630b ЦСП и ядер 640a и 640b процессора могут поддерживать связь с внешней хост-системой через JTAG или некоторый другой тип интерфейса (не показанный на фиг.6). Перекрестный коммутатор 650 принимает входные аппаратные сигналы остановки, выходные аппаратные сигналы возобновления и/или выходные аппаратные сигналы остановки/возобновления от ядер 630a и 630b ЦСП и ядер 640a и 640b процессора. Перекрестный коммутатор 650 выдает входные аппаратные сигналы остановки, входные аппаратные сигналы возобновления и/или входные аппаратные сигналы остановки/возобновления на ЦСП и ядра процессора, например, как описано выше со ссылкой на фиг.4 или 5.

СИС 620 дополнительно подключена к энергозависимой памяти 690 и энергонезависимой памяти 692. Энергозависимая память 690 обеспечивает хранилище большого объема для данных и программных кодов, используемых СИС 620. Энергонезависимая память 692 обеспечивает энергонезависимое хранилище большого объема.

Описанные здесь методы отладки можно реализовать по-разному. Например, эти методы можно реализовать аппаратными, программно-аппаратными, программными или комбинированными средствами. Для аппаратной реализации, методы отладки можно реализовать в виде одной или нескольких СИС, ЦСП, DSPD, ПЛУ, FPGA, процессоров, контроллеров, микроконтроллеров, микропроцессоров, электронных устройств, других электронных блоков, предназначенных для осуществления описанных здесь функций или их комбинации. Некоторые аспекты методов отладки можно реализовать в виде программных модулей (например, процедур, функций и т.д.), которые осуществляют описанные здесь функции. Программные коды могут храниться в памяти (например, памяти 670, 690 или 692, показанной на фиг.6) и выполняться процессором (например, ядром 640a или 640b процессора). Память можно реализовать в процессоре или вне процессора.

Вышеприведенное описание раскрытых вариантов осуществления позволяет специалисту в данной области техники реализовать настоящее изобретение на практике. Специалист в данной области техники может предложить различные модификации этих вариантов осуществления, и установленные здесь общие принципы можно применять к другим вариантам осуществления в рамках сущности или объема изобретения. Таким образом, настоящее изобретение не предусматривает ограничения показанными здесь вариантами осуществления, но подлежит рассмотрению согласно широчайшему объему, отвечающему раскрытым здесь принципам и новым признакам.

Изобретение относится к способу и системе отладки многоядерной системы с возможностями синхронной остановки и синхронного возобновления. Техническим результатом является повышение надежности отладки за счет координации отладки ядер обработки с учетом их взаимодействия. В способе в ходе отладки многоядерного устройства, первое или второе ядро обработки принимает программную команду остановки работы и генерирует первый аппаратный сигнал, указывающий остановку. Другое ядро обработки принимает первый аппаратный сигнал и останавливает работу. Оба ядра обработки останавливаются приблизительно в одно и то же время на основании первого аппаратного сигнала. Затем первое или второе ядро обработки принимает другую программную команду для возобновления работы и генерирует второй аппаратный сигнал, указывающий возобновление работы. Другое ядро обработки принимает второй аппаратный сигнал и возобновляет работу. Оба ядра обработки возобновляют работу приблизительно в одно и то же время на основании второго аппаратного сигнала. 5 н. и 8 з.п. ф-лы, 6 ил.

1. Многоядерное устройство, содержащее:

первое ядро обработки, действующее для генерации аппаратного сигнала возобновления в ответ на получение программной команды возобновления, указывающего возобновление работы из состояния остановки в ходе отладки первого ядра обработки, и действующее для подачи аппаратного сигнала возобновления на второе ядро обработки, при этом второе ядро обработки подключено к первому ядру обработки и действует в ответ на получение аппаратного сигнала возобновления из первого ядра обработки для возобновления работы из состояния остановки в ходе отладки второго ядра обработки; при этом первое ядро обработки возобновляет работу, когда генерируется аппаратный сигнал возобновления, и второе ядро обработки возобновляет работу за заданное количество циклов после получения аппаратного сигнала возобновления; и

первое ядро обработки действует для генерации аппаратного сигнала остановки, указывающего остановку, и при этом второе ядро обработки действует для остановки в ответ на получение аппаратного сигнала остановки; и второе ядро обработки действует для генерации аппаратного сигнала остановки, указывающего остановку первого ядра обработки в ходе отладки второго ядра обработки, при этом первое ядро обработки действует для приема аппаратного сигнала остановки и для остановки синхронно со вторым ядром обработки после получения аппаратного сигнала остановки.

2. Многоядерное устройство по п.1, в котором аппаратный сигнал возобновления соответствует первому фронту физического аппаратного сигнала, и аппаратный сигнал остановки соответствует второму фронту физического аппаратного сигнала.

3. Многоядерное устройство по п.1, в котором, по меньшей мере, одно из первого и второго ядер обработки является ядром обработки цифрового сигнала (ЦСП).

4. Многоядерное устройство по п.1, в котором, по меньшей мере, одно из первого и второго ядер обработки является машиной типа компьютера с сокращенным набором команд (RISC).

5. Многоядерное устройство по п.1, в котором первое и второе ядра обработки изготовлены в виде специализированной интегральной схемы (СИС).

6. Многоядерное устройство, в котором первое ядро обработки подключено ко второму ядру обработки, содержащее:

средство для генерации аппаратного сигнала возобновления из первого ядра обработки в ходе отладки первого ядра обработки, при этом аппаратный сигнал возобновления подается на второе ядро обработки и указывает возобновление работы первого ядра обработки из состояния остановки в ходе отладки первого ядра обработки;

средство для выдачи аппаратного сигнала возобновления на второе ядро обработки;

средство для возобновления работы второго ядра обработки в ответ на получение аппаратного сигнала возобновления от первого ядра обработки;

средство для получения программной команды для возобновления работы первого ядра обработки, при этом аппаратный сигнал возобновления генерируется в ответ на получение программной команды;

средство для генерации аппаратного сигнала остановки первым ядром обработки, при этом аппаратный сигнал остановки указывает остановку;

средство для получения аппаратного сигнала остановки, при этом аппаратный сигнал остановки подается с первого ядра обработки на второе ядро обработки;

средство для остановки работы второго ядра обработки в ответ на получение аппаратного сигнала остановки вторым ядром обработки;

средство для генерирования аппаратного сигнала остановки вторым ядром обработки, при этом аппаратный сигнал остановки указывает остановку;

средство для подачи аппаратного сигнала остановки со второго ядра обработки на первое ядро обработки;

средство для получения аппаратного сигнала остановки первым ядром обработки; и

средство для остановки работы первого ядра обработки в ответ на получение аппаратного сигнала остановки.

7. Способ отладки многоядерного устройства, содержащий этапы, на которых

генерируют аппаратный сигнал возобновления на первом ядре обработки интегральной схемы, при этом аппаратный сигнал возобновления указывает возобновление работы из состояния остановки в ходе отладки первого ядра обработки;

подают аппаратный сигнал возобновления с первого ядра обработки на второе ядро обработки;

получают аппаратный сигнал возобновления на втором ядре обработки, при этом аппаратный сигнал возобновления подают с первого ядра обработки;

возобновляют работу второго ядра обработки в ответ на получение аппаратного сигнала возобновления;

получают программную команду возобновления для возобновления работы первого ядра обработки, при этом аппаратный сигнал возобновления генерируют в ответ на получение программной команды возобновления;

генерируют аппаратный сигнал остановки на первом ядре обработки, указывающий остановку;

принимают аппаратный сигнал остановки на втором ядре обработки;

останавливают работу второго ядра обработки в ответ на получение аппаратного сигнала остановки; и

получают аппаратный сигнал остановки на первом ядре обработки для остановки работы первого ядра обработки, при этом аппаратный сигнал остановки генерируют в ответ на получение программной команды остановки.

8. Многоядерное устройство, содержащее:

множество ядер обработки, включающее в себя первое ядро обработки, второе ядро обработки и третье ядро обработки, при этом первое ядро обработки действует для генерации аппаратного сигнала остановки, указывающего остановку работы в ходе отладки первого ядра обработки, второго ядра обработки и третьего ядра обработки; при этом первое ядро обработки действует для остановки, когда генерируется аппаратный сигнал остановки, и при этом каждое из второго ядра обработки и третьего ядра обработки действует для остановки после получения аппаратного сигнала остановки;

перекрестный коммутатор, электрически подключенный ко множеству ядер обработки, при этом перекрестный коммутатор действует для получения аппаратного сигнала остановки от первого ядра обработки и для выдачи аппаратного сигнала остановки на второе ядро обработки и на третье ядро обработки в ходе отладки первого ядра обработки, второго ядра обработки и третьего ядра обработки;

первое ядро обработки действует для генерации аппаратного сигнала возобновления, указывающего возобновление работы, и при этом перекрестный коммутатор действует для получения аппаратного сигнала возобновления от первого ядра обработки и для выдачи аппаратного сигнала возобновления на второе ядро обработки и на третье ядро обработки; и

второе ядро обработки действует для генерации аппаратного сигнала возобновления, указывающего возобновление работы, при этом перекрестный коммутатор действует для выдачи аппаратного сигнала возобновления со второго ядра обработки, затем на первое ядро обработки и на третье ядро обработки.

9. Многоядерное устройство по п.8, в котором аппаратный сигнал остановки соответствует первому фронту физического аппаратного сигнала, и аппаратный сигнал возобновления соответствует второму фронту физического аппаратного сигнала.

10. Многоядерное устройство по п.8, в котором множество ядер обработки содержат, по меньшей мере, одно ядро обработки цифрового сигнала (ЦСП) и, по меньшей мере, одну машину типа компьютера с сокращенным набором команд (RISC).

11. Многоядерное устройство, содержащее:

первое ядро обработки, действующее для генерации первого сигнала в ходе отладки первого ядра обработки, при этом первое ядро обработки дополнительно действует для получения второго сигнала и третьего сигнала, при этом первый сигнал включает в себя одну из первой команды остановки для остановки работы, первой команды возобновления для возобновления работы и первой команды остановки и возобновления для остановки работы и последующего возобновления работы по истечении заданного периода времени;

второе ядро обработки, действующее для генерации второго сигнала в ходе отладки второго ядра обработки, при этом второе ядро обработки дополнительно действует для получения первого сигнала и третьего сигнала, при этом второй сигнал включает в себя одну из второй команды остановки для остановки работы и второй команды возобновления для возобновления работы;

третье ядро обработки, действующее для генерации третьего сигнала в ходе отладки третьего ядра обработки, при этом третье ядро обработки дополнительно действует для получения первого сигнала и второго сигнала; и

перекрестный коммутатор, электрически подключенный к первому ядру обработки, второму ядру обработки и третьему ядру обработки, при этом перекрестный коммутатор действует для получения первого сигнала и для выдачи первого сигнала одновременно на второе ядро обработки и на третье ядро обработки;

при этом первое ядро обработки действует для остановки работы первого ядра обработки после получения второго сигнала или третьего сигнала, при этом второе ядро обработки действует для остановки работы второго ядра обработки после получения первого сигнала и третьего сигнала, и третье ядро обработки действует для остановки работы третьего ядра обработки после получения первого сигнала или второго сигнала;

при этом второе ядро обработки действует для остановки работы второго ядра обработки и для синхронного возобновления работы второго ядра обработки по истечении заданного периода времени в ответ на получение первого сигнала, и третье ядро обработки действует для остановки работы третьего ядра обработки и для возобновления работы третьего ядра обработки по истечении заданного периода времени в ответ на получение первого сигнала;

при этом первая команда остановки включает в себя команду для остановки работы второго ядра обработки и третьего ядра обработки синхронно с первым ядром обработки; и первая команда возобновления включает в себя команду для возобновления работы второго ядра обработки и третьего ядра обработки синхронно с первым ядром обработки.

12. Многоядерное устройство по п.11, в котором третье ядро обработки содержит ядро обработки цифрового сигнала (ЦСП) и, по меньшей мере, одно из первого ядра обработки и второго ядра обработки содержит машину типа компьютера с сокращенным набором команд (RISC).

13. Многоядерное устройство по п.11, при этом многоядерное устройство встроено в специализированную интегральную схему (СИС).

| US 20050034017 A1, 10.02.2005 | |||

| ОДНОРОДНАЯ ВЫЧИСЛИТЕЛЬНАЯ СРЕДА С ДВУСЛОЙНОЙ ПРОГРАММИРУЕМОЙ СТРУКТУРОЙ | 1998 |

|

RU2134448C1 |

| WO 2004017204 A1, 26.02.2004. | |||

Авторы

Даты

2010-11-27—Публикация

2007-01-17—Подача