[0001] Данная заявка испрашивает приоритет заявки на патент (Китай) номер 201210450263.3, поданной в Патентное ведомство Китая 12 ноября 2012 года и озаглавленной "METHOD, DEVICE AND SYSTEM FOR PROCESSING DATA DURING IDLE LISTENING", которая полностью содержится в данном документе по ссылке.

ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

[0002] Изобретение относится к технологиям связи и, в частности, к способу, устройству и системе для обработки данных в ходе прослушивания в состоянии бездействия.

УРОВЕНЬ ТЕХНИКИ

[0003] В некоторых странах, предусмотрен несертифицируемый спектр, который находится около полосы частот в 60 ГГц и составляет вплоть до нескольких ГГц, так что технология на основе диапазона миллиметровых волн в 60 ГГц имеет огромную пропускную способность связи. Тем не менее, типичная проблема, с которой сталкиваются современные микросхемы на 60 ГГц, состоит в том, что потребление мощности является чрезмерно большим в ходе прослушивания в состоянии бездействия, а для карманного мобильного устройства высокая потребляемая мощность является неприемлемой.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

[0004] С учетом этого, варианты осуществления изобретения предоставляют способ, устройство и систему для обработки данных в ходе прослушивания в состоянии бездействия, которые используются для снижения потребляемой мощности в ходе прослушивания в состоянии бездействия.

[0005] Согласно первому аспекту предоставляется способ для обработки данных в ходе прослушивания в состоянии бездействия, включающий в себя:

- дискретизацию, в режиме прослушивания в состоянии бездействия, первого аналогового сигнала посредством использования N-битового ADC; и

- дискретизацию, в режиме приемо-передачи, второго аналогового сигнала посредством использования M-битового ADC, причем:

- N и M являются целыми числами, и N меньше M.

[0006] В отношении первого аспекта, в первом возможном способе реализации первого аспекта, N равен 1.

[0007] В отношении первого аспекта или первого возможного способа реализации первого аспекта, во втором возможном способе реализации первого аспекта, причем первая последовательность данных получается посредством дискретизации первого аналогового сигнала посредством использования N-битового ADC, способ дополнительно включает в себя:

- определение того, представляет ли собой первая последовательность данных заданную последовательность данных; и

- дискретизация, в режиме приемо-передачи, второго аналогового сигнала посредством использования M-битового ADC включает в себя:

- когда первая последовательность данных представляет собой заданную последовательность данных, дискретизацию второго аналогового сигнала посредством использования M-битового ADC для того, чтобы получать вторую последовательность данных.

[0008] В отношении второго возможного способа реализации первого аспекта, в третьем возможном способе реализации первого аспекта, определение того, представляет ли собой первая последовательность данных заданную последовательность данных, включает в себя:

- сравнение значения энергии первой последовательности данных со значением энергии заданной последовательности данных; если два значения энергии являются идентичными, первая последовательность данных представляет собой заданную последовательность данных.

[0009] В отношении второго возможного способа реализации первого аспекта, в четвертом возможном способе реализации первого аспекта, заданная последовательность данных включает в себя m-последовательность с r циклов, причем длина каждой m-последовательности составляет L, r и L представляют собой заданные значения;

- вторая последовательность данных включает в себя: данные в стандартной структуре кадра; и

- разность времен между первой последовательностью данных и второй последовательностью данных является временем, занимаемым посредством избыточного бита, и время, занимаемое посредством избыточного бита, превышает или равно времени, требуемому для переключения с N-битового ADC на M-битовый ADC.

[0010] Согласно второму аспекту предоставляется способ для обработки данных в ходе прослушивания в состоянии бездействия, включающий в себя:

- формирование последовательности данных и выполнение цифроаналогового преобразования для последовательности данных для того, чтобы получать аналоговые сигналы, причем аналоговые сигналы включают в себя первый аналоговый сигнал и второй аналоговый сигнал; и

- отправку аналоговых сигналов в приемное устройство, так что приемное устройство дискретизирует, в режиме прослушивания в состоянии бездействия, первый аналоговый сигнал посредством использования N-битового ADC и дискретизирует, в режиме приемо-передачи, второй аналоговый сигнал посредством использования M-битового ADC, причем:

- N и M являются целыми числами, и N меньше M.

[0011] В отношении второго аспекта, в первом возможном способе реализации второго аспекта, последовательность данных включает в себя:

- заданную последовательность данных, избыточный бит и данные в стандартной структуре кадра, причем заданная последовательность данных включает в себя m-последовательность с r циклов, длина каждой m-последовательности составляет L, r и L представляют собой заданные значения, и время, занимаемое посредством избыточного бита, превышает или равно времени, требуемому для переключения с N-битового ADC на M-битовый ADC.

[0012] В отношении первого возможного способа реализации второго аспекта, во втором возможном способе реализации второго аспекта, первый аналоговый сигнал представляет собой аналоговый сигнал, получаемый после того, как цифроаналоговое преобразование выполняется для заданной последовательности данных, и второй аналоговый сигнал представляет собой аналоговый сигнал, получаемый после того, как цифроаналоговое преобразование выполняется для данных в стандартной структуре кадра.

[0013] Согласно третьему аспекту предоставляется приемное устройство, включающее в себя:

- первый блок дискретизации, выполненный с возможностью дискретизировать, в режиме прослушивания в состоянии бездействия, первый аналоговый сигнал посредством использования N-битового ADC; и

- второй блок дискретизации, выполненный с возможностью дискретизировать, в режиме приемо-передачи, второй аналоговый сигнал посредством использования M-битового ADC, причем:

- N и M являются целыми числами, и N меньше M.

[0014] В отношении третьего аспекта, в первом возможном способе реализации третьего аспекта, устройство дополнительно включает в себя:

- процессор, выполненный с возможностью определять то, представляет собой или нет первая последовательность данных заданную последовательность данных; и

- второй блок дискретизации, в частности, выполнен с возможностью дискретизировать, когда процессор определяет то, что первая последовательность данных представляет собой заданную последовательность данных, второй аналоговый сигнал посредством использования M-битового ADC для того, чтобы получать вторую последовательность данных.

[0015] В отношении первого возможного способа реализации третьего аспекта, во втором возможном способе реализации третьего аспекта, процессор, в частности, выполнен с возможностью:

- сравнивать значение энергии первой последовательности данных со значением энергии заданной последовательности данных; если два значения энергии являются идентичными, определять то, что первая последовательность данных представляет собой заданную последовательность данных.

[0016] Согласно четвертому аспекту предоставляется отправляющее устройство, включающее в себя:

- процессор, выполненный с возможностью формировать последовательность данных и выполнять цифроаналоговое преобразование для последовательности данных для того, чтобы получать аналоговые сигналы, причем аналоговые сигналы включают в себя первый аналоговый сигнал и второй аналоговый сигнал; и

- блок отправки, выполненный с возможностью отправлять аналоговые сигналы в приемное устройство, так что приемное устройство дискретизирует, в режиме прослушивания в состоянии бездействия, первый аналоговый сигнал посредством использования N-битового ADC и дискретизирует, в режиме приемо-передачи, второй аналоговый сигнал посредством использования M-битового ADC, причем:

- N и M являются целыми числами, и N меньше M.

[0017] В отношении четвертого аспекта, в первом способе реализации четвертого аспекта, последовательность данных включает в себя:

- заданную последовательность данных, избыточный бит и данные в стандартной структуре кадра, причем заданная последовательность данных включает в себя m-последовательность с r циклов, длина каждой m-последовательности составляет L, r и L представляют собой заданные значения, и время, занимаемое посредством избыточного бита, превышает или равно времени, требуемому для переключения с N-битового ADC на M-битовый ADC.

[0018] В отношении первого возможного способа реализации четвертого аспекта, во втором возможном способе реализации четвертого аспекта, первый аналоговый сигнал представляет собой аналоговый сигнал, получаемый после того, как цифроаналоговое преобразование выполняется для заданной последовательности данных, и второй аналоговый сигнал представляет собой аналоговый сигнал, получаемый после того, как цифроаналоговое преобразование выполняется для данных в стандартной структуре кадра.

[0019] Согласно пятому аспекту предоставляется система связи, включающая в себя любое из вышеприведенных приемных устройств и любое из вышеприведенных отправляющих устройств.

[0020] Согласно вышеприведенным техническим решениям эффективная битовая ширина дискретизации ADC, которая используется в ходе прослушивания в состоянии бездействия, составляет N, что меньше эффективной битовой ширины M дискретизации в режиме приемо-передачи; когда коэффициент полезного действия является фиксированным, потребление мощности является прямо пропорциональным эффективной битовой ширине дискретизации, так что когда эффективная битовая ширина дискретизации уменьшается, потребление мощности также уменьшается, и, следовательно, использование небольшой эффективной битовой ширины дискретизации позволяет уменьшать потребление мощности в ходе прослушивания в состоянии бездействия, когда ADC-производительность является фиксированной.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

[0021] Чтобы более понятно описывать технические решения в вариантах осуществления изобретения, далее кратко представлены прилагаемые чертежи, требуемые для описания вариантов осуществления. Очевидно, что прилагаемые чертежи в последующем описании показывают некоторые варианты осуществления изобретения, и специалисты в данной области техники по-прежнему могут получать другие чертежи из этих прилагаемых чертежей без творческих усилий.

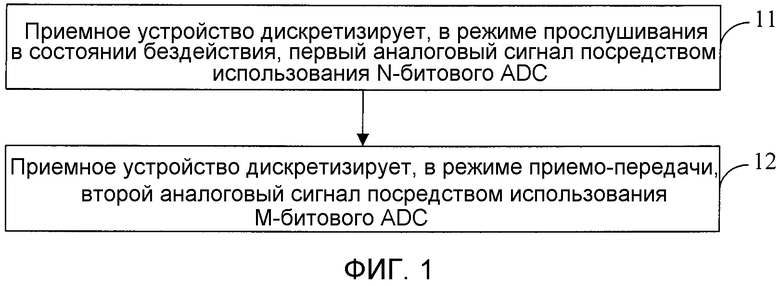

[0022] Фиг. 1 является блок-схемой последовательности операций способа для обработки данных в ходе прослушивания в состоянии бездействия согласно варианту осуществления изобретения;

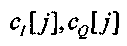

[0023] Фиг. 2 является блок-схемой последовательности операций способа для обработки данных в ходе прослушивания в состоянии бездействия согласно другому варианту осуществления изобретения;

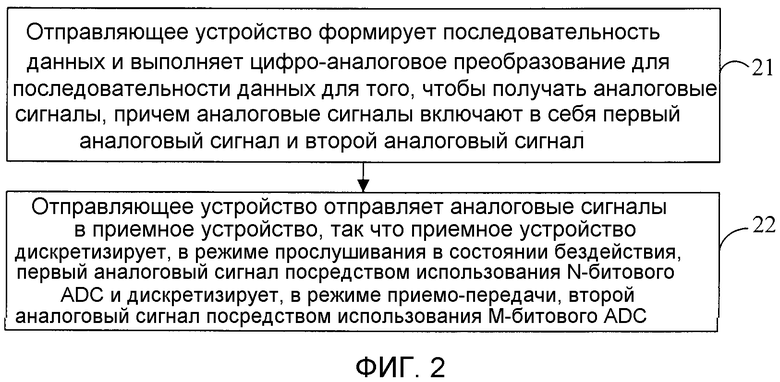

[0024] Фиг. 3 является принципиальной структурной схемой приемного устройства согласно варианту осуществления изобретения;

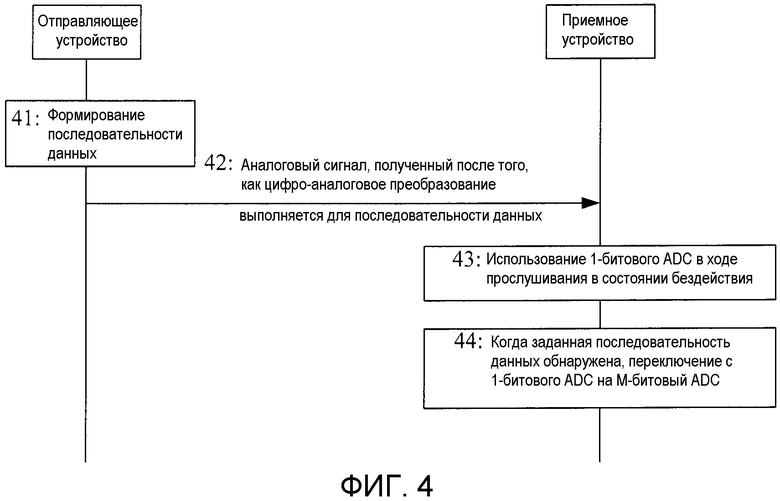

[0025] Фиг. 4 является блок-схемой последовательности операций способа для обработки данных в ходе прослушивания в состоянии бездействия согласно другому варианту осуществления изобретения;

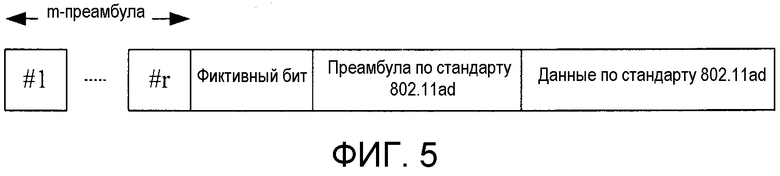

[0026] Фиг. 5 является принципиальной структурной схемой отправленного кадра данных согласно варианту осуществления изобретения;

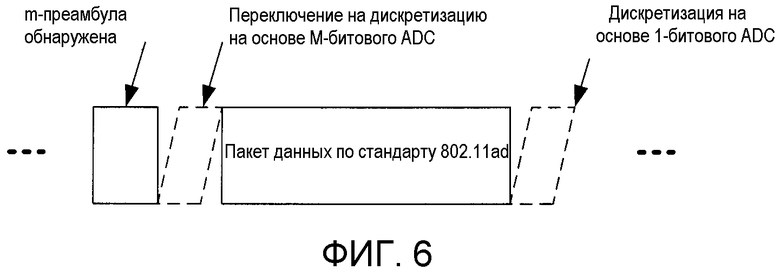

[0027] Фиг. 6 является принципиальной схемой рабочего режима приемной стороны согласно варианту осуществления изобретения;

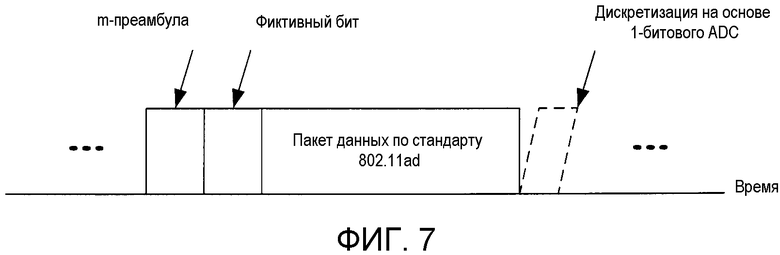

[0028] Фиг. 7 является принципиальной схемой рабочего режима отправляющей стороны согласно варианту осуществления изобретения;

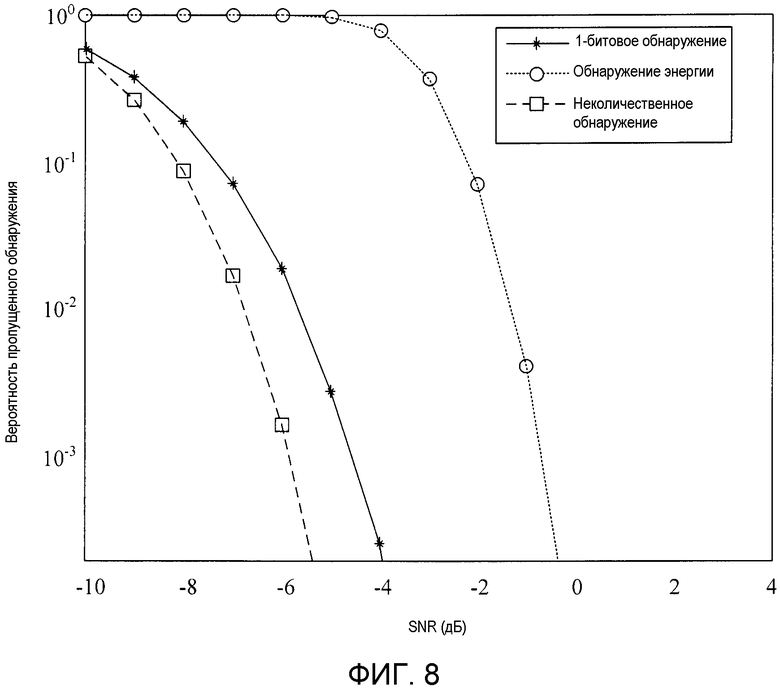

[0029] Фиг. 8 является принципиальной схемой производительности в отношении вероятности пропущенного обнаружения для дискретизации на основе 1-битового ADC и традиционных технологий согласно варианту осуществления изобретения;

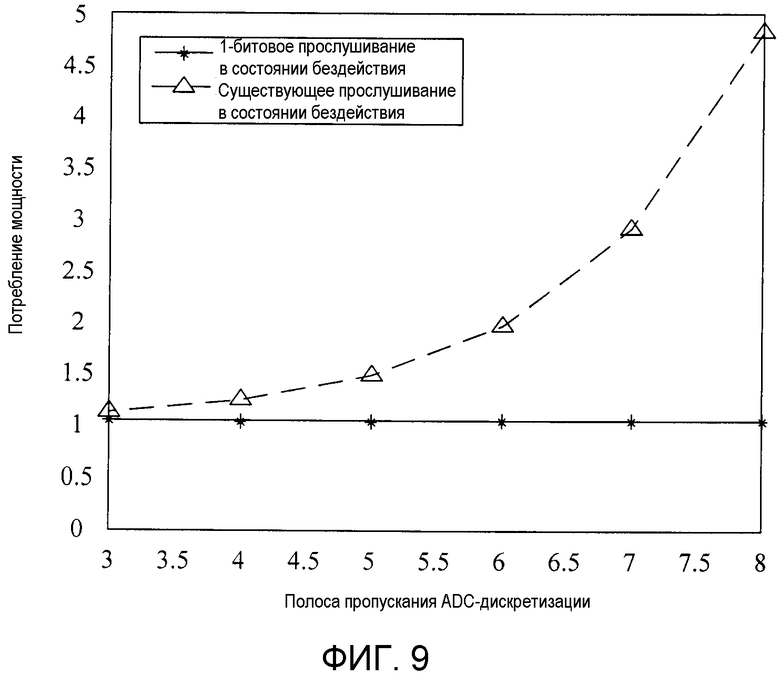

[0030] Фиг. 9 является принципиальной схемой потребления мощности, которое возникает в ходе прослушивания в состоянии бездействия и обусловлено дискретизацией на основе 1-битового ADC и традиционной технологией, согласно варианту осуществления изобретения;

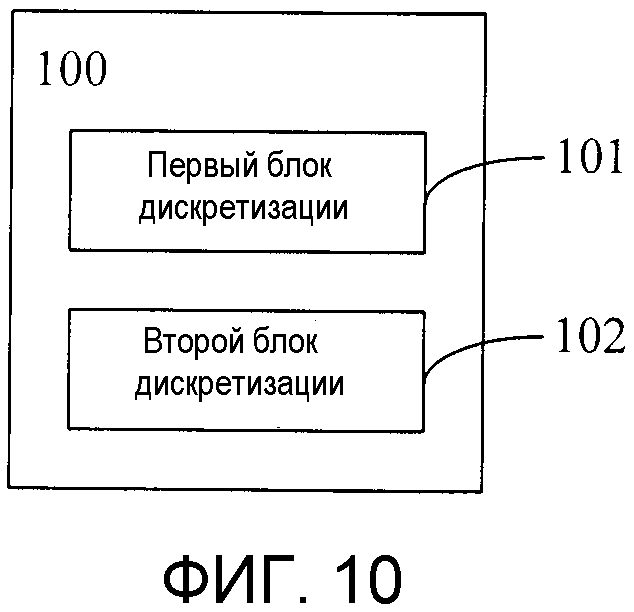

[0031] Фиг. 10 является принципиальной структурной схемой приемного устройства согласно варианту осуществления изобретения;

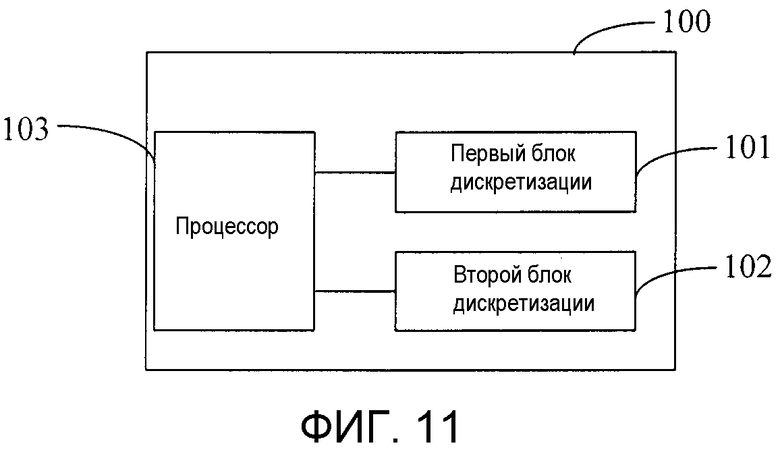

[0032] Фиг. 11 является принципиальной структурной схемой приемного устройства согласно другому варианту осуществления изобретения;

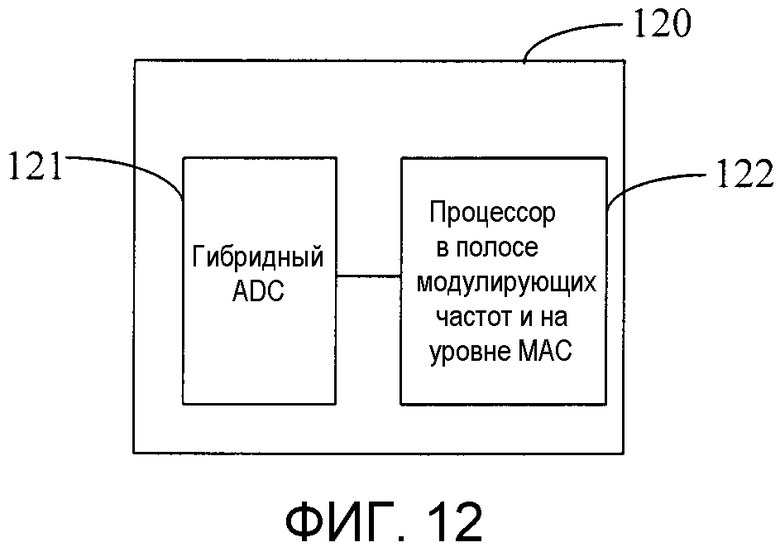

[0033] Фиг. 12 является принципиальной структурной схемой приемного устройства согласно другому варианту осуществления изобретения;

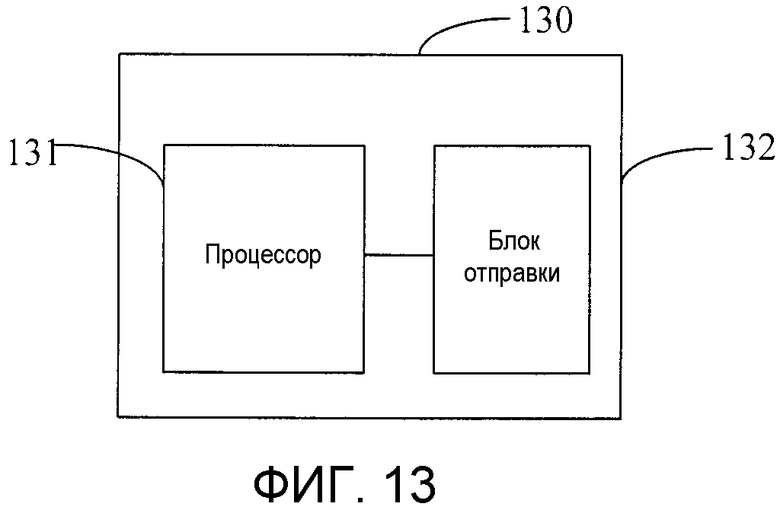

[0034] Фиг. 13 является принципиальной структурной схемой варианта осуществления отправляющего устройства согласно варианту осуществления изобретения;

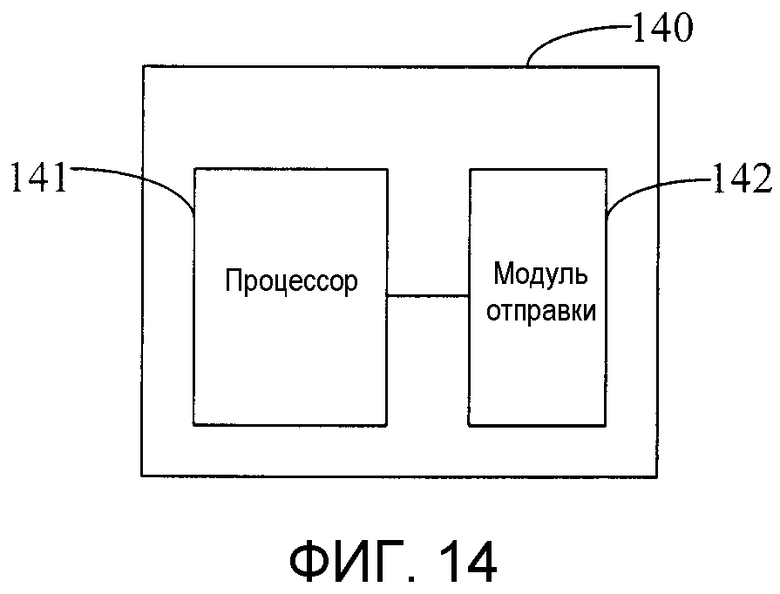

[0035] Фиг. 14 является принципиальной структурной схемой другого варианта осуществления отправляющего устройства согласно другому варианту осуществления изобретения; и

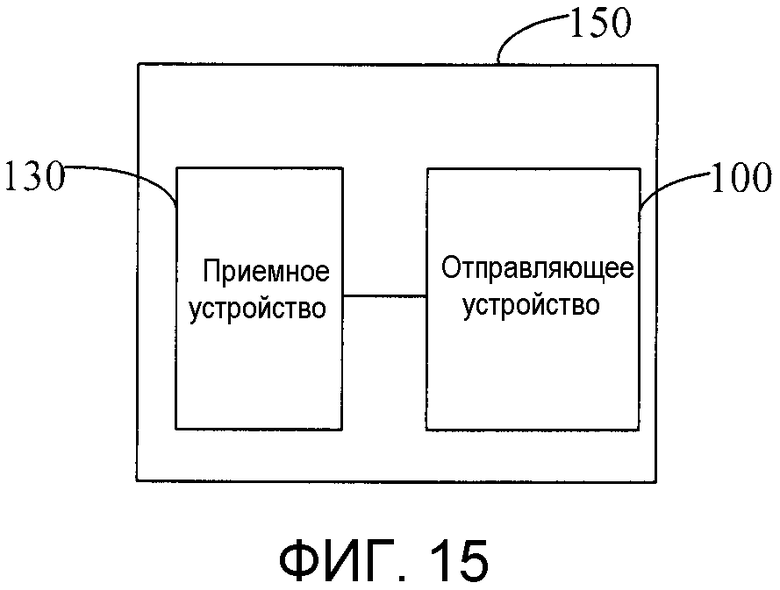

[0036] Фиг. 15 является принципиальной структурной схемой варианта осуществления системы связи согласно варианту осуществления изобретения.

ПОДРОБНОЕ ОПИСАНИЕ ВАРИАНТОВ ОСУЩЕСТВЛЕНИЯ

[0037] Чтобы обеспечивать большую понятность целей, технических решений и преимуществ вариантов осуществления изобретения, далее четко описываются технические решения в вариантах осуществления изобретения со ссылкой на прилагаемые чертежи в вариантах осуществления изобретения. Очевидно, что описанные варианты осуществления представляют собой часть, а не все варианты осуществления изобретения. Все другие варианты осуществления, полученные специалистами в данной области техники на основе вариантов осуществления изобретения без творческих усилий, должны попадать в объем охраны изобретения.

[0038] В системе связи на основе беспроводной персональной вычислительной сети (беспроводной персональной вычислительной сети, WPAN) на 60 ГГц мощность, потребляемая посредством микросхем в ходе прослушивания в состоянии бездействия, является высокой, и мощность, потребляемая посредством некоторых микросхем в ходе прослушивания в состоянии бездействия, составляет приблизительно вплоть до 2 Вт, что существенно ограничивает рыночное позиционирование и объем применения для 60 ГГц.

[0039] На приемной стороне приемное устройство может сначала дискретизировать принимаемый аналоговый сигнал посредством использования аналого-цифрового преобразователя (аналого-цифрового преобразователя, ADC), чтобы получать цифровой сигнал, и затем выполнять обработку в полосе модулирующих частот и на уровне управления доступом к среде (управления доступом к среде, MAC) для цифрового сигнала.

[0040] В потреблении мощности, которое возникает в ходе прослушивания в состоянии бездействия и в WPAN на 60 ГГц, потребление рабочей мощности ADC по технологии на основе мультигигабит выборок в секунду (Multi-Gsps) составляет приблизительно 50%, и в системе мультиплексирования с ортогональным частотным разделением каналов (OFDM) с модуляцией высшего порядка, потребление мощности ADC составляет большую пропорцию. Важный индикатор для оценки производительности преобразования ADC представляет собой показатель качества (показатель качества, FOM), и формула вычисления FOM следующая:

,

,

где  является потреблением мощности,

является потреблением мощности,  является эффективной битовой шириной дискретизации,

является эффективной битовой шириной дискретизации,  является частотой дискретизации, и

является частотой дискретизации, и  представляет варьирование в пикоджоулях в расчете на символ.

представляет варьирование в пикоджоулях в расчете на символ.

[0041] В случае если FOM предположительно является фиксированным, предусмотрено два способа для того, чтобы уменьшать потребление мощности ADC. Один способ заключается в том, чтобы уменьшать частоту  дискретизации ADC, но в ADC по технологии Multi-Gsps, реализация, в общем, должна выполняться посредством использования процесса на глубоком подмикронном уровне, при котором потребление мощности аналоговой подсистемы составляет более 50%, следовательно, преимущество решения, которое реализуется только посредством уменьшения частоты дискретизации ADC, ограничено, и чрезмерно низкая частота дискретизации сильно влияет на производительность обнаружения всего принимаемого кадра. Другой способ заключается в том, чтобы уменьшать эффективную битовую ширину ENOB дискретизации ADC, и по мере того, как снижается ENOB, эффективность FOM-преобразования значительно увеличивается; когда FOM является фиксированным, после того, как ENOB уменьшается, потребление мощности также уменьшается.

дискретизации ADC, но в ADC по технологии Multi-Gsps, реализация, в общем, должна выполняться посредством использования процесса на глубоком подмикронном уровне, при котором потребление мощности аналоговой подсистемы составляет более 50%, следовательно, преимущество решения, которое реализуется только посредством уменьшения частоты дискретизации ADC, ограничено, и чрезмерно низкая частота дискретизации сильно влияет на производительность обнаружения всего принимаемого кадра. Другой способ заключается в том, чтобы уменьшать эффективную битовую ширину ENOB дискретизации ADC, и по мере того, как снижается ENOB, эффективность FOM-преобразования значительно увеличивается; когда FOM является фиксированным, после того, как ENOB уменьшается, потребление мощности также уменьшается.

[0042] Следовательно, варианты осуществления изобретения уменьшают ENOB в ходе прослушивания в состоянии бездействия, с тем чтобы уменьшать потребление мощности.

[0043] Фиг. 1 является блок-схемой последовательности операций способа для обработки данных в ходе прослушивания в состоянии бездействия согласно варианту осуществления изобретения, причем способ включает в себя:

[0044] 11: Приемное устройство дискретизирует, в режиме прослушивания в состоянии бездействия, первый аналоговый сигнал посредством использования N-битового ADC.

[0045] 12: Приемное устройство дискретизирует, в режиме приемо-передачи, второй аналоговый сигнал посредством использования M-битового ADC.

[0046] N и M являются целыми числами, и N меньше M.

[0047] Вышеприведенные N-битовый ADC и M-битовый ADC указывают то, что эффективные битовые ширины дискретизации ADC отдельно составляют N и M.

[0048] Вышеприведенное M является эффективной битовой шириной дискретизации, требуемой посредством ADC, когда данные принимаются или отправляются обычно, и, в общем, является значением, большим 1, например, любым значением в пределах 6-12. В предшествующем уровне техники аналоговый сигнал дискретизирован посредством использования M-битового ADC независимо от того, в ходе обычного приема или отправки данных или в ходе прослушивания в состоянии бездействия.

[0049] Тем не менее, в варианте осуществления изобретения, чтобы уменьшать потребление мощности в ходе прослушивания в состоянии бездействия, значение M уменьшается, и, как описано выше, N-битовый ADC выполнен с возможностью дискретизировать аналоговый сигнал, где N меньше M. Таким образом, когда FOM и частота дискретизации являются фиксированными, по сравнению с потреблением мощности исходной M-битовой дискретизации, потребление мощности, вызываемое посредством N-битовой дискретизации, используемой в варианте осуществления, является эквивалентным только  от исходного потребления мощности.

от исходного потребления мощности.

[0050] Соответственно процедура на отправляющей стороне, предоставленной на фиг. 2, включает в себя:

[0051] 21: Отправляющее устройство формирует последовательность данных и выполняет цифроаналоговое преобразование для последовательности данных для того, чтобы получать аналоговые сигналы, причем аналоговые сигналы включают в себя первый аналоговый сигнал и второй аналоговый сигнал.

[0052] 22: Отправляющее устройство отправляет аналоговые сигналы в приемное устройство, так что приемное устройство дискретизирует, в режиме прослушивания в состоянии бездействия, первый аналоговый сигнал посредством использования N-битового ADC и дискретизирует, в режиме приемо-передачи, второй аналоговый сигнал посредством использования M-битового ADC.

[0053] На вышеприведенных этапах N и M являются целыми числами, и N меньше M.

[0054] В варианте осуществления эффективная битовая ширина дискретизации уменьшается в ходе прослушивания в состоянии бездействия, так что потребление мощности может уменьшаться, когда производительность ADC является фиксированной.

[0055] Выше предоставлен вариант осуществления, в котором N меньше M, минимальное значение N равно 1, и, следовательно, в способе реализации, N равен 1. Ссылаясь на фиг. 3, предоставляется принципиальная структурная схема приемного устройства на 60 ГГц, и приемное устройство включает в себя кварцевый генератор 31, синтезатор 32 частот, усилитель 33, смеситель 34 частот, гибридный ADC 35, процессор 36 в полосе модулирующих частот и на уровне MAC и контур 37 фазовой синхронизации (контур фазовой синхронизации, PLL). Кварцевый генератор 31 выполнен с возможностью формировать тактовую частоту; синтезатор 32 частот выполнен с возможностью осуществлять синтетическую обработку для сформированной тактовой частоты, чтобы получать требуемую синтезируемую частоту; усилитель 33 выполнен с возможностью осуществлять обработку усиления для аналогового сигнала, принимаемого посредством радиочастотной подсистемы; смеситель 34 частот выполнен с возможностью осуществлять обработку преобразования с понижением частоты для усиленного аналогового сигнала; гибридный ADC 35 выполнен с возможностью дискретизировать аналоговый сигнал, который получается после обработки преобразования с понижением частоты, чтобы получать цифровой сигнал; процессор 36 в полосе модулирующих частот и на уровне MAC выполнен с возможностью осуществлять обработку в полосе модулирующих частот для цифрового сигнала и выводить сигнал в главный процессор; PLL 37 выполнен с возможностью осуществлять обработку фазовой синхронизации для сигналов из гибридного ADC 35 и процессора 36 в полосе модулирующих частот и на уровне MAC.

[0056] В предшествующем уровне техники, когда дискретизация выполняется, дискретизация выполняется посредством использования M-битового ADC независимо от того, в режиме приемо-передачи или в режиме прослушивания в состоянии бездействия. В отличие от предшествующего уровня техники, в варианте осуществления: в режиме приемо-передачи M-битовая дискретизация выполняется с тем, чтобы обеспечивать то, что данные, включающие в себя достоверную информацию, дискретизируются; в режиме прослушивания в состоянии бездействия дискретизация выполняется посредством использования 1-битового ADC, с тем чтобы уменьшать потребление мощности в ходе прослушивания в состоянии бездействия. Иными словами, гибридный ADC 35 включает в себя 1-битовый ADC и M-битовый ADC, причем 1-битовый ADC работает в ходе прослушивания в состоянии бездействия, а M-битовый ADC работает в режиме приемо-передачи.

[0057] Переключение выполняется между ADC для различных битов, приемное устройство должно узнавать, когда выполнять переключение. В варианте осуществления изобретения, когда приемное устройство в ходе прослушивания в состоянии бездействия получает последовательность данных посредством использования дискретизации на основе 1-битового ADC, определяется то, представляет собой или нет последовательность данных заданную последовательность данных; и когда последовательность данных представляет собой заданную последовательность данных, выполняется переключение с 1-битового ADC на M-битовый ADC, а когда последовательность данных не является заданной последовательностью данных, дискретизация по-прежнему выполняется посредством использования 1-битового ADC.

[0058] Фиг. 4 является блок-схемой последовательности операций способа для обработки данных в ходе прослушивания в состоянии бездействия согласно другому варианту осуществления изобретения, причем способ включает в себя:

[0059] 41: Отправляющее устройство формирует последовательность данных, причем последовательность данных включает в себя:

- заданную последовательность данных, избыточный бит и данные в стандартной структуре кадра.

[0060] В изобретении последовательность данных, сформированная посредством отправляющего устройства, т.е. кадр данных, используемый для связи, представляет собой улучшенную последовательность данных на основе существующей структуры кадра связи на 60 ГГц и в дополнение к данным в существующей стандартной структуре кадра дополнительно включает в себя заданную последовательность данных и избыточный бит, как конкретно показано на фиг. 5.

[0061] Заданная последовательность данных представлена посредством m-преамбулы (m-преамбулы), и избыточный бит представлен посредством фиктивного бита. Данные в стандартной структуре кадра могут представлять собой пакет данных по стандарту 802.11ad, включающий в себя преамбулу по стандарту 802.11ad (преамбулу по стандарту 802.11ad) и данные по стандарту 802.11ad (данные по стандарту 802.11ad).

[0062] Опционально, заданная последовательность данных может включать в себя: m-последовательность, которая повторяется r раз, причем длина каждой m-последовательности составляет L битов, и значения r и L могут задаваться, например, r=3 и L=127.

[0063] Опционально избыточный бит может составлять n фиктивных битов (фиктивный бит), где n также является заданным значением и может задаваться согласно времени, требуемому для ADC-переключения, и, например, время, занимаемое посредством n фиктивных битов, больше или равно времени, требуемому для переключения с N-битового ADC на M-битовый ADC, с тем чтобы обеспечивать то, что данные, которые находятся в стандартной структуре кадра и идут после избыточного бита, дискретизированы посредством использования M-битового ADC.

[0064] Помимо этого, приемное устройство выполняет дискретизацию посредством использования 1-битового ADC в ходе прослушивания в состоянии бездействия, и информация фазы двух каналов, синфазного компонента (синфазной составляющей, I-канала) и квадратурного компонента (квадратурной составляющей, Q-канала), отбрасывается, так что отправляющее устройство может отправлять идентичную заданную последовательность данных в I-канале и Q-канале. В этом случае последовательность данных, принимаемая посредством приемного устройства, может быть представлена следующим образом:

,

,

где  является последовательностью данных, принимаемой посредством приемного устройства, I-канал и Q-канала принимают

является последовательностью данных, принимаемой посредством приемного устройства, I-канал и Q-канала принимают  ; в примере, в котором предварительно определенная последовательность данных, отправленная посредством отправляющего устройства, является m-последовательностью, c(n) представляет m-последовательность, отправленную посредством отправляющего устройства, w(n) представляет случайный шум, A является амплитудой принимаемого сигнала,

; в примере, в котором предварительно определенная последовательность данных, отправленная посредством отправляющего устройства, является m-последовательностью, c(n) представляет m-последовательность, отправленную посредством отправляющего устройства, w(n) представляет случайный шум, A является амплитудой принимаемого сигнала,  является отклонением частоты между приемной стороной и отправляющей стороной, T является периодом элемента кода,

является отклонением частоты между приемной стороной и отправляющей стороной, T является периодом элемента кода,  является случайной фазой между приемной стороной и отправляющей стороной; H0 представляет случай, в котором сигналы не принимаются, и H1 представляет случай, в котором m-преамбула принимается. В H0-случае приемное устройство принимает только случайный шум в двух каналах: I-канале и Q-канале; в H1-случае предусмотрен чрезвычайно сильный основной тракт при 60 ГГц, и m-последовательность имеет очень желательное свойство автокорреляции, так что воздействие из неосновных трактов здесь игнорируется, и их энергия также трактуется в качестве случайного шума; real(x) представляет действительную часть комплексного числа x, image(x) представляет мнимую часть комплексного числа x, и sgn(x) представляет символьное вычисление, выполняемое для x.

является случайной фазой между приемной стороной и отправляющей стороной; H0 представляет случай, в котором сигналы не принимаются, и H1 представляет случай, в котором m-преамбула принимается. В H0-случае приемное устройство принимает только случайный шум в двух каналах: I-канале и Q-канале; в H1-случае предусмотрен чрезвычайно сильный основной тракт при 60 ГГц, и m-последовательность имеет очень желательное свойство автокорреляции, так что воздействие из неосновных трактов здесь игнорируется, и их энергия также трактуется в качестве случайного шума; real(x) представляет действительную часть комплексного числа x, image(x) представляет мнимую часть комплексного числа x, и sgn(x) представляет символьное вычисление, выполняемое для x.

[0065] 42: Отправляющее устройство выполняет цифроаналоговое преобразование для последовательности данных и отправляет последовательность данных, которая получается после цифро-аналогового преобразования, в приемное устройство.

[0066] 43: Приемное устройство дискретизирует в ходе прослушивания в состоянии бездействия принимаемый аналоговый сигнал посредством использования 1-битового ADC для того, чтобы получать последовательность данных и выполнять обработку.

[0067] Например, ссылаясь на фиг. 3, в гибридном ADC, 1-битовый ADC соединен, а M-битовый ADC отсоединен.

[0068] 44: При обнаружении заданной последовательности данных приемное устройство переключается с 1-битового ADC на M-битовый ADC и дискретизирует принимаемый аналоговый сигнал посредством использования M-битового ADC для того, чтобы получать последовательность данных и выполнять обработку.

[0069] Опционально может быть определено способом обнаружения энергии, то, обнаруживается или нет заданная последовательность данных, например, могут задаваться различные последовательности данных, и энергия различных последовательностей данных отличается, даже если длины различных последовательностей данных являются идентичными, так что обнаружение может выполняться согласно энергии.

[0070] Формула вычисления для обнаружения энергии может быть следующей:

,

,

где  является результатом обнаружения энергии,

является результатом обнаружения энергии,  являются дискретизированными значениями в I-канале и Q-канале отдельно,

являются дискретизированными значениями в I-канале и Q-канале отдельно, являются заданными выигрышами при обработке I-канала и Q-канала отдельно,

являются заданными выигрышами при обработке I-канала и Q-канала отдельно,  является первой точкой дискретизации,

является первой точкой дискретизации,  является длиной каждой m-последовательности, и

является длиной каждой m-последовательности, и  представляет операцию вычисления суммы квадратов.

представляет операцию вычисления суммы квадратов.

[0071] Вышеприведенное обнаружение энергии может реализовываться посредством процессора в полосе модулирующих частот и на уровне MAC на фиг. 3, и при получении,  является заданным значением энергии, т.е. значение энергии является значением энергии заданной последовательности данных, это может указывать то, что обнаруживается заданная последовательность данных. Затем процессор в полосе модулирующих частот и на уровне MAC может отправлять инициирующий сигнал, причем инициирующий сигнал может управлять переключением для того, чтобы переключаться с 1-битового ADC на M-битовый ADC, с тем чтобы реализовывать M-битовую дискретизацию.

является заданным значением энергии, т.е. значение энергии является значением энергии заданной последовательности данных, это может указывать то, что обнаруживается заданная последовательность данных. Затем процессор в полосе модулирующих частот и на уровне MAC может отправлять инициирующий сигнал, причем инициирующий сигнал может управлять переключением для того, чтобы переключаться с 1-битового ADC на M-битовый ADC, с тем чтобы реализовывать M-битовую дискретизацию.

[0072] После этого, когда приемное устройство возвращается к прослушиванию в состоянии бездействия, может выполняться переключение с M-битового ADC обратно на 1-битовый ADC. Фиг. 6 и 7 показывают принципиальные схемы рабочих режимов приемной стороны и отправляющей стороны, соответственно, после вышеприведенной обработки, 1-битовый ADC может использоваться в ходе прослушивания в состоянии бездействия, а M-битовый ADC может использоваться в ходе обычного приема или отправки данных.

[0073] Далее представлен результат моделирования, причем условия моделирования включают в себя: длина m-последовательности L=127, число циклов r=3 и канал конференц-зала по стандарту IEEE 802.11ad используется для того, чтобы выполнять моделирование. В ходе моделирования считается, что начальные фазы приемной стороны и стороны отправки являются произвольными, и отклонение частоты в  возникает как на приемной стороне, так и на отправляющей стороне.

возникает как на приемной стороне, так и на отправляющей стороне.

[0074] Фиг. 8 является принципиальной схемой производительности в отношении вероятности пропущенного обнаружения для дискретизации на основе 1-битового ADC и традиционных технологий согласно варианту осуществления изобретения, причем традиционные технологии представляют собой отдельное неколичественное обнаружение и обнаружение энергии, и неколичественное обнаружение представляет собой алгоритм обнаружения, который в настоящее время имеет оптимальную производительность в отношении вероятности пропущенного обнаружения для 1-битового обнаружения. В случае если обеспечивается то, что вероятность сигнала ложной тревоги удовлетворяет  , как показано на фиг. 8, когда отношение "сигнал-шум" (SNR)>-4,3 дБ, вероятность пропущенного обнаружения удовлетворяет

, как показано на фиг. 8, когда отношение "сигнал-шум" (SNR)>-4,3 дБ, вероятность пропущенного обнаружения удовлетворяет  . Когда

. Когда  , по сравнению с алгоритмом неколичественного обнаружения потеряны только 1,4 дБ, и по сравнению с алгоритмом обнаружения энергии, который первоначально использован, достигается увеличение в 3,0 дБ. Следовательно, можно видеть, что лучшая производительность в отношении пропущенного обнаружения может достигаться посредством использования дискретизации на основе 1-битового ADC согласно варианту осуществления изобретения.

, по сравнению с алгоритмом неколичественного обнаружения потеряны только 1,4 дБ, и по сравнению с алгоритмом обнаружения энергии, который первоначально использован, достигается увеличение в 3,0 дБ. Следовательно, можно видеть, что лучшая производительность в отношении пропущенного обнаружения может достигаться посредством использования дискретизации на основе 1-битового ADC согласно варианту осуществления изобретения.

[0075] Фиг. 9 является принципиальной схемой потребления мощности, которое возникает в ходе прослушивания в состоянии бездействия и обусловлено дискретизацией на основе 1-битового ADC и традиционной технологией, согласно варианту осуществления изобретения, в котором предполагается, что FOM=1,5 пДж/conv, и потребление мощности радиочастотного внешнего интерфейса составляет 1 Вт. Из фиг. 9 можно видеть то, что в сравнении с традиционной технологией используется 6-битовый ADC, потребление мощности, которое возникает в ходе прослушивания в состоянии бездействия и обусловлено 1-битовым ADC по варианту осуществления изобретения, уменьшается приблизительно на 47,5%. Следовательно, существенное уменьшение потребления мощности, которое возникает в ходе прослушивания в состоянии бездействия, и повышение производительности достигаются за счет небольших затрат на аппаратные средства.

[0076] Согласно варианту осуществления изобретения, на основе существующей структуры кадра, m-преамбула и избыточный бит добавляются для структуры кадра прослушивания в состоянии бездействия, так что приемная сторона точно выполняет ADC-переключение; гибридный ADC может использовать, в обычном режиме, существующий M-битовый ADC и предоставлять возможность, в режиме прослушивания в состоянии бездействия, 1-битовому ADC уменьшать потребление мощности в ходе прослушивания в состоянии бездействия; два канала, I и Q, отправляют идентичную m-преамбулу, и, следовательно, высокопроизводительное обнаружение поступления кадров может выполняться в случае, если информация фазы дискретизации на основе 1-битового ADC в двух каналах, I и Q, является неизвестной.

[0077] Фиг. 10 является принципиальной структурной схемой приемного устройства согласно изобретению. Приемное устройство 100 включает в себя первый блок 101 дискретизации и второй блок 102 дискретизации; первый блок 101 дискретизации выполнен с возможностью дискретизировать, в режиме прослушивания в состоянии бездействия, первый аналоговый сигнал посредством использования N-битового ADC; второй блок 102 дискретизации выполнен с возможностью дискретизировать, в режиме приемо-передачи, второй аналоговый сигнал посредством использования M-битового ADC, где N и M являются целыми числами, и N меньше M.

[0078] Опционально N равен 1.

[0079] Опционально, как показано на Фиг. 11, приемное устройство дополнительно включает в себя процессор 103, выполненный с возможностью определять то, представляет собой или нет первая последовательность данных заданную последовательность данных; второй блок 102 дискретизации, в частности, выполнен с возможностью дискретизировать, когда процессор 103 определяет то, что первая последовательность данных представляет собой заданную последовательность данных, второй аналоговый сигнал посредством использования M-битового ADC для того, чтобы получать вторую последовательность данных.

[0080] Опционально процессор 103, в частности, выполнен с возможностью сравнивать значение энергии первой последовательности данных со значением энергии заданной последовательности данных; если два значения энергии являются идентичными, определять то, что первая последовательность данных представляет собой заданную последовательность данных; и если два значения энергии не являются идентичными, определять то, что первая последовательность данных не представляет собой заданную последовательность данных.

[0081] Опционально вторая последовательность данных включает в себя: данные в стандартной структуре кадра; разность времен между первой последовательностью данных и второй последовательностью данных является временем, занимаемым посредством избыточного бита.

[0082] Опционально заданная последовательность данных включает в себя m-последовательность с r циклов, причем длина каждой m-последовательности составляет L, r и L представляют собой заданные значения.

[0083] Опционально время, занимаемое посредством избыточного бита, превышает или равно времени, требуемому для переключения с N-битового ADC на M-битовый ADC.

[0084] Вышеприведенные первый блок дискретизации и второй блок дискретизации могут формировать гибридный ADC, показанный на фиг. 3, и процессор может быть расположен в процессоре в полосе модулирующих частот и на уровне MAC на фиг. 3.

[0085] Иными словами, как показано на фиг. 12, изобретение дополнительно может предоставлять приемное устройство 120. Приемное устройство 120 включает в себя гибридный ADC 121, и гибридный ADC 121 выполнен с возможностью дискретизировать, в режиме прослушивания в состоянии бездействия, первый аналоговый сигнал посредством использования N-битового ADC и дискретизировать, в режиме приемо-передачи, второй аналоговый сигнал посредством использования M-битового ADC, где N и M являются целыми числами, и N меньше M.

[0086] Опционально N равен 1.

[0087] Опционально приемное устройство дополнительно может включать в себя процессор 122 в полосе модулирующих частот и на уровне MAC, выполненный с возможностью определять то, представляет собой или нет первая последовательность данных, полученная посредством дискретизации первого аналогового сигнала посредством использования N-битового ADC, заданную последовательность данных.

[0088] Гибридный ADC 121, в частности, выполнен с возможностью дискретизировать, когда процессор 122 в полосе модулирующих частот и на уровне MAC определяет то, что первая последовательность данных, полученная посредством дискретизации, представляет собой заданную последовательность данных, второй аналоговый сигнал посредством использования M-битового ADC для того, чтобы получать вторую последовательность данных.

[0089] Опционально процессор 122 в полосе модулирующих частот и на уровне MAC, в частности, выполнен с возможностью определять, когда значение энергии первой последовательности данных является идентичным значению энергии заданной последовательности данных, то, что первая последовательность данных, полученная посредством дискретизации, является идентичной заданной последовательности данных.

[0090] Опционально заданная последовательность данных включает в себя m-последовательность с r циклов, причем длина каждой m-последовательности составляет L, r и L представляют собой заданные значения;

- вторая последовательность данных включает в себя: данные в стандартной структуре кадра; и разность времен между первой последовательностью данных и второй последовательностью данных является временем, занимаемым посредством избыточного бита, и время, занимаемое посредством избыточного бита, превышает или равно времени, требуемому для переключения с N-битового ADC на M-битовый ADC.

[0091] Согласно варианту осуществления эффективная битовая ширина дискретизации ADC, которая используется в ходе прослушивания в состоянии бездействия, составляет N, что меньше эффективной битовой ширины M дискретизации в режиме приемо-передачи; когда коэффициент полезного действия является фиксированным, потребление мощности является прямо пропорциональным эффективной битовой ширине дискретизации, так что когда эффективная битовая ширина дискретизации уменьшается, потребление мощности также уменьшается, и, следовательно, использование небольшой эффективной битовой ширины дискретизации позволяет уменьшать потребление мощности в ходе прослушивания в состоянии бездействия, когда ADC-производительность является фиксированной.

[0092] Фиг. 13 является принципиальной структурной схемой отправляющего устройства согласно изобретению. Отправляющее устройство 130 включает в себя процессор 131 и блок 132 отправки; процессор 131 выполнен с возможностью формировать последовательность данных и выполнять цифроаналоговое преобразование для последовательности данных для того, чтобы получать аналоговые сигналы, причем аналоговые сигналы включают в себя первый аналоговый сигнал и второй аналоговый сигнал; блок 132 отправки выполнен с возможностью отправлять аналоговые сигналы в приемное устройство, так что приемное устройство дискретизирует, в режиме прослушивания в состоянии бездействия, первый аналоговый сигнал посредством использования N-битового ADC и дискретизирует, в режиме приемо-передачи, второй аналоговый сигнал посредством использования M-битового ADC, где N и M являются целыми числами, и N меньше M.

[0093] Опционально последовательность данных включает в себя заданную последовательность данных, избыточный бит и данные в стандартной структуре кадра.

[0094] Опционально заданная последовательность данных включает в себя m-последовательность с r циклов, причем длина каждой m-последовательности составляет L, и r и L представляют собой заданные значения.

[0095] Опционально время, занимаемое посредством избыточного бита, превышает или равно времени, требуемому для переключения с N-битового ADC на M-битовый ADC.

[0096] Опционально первый аналоговый сигнал представляет собой аналоговый сигнал, получаемый после того, как цифроаналоговое преобразование выполняется для заданной последовательности данных, и второй аналоговый сигнал представляет собой аналоговый сигнал, получаемый после того, как цифроаналоговое преобразование выполняется для данных в стандартной структуре кадра.

[0097] Помимо этого, как показано на фиг. 14, изобретение предоставляет другое отправляющее устройство. Отправляющее устройство 140 включает в себя процессор 141 и модуль 142 отправки; процессор 141 выполнен с возможностью формировать последовательность данных и выполнять цифроаналоговое преобразование для последовательности данных для того, чтобы получать аналоговые сигналы, причем аналоговые сигналы включают в себя первый аналоговый сигнал и второй аналоговый сигнал; модуль 142 отправки выполнен с возможностью отправлять аналоговый сигнал в приемное устройство, так что приемное устройство дискретизирует, в режиме прослушивания в состоянии бездействия, первый аналоговый сигнал посредством использования N-битового ADC и дискретизирует, в режиме приемо-передачи, второй аналоговый сигнал посредством использования M-битового ADC, где N и M являются целыми числами, и N меньше M.

[0098] Опционально последовательность данных включает в себя:

- заданную последовательность данных, избыточный бит и данные в стандартной структуре кадра, причем заданная последовательность данных включает в себя m-последовательность с r циклов, длина каждой m-последовательности составляет L, r и L представляют собой заданные значения, и время, занимаемое посредством избыточного бита, превышает или равно времени, требуемому для переключения с N-битового ADC на M-битовый ADC.

[0099] Опционально первый аналоговый сигнал представляет собой аналоговый сигнал, получаемый после того, как цифроаналоговое преобразование выполняется для заданной последовательности данных, и второй аналоговый сигнал представляет собой аналоговый сигнал, получаемый после того, как цифроаналоговое преобразование выполняется для данных в стандартной структуре кадра.

[0100] Процессор по варианту осуществления, в частности, может представлять собой процессор общего назначения, процессор цифровых сигналов (DSP), специализированную интегральную схему (ASIC), программируемую пользователем вентильную матрицу (FPGA) или другое программируемое логическое устройство, дискретный логический элемент или устройство на транзисторной логике либо дискретный аппаратный узел. Процессор общего назначения может представлять собой микропроцессор или любой традиционный процессор.

[0101] Вышеприведенный модуль отправки может реализовываться посредством использования антенны, причем антенна может представлять собой линейную антенну, рамочную антенну, антенную решетку и т.п.

[0102] Помимо этого, вариант осуществления дополнительно может включать в себя запоминающее устройство, шину и т.п.

[0103] Согласно варианту осуществления изобретения использование ADC с небольшой эффективной битовой шириной дискретизации для того, чтобы выполнять дискретизацию в ходе прослушивания в состоянии бездействия, позволяет уменьшать потребление мощности в ходе прослушивания в состоянии бездействия, когда ADC-производительность является фиксированной.

[0104] Фиг. 15 является принципиальной структурной схемой варианта осуществления системы связи согласно изобретению, система 150 включает в себя отправляющее устройство 130 и приемное устройство 100, и структуры и функции отправляющего устройства 130 и приемного устройства 100 представляют собой структуры и функции, описанные в вышеприведенных вариантах осуществления, и не повторяются в данном документе. Альтернативно система также может включать в себя отправляющее устройство 140 и приемное устройство 120, и структуры и функции отправляющего устройства 140 и приемного устройства 120 представляют собой структуры и функции, описанные в вышеприведенных вариантах осуществления, и не повторяются в данном документе. Следует понимать, что в целях упрощения фиг. 15 предоставляет только случай, в котором система 150 включает в себя отправляющее устройство 130 и приемное устройство 100.

[0105] Согласно варианту осуществления эффективная битовая ширина дискретизации ADC, которая используется в ходе прослушивания в состоянии бездействия, составляет N, что меньше эффективной битовой ширины M дискретизации в режиме приемо-передачи; когда коэффициент полезного действия является фиксированным, потребление мощности является прямо пропорциональным эффективной битовой ширине дискретизации, так что когда эффективная битовая ширина дискретизации уменьшается, потребление мощности также уменьшается, и, следовательно, использование небольшой эффективной битовой ширины дискретизации позволяет уменьшать потребление мощности в ходе прослушивания в состоянии бездействия, когда ADC-производительность является фиксированной.

[0106] Специалисты в данной области техники могут четко понимать, что для удобного и краткого описания,разделение вышеприведенных функциональных модулей рассматривается в качестве примера для иллюстрации. При фактическом применении вышеприведенные функции могут выделяться различным функциональным модулям и реализовываться требуемым образом, т.е. внутренняя структура устройства разделяется на различные функциональные модули, чтобы реализовывать все или часть функций, описанных выше. На предмет подробного рабочего процесса вышеприведенной системы, устройства и блока, следует обратиться к соответствующему процессу в вышеприведенных вариантах осуществления способа, и подробности не описываются повторно в данном документе.

[0107] В нескольких вариантах осуществления, предоставленных в настоящей заявке, следует понимать, что раскрытая система, устройство и способ могут быть реализованы другими способами. Например, описанный вариант осуществления устройства является просто примерным. Например, разделение на модули или блоки является просто разделением по логическим функциям и может быть другим разделением в фактической реализации. Например, множество блоков или компонентов могут быть комбинированы или интегрированы в другую систему, либо некоторые признаки могут игнорироваться или не выполняться. Помимо этого, отображенные или поясненные взаимные связи либо прямые связи, либо подключения связи могут быть реализованы посредством некоторых интерфейсов. Косвенные связи или подключения связи между устройствами или блоками могут быть реализованы в электронных, механических или других формах.

[0108] Блоки, описанные в качестве отдельных частей, могут быть или не быть физически отдельными, и части, отображаемые в качестве блоков, могут быть или не быть физическими блоками, могут быть расположены в одной позиции либо могут быть распределены по множеству сетевых блоков. Часть или все из блоков могут быть выбраны согласно фактической необходимости для достижения целей решений вариантов осуществления.

[0109] Помимо этого, функциональные блоки в вариантах осуществления настоящей заявки могут быть интегрированы в один процессор, либо каждый из блоков может существовать отдельно физически, либо два или более блоков интегрируются в один блок. Интегрированный блок может быть реализован в форме аппаратных средств или может быть реализован в форме программного функционального блока.

[0110] Когда интегрированный блок реализован в форме программного функционального блока и продается либо используется в качестве независимого продукта, интегрированный блок может быть сохранен на машиночитаемом носителе хранения данных. На основе такого понимания технические решения настоящей заявки по существу или их часть, вносящая усовершенствование в предшествующий уровень техники, либо часть технических решений могут быть реализованы в форме программного продукта. Программный продукт сохраняется на носителе хранения данных и включает в себя несколько инструкций для инструктирования компьютерному устройству (которое может представлять собой персональный компьютер, сервер или сетевое устройство) выполнять все или часть этапов способов, описанных в вариантах осуществления настоящей заявки. Вышеуказанный носитель хранения данных включает в себя любой носитель, который может сохранять программный код, к примеру USB-флэш-накопитель, съемный жесткий диск, постоянное запоминающее устройство (ROM, постоянное запоминающее устройство), оперативное запоминающее устройство (RAM, оперативное запоминающее устройство), магнитный диск или оптический диск.

[0111] Вышеприведенные варианты осуществления предназначаются просто для описания технических решений настоящей заявки, а не для ограничения настоящей заявки. Хотя настоящая заявка подробно описывается со ссылкой на вышеприведенные варианты осуществления, специалисты в данной области техники должны понимать, что они по-прежнему могут вносить модификации в техническое решения, описанные в вышеприведенных вариантах осуществления, или выполнять эквивалентные замены некоторых их технических признаков, без отступления от сущности и объема технических решений вариантов осуществления настоящей заявки.

Изобретение относится к технологиям связи, в частности к способу, устройству и системе для обработки данных в ходе прослушивания в состоянии бездействия. Способ включает в себя дискретизацию, в режиме прослушивания в состоянии бездействия, первого аналогового сигнала посредством использования N-битового ADC и дискретизацию, в режиме приемо-передачи, второго аналогового сигнала посредством использования M-битового ADC, где N и M являются целыми числами, и N меньше M. Варианты осуществления изобретения позволяют уменьшать потребление мощности ADC в ходе прослушивания в состоянии бездействия. 3 н. и 10 з.п. ф-лы, 15 ил.

1. Способ обработки данных в ходе прослушивания в состоянии бездействия, содержащий этапы, на которых:

- дискретизируют, в режиме прослушивания в состоянии бездействия, первый аналоговый сигнал посредством использования N-битового аналого-цифрового преобразователя ADC; и

- дискретизируют, в режиме приемо-передачи, второй аналоговый сигнал посредством использования M-битового ADC, при этом:

- N и M являются целыми числами, и N меньше M.

2. Способ по п. 1, в котором N равен 1.

3. Способ по п. 1, в котором первая последовательность данных получается посредством дискретизации первого аналогового сигнала посредством использования N-битового ADC, причем способ дополнительно содержит этап, на котором:

- определяют то, представляет ли собой первая последовательность данных заданную последовательность данных; и

- дискретизация, в режиме приемо-передачи, второго аналогового сигнала посредством использования M-битового ADC содержит этап, на котором:

- когда первая последовательность данных представляет собой заданную последовательность данных, дискретизируют второй аналоговый сигнал посредством использования M-битового ADC для того, чтобы получать вторую последовательность данных.

4. Способ по п. 3, в котором определение того, представляет ли собой первая последовательность данных заданную последовательность данных, содержит этап, на котором:

- сравнивают значение энергии первой последовательности данных со значением энергии заданной последовательности данных; если значение энергии первой последовательности данных является идентичным со значением энергии заданной последовательности данных, первая последовательность данных представляет собой заданную последовательность данных.

5. Способ по п. 3, в котором:

- заданная последовательность данных содержит: m-последовательность с r циклов, при этом длина каждой m-последовательности составляет L, r и L представляют собой заданные значения;

- вторая последовательность данных содержит: данные в стандартной структуре кадра; и

- разность времен между первой последовательностью данных и второй последовательностью данных является временем, занимаемым посредством избыточного бита, и время, занимаемое посредством избыточного бита, превышает или равно времени, требуемому для переключения с N-битового ADC на M-битовый ADC.

6. Приемное устройство, содержащее:

- первый блок дискретизации, выполненный с возможностью дискретизировать, в режиме прослушивания в состоянии бездействия, первый аналоговый сигнал посредством использования N-битового аналого-цифрового преобразователя ADC; и

- второй блок дискретизации, выполненный с возможностью дискретизировать, в режиме приемо-передачи, второй аналоговый сигнал посредством использования M-битового ADC, при этом:

- N и M являются целыми числами, и N меньше M.

7. Устройство по п. 6, при этом устройство дополнительно содержит:

- процессор, выполненный с возможностью определять то, представляет ли собой первая последовательность данных заданную последовательность данных; и

- второй блок дискретизации выполнен с возможностью дискретизировать, когда процессор определяет то, что первая последовательность данных представляет собой заданную последовательность данных, второй аналоговый сигнал посредством использования M-битового ADC для того, чтобы получать вторую последовательность данных.

8. Устройство по п. 7, в котором процессор, в частности, выполнен с возможностью:

- сравнивать значение энергии первой последовательности данных со значением энергии заданной последовательности данных; если значение энергии первой последовательности данных является идентичным со значением энергии заданной последовательности данных, определять то, что первая последовательность данных представляет собой заданную последовательность данных.

9. Устройство по п. 7, в котором заданная последовательность данных содержит m-последовательность с r циклов, при этом длина каждой m-последовательности составляет L, r и L представляют собой заданные значения;

- вторая последовательность данных содержит: данные в стандартной структуре кадра; и

- разность времен между первой последовательностью данных и второй последовательностью данных является временем, занимаемым посредством избыточного бита, и время, занимаемое посредством избыточного бита, превышает или равно времени, требуемому для переключения с N-битового ADC на M-битовый ADC.

10. Система связи, содержащая приемное устройство и отправляющее устройство, при этом приемное устройство выполнено с возможностью дискретизировать, в режиме прослушивания в состоянии бездействия, первый аналоговый сигнал посредством использования N-битового аналого-цифрового преобразователя ADC и дискретизировать, в режиме приемо-передачи, второй аналоговый сигнал посредством использования M-битового ADC, при этом N и M являются целыми числами, и N меньше M; отправляющее устройство выполнено с возможностью осуществлять связь с приемным устройством, при этом отправляющее устройство выполнено с возможностью формировать последовательность данных и выполнять цифроаналоговое преобразование для последовательности данных для того, чтобы получать аналоговые сигналы и отправлять аналоговые сигналы в приемное устройство, так что приемное устройство дискретизирует, в режиме прослушивания в состоянии бездействия, первый аналоговый сигнал посредством использования N-битового аналого-цифрового преобразователя ADC и дискретизирует, в режиме приемо-передачи, второй аналоговый сигнал посредством использования M-битового ADC, при этом N и M являются целыми числами, и N меньше M.

11. Система по п. 10, в которой последовательность данных содержит:

- заданную последовательность данных, избыточный бит и данные в стандартной структуре кадра, при этом заданная последовательность данных содержит m-последовательность с r циклов, длина каждой m-последовательности составляет L, r и L представляют собой заданные значения, и время, занимаемое посредством избыточного бита, превышает или равно времени, требуемому для переключения с N-битового ADC на M-битовый ADC.

12. Система по п. 10, в которой приемное устройство дополнительно выполнено с возможностью определять то, представляет ли собой первая последовательность данных заданную последовательность данных, и дискретизировать, когда определяется то, что первая последовательность данных представляет собой заданную последовательность данных, второй аналоговый сигнал посредством использования M-битового ADC для того, чтобы получать вторую последовательность данных.

13. Система по п. 12, в которой заданная последовательность данных содержит m-последовательность с r циклов, при этом длина каждой m-последовательности составляет L, r и L представляют собой заданные значения;

- вторая последовательность данных содержит: данные в стандартной структуре кадра; и

- разность времен между первой последовательностью данных и второй последовательностью данных является временем, занимаемым посредством избыточного бита, и время, занимаемое посредством избыточного бита, превышает или равно времени, требуемому для переключения с N-битового ADC на M-битовый ADC.

| US 2011096875 A1, 28.04.2011WO 2012/138947 A2, 11.10.2012 CN 202035008 U, 09.11.2011 | |||

| CN 102185809 A, 14.09.2011 RU 2008116167 A, 10.12.2009. |

Авторы

Даты

2016-10-10—Публикация

2013-11-12—Подача