Изобретение относится к технологии микроэлектроники, а именно к технологии получения монолитных интегральных схем (МИС) на основе полупроводниковых соединений AIIIBV, в которых минимизировано содержание драгоценных металлов.

Известна МИС переключателя на GaAs (Y.C. Wu, E.Y. Chang, Y.C. Lin, H.T. Hsu, S.H. Chen, W.C. Wu, L.H. Chu, C.Y Chang / SPDT GaAs switches with copper metalized interconnects // IEEE MICROWAVE AND WIRELESS COMPONENTS LETTERS, v. 17, n. 2, February 2007), выполненная с использованием гетероструктурных полевых транзисторов с высокой подвижностью электронов. Омические контакты транзисторов выполнены на основе четырехслойной композиции Au/Ge/Ni/Au, затворы транзисторов, а также нижняя обкладка конденсаторов выполнены на основе трехслойной композиции Ti/Pt/Au. В качестве диэлектрика конденсаторов использована тонкая пленка нитрида кремния. Металлизация МИС и верхняя обкладка конденсаторов выполнены на основе трехслойной композиции Ti/Pt/Cu (30 нм/70 нм/2000 нм). Защита поверхности МИС выполнена тонкой пленкой нитрида кремния.

Недостатками данной МИС являются недостаточно низкая себестоимость изготовления, обусловленная использованием Au в составе металлизации омических контактов, затворов транзисторов и нижней обкладки конденсаторов, использованием Pt в составе металлизации МИС и верхней обкладки конденсаторов, а также отсутствие технического решения по формированию металлизации обратной стороны МИС, что накладывает ограничения на возможности создания различных видов МИС.

Известна МИС на основе полупроводникового соединения (Заявка на патент US 2014054608, МПК H01L 29/16, опубл. 27.02.2014), содержащая в своем составе как минимум одно полупроводниковое устройство, первичные слои металлизации, защитный слой, множество вторичных слоев металлизации, как минимум один диэлектрический слой, также может иметь металлизацию обратной стороны МИС. Первичные слои металлизации, содержащие в своем составе Au, электрически соединены с полупроводниковым устройством. Защитный слой, выполненный из SiN, покрывает полупроводниковое устройство и первичные слои металлизации. Как минимум один из вторичных слоев металлизации, содержащих в своем составе Cu, электрически соединен с первичными слоями металлизации. Вторичные слои металлизации разделены между собой диэлектрическими слоями, выполненными из полибензоксазола (polybenzoxazole/PBO) толщиной 10-30 мкм. Металлизация обратной стороны МИС, как минимум, частично выполнена из Cu.

Недостатками данного технического решения являются недостаточно низкая себестоимость изготовления МИС, обусловленная использованием Au в составе первичных слоев металлизации, а также отсутствие оформленного решения по формированию металлизации обратной стороны МИС, что накладывает ограничения на возможности создания различных видов МИС.

Наиболее близкой к заявляемому устройству по наибольшему числу существенных признаков является выбранная за прототип МИС с медной металлизацией (Заявка на патент US 20130207266, МПК H01L 23/535, опубл. 15.08 2013), содержащая в своем составе, как минимум, одно полупроводниковое устройство, пассивирующие слои, уровни металлизации и межуровневый диэлектрик. Первый пассивирующий слой, выполненный из SiNx, покрывает полупроводниковое устройство, на нем располагаются уровни металлизации, электрически соединенные как с полупроводниковым устройством, так и между собой. Каждый уровень металлизации также покрыт пассивирующим слоем, выполненным из SiNx. Между собой уровни металлизации разделены слоями межуровневого диэлектрика. Каждый уровень металлизации представляет собой многослойную композицию, состоящую из двух групп слоев: контактных и медьсодержащих слоев. Контактные слои могут иметь различные комбинации слоев Ti/Pd/Cu, Ti/NiV/Cu, TiW/TiWN/TiW/Cu, TiW/TiWN/TiW/Au, TiW/Cu, TiW/Au, где слои Ti и TiW выполняют роль адгезионного слоя, слои Pd, NiV, TiW и TiWN выполняют роль диффузионного барьера для меди, слои Cu и Au выполняют роль затравочных слоев. Медьсодержащие слои включают в себя защитные слои, покрывающие слой меди, для защиты меди от окисления. Защитные слои могут быть выполнены из Ni/Au, Ni/Pd/Au, NiV/Au или припоя.

Недостатками данного технического решения являются недостаточно низкая себестоимость изготовления МИС, обусловленная использованием Au и Pd в составе металлизации, а также отсутствие оформленных решений по формированию контактных площадок полупроводниковых устройств (омические контакты, контакты Шоттки), металлизации обратной стороны МИС, что не позволяет изготавливать МИС на основе только данного технического решения.

Основной технической задачей, решаемой заявляемым изобретением, является создание МИС на основе полупроводниковых соединений AIIIBV с более низкой себестоимостью изготовления, за счет использования металлизации, в которой минимизировано содержание драгоценных металлов, отвечающей современным требованиям по надежности, а также совместимой с технологией Si микроэлектроники, для формирования современных приборов гетероинтегрированной электроники.

Основная техническая задача достигается тем, что в монолитной интегральной схеме на основе полупроводникового соединения, включающей полупроводниковую пластину с расположенными на ней активными и пассивными элементами, сквозными отверстиями и металлизацией обратной стороны, выполненной из омических контактов и затворов, расположенных на поверхности активного слоя полупроводниковой пластины, первого слоя защитного диэлектрика, покрывающего омические контакты и поверхность полупроводниковой пластины, нижней обкладки конденсаторов, расположенной на поверхности первого слоя защитного диэлектрика, второго слоя защитного диэлектрика, покрывающего нижнюю обкладку конденсаторов, затворы и первый слой защитного диэлектрика, металлизации первого уровня, расположенной на поверхности второго слоя защитного диэлектрика, омических контактов, в специально сформированных окнах в первом и втором слоях защитного диэлектрика, затворов и нижней обкладки конденсаторов, в специально сформированных окнах во втором слое защитного диэлектрика, резистивного слоя, расположенного на поверхности второго слоя защитного диэлектрика и металлизации первого уровня, металлизации второго уровня, расположенной на поверхности металлизации первого уровня и резистивного слоя, третьего слоя защитного диэлектрика, покрывающего металлизации первого и второго уровней, резистивный слой и второй слой защитного диэлектрика, при этом металлизация первого уровня включает последовательно расположенные слой диффузионного барьера, слой Cu и проводящий защитный слой, металлизация второго уровня включает последовательно расположенные адгезионный слой и слой Cu, металлизация обратной стороны содержит слой Cu, согласно предложенному решению введены четвертый слой защитного диэлектрика, расположенный на поверхности третьего слоя защитного диэлектрика, металлизация третьего уровня, частично расположенная на поверхности четвертого слоя защитного диэлектрика, частично на поверхности металлизации второго уровня в специально сформированных окнах в третьем и четвертом слоях защитного диэлектрика, при этом омические контакты и затвор включают слой Al, в металлизации первого уровня слой диффузионного барьера выполнен по площади осаждения шире, чем слой Cu, и проводящий защитный слой покрывает как верхнюю планарную, так и все торцевые поверхности слоя Cu, а металлизация обратной стороны включает последовательно расположенные на полупроводниковой пластине выравнивающий слой Ni, слой диффузионного барьера, слой Cu и проводящий защитный слой.

В частном случае омический контакт включает последовательно расположенные слои Pd, Ge и Al соответственно толщиной 5-200 нм, 5-500 нм и 5-500 нм.

В частном случае затвор включает последовательно расположенные барьерный слой Ti и слой Al соответственно толщиной 5-500 нм и 5-1000 нм.

В частном случае нижняя обкладка конденсаторов включает последовательно расположенные слой диффузионного барьера, слой Cu и проводящий защитный слой соответственно толщиной 5-500 нм, 5-3000 нм и 5-500 нм, при этом слой диффузионного барьера по площади осаждения шире, чем слой Cu, и проводящий защитный слой покрывает как верхнюю планарную, так и все торцевые поверхности слоя Cu.

В частном случае нижняя обкладка конденсаторов включает последовательно расположенные барьерный слой Ti и слой Al соответственно толщиной 5-500 нм и 5-1000 нм.

В частном случае в металлизации первого уровня слои диффузионного барьера, слой Cu и проводящий защитный слой выполнены соответственно толщиной 5-500 нм, 5-3000 нм и 5-500 нм.

В частном случае в металлизации второго уровня адгезионный слой и слой Cu выполнены соответственно толщиной 5-500 нм и 5-5000 нм.

В частном случае четвертый слой защитного диэлектрика выполнен на основе слоя органического диэлектрика толщиной 1000-30000 нм.

В частном случае в качестве слоя органического диэлектрика используют бензоциклобутен.

В частном случае в состав омического контакта, затвора, нижней обкладки конденсаторов дополнительно введен проводящий защитный слой на основе слоя Mo, или Ti, или Ta, или W, или TaNx, или TiNx, или WNx, а также их комбинаций толщиной 5-500 нм, расположенный на поверхности слоя Al.

В частном случае в состав омического контакта, затвора, нижней обкладки конденсаторов дополнительно введен стоп-слой травления на основе слоя Ni толщиной 5-500 нм, расположенный на поверхности слоя Al.

В частном случае в состав омического контакта, затвора, нижней обкладки конденсаторов дополнительно введен стоп-слой травления на основе слоя Ni толщиной 5-500 нм, расположенный на поверхности проводящего защитного слоя.

В частном случае в качестве материала слоя диффузионного барьера и проводящего защитного слоя металлизации первого уровня и нижней обкладки конденсаторов используют слой Mo, или Ta, или W, или TaNx, или TiNx, или WNx, а также их комбинации.

В частном случае в металлизации второго уровня в качестве материала адгезионного слоя используют слой Мо, или Ta, или W, или TaNx, или TiNx, а также их комбинации.

В частном случае в металлизации обратной стороны выравнивающий слой Ni, слой диффузионного барьера и слой Cu выполнены соответственно толщиной 5-5000 нм, 5-500 нм и 5-30000 нм.

В частном случае в качестве материала слоя диффузионного барьера металлизации обратной стороны используют слой Mo, или Ta, или W, или TaNx, или TiNx, или WNx, а также их комбинации.

В частном случае в качестве материала проводящего защитного слоя металлизации обратной стороны используют слой Мо, или Та, или W, или TaNx, или TiNx, или WNx, или Au, или двухслойной композиции Ni/Au толщиной 5-300 нм.

В частном случае в качестве материала проводящего защитного слоя металлизации обратной стороны используют слой SnPb, или AgCuSn, или двухслойные композиции Ni/SnPb, или Ni/AgCuSn толщиной 100-10000 нм.

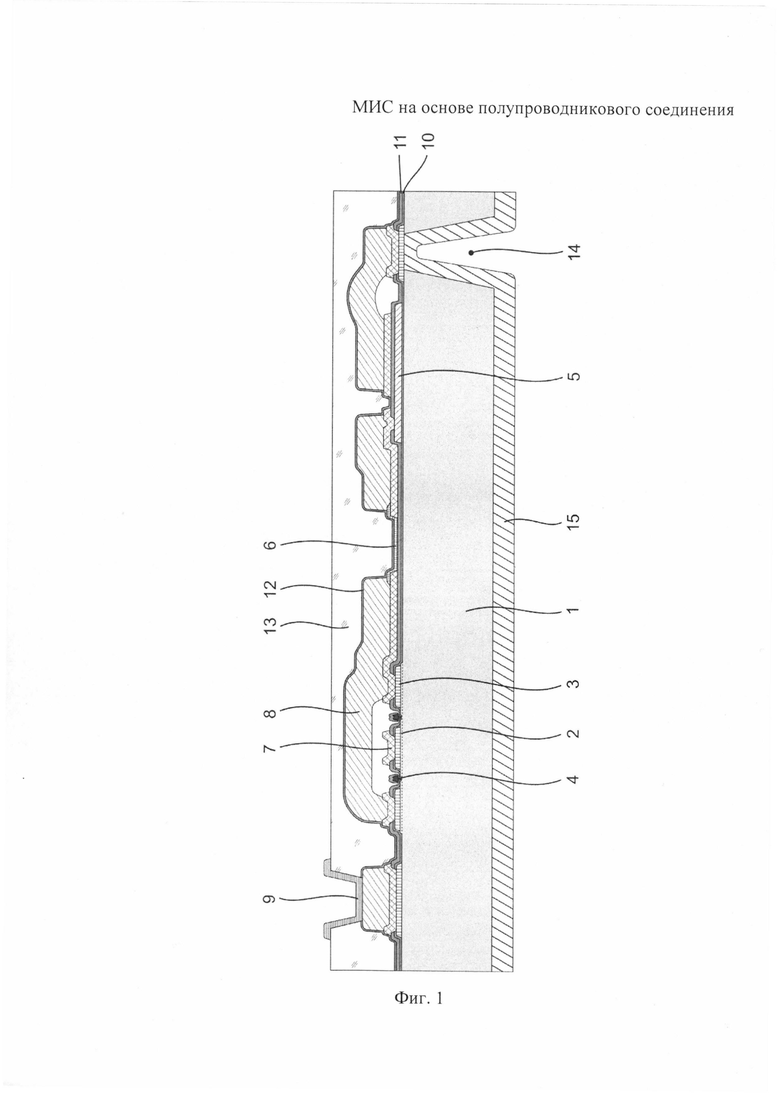

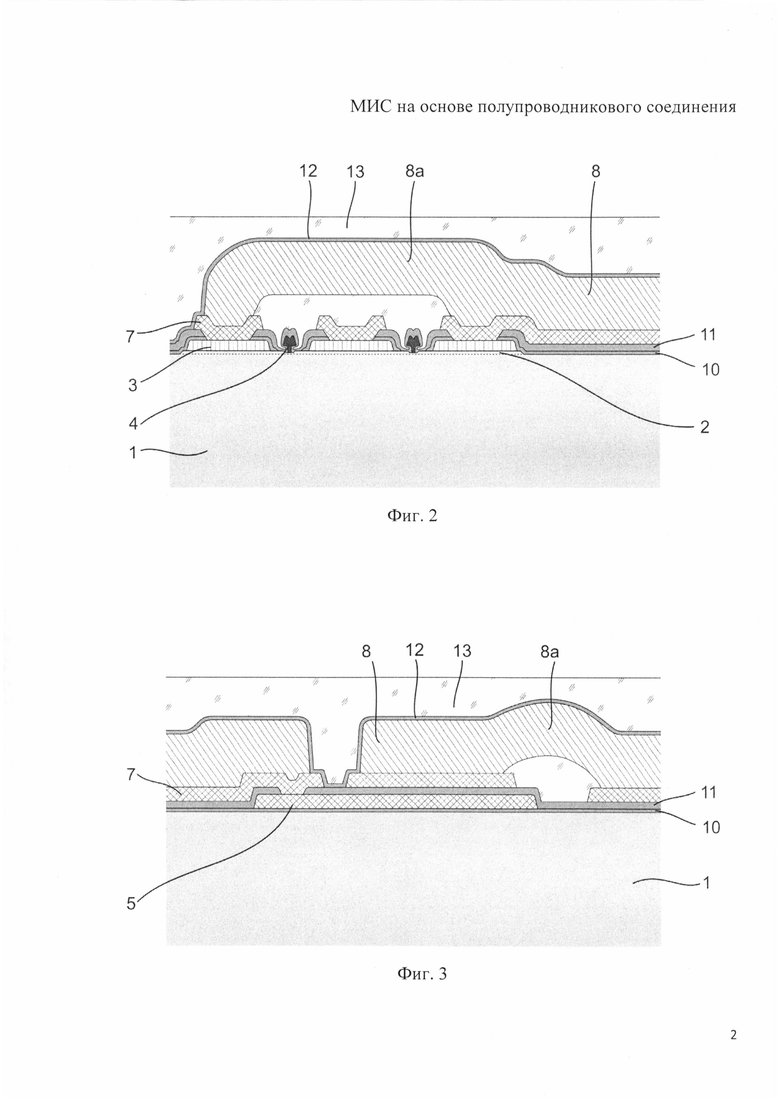

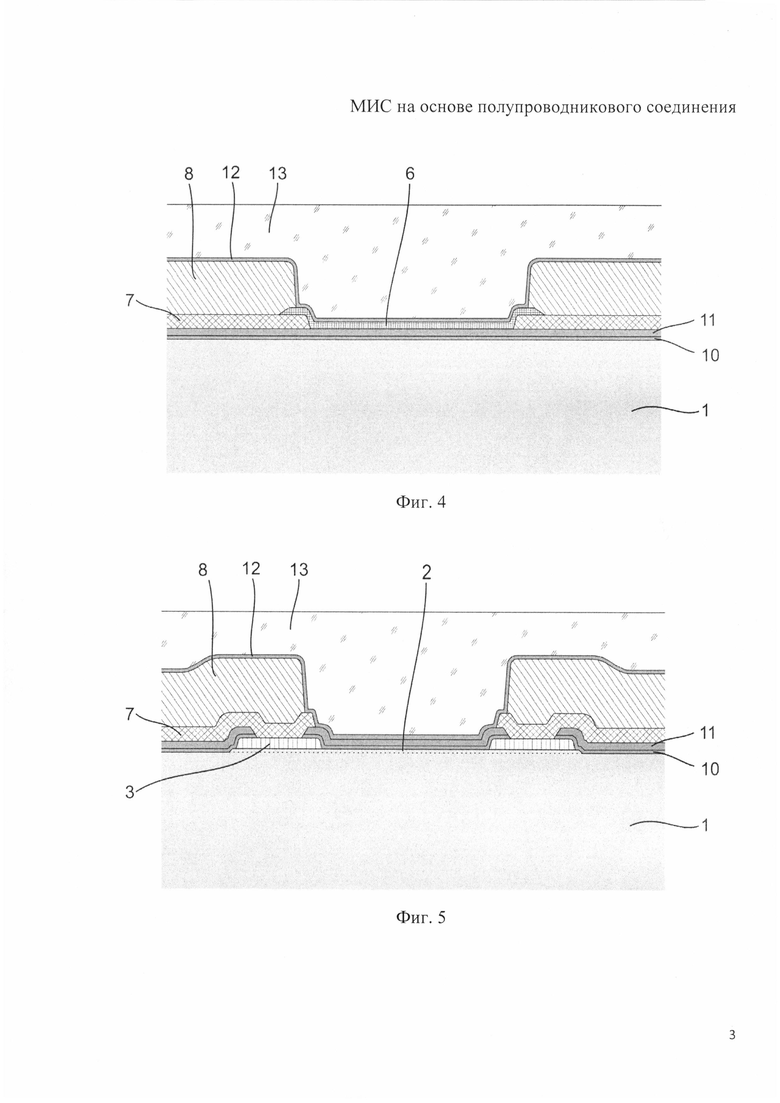

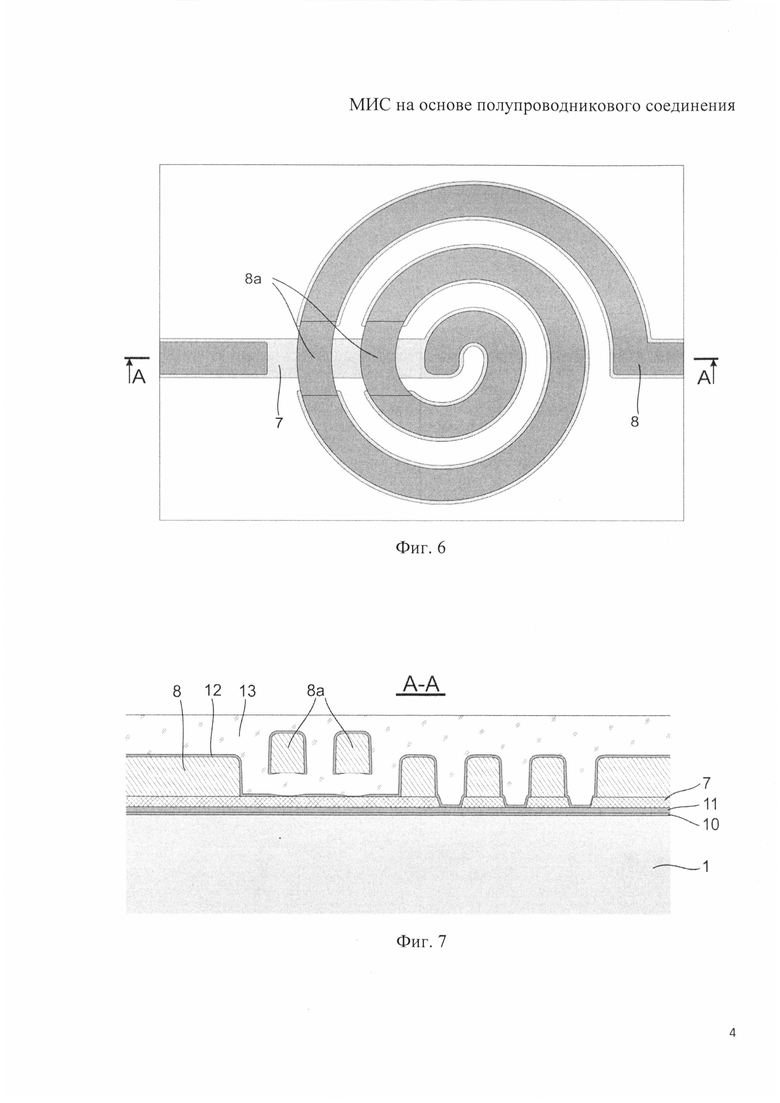

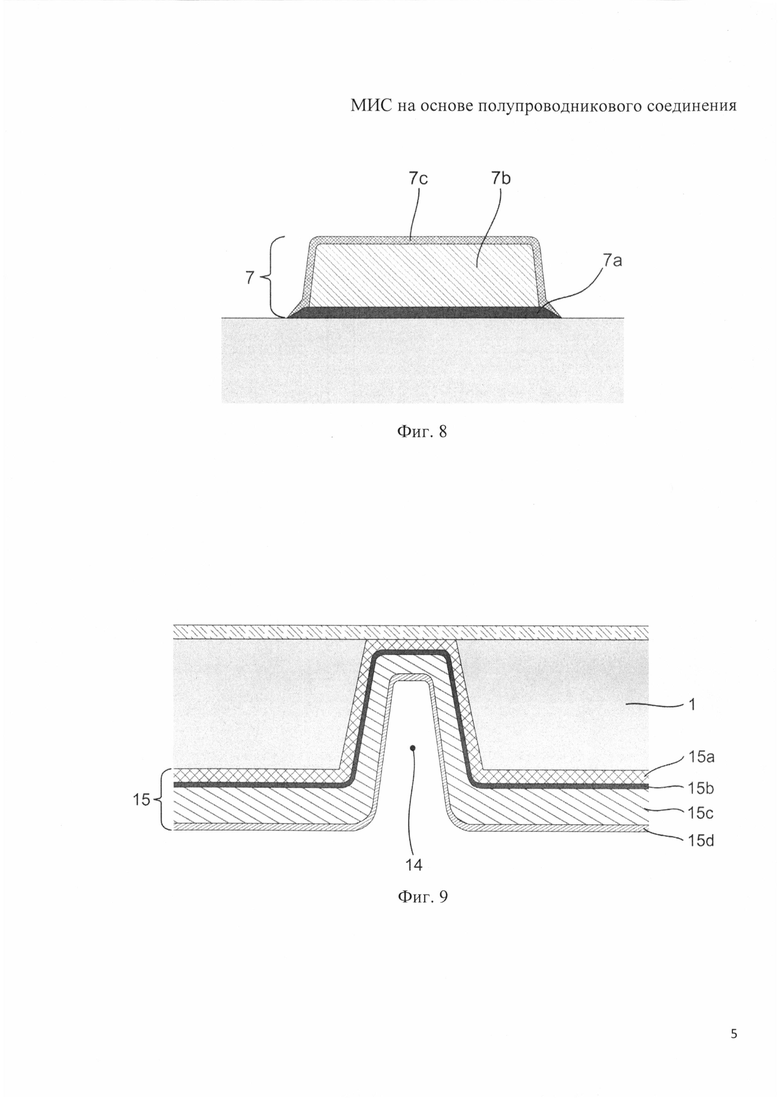

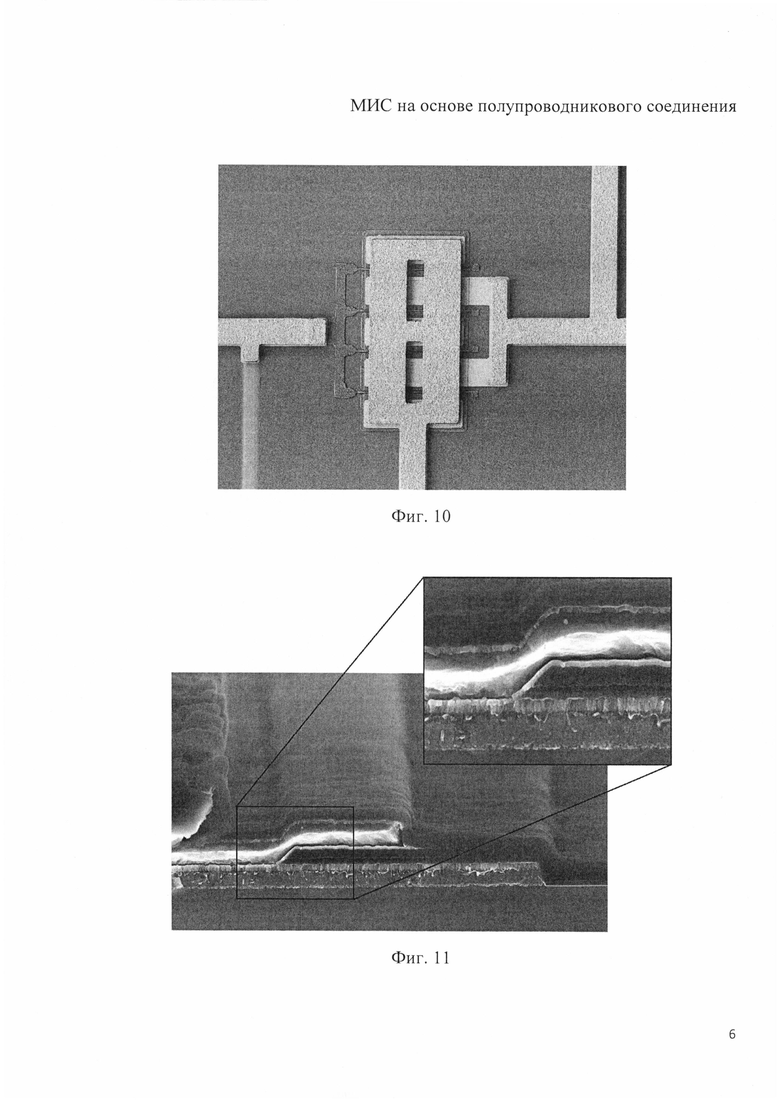

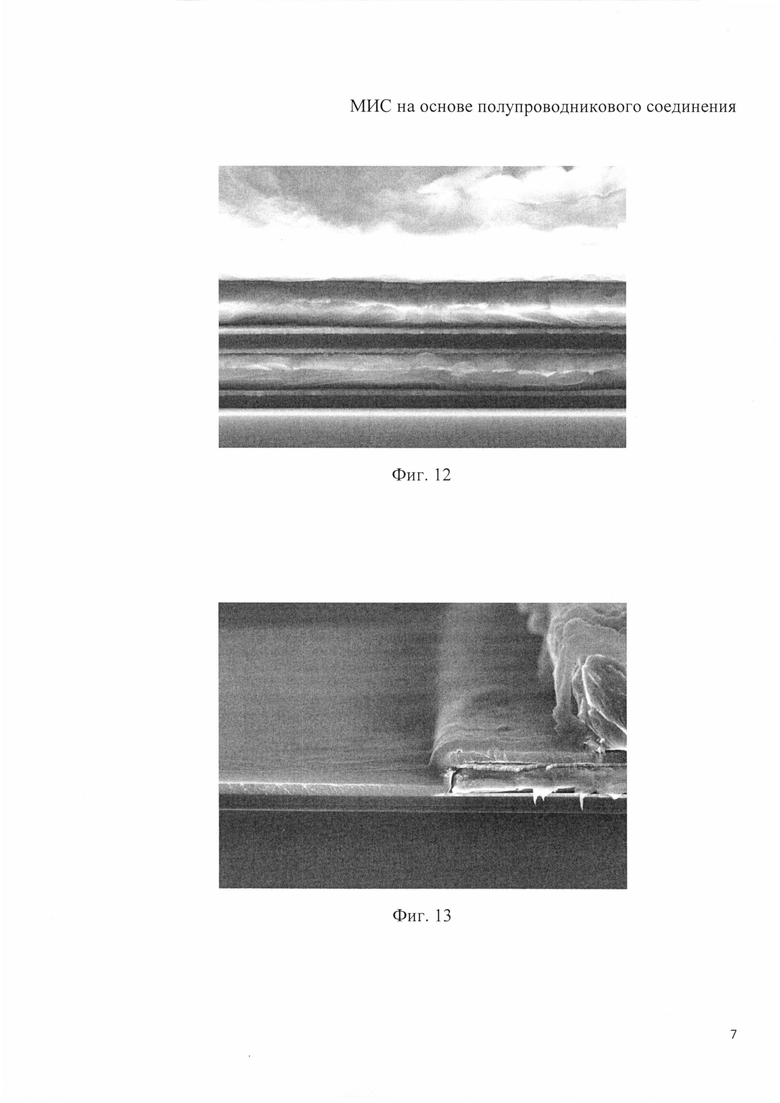

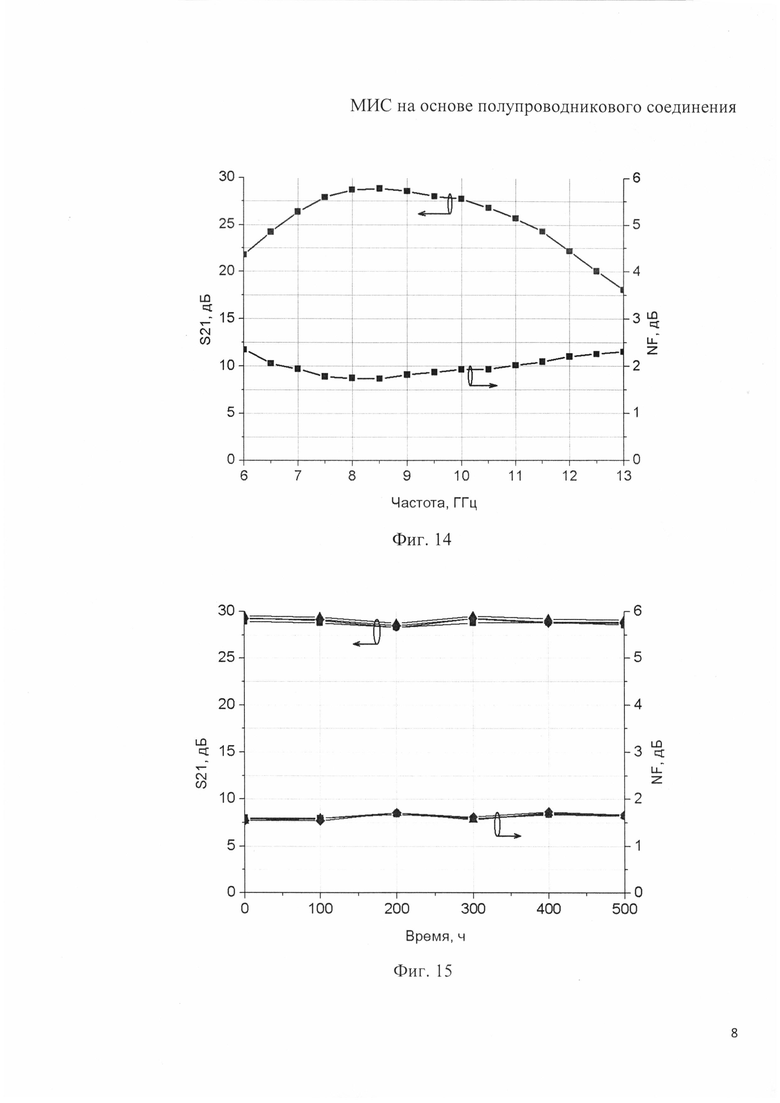

Изобретение поясняется рисунками, где на фиг. 1 представлен общий вид заявляемого устройства; на фиг. 2-7 представлены конструкции элементов заявляемой МИС, соответственно: транзистора (полевого транзистора с затвором Шоттки или гетероструктурного транзистора с высокой подвижностью электронов); конденсатора; тонкопленочного резистора; объемного резистора; индуктивности (вид сверху и вид в разрезе A-A); на фиг. 8 представлена конструкция металлизации первого уровня; на фиг. 9 представлена конструкция металлизации обратной стороны со сквозными отверстиями; на фиг. 10 представлено микроскопическое изображение транзистора после этапа формирования металлизации второго уровня; на фиг. 11-13 представлены микроскопические изображения поперечных сечений элементов МИС, соответственно: контактной площадки истока транзистора; конденсатора; тонкопленочного резистора. На фиг. 14 представлены зависимости коэффициентов усиления S21 и шума NF от частоты для МИС малошумящего усилителя, выполненного на основе GaAs. На фиг. 15 представлены зависимости коэффициентов усиления S21 и шума NF МИС малошумящего усилителя на частоте 9 ГГц от времени выдержки при температуре T=125°C с одновременной подачей на МИС напряжения питания 5 В.

Заявляемое устройство (фиг. 1) состоит из полупроводниковой пластины 1 с активным слоем 2, содержащим канальный и контактный слои, включающее активные и пассивные элементы, выполненные на основе омических контактов 3, затворов 4, нижней обкладки конденсаторов 5, резистивного слоя 6, металлизации первого 7, второго 8 и третьего 9 уровней, первого 10, второго 11 третьего 12 и четвертого 13 слоев защитного диэлектрика, сквозных отверстий 14 и металлизации обратной стороны 15.

Транзистор в составе заявляемого устройства (фиг. 2) состоит из полупроводниковой пластины 1, активного слоя 2, омических контактов 3, затворов 4, металлизаций первого и второго уровней 7 и 8 соответственно, первого, второго, третьего и четвертого слоев защитного диэлектрика 10, 11, 12 и 13 соответственно. Первый слой защитного диэлектрика 10 расположен на поверхности полупроводниковой пластины 1 и омических контактов 3, расположенных на поверхности активного слоя 2. Второй слой защитного диэлектрика 11 расположен на поверхности первого слоя защитного диэлектрика 10 и затворов 4. Металлизация первого уровня 7 расположена на поверхности второго слоя защитного диэлектрика 11 и омических контактов 3, в специально сформированных окнах, в первом и втором слоях защитного диэлектрика 10 и 11 соответственно. Металлизации второго уровня 8 расположена на поверхности металлизации первого уровня 7. Третий слой защитного диэлектрика 12 расположен на поверхности второго слоя защитного диэлектрика 11, первого и второго уровней металлизации 7 и 8 соответственно. Четвертый слой защитного диэлектрика 13 расположен на поверхности третьего слоя защитного диэлектрика 12. «Воздушный» мост 8а, содержащийся в составе металлизации второго уровня 8, предназначен для электрического соединения площадок контактов истоков транзистора.

Конденсатор в составе заявляемой МИС (фиг. 3) состоит из полупроводниковой пластины 1, нижней обкладки конденсатора 5, металлизаций первого и второго уровня 7 и 8 соответственно, первого, второго, третьего и четвертого слоев защитного диэлектрика 10, 11, 12 и 13 соответственно. На поверхности полупроводниковой пластины 1 расположен первый слой защитного диэлектрика 10, на котором расположена нижняя обкладка конденсатора 5. Второй слой защитного диэлектрика 11, также выполняющий роль диэлектрика конденсатора, расположен на поверхности первого слоя защитного диэлектрика 10 и нижней обкладки конденсатора 5. Металлизация первого уровня 7, также выполняющая роль верхней обкладки конденсатора, расположена на поверхности второго слоя защитного диэлектрика 11 и нижней обкладки конденсатора 5, в специально сформированном окне, во втором слое защитного диэлектрика 11. Металлизация второго уровня 8 расположена на поверхности металлизации первого уровня 7. Третий слой защитного диэлектрика 12 расположен на поверхности второго слоя защитного диэлектрика 11, первого и второго уровней металлизации 7 и 8 соответственно. Четвертый слой защитного диэлектрика 13 расположен на поверхности третьего слоя защитного диэлектрика 12. «Воздушный» мост 8a, содержащийся в составе металлизации второго уровня 8, обеспечивает электрический контакт между верхней обкладкой конденсатора и металлизацией первого уровня 7 устройства.

Тонкопленочный резистор в составе заявляемой МИС (фиг. 4) состоит из полупроводниковой пластины 1, резистивного слоя 6, металлизаций первого и второго уровня 7 и 8 соответственно, первого, второго, третьего и четвертого слоев защитного диэлектрика 10, 11, 12 и 13 соответственно. На поверхности полупроводниковой пластины 1 последовательно расположены первый и второй слои защитного диэлектрика 10 и 11 соответственно. Металлизация первого уровня 7 расположена на поверхности второго слоя защитного диэлектрика 11. Резистивный слой 6 расположен на поверхности второго слоя защитного диэлектрика 11 и первого уровня металлизации 7. Металлизации второго уровня 8 расположена на поверхности металлизации первого уровня 7 и резистивного слоя 6. Третий слой защитного диэлектрика 12 расположен на поверхности резистивного слоя 6 и второго уровней металлизации 8. Четвертый слой защитного диэлектрика 13 расположен на поверхности третьего слоя защитного диэлектрика 12.

Объемный резистор в составе заявляемого устройства (фиг. 5) состоит из полупроводниковой пластины 1 с активным слоем 2, выполняющим роль резистивного слоя, омических контактов 3, металлизации первого и второго уровней 7 и 8 соответственно, первого, второго, третьего и четвертого слоев защитного диэлектрика 10, 11, 12 и 13 соответственно. Омические контакты 3 расположены на поверхности активного слоя 2. Первый слой защитного диэлектрика 10 расположен на поверхности полупроводниковой пластины 1 и омических контактов 3, второй слой защитного диэлектрика 11 расположен на поверхности первого слоя защитного диэлектрика 10. Металлизация первого уровня 7 расположена на поверхности второго слоя защитного диэлектрика 11 и на поверхности омических контактов 3, в специально сформированных окнах, в первом и втором слоях защитного диэлектрика 10 и 11 соответственно. Металлизация второго уровня 8 расположена на поверхности металлизации первого уровня 7. Третий слой защитного диэлектрика 12 расположен на поверхности второго слоя защитного диэлектрика 11, металлизаций первого и второго уровней 7 и 8 соответственно. Четвертый слой защитного диэлектрика 13 расположен на поверхности третьего слоя защитного диэлектрика 12.

Индуктивность в составе заявляемой МИС (фиг. 6 и фиг. 7) состоит из последовательно расположенных на поверхности полупроводниковой пластины 1 первого и второго слоев защитного диэлектрика 10 и 11 соответственно, металлизации первого и второго уровней 7 и 8 соответственно, третьего и четвертого слоев защитного диэлектрика 12 и 13 соответственно. «Воздушные» мосты 8a, содержащиеся в составе металлизации второго уровня 8, обеспечивают электрическую развязку между внутренним концом и витками индуктивности.

Металлизация первого уровня 7 (фиг. 8) состоит из последовательно расположенных слоя диффузионного барьера 7a, слоя меди 7b и проводящего защитного слоя 7с. Слой диффузионного барьера 7a выполнен по площади осаждения шире, чем слой меди 7b, и проводящий защитный слой 7с покрывает как верхнюю планарную, так и все торцевые поверхности слоя меди 7b.

Аналогично металлизации первого уровня 7 устроена нижняя обкладка конденсаторов 5, в варианте ее исполнения на основе слоя меди.

Металлизация обратной стороны МИС 15 (фиг. 9) состоит из последовательно расположенных на поверхности обратной стороны полупроводниковой пластины 1 выравнивающего слоя 15a, слоя диффузионного барьера 15b, слоя меди 15c и проводящего защитного слоя 15d. Металлизация обратной стороны 15 может контактировать с омическим контактом 3, затвором 4, нижней обкладкой конденсатора 5, металлизацией первого уровня 7 или металлизацией второго уровня 8.

Пример

Заявляемая МИС была реализована на примере изготовления GaAs МИС трехкаскадного малошумящего усилителя. Была использована полуизолирующая пластина GaAs, на поверхности которой методом молекулярно-лучевой эпитаксии была выращена гетероструктура AlGaAs/InGaAs/AlGaAs. Формирование элементов МИС было проведено с использованием методов контактной и электронно-лучевой литографий.

Формирование межэлементной изоляции активных элементов было выполнено посредством жидкостного травления GaAs меза-структуры в растворе H3PO4:H2O2:H2O. В качестве омических контактов 3 транзисторов с высокой подвижностью электронов была использована многослойная тонкопленочная композиция Pd/Ge/Al/Mo, осаждаемая методом электронно-лучевого испарения. Отжиг омических контактов 3 был проведен на горячей плите при температуре 250°C в течение 20 мин. Т-образные затворы 4 транзисторов на основе трехслойной композиции Ti/Al/Mo имели длину основания 250 нм и осаждались методом электронно-лучевого испарения.

Металлизация первого уровня 7 и нижняя обкладка конденсаторов 5 были изготовлены из трехслойной композиции W/Cu/WNx с общей толщиной 470 нм. Слои диффузионного барьера 7a (W) и проводящего защитного слоя 7c (WNX) сформированы с помощью магнетронного распыления вольфрамовой мишени в газовой среде аргона в режиме на постоянном токе (DC), а также в среде аргона и азота в импульсном DC режиме соответственно. Слой меди 7b был осажден методом электронно-лучевого испарения.

Металлизация второго уровня 8 была сформирована методом электрохимического осаждения слоя Cu толщиной 3 мкм из электролита CuSO4:H2SO4. В качестве подслоя для электрохимического осаждения Cu была использована двухслойная композиция Ti/Cu, получаемая методом электронно-лучевого испарения.

Тонкопленочные резисторы сформированы магнетронным распылением мишени из сплава РС5406Н в среде аргона на постоянном токе.

Для формирования первого и второго слоев защитного диэлектрика 10 и 11 соответственно использованы слои SiNx, окна в которых к ниже расположенным элементам МИС сформированы методом реактивно-ионного травления в индуктивно-связанной плазме. Финальная защита поверхности МИС выполнена последовательно сформированными третьим и четвертым слоями защитного диэлектрика 12 и 13 соответственно, которые выполнены на основе SiNx и ВСВ соответственно, общей толщиной около 5 мкм.

Для формирования металлизации обратной стороны 15 полупроводниковая пластина 1 утонялась до толщины 100 мкм. Формирование сквозных отверстий 14 было произведено методом реактивно-ионного травления в индуктивно-связанной плазме. Металлизация обратной стороны 15 полупроводниковой пластины 1 выполнена на основе многослойной композиции Ni/W/Cuм/Cuэ/W. Выравнивающий слой 15a (Ni) осажден химическим методом. Слой диффузионного барьера 15b (W), подслой 15c (Cuм) и проводящий защитный слой 15d (W) были сформированы методом магнетронного распыления вольфрамовой, медной и вольфрамовой мишени соответственно, в газовой среде аргона в DC режиме. Осаждение слоя 15c (Cuэ) было проведено методом электрохимического осаждения из электролита CuSO4:H2SO4. Общая толщина металлизации обратной стороны 15 составляла 5 мкм.

Микроскопические изображения элементов заявляемой МИС были получены с помощью сканирующей электронной микроскопии (фиг. 10-13). Измерение малосигнальных параметров МИС было проведено на пластине с помощью зондовой станции Suss-PA200 с использованием векторного анализатора цепей Р4М-18 и измерителя коэффициента шума N8975A. Измерение коэффициентов усиления и шума МИС, при проведении ускоренных испытаний, было выполнено с помощью измерителя коэффициента шума N8975А.

Изготовленная МИС малошумящего усилителя в диапазоне частот 8-10 ГГц имела коэффициент усиления 28±1 дБ, при этом коэффициент шума не превышал 2 дБ (фиг. 14). Ток потребления МИС при напряжении питания +5 В составлял 40 мА. В качестве критерия годности выступал коэффициент усиления. Выход годных МИС, выполненных на полупроводниковой пластине диаметром 100 мм, составил 45%.

Далее пластина с МИС проходила процедуру термостабилизации в печи в атмосфере азота при температуре 200°C в течение 24 ч. При повторных измерениях изменений малосигнальных параметров и тока потребления МИС не выявлено.

После того как полупроводниковая пластина была разделена на отдельные кристаллы, среди годных МИС была проведена выборка в количестве пяти групп по четыре штуки. МИС выборки были подвергнуты ускоренным испытаниям на надежность, для чего они были смонтированы в модули с разъемами для подведения напряжения питания и с СВЧ разъемами для проведения измерений параметров. Модули помещались в камеру при температуре 125°C с одновременной подачей на МИС напряжения питания 5 В. Через каждые 100 ч модули извлекались из камеры, и проводилось измерение коэффициентов усиления S21 и шума NF МИС. Общее время ускоренных испытаний составляло 500 ч. В течение времени испытаний деградации параметров МИС не наблюдалось (фиг. 15).

Полученный результат демонстрирует, что заявляемая МИС, с металлизацией выполненной на основе Al и Cu, обладает параметрами и надежностью на уровне МИС с традиционной металлизацией на основе Au.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТРАНЗИСТОР НА ОСНОВЕ ПОЛУПРОВОДНИКОВОГО СОЕДИНЕНИЯ | 2010 |

|

RU2442243C1 |

| СВЕРХВЫСОКОЧАСТОТНЫЙ ТРАНЗИСТОР | 2013 |

|

RU2540234C1 |

| СПОСОБ МЕТАЛЛИЗАЦИИ СКВОЗНЫХ ОТВЕРСТИЙ В ПОЛУИЗОЛИРУЮЩИХ ПОЛУПРОВОДНИКОВЫХ ПОДЛОЖКАХ | 2019 |

|

RU2708677C1 |

| Способ формирования Т-образного затвора | 2017 |

|

RU2686863C1 |

| Способ изготовления СВЧ-гибридной интегральной микросхемы космического назначения с многоуровневой коммутацией | 2019 |

|

RU2713572C1 |

| ТРАНЗИСТОР НА ОСНОВЕ ПОЛУПРОВОДНИКОВОГО СОЕДИНЕНИЯ И СПОСОБ ЕГО ИЗГОТОВЛЕНИЯ | 2011 |

|

RU2460172C1 |

| Способ изготовления омического контакта к AlGaN/GaN | 2018 |

|

RU2696825C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МНОГОСЛОЙНОГО ОМИЧЕСКОГО КОНТАКТА К n-GaAs | 2009 |

|

RU2407104C1 |

| Способ формирования субмикронного Т-образного затвора | 2019 |

|

RU2724354C1 |

| ВСТРАИВАЕМАЯ С СБИС ТЕХНОЛОГИИ КМОП/КНИ ПАМЯТЬ "MRAM" И СПОСОБ ЕЕ ИЗГОТОВЛЕНИЯ (ВАРИАНТЫ) | 2012 |

|

RU2532589C2 |

Изобретение относится к микроэлектронике, а именно к технологии получения монолитных интегральных схем (МИС) на основе полупроводниковых соединений AIIIBV. Изобретение обеспечивает получение МИС на основе полупроводниковых соединений AIIIBV с более низкой себестоимостью изготовления за счет использования металлизации, в которой минимизировано содержание драгоценных металлов, по технологии, совместимой с технологией Si микроэлектроники, для формирования современных приборов гетероинтегрированной электроники. Устройство содержит полупроводниковую пластину с активным слоем, содержащим канальный и контактный слои, включающее активные и пассивные элементы, выполненные на основе омических контактов, затворов, нижней обкладки конденсаторов, резистивного слоя, металлизации первого, второго и третьего уровней, первого, второго, третьего и четвертого слоев защитного диэлектрика, сквозных отверстий и металлизации обратной стороны. Металлизации первого, второго уровней и обратной стороны выполнены на основе Cu, а омических контактов и затворов - на основе Al. 17 з.п. ф-лы, 15 ил.

1. Монолитная интегральная схема (МИС) на основе полупроводникового соединения, включающая полупроводниковую пластину с расположенными на ней активными и пассивными элементами, сквозными отверстиями и металлизацией обратной стороны, выполненная из омических контактов и затворов, расположенных на поверхности активного слоя полупроводниковой пластины, первого слоя защитного диэлектрика, покрывающего омические контакты и поверхность полупроводниковой пластины, нижней обкладки конденсаторов, расположенной на поверхности первого слоя защитного диэлектрика, второго слоя защитного диэлектрика, покрывающего нижнюю обкладку конденсаторов, затворы и первый слой защитного диэлектрика, металлизации первого уровня, расположенной на поверхности второго слоя защитного диэлектрика, омических контактов, в специально сформированных окнах в первом и втором слоях защитного диэлектрика, затворов и нижней обкладки конденсаторов, в специально сформированных окнах во втором слое защитного диэлектрика, резистивного слоя, расположенного на поверхности второго слоя защитного диэлектрика и металлизации первого уровня, металлизации второго уровня, расположенной на поверхности металлизации первого уровня и резистивного слоя, третьего слоя защитного диэлектрика, покрывающего металлизации первого и второго уровней, резистивный слой и второй слой защитного диэлектрика, при этом металлизация первого уровня включает последовательно расположенные слой диффузионного барьера, слой Cu и проводящий защитный слой, металлизация второго уровня включает последовательно расположенные адгезионный слой и слой Cu, металлизация обратной стороны содержит слой Cu, отличающаяся тем, что введены четвертый слой защитного диэлектрика, расположенный на поверхности третьего слоя защитного диэлектрика, металлизация третьего уровня, частично расположенная на поверхности четвертого слоя защитного диэлектрика, частично на поверхности металлизации второго уровня в специально сформированных окнах в третьем и четвертом слоях защитного диэлектрика, при этом омические контакты и затвор включают слой Al, в металлизации первого уровня слой диффузионного барьера выполнен по площади осаждения шире, чем слой Cu, и проводящий защитный слой покрывает как верхнюю планарную, так и все торцевые поверхности слоя Cu, а металлизация обратной стороны включает последовательно расположенные на полупроводниковой пластине выравнивающий слой Ni, слой диффузионного барьера, слой Cu и проводящий защитный слой.

2. МИС по п. 1, отличающаяся тем, что омический контакт включает последовательно расположенные слои Pd, Ge и Al соответственно толщиной 5-200 нм, 5-500 нм и 5-500 нм.

3. МИС по п. 1, отличающаяся тем, что затвор включает последовательно расположенные барьерный слой Ti и слой Al соответственно толщиной 5-500 нм и 5-1000 нм.

4. МИС по п. 1, отличающаяся тем, что нижняя обкладка конденсаторов включает последовательно расположенные слой диффузионного барьера, слой Cu и проводящий защитный слой соответственно толщиной 5-500 нм, 5-3000 нм и 5-500 нм, при этом слой диффузионного барьера по площади осаждения шире, чем слой Cu, и проводящий защитный слой покрывает как верхнюю планарную, так и все торцевые поверхности слоя Cu.

5. МИС по п. 1, отличающаяся тем, что нижняя обкладка конденсаторов включает последовательно расположенные барьерный слой Ti и слой Al соответственно толщиной 5-500 нм и 5-1000 нм.

6. МИС по п. 1, отличающаяся тем, что в металлизации первого уровня слои диффузионного барьера, слой Cu и проводящий защитный слой выполнены соответственно толщиной 5-500 нм, 5-3000 нм и 5-500 нм.

7. МИС по п. 1, отличающаяся тем, что в металлизации второго уровня адгезионный слой и слой Cu выполнены соответственно толщиной 5-500 нм и 5-5000 нм.

8. МИС по п. 1, отличающаяся тем, что четвертый слой защитного диэлектрика выполнен на основе слоя органического диэлектрика толщиной 1000-30000 нм.

9. МИС по п. 1, отличающаяся тем, что в качестве слоя органического диэлектрика используют бензоциклобутен.

10. МИС по п. 2, или 3, или 5, отличающаяся тем, что дополнительно введен проводящий защитный слой на основе слоя Мо, или Ti, или Та, или W, или TaNx, или TiNx, или WNx, а также их комбинаций толщиной 5-500 нм, расположенный на поверхности слоя Al.

11. МИС по п. 2, или 3, или 5, отличающаяся тем, что дополнительно введен стоп-слой травления на основе слоя Ni толщиной 5-500 нм, расположенный на поверхности слоя Al.

12. МИС по п. 10, отличающаяся тем, что дополнительно введен стоп-слой травления на основе слоя Ni толщиной 5-500 нм, расположенный на поверхности проводящего защитного слоя.

13. МИС по п. 1, отличающаяся тем, что в качестве материала слоя диффузионного барьера и проводящего защитного слоя металлизации первого уровня и нижней обкладки конденсаторов используют слой Мо, или Та, или W, или TaNx, или TiNx, или WNx, а также их комбинации.

14. МИС по п. 1, отличающаяся тем, что в металлизации второго уровня в качестве материала адгезионного слоя используют слой Мо, или Та, или W, или TaNx, или TiNx, а также их комбинации.

15. МИС по п. 1, отличающаяся тем, что в металлизации обратной стороны выравнивающий слой Ni, слой диффузионного барьера и слой Cu выполнены соответственно толщиной 5-5000 нм, 5-500 нм и 5-30000 нм.

16. МИС по п. 1, отличающаяся тем, что в качестве материала слоя диффузионного барьера металлизации обратной стороны используют слой Мо, или Та, или W, или TaNx, или TiNx, или WNx, а также их комбинации.

17. МИС по п. 1, отличающаяся тем, что в качестве материала проводящего защитного слоя металлизации обратной стороны используют слой Мо, или Та, или W, или TaNx, или TiNx, или WNx, или Au, или двухслойной композиции Ni/Au толщиной 5-300 нм.

18. МИС по п. 1, отличающаяся тем, что в качестве материала проводящего защитного слоя металлизации обратной стороны используют слой SnPb, или AgCuSn, или двухслойные композиции Ni/SnPb, или Ni/AgCuSn толщиной 100-10000 нм.

| Многоступенчатая активно-реактивная турбина | 1924 |

|

SU2013A1 |

| Способ защиты переносных электрических установок от опасностей, связанных с заземлением одной из фаз | 1924 |

|

SU2014A1 |

| Способ и приспособление для нагревания хлебопекарных камер | 1923 |

|

SU2003A1 |

| US 7557034 B2, 07.07.2009 | |||

| US 8310033 B2, 13.11.2012 | |||

| МОНОЛИТНАЯ ИНТЕГРАЛЬНАЯ СХЕМА МИЛЛИМЕТРОВОГО ДИАПАЗОНА | 2012 |

|

RU2503087C1 |

Авторы

Даты

2016-10-27—Публикация

2015-07-08—Подача