Изобретение относится к радиотехнике, служит для преобразования аналоговых знакопеременных сигналов в прямоугольные импульсы и может быть использовано при построении цифровых средств обработки сигналов и измерении их параметров.

Как правило в качестве устройства для клиппирования сигналов применяют аналоговый компаратор, на один из входов которого подают аналоговый клиппируемый сигнал, а на другой - пороговый уровень, равный нулю или близкий к нему, см., например, [Справочник по нелинейным схемам / Под ред. Д. Шейнголда. - М.: Мир, 1977, стр. 20-22]. Хорошо известным недостатком такого устройства является его невысокая помехоустойчивость. Наличие помех на входе компаратора приводит к появлению серии коротких ложных импульсов вблизи фронтов выходного импульса, что объясняется многократным пересечением порогового уровня входным сигналом в областях, где его мгновенные значения близки к пороговому уровню. Для исключения появления ложных импульсов используют два наиболее распространенных способа. Первый предусматривает формирование, в ответ на первое срабатывание компаратора, «чистого» импульса, длительность которого задается введенным в схему одновибратором, подключенным к выходу компаратора. Такой подход обеспечивает эффективное подавление ложных импульсов, но и имеет ограниченное применение, поскольку в выходной последовательности импульсов сохраняется лишь информация о моментах пересечения сигналом порогового уровня при его переходе через нуль только при одном знаке производной (при смене знака мгновенных значений в одном направлении), и теряется информация о длительностях полуволн клиппируемых сигналов. Больше информации позволяет сохранить второй способ, предусматривающий введение в переключательную характеристику устройства гистерезиса, то есть задания уровня включения UITP и уровня выключения UITN, для которых соблюдается условие: UITP>UITN [Аванесян Г.Р. Цифровые интегральные микросхемы. Справочное пособие. - М.: Радиотехника, 2008, стр. 93-93, рис. 2.19]. В этом случае при уровне помех, определяемом шириной искусственно созданной петли гистерезиса, удается избежать появления ложных импульсов, но при этом искажается длительность выходного импульса. Если пороговые уровни имеют один знак, длительность уменьшается. Причем искаженным будет выходной импульс как при наличии помех, так и при их полном отсутствии или незначительном уровне, не приводящем к многократным срабатывания компаратора. Примером такого устройства, в котором предусмотрена возможность управления пороговыми уровнями (уровнями срабатывания), является техническое решение, описанное в [Пат. RU 2007855. Опубл. 15.02.1994], принятое за прототип. Указанное устройство содержит два компаратора и D-триггер, выход которого является выходом устройства, а входом - объединенные прямой вход первого компаратора и инвертирующий вход второго компаратора, инвертирующий вход первого компаратора является входом первого порогового напряжения, прямой вход второго компаратора - входом второго порогового напряжения, выход второго компаратора соединен с тактовым входом D-триггера, выход первого компаратора через дифференцирующую цепочку соединен со входом асинхронной установки в единицу D-триггера, D-вход которого соединен с его инверсным выходом.

Технический результат, достигаемый при использовании настоящего изобретения, состоит главным образом в возможности получения импульсов неискаженной длительности в отсутствие помех и снижения искажений импульсов при наличии помех.

Технический результат по варианту 1 достигается тем, что в устройство с обратной связью для для клиппирования знакопеременных сигналов, содержащее два компаратора и D-триггер, выход которого является выходом устройства, а входом - объединенные прямой вход первого компаратора и инвертирующий вход второго компаратора, согласно изобретению, введены второй D-триггер, элемент задержки и элемент И, выход первого компаратора соединен с тактовым входом первого D-триггера, D-вход которого является входом фиксированного уровня логической единицы, выход второго компаратора соединен с обнуляющим входом второго D-триггера, тактовый вход которого соединен с выходом элемента И, первый вход которого соединен с выходом элемента задержки, вход которого соединен с выходом первого D-триггера, обнуляющий вход которого соединен с выходом второго D-триггера, D-вход которого является входом фиксированного уровня логической единицы, второй вход элемента И соединен с инверсным выходом второго компаратора, инвертирующий вход первого компаратора является входом первого порогового напряжения, прямой вход второго компаратора является входом второго порогового напряжения.

Технический результат по варианту 2 достигается тем, что в устройство с обратной связью для клиппирования знакопеременных сигналов, содержащее компаратор и D-триггер, выход которого является выходом устройства, а входом - прямой вход первого компаратора, согласно изобретению, введены элемент задержки и элемент И, выход компаратора соединен с тактовым входом D-триггера, D-вход которого является входом фиксированного уровня логической единицы, выход D-триггера соединен с элементом задержки, выход которого соединен с первым входом элемента И, второй вход которого соединен с инверсным выходом компаратора, выход элемента И соединен с обнуляющим входом D-триггера, инвертирующий вход компаратора является входом порогового напряжения.

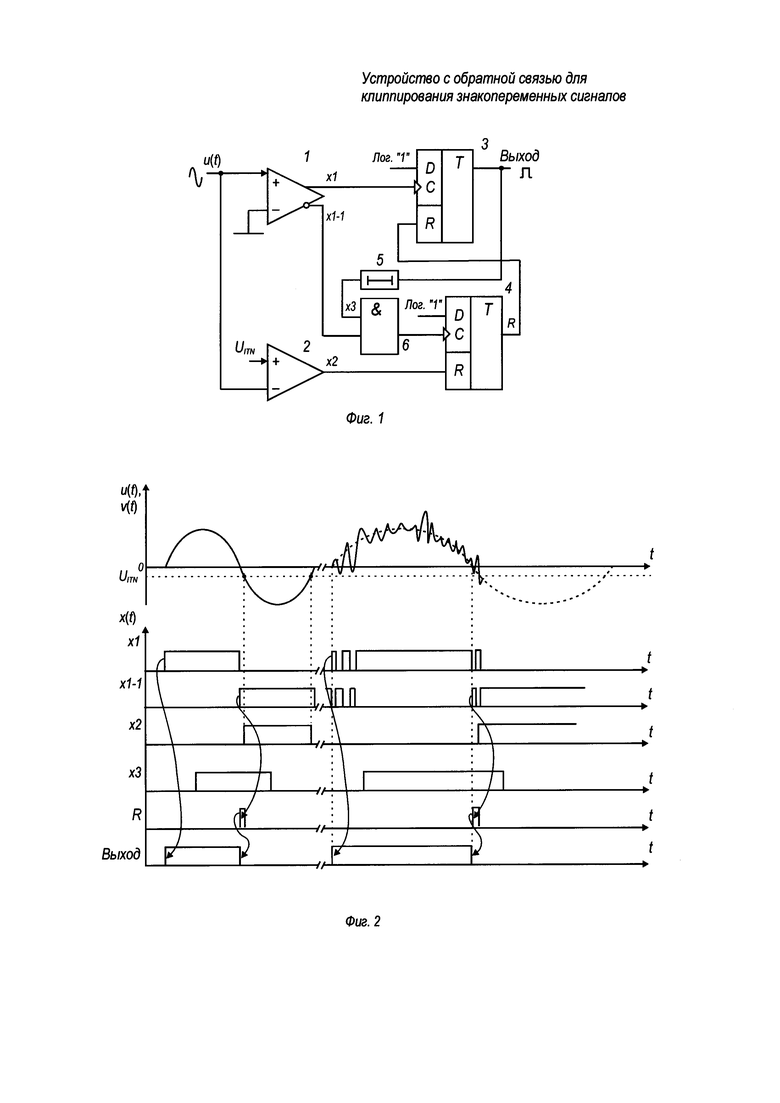

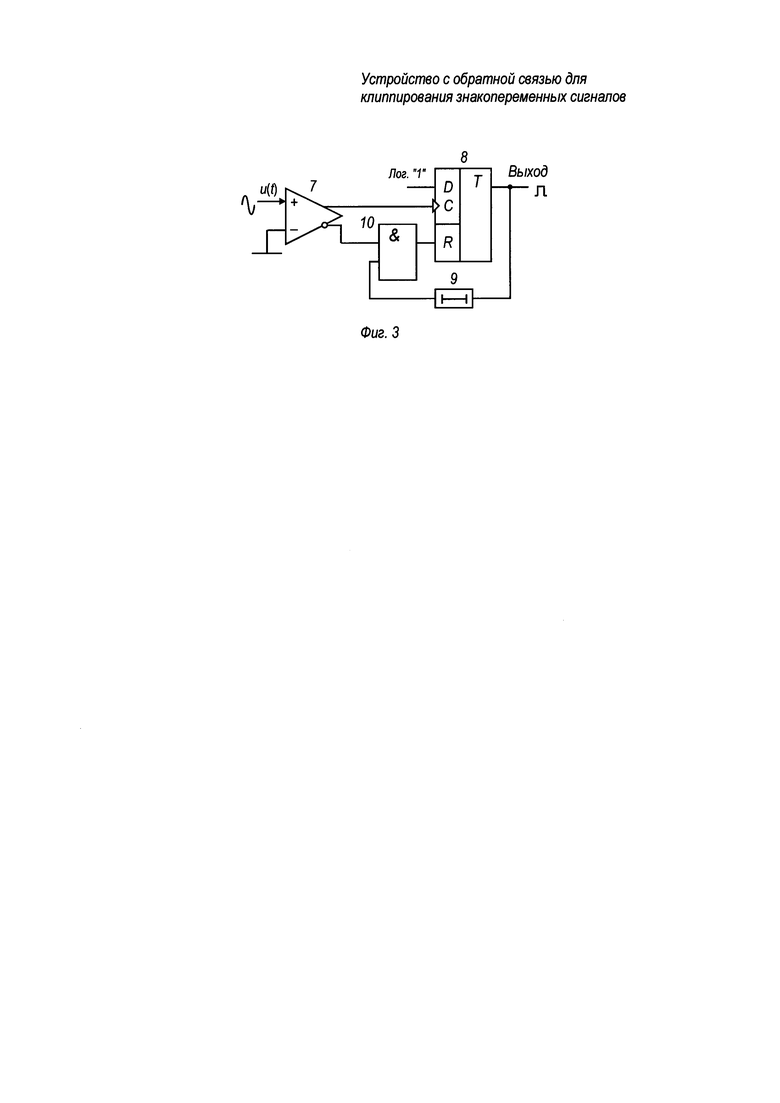

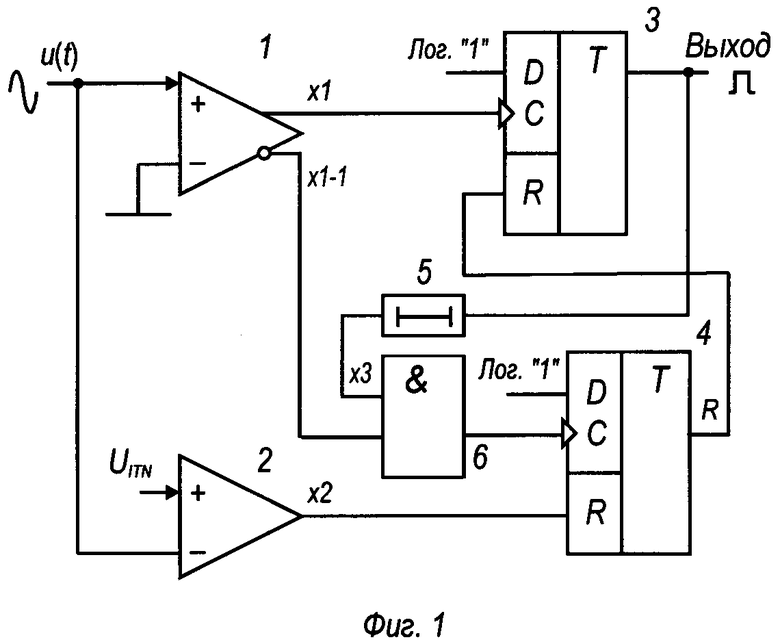

Сущность изобретения иллюстрируется графическим материалом. На фиг. 1 показана функциональная схема устройства по варианту 1, на фиг. 2 - временные диаграммы, поясняющие принцип действия указанного устройства, на фиг. 3 - функциональная схема устройства по варианту 2.

Функциональная схема, представленная на фиг. 1, содержит два аналоговых компаратора 1, 2, два D-триггера 3, 4, элемент 5 задержки и логический элемент И 6. Входом u(t) устройства являются объединенные входы компараторов 1, 2 (прямой и инвертирующий), выход компаратора 1 соединен с тактовым входом D-триггера 3, D-вход которого является входом фиксированного уровня логической единицы, выход D-триггера 3 является выходом устройства и соединен со входом элемента 5 задержки, выход которой соединен с первым входом элемента И 6, второй вход которого соединен с инверсным выходом компаратора 1, выход элемента И 6 соединен с тактовым входом D-триггера 4, выход которого соединен со входом асинхронного обнуления D-триггера 3, D-вход D-триггера 4 является входом фиксированного уровня логической единицы, а вход асинхронного обнуления соединен с выходом компаратора 2, инвертирующий вход компаратора 1 соединен с шиной нулевого потенциала, прямой вход компаратора 2 является входом порогового напряжения UITN.

Временные диаграммы (фиг. 2) содержат входной u(t) синусоидальный сигнал без помех (слева на графике) и обогащенный помехами (справа), а также импульсы:

- на выходе компаратора 1 - x1;

- на инверсном выходе компаратора 1 - x1-1;

- на выходе компаратора 2 - х2;

- на выходе элемента 5 задержки - х3;

- на выходе D-триггера 4 - R;

- на выходе устройства.

Функциональная схема по фиг. 3 содержит компаратор 7, D-триггер 8, элемент 9 задержки и логический элемент И 10, прямой вход компаратора является входом устройства, а инвертирующий вход соединен с шиной нулевого потенциала, выход компаратора 7 соединен с тактовым входом D-триггера 8, D-вход которого является входом фиксированного уровня логической единицы, выход D-триггера 8 соединен со входом элемента 9 задержки, выход которого соединен с первым входом элемента И 10, второй вход которого соединен с инверсным выходом компаратора 7, выход элемента И 10 соединен со входом асинхронного обнуления D-триггера 8, выход которого является выходом устройства.

Работает устройство (см. фиг. 1) следующим образом. При поступлении на вход аналогового знакопеременного сигнала u(t), например, синусоидального, как показано на фиг. 2 слева, в момент пересечения им нулевого уровня, при смене знака с отрицательного на положительный срабатывает компаратор 1 (на выходе x1 устанавливается высокий логический уровень) и по переднему фронту импульса на его выходе D-триггер 3 переходит в состояние логической единицы на выходе (формируется передний фронт выходного импульса). С задержкой Δt, на выходе элемента 5 (выход х3) также появляется высокий логический уровень, передаваемый на первый вход (верхний по схеме) элемента И 6. В момент перехода через нуль, обусловленного возвратом значений сигнала u(t) в отрицательную область, появляется положительный перепад напряжений на инверсном выходе компаратора 1 (выход x1-1), который, воздействуя на нижний по схеме вход элемента И 6, приводит к появлению на выходе последнего и соответственно на тактовом входе D-триггера 4 импульса, переводящего указанный триггер в состояние логической единицы. В результате появляется обнуляющий логический уровень (выход R) на обнуляющем входе D-триггера 3, переводя последний в состояние низкого логического уровня на выходе - таким образом формируется задний фронт выходного импульса. Через время, необходимое сигналу u(t), находящемуся в отрицательной области, для достижения уровня UITN, появляется перепад напряжений на выходе компаратора 2 (выход х2), обнуляющий D-триггер 4.

Описанная работа устройства происходила в предположении, что помехи на входе отсутствовали и клиппированию подвергался чистый синусоидальный сигнал. Из показанного, включая содержание левой части временных диаграмм, соответствующей синусоидальному входному воздействию, несложно видеть, что фронты выходного импульса формировались строго в моменты перехода сигналом нулевого уровня, то есть клиппирование происходило без искажений, с сохранением длительности импульса, равной длительности положительной полуволны входного сигнала.

Рассмотрим далее типичный на практике случай поступления на вход устройства сигнала v(t)=u(t)+n(t), представляющего собой сумму синусоидального полезного сигнала u(t) и помех n(t), как показано в правой части временных диаграмм по фиг. 2. При первом же пересечении нулевого уровня сигналом v(t) в области, соответствующей условию  , срабатывает компаратор 1, и D-триггер 3 переходит в состояние высокого логического уровня на выходе, формируя таким образом передний фронт выходного импульса. Следующие случайные пересечения нулевого уровня, вызванные возвратом сигнала в отрицательную область и выходом из нее, на состоянии выхода устройства не отражаются, так как ложные импульсы в окрестности переднего фронта выходного импульса уже не могут оказать влияния на состояния D-триггеров 3 и 4. Обеспечивается подобная защита от ложных переключений наличием задержанной обратной связи, включающей элемент 5 задержки, который блокирует на время Δt, в течение которого возможны хаотичные пересечения нулевого уровня входным сигналом v(t), поступление импульсов на выход элемента И 6 - тактовый вход D-триггера 4. Таким образом, обнуление D-триггера 3 становится возможным не раньше чем через время Δt и наступает по первому положительному перепаду напряжений на инверсном выходе компаратора 1, появившемуся через время, равное или большее Δt. Указанный перепад напряжений приводит к формированию отрицательного фронта выходного импульса. Причем из-за воздействия помех этим перепадом может быть передний фронт первого короткого импульса из серии ложных импульсов в окрестности отрицательного фронта импульса на выходе компаратора 1 (выход x1). Однако снятие активного уровня обнуления с обнуляющего входа D-триггера 3 произойдет только после того, как случайная составляющая сигнала v(t) не сможет вернуть D-триггер 3 в состояние высокого логического уровня на выходе. Это обеспечивается заданием такого значения напряжения отключения UITN, при котором изменения мгновенных значений n(t) уже не переведут сигнал v(t) в положительную область. Для этого UITN выбирают исходя из условия:

, срабатывает компаратор 1, и D-триггер 3 переходит в состояние высокого логического уровня на выходе, формируя таким образом передний фронт выходного импульса. Следующие случайные пересечения нулевого уровня, вызванные возвратом сигнала в отрицательную область и выходом из нее, на состоянии выхода устройства не отражаются, так как ложные импульсы в окрестности переднего фронта выходного импульса уже не могут оказать влияния на состояния D-триггеров 3 и 4. Обеспечивается подобная защита от ложных переключений наличием задержанной обратной связи, включающей элемент 5 задержки, который блокирует на время Δt, в течение которого возможны хаотичные пересечения нулевого уровня входным сигналом v(t), поступление импульсов на выход элемента И 6 - тактовый вход D-триггера 4. Таким образом, обнуление D-триггера 3 становится возможным не раньше чем через время Δt и наступает по первому положительному перепаду напряжений на инверсном выходе компаратора 1, появившемуся через время, равное или большее Δt. Указанный перепад напряжений приводит к формированию отрицательного фронта выходного импульса. Причем из-за воздействия помех этим перепадом может быть передний фронт первого короткого импульса из серии ложных импульсов в окрестности отрицательного фронта импульса на выходе компаратора 1 (выход x1). Однако снятие активного уровня обнуления с обнуляющего входа D-триггера 3 произойдет только после того, как случайная составляющая сигнала v(t) не сможет вернуть D-триггер 3 в состояние высокого логического уровня на выходе. Это обеспечивается заданием такого значения напряжения отключения UITN, при котором изменения мгновенных значений n(t) уже не переведут сигнал v(t) в положительную область. Для этого UITN выбирают исходя из условия:

,

,

где  - максимально возможное мгновенное значение модуля помехи n(t). Выбор указанным образом модуля напряжения UITN, которое обязательно должно быть отрицательным, приведет к тому, что импульс асинхронного обнуления R будет удерживать D-триггер 3 в обнуленном состоянии до тех пор, пока мгновенные значения сигнала v(t) гарантированно не окажутся в отрицательной области.

- максимально возможное мгновенное значение модуля помехи n(t). Выбор указанным образом модуля напряжения UITN, которое обязательно должно быть отрицательным, приведет к тому, что импульс асинхронного обнуления R будет удерживать D-триггер 3 в обнуленном состоянии до тех пор, пока мгновенные значения сигнала v(t) гарантированно не окажутся в отрицательной области.

Из вышеизложенного, включая правую часть временных диаграмм (см. фиг. 2), видно, что как при наличии помех, так и при их отсутствии передний фронт выходного импульса формируется строго в момент первого пересечения нулевого уровня входным сигналом при смене знака с отрицательного на положительный, а задний - при первом пересечении нулевого уровня при смене знака с положительного на отрицательный. Снижение искажений длительности выходного импульса при воздействии помех объясняется тем, что порог срабатывания находится на уровне нулевого потенциала и отсутствует дополнительное смещение фронта импульса, вызванное отличным от нуля пороговым напряжением, свойственным схемам с гистерезисом.

Существенную роль в функционировании устройства играет корректный выбор значения Δt. Время Δt следует выбирать, с одной стороны, исходя из продолжительности действия ложных коротких импульсов tn, а с другой - с учетом верхней границы диапазона рабочих частот устройства, то есть наименьшего периода Tmin сигнала. В качестве оценки можно рекомендовать выбор Δt из неравенства

tn<Δt<(0,2-0,3)Tmin.

Некоторые трудности у разработчика может вызывать правильный выбор значения tn, которое зависит как от уровня помех n(t), так и от амплитуды и частоты входного сигнала. Причем, если с ростом n(t) величина tn также должна расти, то с ростом амплитуды и/или частоты время tn должно уменьшаться. Наиболее точные сведения можно получить, исходя из предварительной экспериментальной оценки помеховой ситуации и знаний о параметрах рабочих сигналов. В отсутствие же априорных эмпирических данных следует исходить из крайнего максимального значения (0,2-0,3)Tmin. Кроме того, в ряде случаев для расширения диапазона рабочих частот устройства может оказаться полезным управление временем Δt путем его изменения в соответствии с изменением значений Tmin.

В отсутствие полезного сигнала, при наличии на входе только помех, при условии, что инвертирующий вход компаратора 1 соединен с шиной нулевого потенциала, на выходе устройства будет присутствовать низкий логический уровень, поскольку первые срабатывания компаратора 1 под воздействием помех приведут к установке логической единицы на выходе не только D-триггера 3, но D-триггера 4. Последний примерно через время Δt от начала работы переведет D-триггер 3 в исходное нулевое состояние и будет удерживать его в этом состоянии до поступления полезного сигнала, поскольку для снятия обнуляющего уровня (выход R) необходим сигнал, превосходящий по модулю порог UITN.

Упрощенной версией устройства для клиппирования знакопеременных сигналов является показанное на схеме по фиг. 3. Передний фронт импульса на выходе устройства - выходе D-триггера 8 - формируется аналогично рассмотренному выше в момент первого пересечения порогового уровня, а задний при появлении первого через время Δt отрицательного перепада напряжений на выходе компаратора 7. Задержку Δt выбирают в соответствии с вышеприведенными рекомендациями. Особенностью устройства является наличие выходной последовательности импульсов при отсутствии полезного сигнала, но наличии помех (клиппированию может подвергаться шум на входе), что ограничивает области применения устройства. В то же время в тех случаях, когда наличие входного сигнала является обязательным требованием, а присутствие помех неизбежно, и частота меняется в небольших пределах, устройство по эффективности оказывается не хуже представленного на фиг. 1 и предпочтительней, поскольку проще, надежней и имеет меньшее энергопотребление.

Изобретение относится к радиотехнике, служит для преобразования аналоговых знакопеременных сигналов в прямоугольные импульсы и может быть использовано при построении цифровых средств обработки сигналов и измерении их параметров. Технический результат, достигаемый при использовании настоящего изобретения, состоит главным образом в возможности получения импульсов неискаженной длительности в отсутствие помех и снижения искажений импульсов при наличии помех. Особенностью устройства является наличие задержанной обратной связи, позволяющей блокировать появление коротких ложных импульсов в окрестности фронтов формируемых импульсов. При этом формирование переднего фронта выходного импульса происходит строго в момент первого пересечения сигналом нулевого уровня при переходе от отрицательных значений к положительным, а заднего - при переходе от положительных значений к отрицательным при условии, что напряжение на входе превысило порог возможных помех. Основу устройства составляют два компаратора, два триггера и элемент задержки, в упрощенной версии - один компаратор, один триггер и элемент задержки. 2 н. и 6 з.п. ф-лы, 3 ил.

1. Устройство с обратной связью для клиппирования знакопеременных сигналов, содержащее два компаратора и D-триггер, выход которого является выходом устройства, а входом - объединенные прямой вход первого компаратора и инвертирующий вход второго компаратора, отличающееся тем, что в него введены второй D-триггер, элемент задержки и элемент И, выход первого компаратора соединен с тактовым входом первого D-триггера, D-вход которого является входом фиксированного уровня логической единицы, выход второго компаратора соединен с обнуляющим входом второго D-триггера, тактовый вход которого соединен с выходом элемента И, первый вход которого соединен с выходом элемента задержки, вход которого соединен с выходом первого D-триггера, обнуляющий вход которого соединен с выходом второго D-триггера, D-вход которого является входом фиксированного уровня логической единицы, второй вход элемента И соединен с инверсным выходом второго компаратора, инвертирующий вход первого компаратора является входом первого порогового напряжения, прямой вход второго компаратора является входом второго порогового напряжения.

2. Устройство по п. 1, отличающееся тем, что первое пороговое напряжение выбирают равным нулю, а второе пороговое напряжение - отрицательным, при этом его абсолютное значение меньше амплитуды клиппируемых сигналов.

3. Устройство по п. 1, отличающееся тем, что первое пороговое напряжение выбирают положительными, а второе пороговое напряжение - отрицательным, при этом их абсолютные значения меньше амплитуды клиппируемых сигналов.

4. Устройство по п. 1, отличающееся тем, что элемент задержки выполнен в виде элемента с управляемой задержкой.

5. Устройство с обратной связью для клиппирования знакопеременных сигналов, содержащее компаратор и D-триггер, выход которого является выходом устройства, а входом - прямой вход первого компаратора, отличающееся тем, что в него введены элемент задержки и элемент И, выход компаратора соединен с тактовым входом D-триггера, D-вход которого является входом фиксированного уровня логической единицы, выход D-триггера соединен с элементом задержки, выход которого соединен с первым входом элемента И, второй вход которого соединен с инверсным выходом компаратора, выход элемента И соединен с обнуляющим входом D-триггера, инвертирующий вход компаратора является входом порогового напряжения.

6. Устройство по п. 5, отличающееся тем, что пороговое напряжение выбирают равным нулю.

7. Устройство по п. 5, отличающееся тем, что пороговое напряжение выбирают положительным и меньшим амплитуды клиппируемых сигналов.

8. Устройство по п. 5, отличающееся тем, что элемент задержки выполнен в виде элемента с управляемой задержкой.

| ПОРОГОВОЕ УСТРОЙСТВО | 1991 |

|

RU2007855C1 |

| СЕНСОР ДЛЯ ОБНАРУЖЕНИЯ ДВИЖУЩИХСЯ ОБЪЕКТОВ ПРИ ПОМОЩИ СВЕРХШИРОКОПОЛОСНОГО ЗОНДИРУЮЩЕГО СИГНАЛА (ВАРИАНТЫ) | 2006 |

|

RU2311658C9 |

| EP 0875733 A2, 01.04.1998. | |||

Авторы

Даты

2017-01-11—Публикация

2015-10-05—Подача