Изобретение относится к области радиотехники и предназначено для формирования периодической последовательности импульсов с упреждающей задержкой относительно исходной последовательности, что, в частности, необходимо для компенсации задержек возникающих в каналах связи.

Для получения упреждающей задержки τ периодической последовательности импульсов, при известном периоде Т следования импульсов, достаточно задержать входной сигнал на время T-τ. При этом, учитывая периодичность сигнала, будет получена копия, опережающая входной сигнал на время τ - время упреждения. Реализация такого подхода трудностей не вызывает, и в качестве устройства упреждающего временного сдвига может быть применена, в частности, цифровая линия задержки, позволяющая задерживать сигнал на требуемое время, описанная в [А.с. СССР SU 1431053. Устройство временной задержки. Опубл. 15.10.1988, Бюл. №38] и выбранная в качестве прототипа. Устройство содержит три триггера, два счетчика, два дешифратора, четыре логических элемента И и два инвертора; предусмотрены информационный вход, на который поступают задерживаемые импульсы и отдельно управляющий вход, на который подают информацию о вводимой задержке. Каждый поступающий на вход такого устройства импульс будет задерживаться на время (T-τ)+Δt, где Δt - погрешность формируемой задержки, носящая случайный характер. Таким образом, при наличии на входе последовательности импульсов с высокостабильной фазой выходная последовательность импульсов будет случайным образом смещаться относительно исходной в пределах, обусловленных погрешностью конкретного устройства. Указанное является недостатком как прототипа, так и в целом традиционного подхода, реализуемого в цифровых устройствах задержки импульсов (в аналоговых устройствах этот недостаток проявляется в гораздо меньшей степени, однако они не позволяют получать широкий диапазон задержек с требуемым разрешением).

Технический результат, достигаемый при использовании настоящего изобретения, состоит в снижении фазовых флуктуаций выходного сигнала.

Технический результат по первому варианту достигается тем, что в устройство упреждающего временного сдвига импульсов, содержащее триггер и счетчик, согласно изобретению, введен блок задания коэффициента пересчета, выход которого является выходом устройства, информационным входом которого служит тактовый вход триггера, выход которого соединен со входом разрешения счетчика и обнуляющим входом блока задания коэффициента пересчета, обнуляющий вход счетчика соединен с выходом блока задания коэффициента пересчета, информационный вход которого соединен с выходом счетчика, счетный вход которого является тактовым входом устройства, стартовым и обнуляющим входами которого являются соответственно D-вход триггера и его обнуляющий вход.

Технический результат по второму варианту достигается тем, что в устройство упреждающего временного сдвига импульсов, содержащее триггер и счетчик, согласно изобретению, введен блок задания коэффициента пересчета, выход которого соединен с обнуляющим входом счетчика, информационным входом которого служит тактовый вход триггера, выход которого соединен со входом разрешения счетчика и обнуляющим входом блока задания коэффициента пересчета, информационный вход которого соединен с выходом счетчика, счетный вход которого является тактовым входом устройства, стартовым и обнуляющим входами которого являются соответственно D-вход триггера и его обнуляющий вход, выходом устройства служит выход переноса счетчика.

Технический результат по третьему варианту достигается тем, что в устройство упреждающего временного сдвига импульсов, содержащее триггер и счетчик, согласно изобретению, введены блок задания коэффициента пересчета, одновибратор и логический элемент И, выход которого является выходом устройства, информационным входом которого служит тактовый вход триггера, выход которого соединен со входом разрешения счетчика и обнуляющим входом блока задания коэффициента пересчета, обнуляющий вход счетчика соединен с выходом блока задания коэффициента пересчета, информационный вход которого соединен с выходом счетчика, счетный вход которого является тактовым входом устройства, стартовым и обнуляющим входами которого являются соответственно D-вход триггера и его обнуляющий вход, первый вход логического элемента И соединен с выходом блока задания коэффициента пересчета, а второй вход - с выходом одновибратора, вход которого объединен с тактовым входом триггера.

Технический результат по четвертому варианту достигается тем, что в устройство упреждающего временного сдвига импульсов, содержащее триггер и счетчик, согласно изобретению, введен регистр, выход которого соединен с информационным входом счетчика, выход переноса которого является выходом устройства, тактовым входом которого является счетный вход счетчика, разрешающий вход которого соединен с прямым выходом триггера, а вход управления загрузкой данных счетчика соединен с инверсным выходом триггера, стартовым и обнуляющим входами устройства являются соответственно D-вход триггера и его обнуляющий вход, информационным входом устройства является тактовый вход триггера.

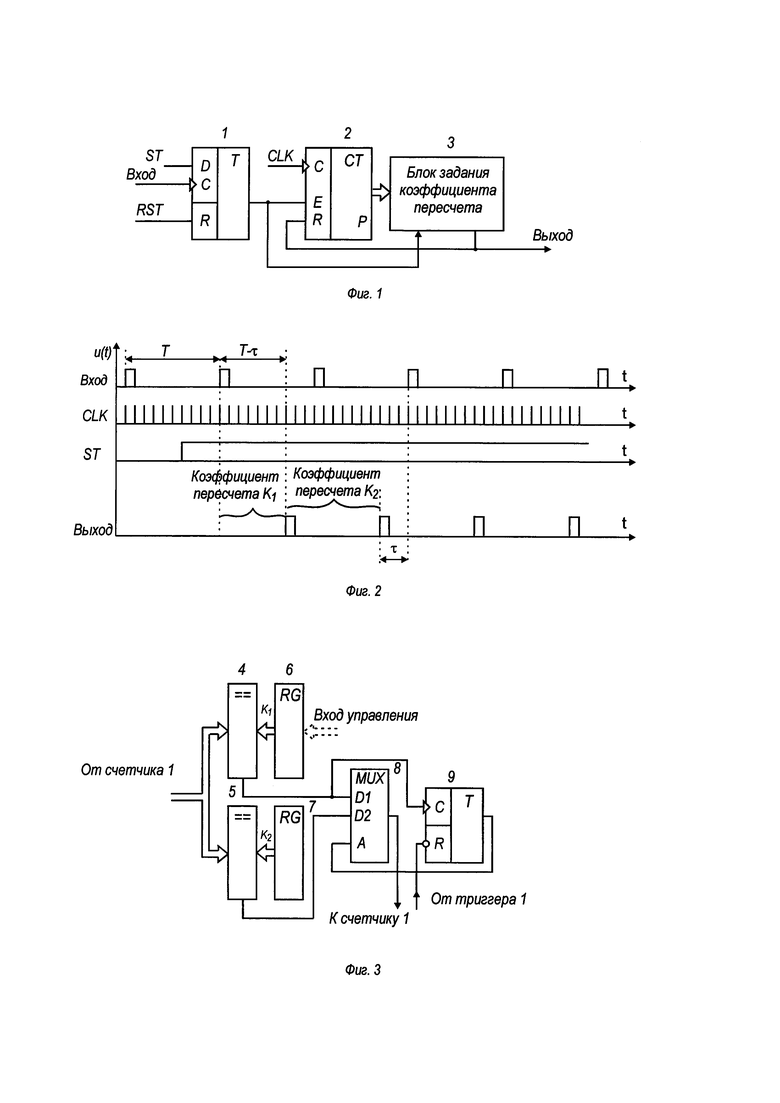

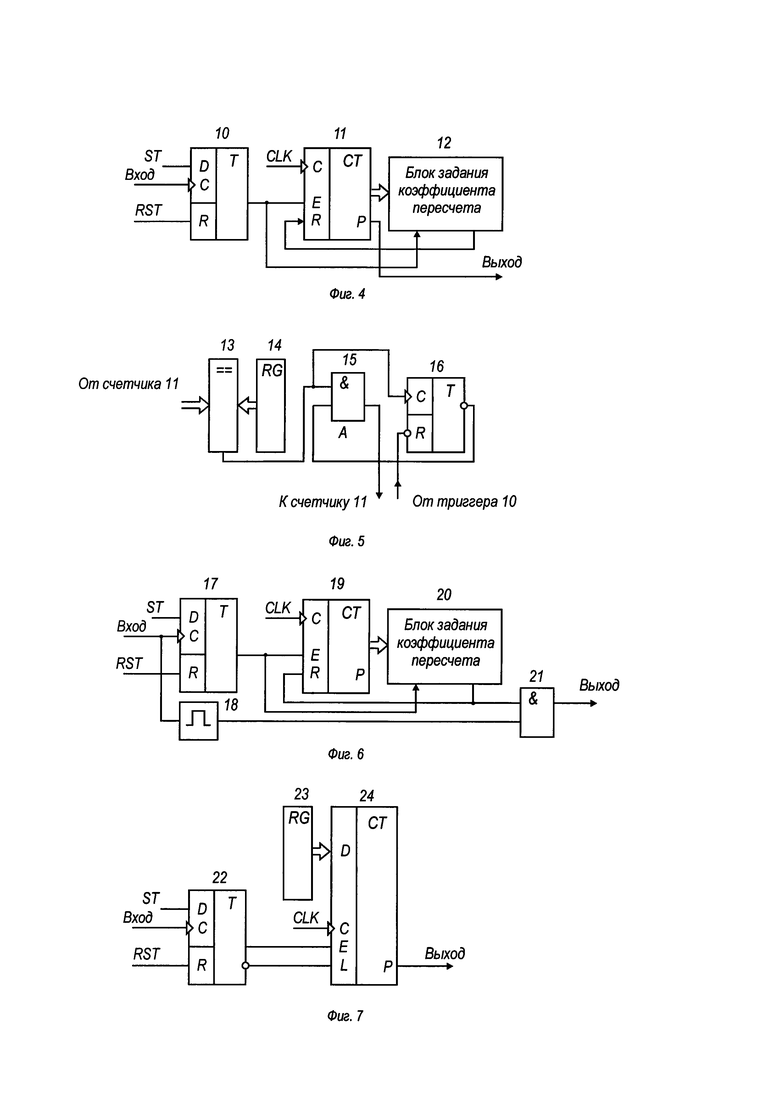

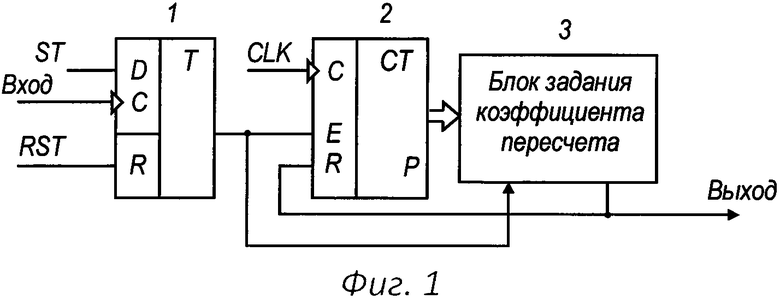

Сущность изобретения поясняется графическим материалом. На фиг. 1 показана функциональная схема первого варианта устройства. На фиг. 2 приведены временные диаграммы, поясняющие принцип действия устройства. На фиг. 3, в виде функциональной схемы, представлен один из возможных вариантов реализации блока задания коэффициента пересчета для применения в устройстве по первому варианту. На фиг. 4 показана функциональная схема второго варианта устройства, а на фиг. 5 - схема блока задания коэффициента пересчета для применения в устройстве по второму варианту. На фиг. 6 показана функциональная схема третьего варианта устройства, а на фиг. 7 - схема четвертого варианта.

Функциональная схема по фиг. 1 содержит триггер 1, счетчик 2 и блок 3 задания коэффициента пересчета, выход которого является выходом устройства, информационным входом которого служит тактовый вход С триггера 1, выход которого соединен со входом разрешения счетчика 2 и обнуляющим входом блока 3 задания коэффициента пересчета, обнуляющий вход счетчика 2 соединен с выходом блока 3 задания коэффициента пересчета, информационный вход которого соединен с выходом счетчика 2, счетный вход которого является тактовым входом CLK устройства, стартовым ST и обнуляющим RST входами которого являются соответственно D-вход триггера 1 и его обнуляющий вход.

На временных диаграммах по фиг. 2 показаны входные импульсы следующие с периодом Т, тактовые импульсы CLK, поступающие на тактовый вход устройства, перепад напряжений на стартовом входе ST устройства и импульсы на выходе устройства.

Функциональная схема по фиг. 3 содержит два компаратора 4, 5, два регистра 6, 7, мультиплексор 8 и триггер 9, выход которого соединен с адресным входом мультиплексора 8, первый и второй информационные входы которого соединены с выходами соответственно компараторов 4 и 5, первые информационные входы которых объединены и составляют информационный вход блока, второй информационный вход компаратора 4 соединен с выходом регистра 6, второй информационный вход компаратора 5 соединен с выходом регистра 7, выход мультиплексора 8 является выходом блока, тактовый вход триггера соединен с выходом первого компаратора, инвертирующий обнуляющий вход триггера является обнуляющим входом блока.

Функциональная схема по фиг. 4 содержит триггер 10, счетчик 11 и блок 12 задания коэффициента пересчета, выход которого соединен с обнуляющим входом счетчика 11, информационным входом которого служит тактовый вход С триггера 10, выход которого соединен со входом разрешения счетчика 11 и обнуляющим входом блока 12 задания коэффициента пересчета, информационный вход которого соединен с выходом счетчика 11, счетный вход которого является тактовым входом CLK устройства, стартовым ST и обнуляющим RST входами которого являются соответственно D-вход триггера 10 и его обнуляющий вход, выходом устройства служит выход переноса счетчика.

Функциональная схема по фиг. 5 содержит компаратор 13 двоичных кодов, регистр 14, логический элемент И 15 и триггер 16, выход элемента И 15 является выходом блока, тактовый вход триггера 16 объединен с первым входом элемента И 15 и соединен с выходом компаратора 13, инвертирующий обнуляющий вход триггера 16 является обнуляющим входом блока, инверсный выход триггера 15 соединен со вторым входом элемента И 15, первый вход компаратора 13 является информационным входом блока, а второй вход соединен с выходом регистра 14.

Функциональная схема по фиг. 6 содержит триггер 17, одновибратор 18, счетчик 19, блок 20 задания коэффициента пересчета и логический элемент И 21, выход которого является выходом устройства, информационным входом которого служит тактовый вход С триггера 17, выход которого соединен со входом разрешения счетчика 19 и обнуляющим входом блока 20, обнуляющий вход счетчика 19 соединен с выходом блока 20, информационный вход которого соединен с выходом счетчика 19, счетный вход которого является тактовым входом CLK устройства, стартовым ST и обнуляющим RST входами которого являются соответственно D-вход триггера 17 и его обнуляющий вход, первый вход логического элемента И 21 соединен с выходом блока 20, а второй вход - с выходом одновибратора 18, вход которого объединен с тактовым входом триггера 17.

Функциональная схема по фиг. 7 содержит триггер 22, регистр 23 и счетчик 24, выход переноса которого является выходом устройства, тактовым входом CLK которого является счетный вход счетчика 24, разрешающий вход которого соединен с прямым выходом триггера 22, а вход L управления загрузкой данных счетчика 24 соединен с инверсным выходом триггера, ST и обнуляющим RST входами устройства являются соответственно D-вход триггера 22 и его обнуляющий вход, информационным входом устройства является тактовый вход триггера 22, выход регистра 23 соединен с информационным входом (входом загрузки данных) счетчика 24.

Идея, лежащая в основе алгоритма функционирования предложенного устройства, состоит в том, что периодическую последовательность импульсов с необходимым смещением во времени получают не путем сдвига исходной, а путем формирования автономной последовательности импульсов с требуемой частотой, то есть путем регенерации с использованием опорных тактовых импульсов и информации о фазе входной последовательности. Проиллюстрируем вышеизложенное на примере функционирования конкретного устройства.

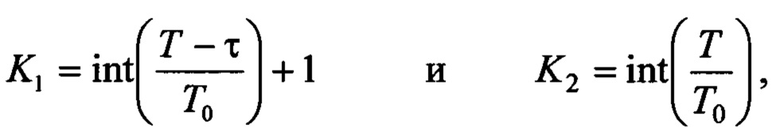

Запуск устройства (см. фиг. 1) осуществляется подачей высокого логического уровня на стартовый вход ST устройства - D-вход триггера 1 (см. фиг. 2), в связи с чем первый после стартового сигнала входной импульс, поступающий на тактовый вход триггера 1, переводит указанный триггер в состояние высокого логического уровня на выходе и разрешает таким образом работу счетчика 2. Последний работает в режиме суммирования тактовых импульсов, поступающих на вход CLK устройства и управляется блоком 3 задания коэффициента пересчета. В общем случае блок 3 задает два отличающихся коэффициента пересчета К1 и К2, первый из которых необходим для отсчета интервала времени, равного разности T-τ, а второй К2 для отсчета периода следования импульсов T. Полагая, что период следования тактовых импульсов CLK составляет T0, указанные коэффициенты определятся следующим образом

в приведенных записях int - обозначение целой части.

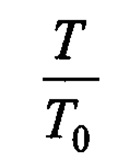

Отсчет интервала времени T-τ начинается непосредственно после первого импульса, поступившего на информационный вход после запуска устройства и осуществляется согласно заданному блоком 3 коэффициенту пересчета К1. По завершении указанного интервала времени, с некоторой погрешностью во времени, на выходе блока 3 появляется импульс окончания счета, который является обнуляющим для счетчика 2 и одновременно выходным импульсом устройства, смещенным во времени на величину (T-τ)+Δt относительно входного импульса. С целью упрощения понимания материала погрешность Δt на временных диаграммах по фиг. 2 не отражена. В приведенном примере полагается, что отношение  является целым числом и первый тактовый импульс поступил в момент времени отстоящий от фронта входного импульса на пренебрежимо малую величину, что позволяет пренебречь погрешностью Δt и считать, что выходной импульс опережает ближайший к нему входной импульс на время τ. Это идеальный случай. В реальности же, если исходить из наилучшего случая, при котором периоды T и T0 кратны (условие, которое в принципе удается соблюсти на практике), максимальное значение абсолютной погрешности Δt следует принять равной периоду Т0.

является целым числом и первый тактовый импульс поступил в момент времени отстоящий от фронта входного импульса на пренебрежимо малую величину, что позволяет пренебречь погрешностью Δt и считать, что выходной импульс опережает ближайший к нему входной импульс на время τ. Это идеальный случай. В реальности же, если исходить из наилучшего случая, при котором периоды T и T0 кратны (условие, которое в принципе удается соблюсти на практике), максимальное значение абсолютной погрешности Δt следует принять равной периоду Т0.

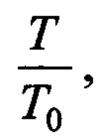

Далее блок 3 переходит в режим задания коэффициента К2 и счетчик 2 начинает отсчитывать интервал времени равный периоду T, регенерируя входную последовательность импульсов с привязкой только к первому рабочему импульсу. Ни фазовые флуктуации импульсов входной последовательности, ни случайные смещения тактовых импульсов относительно входных импульсов на работе устройства не отразятся, так как временные параметры выходной последовательности импульсов определяются только характеристиками опорного тактового сигнала CLK и отношением  которое в случае равенства целому числу позволит получить последовательность импульсов с периодом равным Т, с погрешностью определяемой только стабильностью частоты тактового сигнала CLK.

которое в случае равенства целому числу позволит получить последовательность импульсов с периодом равным Т, с погрешностью определяемой только стабильностью частоты тактового сигнала CLK.

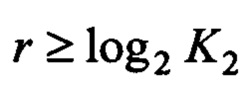

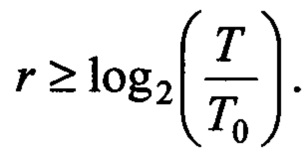

Отметим, что разрядность r счетчика 2 должна выбираться исходя из условия

или

Блок 3 задания коэффициента пересчета может быть выполнен по схеме, показанной на фиг. 3, где в регистрах 6 и 7 хранятся двоичные коды коэффициентов К1 и К2 соответственно. Началу работы блока 3 предшествует появление на выходе триггера 1 высокого логического уровня, который снимает запрещающий обнуляющий уровень с инвертирующего обнуляющего входа триггера 9. При этом поступающий в момент начала работы устройства низкий логический уровень с выхода триггера 9 на адресный вход мультиплексора 8 коммутирует на его выход сигнал с выхода компаратора 4. Согласно принципу действия устройства, всегда выполняется условие К1<К2, в этом несложно убедиться, если сравнить вышеприведенные выражения для вычисления указанных коэффициентов, следовательно, при поступлении на входы одновременно двух компараторов 4 и 5 текущего кода с выхода счетчика 2, первым выдаст скачок логических уровней, указывающий на равенство кодов, компаратор 4. То есть компаратор сравнивающий входной текущий код с кодом К1. Этот перепад напряжений поступает через мультиплексор 8 на выход блока и одновременно на тактовый вход триггера 9, который работает в режиме счета (T-триггер). Последний переходит в состояние высокого логического уровня на выходе, переключает входы мультиплексора 8 и остается в таком состоянии до окончании работы устройства. Перепад напряжений с выхода блока 3, поступая на обнуляющий вход счетчика 2, обнуляет последний для начала следующего цикла счета, который будет вестись уже с коэффициентом пересчета К2, так как на выход блока 3 коммутируется через мультиплексор 8 сигнал с выхода компаратора 5, который сравнивает входной текущий код с кодом К2.

Можно расширить возможности устройства за счет введения возможности управления коэффициентом пересчета К1. Это позволит изменять время T-τ в процессе эксплуатации устройства. Для введения такой возможности достаточно предусмотреть в регистре 6 информационный вход записи данных, поступающих извне, содержащих соответствующий коэффициент пересчета. Указанный вход показан штриховыми линиями на фиг. 3. Необходимые для записи данных в регистр, цепи управления на схеме не показаны, так как определяются типом конкретных используемых регистров и строятся по известным схемам. Важным является то, что после изменения коэффициента К1 устройство следует перезапустить, для чего достаточно, не снимая высокого логического уровня со стартового входа ST устройства (см. фиг. 1), подать импульс на вход RST, длительностью не менее длительности импульсов входной последовательности

Заметим, что в частном случае, когда период Т следования входных импульсов считается известным и неизменным, можно, учитывая, что К2>К1, выбрать счетчик 2 с максимальным коэффициентом пересчета равным К2, то есть счетчик, разрядность которого равна log2K2. При такой разрядности двоичный счетчик, работая в режиме циклического счета, будет формировать на выходе переноса импульсы следующие с периодом Т с началом, приходящимся на момент времени первого обнуления счетчика, задаваемого соответствующим импульсом с выхода блока задания коэффициента пересчета. Схема устройства с фиксированным К2 показана на фиг. 4. Работа устройства повторяет работу вышеописанного (см. фиг. 1) с незначительными особенностями. После поступления первого информационного импульса на вход устройства (тактовый вход триггера 10) при условии, что устройство запущено, счетчик 11 начинает счет тактовых импульсов CLK до момента времени, задаваемого блоком 12. Указанный блок по достижении на выходе счетчика 11 кода, соответствующего числу T-τ, обнуляет счетчик и далее в работе устройства не участвует. Дальнейшая работа устройства фактически сводится к счету импульсов счетчиком 11 и снятии упреждающих импульсов с выхода его переноса. При этом блок 12 задания коэффициента пересчета в такой схеме упрощается (см. фиг. 5), так как не требуется хранить информацию о двух коэффициентах. В регистр 14 заносится код коэффициента К1, который при помощи компаратора 13 сравнивается с текущим кодом, поступающим от счетчика 11, что необходимо для определения момента обнуления счетчика 11, то есть отсчета интервала T-τ. По завершении указанного интервала времени на тактовый вход триггера 16 подается положительный перепад напряжений, который переключает триггер и снимает таким образом разрешающий высокий логический уровень с нижнего по схеме входа элемента И 15. Таким образом запрещается поступление импульсов на обнуляющий вход счетчика 11 и последний ведет счет с максимальным для него коэффициентом пересчета К2.

Рассмотренные схемы позволяют получать последовательности импульсов с упреждающим сдвигом и инварианты к фазовым флуктуациям входных последовательностей, что, безусловно, является их преимуществом. Однако регенерируемая выходная последовательность импульсов после первой и единственной привязки к первому импульсу входной последовательности далее становится независимой от входной последовательности, а следовательно, при пропадании входной последовательности продолжает формироваться. В тех случаях, когда входная последовательность импульсов пропадает по причине сбоев в канале связи или в формирующих устройствах, такой алгоритм обеспечивает высокую помехозащищенность. Но в то же время в ситуациях, когда в наличии или отсутствии входных импульсов заложена некоторая информация, независимая регенерация может оказаться недопустимой. В этих случаях целесообразно прерывать подачу импульсов на выход и начинать ее только после возобновления поступления импульсов на вход устройства. Устройство, которое отслеживает наличие входных импульсов, показано на фиг. 6. Работает устройство аналогично показанному на фиг. 1, за тем исключением, что подача на выход смещенной во времени последовательности импульсов разрешается только при наличии входных импульсов. Для этого в схеме предусмотрен одновибратор 18 с перезапуском, который вырабатывает импульс длительностью не менее периода Т входного сигнала в ответ на каждый входной импульс. При таком выборе длительностей импульсов, на выходе одновибратора 18 всегда будет присутствовать высокий логический уровень при наличии входных импульсов, который поступая на нижний по схеме вход логического элемента И 21 разрешает прохождение регенерируемой последовательности на выход устройства. При пропадании входных импульсов, через время равное, длительности выходного импульса одновибратора, снимается разрешающий сигнал со входа элемента И 21 и, как следствие, прекращается подача импульсов на выход устройства с выхода блока 20.

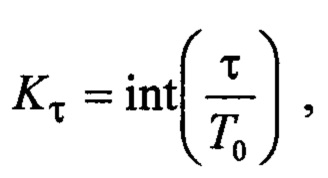

Еще одним из вариантов устройства является схема, показанная на фиг. 7 и ориентированная на применение при известном и фиксированном периоде Т, однако отличается от уже рассмотренного варианта (см. фиг. 4) отсутствием блока задания коэффициента пересчета. Исключение указанного блока возможно в случае применения счетчика с возможностью предварительной загрузки данных и коэффициентом пересчета равным К2. При этом предусматривается регистр 23 в котором хранится код задержки Kτ:

который перед началом работы устройства записывается в счетчик 24, что происходит при нахождении триггера 22 в состоянии низкого логического уровня на его прямом выходе. В этом случае на вход загрузки подается высокий логический уровень и по первому тактовому импульсу на входе CLK код Kτ записывается в память счетчика 24. Далее после перехода триггера 22 в состояние высокого логического уровня на выходе (после запуска устройства и поступления первого информационного импульса) счетчик 24 начинает отсчет тактовых интервалов длительностью Т0 и с учетом своего первоначального состояния в первом цикле переполняется на время τ раньше, чем в последующие. Таким образом задается первоначальный упреждающий сдвиг. Усложнение счетчика в представленной схеме окупается таким ее достоинством как отсутствие внешних (по отношению к счетчику) обратных связей, что позволяет повысить быстродействие устройства в целом. Кроме того, при малых значениях τ, то есть когда τ<<T целесообразно применение именно этой схемы, так как потребуется регистр 23 небольшой разрядности по сравнению с регистром 14, в котором хранится код К1, определяемый разностью T-τ.

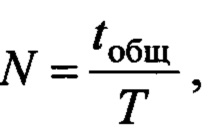

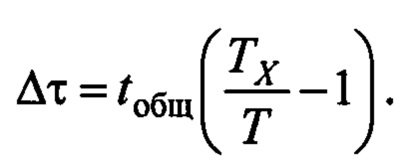

При применении вышеописанных устройств следует учитывать наличие погрешности вводимой задержки, обусловленной неидеальным соответствием периода выходной последовательности TX периоду входной T. Реальная задержка τX от вышеуказанных периодов зависит следующим образом:

τX=τ+N(TX-T),

где N - количество периодов T, прошедших за время работы tобщ устройства, начиная с момента поступления первого входного импульса.

Следовательно, абсолютная погрешность Δτ=τX-τ определится так

Δτ=N(TX-T)

или, полагая, что

Из последнего выражения несложно видеть, что погрешность Δτ, при неизменных TX и T, зависит от продолжительности работы устройства, находящегося в автономном режиме, то есть после запуска и первой синхронизации (привязки к первому рабочему импульсу). По этой причине, в ситуациях, когда при заданной погрешности не удается получить минимально необходимое отношение  или время работы tобщ оказывается чрезмерно большим, целесообразно, для снижения погрешности Δτ, периодически перезапускать устройство, с предварительным обнулением в паузах между выходными импульсами.

или время работы tобщ оказывается чрезмерно большим, целесообразно, для снижения погрешности Δτ, периодически перезапускать устройство, с предварительным обнулением в паузах между выходными импульсами.

Группа изобретений относится к области радиотехники и предназначена для формирования периодической последовательности импульсов с упреждающей задержкой относительно исходной последовательности, что, в частности, необходимо для компенсации задержек возникающих в каналах связи. Технический результат, достигаемый при использовании настоящей группы изобретений, состоит в снижении фазовых флуктуаций выходного сигнала. Для этого предложены устройства, в которых особенностью является то, что периодическая последовательность импульсов с необходимым смещением во времени образуется не путем сдвига исходной, а путем формирования автономной последовательности импульсов с требуемой частотой, с использованием опорных тактовых импульсов и информации о фазе входной последовательности. Основу устройств составляют триггер, счетчик и блок задания коэффициента пересчета. 6 н. и 3 з.п. ф-лы, 7 ил.

1. Устройство упреждающего временного сдвига импульсов содержащее триггер и счетчик, отличающееся тем, что в него введен блок задания коэффициента пересчета, выход которого является выходом устройства, информационным входом которого служит тактовый вход триггера, выход которого соединен со входом разрешения счетчика и обнуляющим входом блока задания коэффициента пересчета, обнуляющий вход счетчика соединен с выходом блока задания коэффициента пересчета, информационный вход которого соединен с выходом счетчика, счетный вход которого является тактовым входом устройства, стартовым и обнуляющим входами которого являются соответственно D-вход триггера и его обнуляющий вход.

2. Устройство по п. 1, отличающееся тем, что блок задания коэффициента пересчета выполнен таким образом, что имеется возможность изменения коэффициента пересчета в процессе применения устройства по назначению.

3. Блок задания коэффициента пересчета для применения в устройстве по п. 1, отличающийся тем, что содержит два компаратора двоичных кодов, два регистра, мультиплексор и триггер, выход которого соединен с адресным входом мультиплексора, первый и второй информационные входы которого соединены с выходами соответственно первого и второго компараторов, первые информационные входы которых объединены и составляют информационный вход блока, второй информационный вход первого компаратора соединен с выходом первого регистра, второй информационный вход второго компаратора соединен с выходом второго регистра, выход мультиплексора является выходом блока, тактовый вход триггера соединен с выходом первого компаратора, инвертирующий обнуляющий вход триггера является обнуляющим входом блока.

4. Блок по п. 3, отличающийся тем, что во втором регистре предусмотрена возможность смены данных за счет наличия информационного входа, служащего для ввода коэффициента пересчета.

5. Устройство упреждающего временного сдвига импульсов, содержащее триггер и счетчик, отличающееся тем, что в него введен блок задания коэффициента пересчета, выход которого соединен с обнуляющим входом счетчика, информационным входом которого служит тактовый вход триггера, выход которого соединен со входом разрешения счетчика и обнуляющим входом блока задания коэффициента пересчета, информационный вход которого соединен с выходом счетчика, счетный вход которого является тактовым входом устройства, стартовым и обнуляющим входами которого являются соответственно D-вход триггера и его обнуляющий вход, выходом устройства служит выход переноса счетчика.

6. Блок задания коэффициента пересчета для применения в устройстве по п. 5, отличающийся тем, что содержит компаратор двоичных кодов, регистр, триггер и логический элемент И, выход которого является выходом блока, тактовый вход триггера объединен с первым входом элемента И и соединен с выходом компаратора, инвертирующий обнуляющий вход триггера является обнуляющим входом блока, инверсный выход триггера соединен со вторым входом элемента И, первый вход компаратора является информационным входом блока, а второй вход соединен с выходом регистра.

7. Блок по п. 6, отличающийся тем, что в регистре предусмотрена возможность смены данных за счет наличия информационного входа, служащего для ввода коэффициента пересчета.

8. Устройство упреждающего временного сдвига импульсов, содержащее триггер и счетчик, отличающееся тем, что в него введены блок задания коэффициента пересчета, одновибратор и логический элемент И, выход которого является выходом устройства, информационным входом которого служит тактовый вход триггера, выход которого соединен со входом разрешения счетчика и обнуляющим входом блока задания коэффициента пересчета, обнуляющий вход счетчика соединен с выходом блока задания коэффициента пересчета, информационный вход которого соединен с выходом счетчика, счетный вход которого является тактовым входом устройства, стартовым и обнуляющим входами которого являются соответственно D-вход триггера и его обнуляющий вход, первый вход логического элемента И соединен с выходом блока задания коэффициента пересчета, а второй вход - с выходом одновибратора, вход которого объединен с тактовым входом триггера.

9. Устройство упреждающего временного сдвига импульсов, содержащее триггер и счетчик, отличающееся тем, что в него введен регистр, выход которого соединен с информационным входом счетчика, выход переноса которого является выходом устройства, тактовым входом которого является счетный вход счетчика, разрешающий вход которого соединен с прямым выходом триггера, а вход управления загрузкой данных счетчика соединен с инверсным выходом триггера, стартовым и обнуляющим входами устройства являются соответственно D-вход триггера и его обнуляющий вход, информационным входом устройства является тактовый вход триггера.

| Устройство временной задержки | 1987 |

|

SU1431053A1 |

| Устройство для сдвига импульсов | 1981 |

|

SU1086459A1 |

| US 5465076 A1, 07.11.1995 | |||

| ЛИНИЯ ЗАДЕРЖКИ | 1996 |

|

RU2100900C1 |

Авторы

Даты

2020-04-14—Публикация

2019-12-06—Подача