Изобретение относится к автоматике и импульсной технике и может быть использовано при построении устройства автоматики с гистерезисными и широтно-импульсными характеристиками.

Известно пороговое устройство, содержащее два операционных усилителя (компаратора) и логические элементы.

Однако, в этом устройстве нельзя устанавливать порог отпускания выше порога срабатывания, что ограничивает его возможности.

Наиболее близким по технической сущности к предлагаемому является устройство, содержащее два компаратора, два D-триггера, диод, резисторы, конденсаторы.

Недостатком этого устройства является сложность и связанная с этим большая потребляемая мощность.

Цель изобретения - упрощение и снижение потребляемой мощности.

Это достигается тем, что в пороговом устройстве, содержащем два компаратора, прямой вход первого и инверсный вход второго подключены к входной шине, вторые входы компараторов соответственно подключены к первой и второй шинам опорных сигналов, а выходы компараторов подключены к блоку анализа, содержащему D-триггер, первый и второй резисторы, первый и второй конденсаторы, счетный вход D-триггера соединен с выходом второго компаратора, применен D-триггер с установочными входами по уровню логической единицы, инверсный выход D-триггера соединен с его D-входом, установочные входы через первый и второй резисторы соответственно соединены с общей шиной, вход установки в ноль через первый конденсатор соединен с напряжением уровня логической единицы, вход установки в единицу D-триггера через второй конденсатор соединен с выходом первого компаратора.

Положительный эффект достигается за счет уменьшения количества элементов по сравнению с устройством-прототипом на два. Исключены второй D-триггер и диод, что упрощает устройство и снижает потребляемую мощность, так как один D-триггер потребляет мощность меньшую, чем два в устройстве-прототипе.

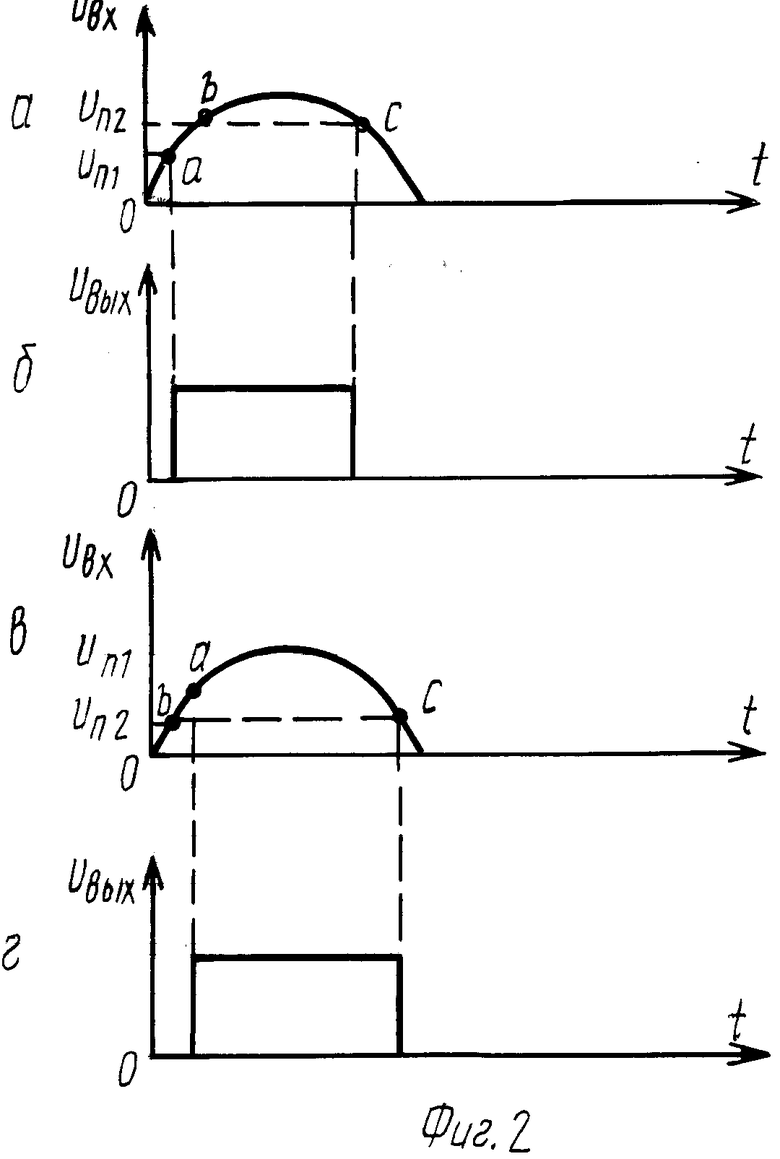

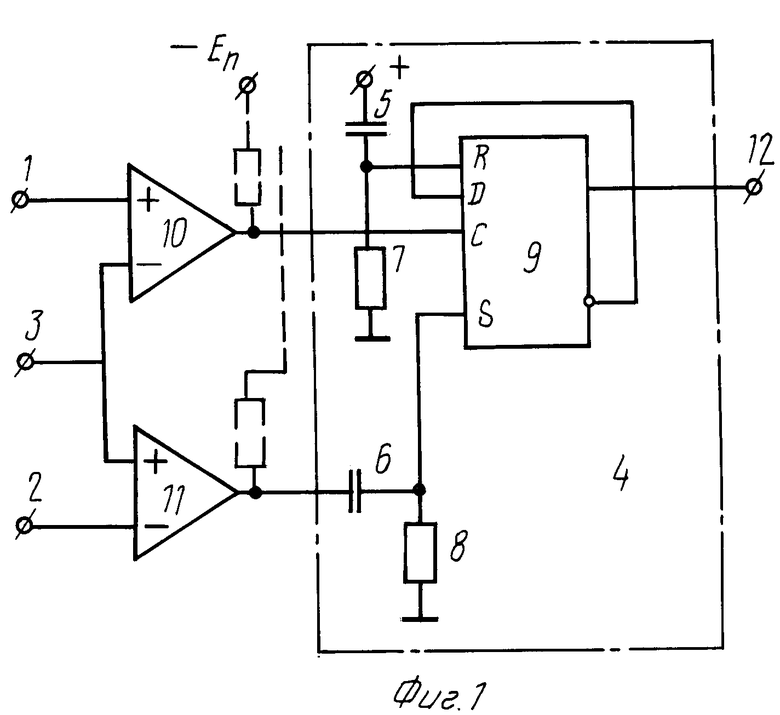

На фиг. 1 показана принципиальная схема предлагаемого устройства; на фиг. 2 - временные диаграммы, иллюстрирующие работу.

Пороговое устройство содержит шины 1 и 2 опорных сигналов, входную шину 3, блок 4 анализа, в который входят конденсаторы 5 и 6, резисторы 7 и 8, D-триггер 9, компараторы 10 и 11 и выходную шину 12.

Прямой и инверсный входы компараторов 10 и 11 соединены с входной шиной 3, а их вторые входы - с шинами 2 и 1 опорных сигналов соответственно. Выход компаратора 10 соединен со счетным входом D-триггера 9, инверсный выход которого соединен с его счетным входом, а прямой - с выходной шиной 12. Установочные входы D-триггера 9 через резисторы 7 и 8 соединены с общей шиной, вход установки в ноль D-триггера через, конденсатор 5 соединен с напряжением уровня логической единицы, вход установки в единицу через конденсатор 6 соединен с выходом компаратора 11.

Работа устройства для случая, когда напряжение отпускания выше напряжения срабатывания (фиг. 2а, б). При подаче на устройство питающего напряжения на его выходе устанавливается сигнал, равный логическому нулю, что связано с тем, что разряженный в исходном состоянии конденсатор 5 заряжается через резистор 7 и обеспечивает установку D-триггера 9 в нулевое состояние выхода. При этом при отсутствии входного сигнала на выходе компаратора 10 устанавливается логическая единица, а на выходе компаратора 11 - логический ноль, поэтому конденсатор 6 разряжен. Как только входное напряжение превышает значение Uп1, поступающее на инверсный вход компаратора 11, на его выходе появляется логическая единица, что приводит к появлению логической единицы на выходе устройства (точка а), так как конденсатор 6 обеспечивает кратковременное (на время его заряда) подключение выхода компаратора 11 к входу установки в единицу D-триггера 9. Поэтому на прямом выходе D-триггера появляется логическая единица, а на инверсном - логический ноль. При превышении входным сигналом порогового уровня Uп2 на шине 1 (точка b) изменяется состояние (с единицы на ноль) на выходе компаратора 10, однако это не влияет на состояние D-триггера 9 и устройства в целом, так как счетный вход D-триггера реагирует только на переход входного сигнала из нуля в единицу. При снижении входного напряжения ниже уровня на шине 1 на выходе компаратора 10 устанавливается логическая единица, поэтому нулевой сигнал на D-входе D-триггера поступает на его выход и на выходе устройства (шине 12) также устанавливается сигнал логического нуля (точка с). Формирование выходного сигнала устройства завершается.

Работа устройства, когда напряжение отпускания ниже напряжения срабатывания, происходит аналогично (фиг. 2в, г).

При практической реализации устройства возможно использование компараторов 521САЗ, снабжая их режимными резисторами (показаны на фиг. 1 пунктиром) и D-триггеры 564ТМ2. (56) Авторское свидетельство СССР N 1750041, кл. H 03 K 5/24, 1989.

| название | год | авторы | номер документа |

|---|---|---|---|

| Пороговое устройство | 1989 |

|

SU1750041A1 |

| Триггер | 1990 |

|

SU1760628A1 |

| Устройство для передачи информации с вращающегося объекта | 1986 |

|

SU1334173A1 |

| Реле времени | 1986 |

|

SU1406770A1 |

| Устройство для считывания графической информации | 1989 |

|

SU1683046A1 |

| Устройство автоматического управления диапроекторами | 1987 |

|

SU1453361A1 |

| Способ декодирования кода с расщепленной фазой и устройство для его осуществления | 1990 |

|

SU1728970A1 |

| УСТРОЙСТВО ДЛЯ ТРЕВОЖНОЙ СИГНАЛИЗАЦИИ | 1991 |

|

RU2025781C1 |

| Дискретно-аналоговый интегратор | 1986 |

|

SU1372337A1 |

| Устройство для управления электромагнитом | 1989 |

|

SU1647667A1 |

Использование: автоматика, импульсная техника и может быть использовано при построении устройств автоматики с гистерезисными и широтно-импульсными характеристиками. Цель изобретения - упрощение и снижение потребляемой мощности. Сущность: в пороговом устройстве, содержащем шины источников опорных сигналов, шину входного сигнала, выходную шину, компараторы, блок анализа, состоящий из резисторов, конденсаторов, D-триггера, инверсный выход D-триггера соединен с его D-входом, установочные входы соединены через резисторы с общей шиной, а через конденсаторы - с напряжением логической единицы и выходом второго компаратора соответственно. 2 ил.

ПОРОГОВОЕ УСТРОЙСТВО, содержащее два компаратора, инверсный вход первого и прямой вход второго подключены к входной шине, вторые входы компараторов соответственно подключены к первой и второй шинам опорных сигналов, а выходы компараторов соответственно подключены к блоку анализа, выход которого является выходом устройства, причем блок анализа содержит D-триггер, первый и второй резисторы, первый и второй конденсаторы, счетный вход D-триггера соединен с выходом первого компаратора, а его прямой выход является выходом блока анализа, отличающееся тем, что, с целью упрощения и снижения потребляемой мощности, в устройстве применен D-триггер с установочными входами по уровню логической единицы, инверсный вход D-триггера соединен с его D-входом, установочные входы через первый и второй резисторы соответственно соединены с общей шиной, вход установки в "0" через первый конденсатор соединен с напряжением уровня логической единицы, а вход установки в "1" D-триггера через второй конденсатор соединен с выходом второго компаратора.

Авторы

Даты

1994-02-15—Публикация

1991-07-22—Подача