ОБЛАСТЬ ТЕХНИКИ

Настоящее изобретение относится в целом к обмену информацией между встроенными процессорами в электронных системах. Более конкретно, различные изобретательские способы и устройства, описываемые здесь, относятся к высокоскоростному протоколу связи для малых встроенных процессоров в осветительной системе.

УРОВЕНЬ ТЕХНИКИ

Мониторинг рабочих параметров, так же как и управление входами/выходами (I/O) и/или схемами обратной связи, такими как схемы широтно-импульсной модуляции (PWM), в цепях электропитания являются сложной задачей и могут быть дорогостоящими, особенно через изоляционный барьер. При использовании небольших встроенных микроконтроллеров для управления системой, не существует много ресурсов, отведенных для функций коммуникации и командного интерфейса. Это представляет собой проблему с точки зрения времени обработки, требуемого для обработки сообщения или кадра при сохранении целостности данных. Данные, которые должны быть переданы с определенной скоростью обновления, представляют особый интерес. Таким образом, имеется потребность в создании протокола связи для устройств с ограниченными ресурсами, который сможет обеспечить быстрый, гибкий, эффективный и надежный обмен данными, не затрачивая слишком много ресурсов на обработку.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

Настоящее изобретение направлено на изобретательские способы и устройства для обеспечения обратной связи и управления в электронных системах, конкретно, на протокол связи, поддерживающий такую обратную связь и управление. Например, различные варианты осуществления относятся к системам и способам, которые используют симметричный протокол связи для осуществления связи между встроенными процессорами в электронных системах, в частности, в электронных системах электропитания и, более конкретно, в осветительных системах.

В целом, в одном из аспектов, изобретение относится к устройству, которое включает в себя осветительный блок, оптический изолятор и первичный процессор. Осветительный блок включает в себя осветительный модуль и драйвер освещения, выполненный с возможностью подачи электропитания на осветительный модуль. Осветительный модуль включает в себя: один или более источников света, один или более датчиков для считывания данных, указывающих один или более рабочих параметров осветительного модуля, и вторичный процессор, выполненный с возможностью приема считанных данных, указывающих один или более рабочих параметров. Первичный процессор выполнен с возможностью мониторинга одного или более рабочих параметров. Первичный процессор и вторичный процессор связаны друг с другом через оптический изолятор согласно протоколу связи, основанному на обмене сообщениями, в котором каждое сообщение, пересылаемое между первичным процессором и вторичным процессором, имеет идентичный формат сообщения и включает в себя поле команд и поле откликов, причем упомянутое поле откликов обеспечено для указания отклика на команду.

Согласно одному или более вариантам осуществления каждое сообщение дополнительно включает в себя: поле начала кадра; поле конца кадра; поле длины сообщения; биты циклического контроля избыточности (CRC) для полного соответствия сообщения контрольной сумме за исключением самих CRC битов и полей начала кадра, конца кадра и длины сообщения.

Согласно одному или более вариантам осуществления один или более рабочих параметров включают в себя ток, подаваемый по меньшей мере в один из одного или более источников света, напряжение, подаваемое по меньшей мере на один из одного или более источников света, и рабочую температуру осветительного модуля. В одной или более версий этих вариантов изобретения один или более источников света включают в себя по меньшей мере два источника света.

Согласно одному или более вариантам осуществления поле команд включает в себя команду, выбранную из набора разрешенных команд, причем упомянутый набор разрешенных команд включает в себя: установку состояния вторичного процессора в одно из набора назначенных состояний; запрос подтверждения от вторичного процессора, указывающего, готов ли к работе осветительный модуль; установку значения широтно-импульсной модуляции для широтно-импульсного модулятора, включенного в состав осветительного блока; и запрос на передачу вторичным процессором выбранного набора считанных данных из группы назначенных наборов считанных данных. Набор разрешенных команд может дополнительно включать в себя установку осветительного модуля в демонстрационный режим.

Согласно одной или более версий этих вариантов осуществления набор назначенных состояний включает в себя активное состояние, состояние ожидания, состояние сброса, состояние сбережения электроэнергии и состояние мониторинга только тока.

Согласно одной или более версий этих вариантов осуществления один или более источников света включают в себя по меньшей мере первый и второй источники света, и при этом назначенные наборы считанных данных включают в себя: первый и второй токи, подаваемые в первый и второй источники света; токи от первого и второго источников света и первое напряжение, подаваемое на первый источник света; первый и второй токи, подаваемые в первый и второй источники света, и второе напряжение, подаваемое на второй источник света; первый и второй токи, подаваемые в первый и второй источники света, и температуру осветительного модуля; и первый и второй токи, подаваемые в первый и второй источники света, и значение широтно-импульсной модуляции для широтно-импульсного модулятора осветительного блока.

Согласно одному или более вариантам осуществления формат сообщения является следующим:

[SOF/MSGL]-[CMD/RESP]-([DATA(0)]…[DATA(x)])-[CRC2]-[(CRC1/2)/EOF],

где SOF указывает начало сообщения, MSLG указывает длину сообщения, CMD указывает конкретную команду, RESP указывает конкретный ожидаемый отклик, DATA указывает данные, связанные с конкретной командой или откликом, CRC2 указывает младшие 8 битов 16-битового значения циклического контроля избыточности для сообщения, CRC1/2 указывает половину старших 8 битов 16-битового значения циклического контроля избыточности для сообщения и EOF указывает конец сообщения.

Согласно одному или более вариантам осуществления осветительный блок дополнительно включает в себя широтно-импульсный модулятор для регулировки выходного уровня драйвера освещения, причем один или более рабочих параметров дополнительно содержат значение широтно-импульсной модуляции для широтно-импульсного модулятора.

Осветительный блок дополнительно может включать в себя второй оптический изолятор, выполненный с возможностью подачи сигнала обратной связи от осветительного модуля к драйверу освещения.

В целом, в другом аспекте, изобретение относится к способу, который включает в себя: во вторичном процессоре, встроенном в осветительный модуль, который включает в себя один или более источников света, прием от первичного процессора первого сообщения, переданного согласно протоколу связи, основанному на обмене сообщениями, в котором каждое сообщение, пересылаемое между первичным процессором и вторичным процессором, имеет идентичный формат сообщения и включает в себя поле команд и поле откликов, причем поле откликов обеспечено для указания отклика на команду; выполнение первой операции в осветительном модуле в ответ на первую команду, включенную в состав поля команд сообщения; отправку от вторичного процессора в первичный процессор второго сообщения в соответствии с протоколом связи, основанным на обмене сообщениями, причем упомянутое второе сообщение включает в состав поля откликов первый отклик на первую команду, принятую в первом сообщении.

Согласно одному или более вариантам осуществления первая команда содержит запрос на отправку вторичным процессором первичному процессору выбранных данных, считанных в осветительном модуле, которые указывают один или более рабочих параметров осветительного модуля.

Согласно одной или более версий этих вариантов осуществления выполнение первой операции в осветительном модуле включает в себя считывание выбранных данных, и при этом второе сообщение дополнительно включает в себя упомянутые выбранные данные.

Используемый здесь в целях настоящего описания термин “LED” (“светодиод” или «СИД») должен пониматься как включающий в себя любой электролюминесцентный диод или другой тип системы, основанной на инжекции/переходе носителей заряда, которая способна генерировать излучение в ответ на электрический сигнал. Таким образом, термин LED включает в себя, не ограничиваясь нижеперечисленным, различные полупроводниковые структуры, которые вырабатывают свет в ответ на ток, светоизлучающие полимеры, органические светоизлучающие диоды (OLED), электролюминесцентные ленты, и т.п. В частности, термин LED относится к светоизлучающим диодам всех типов (включая сюда полупроводниковые и органические светоизлучающие диоды), которые могут быть выполнены с возможностью генерации излучения в одном или более из инфракрасного спектра, ультрафиолетового спектра и различных участков видимой области спектра (в общем случае включающей в себя длины волн излучения от приблизительно 400 нанометров до приблизительно 700 нанометров). Некоторые примеры LED включают в себя, не ограничиваясь нижеперечисленным, различные типы инфракрасных LED, ультрафиолетовых LED, LED красного свечения, LED голубого свечения, LED зеленого свечения, LED желтого свечения, LED янтарного свечения, LED оранжевого свечения и LED белого свечения (которые будут обсуждаться ниже). Должно быть также понятно, что LED могут выполняться с возможностью генерации и/или управляться для генерации излучения, имеющего различные полосы частот (например, полная ширина на полувысоте максимума, или FWHM) для данного спектра (например, узкая полоса частот, широкая полоса частот), и возможно разнообразие доминирующих длин волн в пределах данного общего разделения на цветовые категории.

Например, один вариант осуществления LED, выполненного с возможностью генерации по существу белого света (например, LED белого свечения), может включать в себя набор кристаллов, генерирующих соответственно разные спектры электролюминесценции, которые, смешиваясь, образуют в сочетании по существу белый свет. В другом варианте осуществления LED белого свечения может быть соединен с материалом люминофора, что преобразует электролюминесценцию, имеющую первый спектр, в другой второй спектр. В одном примере этого варианта осуществления электролюминесцентный материал, имеющий относительно короткую длину волны и спектр с узкой полосой частот, “накачивает” материал люминофора, который, в свою очередь, испускает излучение с большей длиной волны, имеющее несколько более широкий спектр.

Термин “источник света” должен пониматься как относящийся к любому одному или более источникам света из всего разнообразия, включающего в себя, не ограничиваясь нижеперечисленным, основанные на использовании LED источники света (включающие в себя один или более LED, как определено выше), источники с элементами накаливания (например, лампы накаливания, галогенные лампы), люминесцентные источники света, фосфоресцирующие источники света, высокоинтенсивные разрядные источники (например, натриевые, ртутные дуговые и металло-галогенные лампы), лазеры, другие типы электролюминесцентных источников, пиро-люминесцентные источники (например, факелы), свечные люминесцентные источники (например, калильные сетки газового фонаря, дуговые лампы с угольным электродом), фотолюминесцентные источники (например, газоразрядные источники), катодолюминесцентные источники, использующие электронное насыщение, гальванолюминесцентные источники, кристаллолюминесцентные источники, кинелюминесцентные источники, термолюминесцентные источники, триболюминесцентные источники, сонолюминесцентные источники, радиолюминесцентные источники и люминесцентные полимеры.

Термин “осветительный блок” используется здесь применительно к устройству, включающему в себя один или более источников света одного и того же или разных типов. Данный осветительный блок может иметь одно или множество монтажных приспособлений для источника (источников) света, ограждающих/вмещающих в себя приспособлений и форм, и/или конфигураций электрических и механических соединений. Дополнительно данный осветительный бок опционально может быть связан (например, включать в себя, быть подсоединенным и/или упакованным вместе) с различными другими компонентами (например, со схемой управления, которая может включать в себя один ил более драйверов), относящимися к работе источника (источников) света. Термин “основанный на использовании LED осветительный блок” относится к осветительному блоку, который включает в себя один или более основанных на LED источников света, которые обсуждались выше, отдельных или в сочетании с другими источниками света, не основанными на использовании LED.

Термины “драйвер” («источник питания») и “драйвер освещения” («источник питания освещения») используются здесь в общем случае применительно к устройству для приема входного электропитания с целью подачи этого электропитания в формате на один или более источников света, чтобы заставить источник (источники) света вырабатывать свет. В частности, термин “LED драйвер” относится к устройству для приема входного электропитания и подачи электропитания на нагрузку из одного или более основанных на LED источников света, включающих в себя один или более LED, как обсуждалось выше, чтобы заставить один или более основанных на LED источников света вырабатывать свет.

Термин “осветительный модуль” используется здесь применительно к элементам осветительного блока, которые могут приводиться в действие драйвером освещения и могут включать в себя один или более источников света, один или более датчиков и, опционально, схему обратной связи для обеспечения сигнала обратной связи для драйвера освещения. В некоторых случаях осветительный модуль представляет собой элементы осветительного блока, которые гальванически изолированы от драйвера освещения.

Используемый здесь термин “гальваническая изоляция” относится к принципу изоляции функциональных секций электрических систем, препятствующему перемещению переносящих заряды частиц от одной секции в другую. Когда первая и вторая секции гальванически изолированы друг от друга, отсутствует электрический ток, текущий непосредственно из первой секции во вторую секцию. Обмен энергией или информацией может по-прежнему осуществляться между этими секциями другими средствами, например, индукцией, электромагнитными волнами, оптическими, акустическими или механическими средствами.

Используемый здесь термин “оптический изолятор” определяет электронное устройство, которое выполнено с возможностью передачи электрических сигналов, используя световые волны, для обеспечения связи через электрическую изоляцию/гальваническую изоляцию между своим входом и выходом, и может иногда называться также оптоизолятором, оптроном или оптосоединителем.

Термин “контроллер” используется здесь в общем случае для описания различных устройств, относящихся к работе одного или более источников света. Контроллер может быть реализован многочисленными способами (например, в виде специализированного аппаратного обеспечения) для выполнения различных функций, обсуждаемых здесь.

“Процессор ” является одним примером контроллера, который использует один или более микропроцессоров, которые могут быть запрограммированы, используя программное обеспечение (например, микрокод), для выполнения различных обсуждаемых здесь функций. Контроллер может быть реализован с использованием или без использования процессора, и также может быть реализован в виде сочетания специализированного аппаратного обеспечения для выполнения некоторых функций и процессора (например, одного или более программируемы микропроцессоров и связанных с ними схем) для выполнения других функций. Примеры компонентов контроллера, которые могут быть использованы в различных вариантах осуществления настоящего изобретения, включают в себя, не ограничиваясь нижеперечисленным, обычные микропроцессоры, специализированные интегральные схемы (ASIC) и программируемые пользователем вентильные матрицы (FPGA).

В различных вариантах осуществления процессор или контроллер может быть связан с одним или более носителями информации (в общем случае называемыми здесь “запоминающими устройствами”, например, энергозависимое и энергонезависимое запоминающее устройство компьютера, такое как RAM, ROM, EPROM и EEPROM, гибкие магнитные диски, компакт-диски, оптические диски, магнитная лента, и т.п.). В некоторых вариантах осуществления носитель информации может быть кодирован одной или более программами, с тем чтобы при выполнении на одном или более процессорах и/или контроллерах, выполнялись по меньшей мере некоторые из обсуждаемых здесь функций. Различные накопители информации могут быть установлены внутри процессора или контроллера или могут быть переносимыми, так что одна или более программ, запомненных на них, могут загружаться в процессор или контроллер, с тем чтобы реализовывать различные аспекты настоящего изобретения, обсуждаемые здесь. Термины “программа” или “компьютерная программа” используются здесь в общем смысле применительно к любому типу компьютерных программ (например, программному обеспечению или системе микрокоманд), которые могут быть использованы для программирования одного или более процессоров или контроллеров.

Должно быть понятно, что все сочетания упомянутых выше концепций и дополнительных концепций, обсуждаемых более подробно ниже (при условии, что эти концепции не являются взаимно несовместимыми), рассматриваются как часть предмета изобретения, описываемого здесь. В частности, все сочетания заявленного предмета изобретения, представленного в конце настоящего описания, рассматриваются как часть предмета изобретения, описываемого здесь. Должно быть также понятно, что терминология, явным образом используемая здесь, которая может также присутствовать в любом описании, включенном сюда путем ссылки, должна наиболее близко соответствовать по значению конкретным концепциям, обсуждаемым здесь.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

На чертежах одинаковые позиционные обозначения в общем случае относятся к одним и тем же частям на разных чертежах. Кроме того, на чертежах не обязательно выдержан масштаб, вместо этого упор в целом сделан на представлении принципов изобретения.

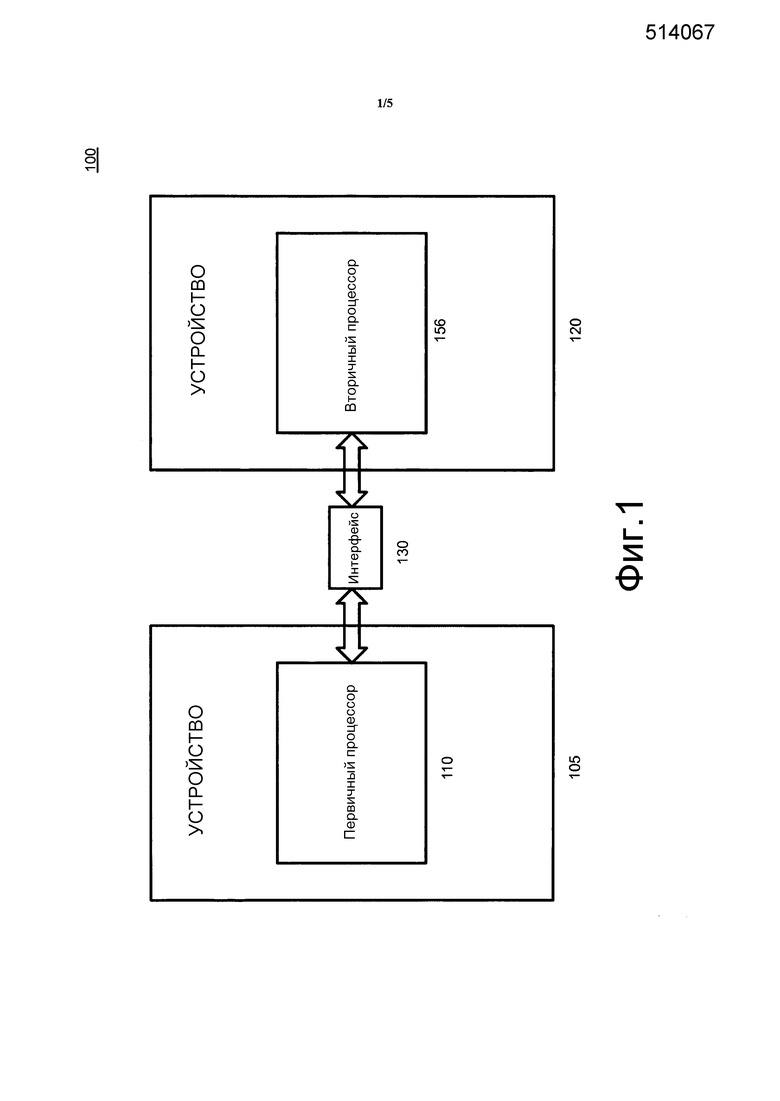

Фиг. 1 - функциональная блок-схема высокого уровня, иллюстрирующая связь между первичным процессором и вторичным процессором, встроенными в устройства.

Фиг. 2 - функциональная блок-схема одного варианта осуществления осветительной системы.

Фиг. 3 - принципиальная схема одного варианта осуществления осветительной системы.

Фиг. 4 - блок-схема последовательности операций, иллюстрирующая пример связей между первичным процессором и вторичным процессором, такими как первичный процессор и вторичный процессор на Фиг. 1.

Фиг. 5 - один вариант осуществления формата сообщения для одного варианта осуществления симметричного протокола связи, основанного на обмене сообщениями, который может быть использован первичным и вторичными процессорами согласно Фиг. 1-3.

ПОДРОБНОЕ ОПИСАНИЕ

Как обсуждалось выше, мониторинг параметров, так же как и управление входами/выходами (I/O) и/или схемами обратной связи, такими как схемы широтно-импульсной модуляции (PWM), в цепях электропитания являются сложной задачей и могут быть дорогостоящими, особенно через изоляционный барьер. При использовании небольших встроенных микроконтроллеров для управления системой не существует много ресурсов, отведенных для функций коммуникации и командного интерфейса. Это представляет проблему с точки зрения времени обработки, требуемого для обработки сообщения или кадра при условии сохранения целостности данных. Данные, которые должны передаваться с определенной частотой обновления, представляют особый интерес.

В более общем смысле Заявитель признал и оценил, что было бы практически значимо обеспечить протокол связи для таких устройств с ограниченными ресурсами, который сможет передавать данные быстро, гибко, эффективно и надежно, не затрачивая слишком много ресурсов на обработку.

С учетом вышесказанного, различные варианты осуществления и осуществления настоящего изобретения направлены на гибкий, эффективный и надежный высокоскоростной протокол связи для использования с небольшими микроконтроллерами для выполнения обратной связи и управления в электронных системах электропитания, например, в осветительных системах, и на системы и способы, которые используют такой протокол.

На Фиг. 1 представлена функциональная блок-схема высокого уровня, иллюстрирующая связь между первичным процессором и вторичным процессором, встроенными в устройства. Конкретно, на Фиг. 1 показана система 100, включающая в себя первое устройство 105 и второе устройство 120. Первое устройство 105 включает в себя встроенный первичный процессор 110, а второе устройство 120 включает в себя встроенный вторичный процессор 156. Первичный процессор 110 и вторичный процессор 156 связаны друг с другом через интерфейс 130.

В некоторых практически значимых вариантах осуществления как первичный процессор 110, так и вторичный процессор 156 могут быть небольшими и недорогими устройствами, которые выполняют набор функций, так что они имеют ограниченные ресурсы для выполнения функций коммуникации и командного интерфейса. В некоторых вариантах осуществления первичному процессору 110 и вторичному процессору 156 может оказаться необходимым передавать определенное количество данных в пределах определенного интервала времени, чтобы поддержать требования взаимодействия первого устройства 105 и второго устройства 120. Кроме того, в некоторых вариантах осуществления интерфейс 130 может быть в некоторой степени привязан к полосе частот, например, когда интерфейс 130 обеспечивает гальванический изоляционный барьер между первым устройством 105 и вторым устройством 120.

В соответствии с этим, как будет описано намного более подробно ниже, первичный процессор 110 и вторичный процессор 156 могут связываться друг с другом согласно симметричному протоколу связи, основанному на обмене сообщениями, который обеспечивает желаемую степень скорости, надежности и гибкости. Типовые варианты осуществления такого протокола связи, основанного на обмене сообщениями, и типовые системы и способы, которые могут использовать такой основанный на обмене сообщениями протокол связи, будут описаны ниже в контексте осветительной системы. Этот конкретный контекст имеет определенные требования к связи, для удовлетворения которых могут быть полезными различные признаки такого симметричного протокола связи, основанного на обмене сообщениями, и в соответствии с этим использование этого контекста в качестве конкретного примера будет ясно иллюстрировать различные аспекты и преимущества этого протокола. Однако должно быть понято и оценено, что симметричный протокол связи, основанный на обмене сообщениями, описываемый ниже, применим и может быть использован в других контекстах, не относящихся к осветительной системе.

На Фиг. 2 представлена функциональная блок-схема одного варианта осуществления осветительной системы 200, которая может использовать симметричный протокол связи, основанный на обмене сообщениями. Осветительная система 200 включает в себя первичный процессор 210, осветительный блок 220 и оптический изолятор 230. Осветительный блок 220 включает в себя драйвер 240 освещения и осветительный модуль 250. Осветительный модуль 250 включает в себя первую и вторую LED нагрузки 252-1 и 252-2, один или более датчиков 254, вторичный процессор 256 и схему 258 обратной связи. Каждая из первой и второй LED нагрузок 252-1 и 252-2 включает в себя один или более светодиодов (LED), например, множество LED, соединенных последовательно друг с другом и называемых здесь LED цепочкой. Каждая из первой и второй LED нагрузок 252-1 и 252-2 может включать в себя одну или более LED цепочек.

Драйвер 240 освещения выполнен с возможностью подачи во время работы электропитания на осветительный модуль 250, включающий в себя первую и вторую LED нагрузки 252-1 и 252-2. Конкретно, драйвер 240 освещения подает выходной ток в первую и вторую LED нагрузки 252-1 и 252-2, приводя в активное состояние светодиоды (LED), включенные в их состав, в желаемый момент работы, с тем чтобы осветительный модуль 250 обеспечивал желаемый световой выход. В некоторых вариантах осуществления драйвер 240 освещения может реагировать на сигнал обратной связи, подаваемый схемой 258 обратной связи, для управления выходным током, который он подает в первую и вторую LED нагрузки 252-1 и 252-2.

Датчик(и) 254 считывает один или более рабочих параметров осветительного модуля 250 и подает упомянутые считанные данные на вторичный процессор 256. Такой рабочий параметр (параметры) может включать в себя ток и/или напряжение, подаваемые на каждую из первой и второй LED нагрузок 252-1 и 252-2, и/или рабочую температуру осветительного модуля 250. В некоторых вариантах осуществления датчик(и) 254 может включать в себя один или более аналого-цифровых преобразователей (ADC) для преобразования измеренного значения (например, тока, напряжения или температуры) в цифровые считанные данные, которые могу обрабатываться вторичным процессором 256.

Схема 258 обратной связи подает на драйвер 240 освещения сигнал обратной связи, который драйвер 240 освещения может использовать для регулировки выходного тока, который он подает в первую и вторую LED нагрузки 252-1 и 252-2. В некоторых вариантах осуществления схема 258 обратной связи может принимать от вторичного процессора 256 сигнал управления, из которого она генерирует сигнал обратной связи. В некоторых вариантах осуществления схема 258 обратной связи может содержать схему обратной связи с пропорциональным интегратором (PI), которая обеспечивает значение широтно-импульсной модуляции для широтно-импульсного модулятора драйвера 240 освещения, чтобы регулировать выходной ток, который драйвер 240 освещения подает в первую и вторую LED нагрузки 252-1 и 252-2.

Вторичный процессор 256 также связан с первичным процессором 210 для приема команд, которые вторичный процессор 256 выполняет для управления одной или более операциями осветительного блока 220 и, в частности, осветительного модуля 250. Например, вторичный процессор 256 может принимать одну или более команд от первичного процессора 210, чтобы считывать данные для определенных рабочих параметров осветительного блока 220 и подавать упомянутые считанные данные на первичный процессор 210. В ответ на считанные данные и/или одну или более команд от первичного процессора 210 вторичный процессор 256 может управлять параметрами схемы 258 обратной связи, чтобы регулировать сигнал обратной связи, подаваемый на драйвер 240 освещения, и тем самым оказывать также воздействие на выходной ток, который подается драйвером 240 освещения в первую и вторую LED нагрузки 252-1 и 252-2.

В некоторых вариантах осуществления драйвер 240 освещения может быть гальванически изолирован от осветительного модуля 250. Например, драйвер 240 освещения может подавать свой выходной ток на осветительный модуль 250 через развязывающий трансформатор, а осветительный модуль 250 может подавать свой сигнал обратной связи на драйвер 240 освещения через второй оптический изолятор.

Оптический изолятор 230 создает интерфейс между первичным процессором 210 и вторичным процессором 256. Оптический изолятор 230 обеспечивает возможность связи между первичным процессором 210 и вторичным процессором 256, гальванически изолируя в то же время первичный процессор 210 и вторичный процессор 256 друг от друга. Первичный процессор 210 и вторичный процессор 256 могут связываться между собой через оптический изолятор 230 для обмена командами, откликами и данными. Практически значимо то, что первичный процессор 210 связывается с вторичным процессором 256 в соответствии с симметричным протоколом связи, основанным на обмене сообщениями, который обеспечивает желаемую степень скорости, надежности и гибкости. Приводимые в качестве примера варианты осуществления такого симметричного протокола связи, основанного на обмене сообщениями, и типовые системы и способы, которые могут использовать такой симметричный протокол связи, основанный на обмене сообщениями, будут описаны более подробно ниже. Посредством такого протокола связи первичный процессор 210 взаимодействует с вторичным процессором 256 для считывания и регулировки рабочих параметров осветительного модуля 220.

Тогда как на Фиг. 2 представлен вариант осуществления, в котором осветительный модуль 220 является осветительным модулем на основе LED, в других вариантах осуществления осветительный модуль 220 может использовать другие источники света, включая сюда, но не ограничиваясь нижеперечисленным, источники с элементами накаливания (например, лампы накаливания, галогенные лампы), люминесцентные источники света, фосфоресцирующие источники света, высокоинтенсивные разрядные источники (например, натриевые, ртутные и металло-галогенные лампы), лазеры, другие типы электролюминесцентных источников, пиро-люминесцентные источники (например, факелы), свечные люминесцентные источники (например, калильные сетки газового фонаря, дуговые лампы с угольным электродом), фотолюминесцентные источники (например, газоразрядные источники), катодолюминесцентные источники, использующие электронное насыщение, гальванолюминесцентные источники, кристаллолюминесцентные источники, кинелюминесцентные источники, термолюминесцентные источники, триболюминесцентные источники, сонолюминесцентные источники, радиолюминесцентные источники и люминесцентные полимеры. В некоторых из этих вариантов осуществления гальваническая развязка между первичным процессором и осветительным модулем 250 может не требоваться. В таких вариантах осуществления оптический изолятор 230 может отсутствовать, и первичный процессор 210 и вторичный процессор 256 могут соединяться непосредственно для обеспечения связи.

Тогда как на Фиг. 2 представлен вариант осуществления только с одним осветительным блоком 220, в других вариантах осуществления осветительная система 200 может включать в себя множество осветительных блоков 220, каждый из которых связан с первичным процессором 210 согласно симметричному протоколу связи, основанному на обмене сообщениями, как описано ниже.

На Фиг. 3 представлена принципиальная схема одного варианта осуществления осветительной системы 300, которая может служить одним примером осветительной системы 200. Осветительная система 300 включает в себя первичный процессор 310, осветительный блок 320 и первый оптический изолятор 330. Осветительный блок 320 включает в себя драйвер 340 освещения и осветительный модуль 350. Осветительный модуль 350 включает в себя первую и вторую LED нагрузки 352-1 и 352-2, один или более датчиков 354, вторичный процессор 356 и схему 358 обратной вязи. Каждая из первой и второй LED нагрузок 352-1 и 352-2 включает в себя один или более светодиодов (LED), например, множество LED, соединенных последовательно друг с другом и называемых здесь LED цепочкой. Каждая из первой и второй LED нагрузок 352-1 и 352-2 может включать в себя одну или более LED цепочек.

Драйвер 340 освещения выполнен с возможностью подачи во время работы электропитания на осветительный модуль 350, включающий в себя первую и вторую LED нагрузки 352-1 и 352-2. Конкретно, драйвер 340 освещения подает выходной ток в первую и вторую LED нагрузки 352-1 и 352-2, приводя в активное состояние светодиоды (LED), включенные в их состав, в желаемый момент работы, с тем чтобы осветительный модуль 350 обеспечивал желаемый световой выход. В некоторых вариантах осуществления драйвер 340 освещения может реагировать на сигнал обратной связи, подаваемый схемой 258 обратной связи, для управления выходным током, который он подает в первую и вторую LED нагрузки 352-1 и 352-2. В осветительной системе 300 драйвер 340 освещения подает выходной ток в первую и вторую LED нагрузки 352-1 и 352-2 через развязывающий трансформатор 322 для обеспечения гальванической развязки между драйвером 340 освещения и осветительным модулем 350.

Датчик(и) 354 считывает один или более рабочих параметров осветительного модуля 350 и отправляет упомянутые считанные данные во вторичный процессор 356. Такие рабочие параметры могут включать в себя ток и/или напряжение, подаваемые на каждую из первой и второй LED нагрузок 352-1 и 352-2, и/или рабочую температуру осветительного модуля 350.

В некоторых вариантах осуществления датчик(и) 354 может включать в себя один или более аналого-цифровых преобразователей (ADC) для преобразования измеренного значения (например, тока, напряжения или температуры) в цифровые считанные данные, которые могут обрабатываться вторичным процессором 356. В некоторых вариантах осуществления ADC может быть SRM85903K ADC. В некоторых вариантах осуществления ADC может выполнять ADC преобразование за время 2,33 мкс при подаче питающего напряжения 5 вольт и тактовой частоте 6 МГц. В этом случае в некоторых вариантах осуществления ADC может быть способен считывать ADC значения и запоминать соответствующие данные в связанном с ним пространстве памяти за время 10 мкс. В этом случае в некоторых вариантах осуществления, в которых вторичный процессор требует еще 10 мкс для обработки принятого сообщения и в худшем случае имеет время задержки на установку 5 мкс, это увеличивает общий период времени до 50 мкс для обработки полезных данных, удовлетворяя требованию непрерывной передачи полезных данных в течение 200 мкс.

Схема 358 обратной связи подает па драйвер 340 освещения сигнал обратной связи, который драйвер 340 освещения может использовать для регулировки выходного тока, который он подает в первую и вторую LED нагрузки 352-1 и 352-2. В некоторых вариантах осуществления схема 358 обратной связи может принимать от вторичного процессора 356 сигнал управления, из которого она генерирует сигнал обратной связи. В некоторых вариантах осуществления схема 358 обратной связи может содержать схему обратной связи c пропорциональным интегратором (PI), которая подает широтно-импульсную модуляцию на широтно-импульсный модулятор драйвера 340 освещения (который может включать в себя контроллер 342 и переключающие устройства 344-1 и/или 344-2) для регулировки выходного тока, который драйвер 340 освещения подает в первую и вторую LED нагрузки 352-1 и 352-2. В осветительном блоке 320 драйвер 340 освещения подает выходной ток в первую и вторую LED нагрузки 352-1 и 352-2 через развязывающий трансформатор 322 для обеспечения гальванической развязки между драйвером 340 освещения и осветительным модулем 350. В осветительном блоке 320 схема 358 обратной связи подает свой сигнал обратной связи на драйвер 340 освещения через второй оптический изолятор 324 для обеспечения гальванической развязки между драйвером 340 освещения и осветительным модулем 350.

Вторичный процессор 356 также связан с первичным процессором 310 для приема команд, которые вторичный процессор 356 выполняет для управления одной или более операциями осветительного блока 320, в частности, осветительного модуля 350. Например, вторичный процессор 356 может принимать одну или более команд от первичного процессора 310, чтобы считывать данные для определенных рабочих параметров осветительного блока 320 и подавать упомянутые считанные данные на первичный процессор 310. В ответ на считанные данные и/или одну или более команд от первичного процессора 310 вторичный процессор 356 может управлять параметрами схемы 358 обратной связи, чтобы регулировать сигнал обратной связи, подаваемый на драйвер 340 освещения, оказывая тем самым также воздействие на выходной ток, который подается драйвером 340 освещения в первую и вторую LED нагрузки 352-1 и 352-2.

Оптический изолятор 330 обеспечивает интерфейс между первичным процессором 310 и вторичным процессором 356. Оптический изолятор 330 создает возможность связи между первичным процессором 310 и вторичным процессором 356, гальванически изолируя при этом первичный процессор 310 и осветительный модуль 350 друг от друга. Первичный процессор 310 и вторичный процессор 356 могут сообщаться друг с другом через оптический изолятор 330 для обмена командами, откликами и данными. Практически значимо, что первичный процессор 310 связывается с вторичным процессором 356 в соответствии с симметричным протоколом связи, основанным на обмене сообщениями, который обеспечивает желаемую степень скорости, надежности и гибкости. Типовые варианты осуществления такого симметричного протокола связи, основанного на обмене сообщениями, будут описаны более подробно ниже. Посредством такого протокола связи первичный процессор 310 взаимодействует с вторичным процессором 356 для считывания и регулировки рабочих параметров осветительного блока 320.

В приводимом в качестве примера варианте осуществления как первичный процессор 310, так и вторичный процессор 356 могут включать в себя универсальный асинхронный приемник/передатчик (UART) для обеспечения связи друг с другом. В предпочтительном варианте построения, сигнал является последовательным потоком данных, который может обрабатываться обычным UART, способным работать при скоростях передачи и приема данных до 500 кбит/с. Если исходить из предположения, что в приводимом в качестве примера варианте осуществления к осветительной системе 300 предъявляется требование непрерывной передачи полезных данных за время 200 мкс, тогда скорость передачи данных в 350 кбит/с означает, что максимальная длина сообщения составляет 10 байтов (полагая, что один стартовый бит и один стоповый бит включены в состав каждого 8-битового байта). Кроме того, практически значимо, чтобы физический интерфейс между первичным процессором 310 и вторичным процессором 356, включающий в себя, например оптический изолятор 330, был способен поддерживать в изолированном режиме скорость передачи буферированных данных 1 Мбит/с для защиты от чрезмерного искажения на контактах первичного процессора 310 и вторичного процессора 356, соответственно.

В этом случае, в некоторых вариантах осуществления установочные параметры физической связи для осуществления связи между первичным процессором 310 и вторичным процессором 356 могут быть определены по приведенной ниже таблице 1.

Контроль по четности: отсутствует

Биты данных: 8

Стоповые биты: 1

Управление потоками: отсутствует

В приводимом в качестве примера варианте осуществления как первичный процессор 310, так и вторичный процессор 356 могут работать с тактовой частотой 16 МГц, обусловливая период подачи команд процессора равным 62,5 нс.

Тогда как на Фиг. 3 представлен вариант осуществления, в котором осветительный блок 320 является осветительным блоком, основанным на LED, в других вариантах осуществления осветительного блока 320 могут использоваться другие источники света, включающие в себя, не ограничиваясь нижеперечисленным, источники с элементами накаливания (например, лампы накаливания, галогенные лампы), люминесцентные источники света, фосфоресцирующие источники света, высокоинтенсивные разрядные источники (например, натриевые, ртутные и металло-галогенные лампы), лазеры, другие типы электролюминесцентных источников, пиро-люминесцентные источники (например, факелы), свечные люминесцентные источники (например, калильные сетки газового фонаря, дуговые лампы с угольным электродом), фотолюминесцентные источники (например, газоразрядные источники), катодолюминесцентные источники, использующие электронное насыщение, гальванолюминесцентные источники, кристаллолюминесцентные источники, кинелюминесцентные источники, термолюминесцентные источники, триболюминесцентные источники, сонолюминесцентные источники, радиолюминесцентные источники и люминесцентные полимеры. В некоторых из этих вариантов осуществления гальваническая развязка между первичным процессором и осветительным модулем 350, и между драйвером 340 освещения и осветительным модулем 350 может не потребоваться. В таких вариантах осуществления оптические изоляторы 330 и 324 могут отсутствовать, и первичный процессор 310 и вторичный процессор 356 могут соединяться непосредственно для осуществления связи.

Хотя на Фиг. 3 представлен вариант осуществления только с одним осветительным блоком 320, в других вариантах осуществления осветительная система 300 может включать в себя множество осветительных блоков 320, каждый из которых связан с первичным процессором 310 в соответствии с симметричным протоколом связи, основанным на обмене сообщениями, как описано ниже.

На Фиг. 4 представлена блок-схема последовательности операций, иллюстрирующая процесс 400 связи между первичным процессором и вторичным процессором, такими как первичный и вторичный процессоры на Фиг. 1-3. Процесс 400 может выполняться первичным и вторичным процессорами в любой из осветительных систем 200 и 300.

В операции 410 первичный процессор передает сообщение во встроенный вторичный процессор в соответствии с симметричным протоколом связи, основанным на обмене сообщениями. Это сообщение включает в себя команду для операции, подлежащей выполнению вторичным процессором. Варианты осуществления симметричного протокола связи, основанного на обмене сообщениями, будут описаны более подробно ниже. Команда может быть выбрана из набора разрешенных команд. В некоторых вариантах осуществления набор разрешенных команд включает в себя: (1) установку состояния вторичного процессора на одно из набора назначенных состояний; (2) запрос подтверждения от вторичного процессора, указывающего на то, готов ли к работе осветительный модуль, к которому принадлежит вторичный процессор; (3) установку значения широтно-импульсной модуляции для широтно-импульсного модулятора, включенного в состав осветительного блока, к которому принадлежит вторичный процессор; (4) запрос на передачу вторичным процессором выбранного набора считанных данных из группы назначенных наборов считанных данных; и (5) установку осветительного модуля в демонстрационный режим.

В некоторых вариантах осуществления набор назначенных состояний для вторичного процессора включает в себя активное состояние, состояние ожидания, состояние сброса, состояние сбережения электроэнергии и состояние мониторинга только тока.

В некоторых вариантах осуществления назначенные наборы считанных данных включают в себя: первый и второй токи, подаваемые в первый и второй источники света осветительного модуля, к которому принадлежит вторичный процессор; первый и второй токи, подаваемые в первый и второй источники света, и первое напряжение, подаваемое на первый источник света; первый и второй токи, подаваемые в первый и второй источники света, и второе напряжение, подаваемое на второй источник света; первый и второй токи, подаваемые в первый и второй источники света и температуру осветительного модуля; и первый и второй токи, подаваемые на первый и второй источники света, и значение широтно-импульсной модуляции для широтно-импульсного модулятора, включенного в состав осветительного блока, к которому принадлежит вторичный процессор.

В операции 420 встроенный вторичный процессор выполняет команду, принятую в операции 410. В некоторых вариантах осуществления это может включать в себя: (1) установку состояния вторичного процессора на одно из набора назначенных состояний; (2) установку значения широтно-импульсной модуляции для широтно-импульсного модулятора, включенного в состав осветительного блока, к которому принадлежит вторичный процессор; (3) сбор выбранного набора считанных данных из группы назначенных наборов считанных данных; и (4) установку осветительного модуля в демонстрационный режим.

В некоторых вариантах осуществления встроенный вторичный процессор может самостоятельно устанавливаться в назначенное состояние, выбранное из активного состояния, состояния ожидания, состояния сброса, состояния сбережения электроэнергии и состояния мониторинга только тока.

В операции 430 встроенный вторичный процессор передает сообщение в первичный процессор в соответствии с симметричным протоколом связи, основанным на обмене сообщениями. Это сообщение может включать в себя отклик на ранее принятую команду, посланную от первичного процессора вторичному процессору в операции 410. В некоторых вариантах осуществления упомянутый отклик может включать в себя считанные данные, запрошенные первичным процессором в ранее принятой команде. В некоторых вариантах осуществления упомянутый отклик может включать в себя подтверждение того, что осветительный блок готов к работе.

В операции 440 определяется, должен ли быть послан дополнительный отклик от вторичного процессора первичному процессору. Это может включать в себя передачу первичному процессору периодических обновлений считанных данных, таких как рабочий ток (токи), напряжение (напряжения), температура, и т.п., осветительного модуля. Если должны отправляться дополнительные отклики, то процесс возвращается к операции 430.

В операции 450 определяется, должны ли отправляться дополнительные команды от первичного процессора во вторичный процессор. Если дополнительные команды должны отправляться, процесс возвращается к операции 430.

Как отмечалось выше, осветительные системы 200 и 300, и процесс 400 выгодно используют симметричный протокол связи, основанный на обмене сообщениями. Практически значимо, что этот протокол может использовать кадры сообщений, каждый из которых включает в себя сообщение, соответствующее определенному формату сообщения. Практически значимо, что протокол симметричен в том смысле, что этот формат сообщения является одним и тем же как для исходящих сообщений, так и для входящих сообщений, наблюдаются ли они с позиции первичного процессора или с позиции вторичного процессора.

Подробное объяснение варианта осуществления симметричного протокола связи, основанного на обмене сообщениями, будет теперь дано в контексте осветительной системы 300, описанной выше и показанной на Фиг. 3. Конкретно, в этом примере осветительной системы 300 предполагается, что датчик(и) 354 включает в себя один или более ADC для преобразования одного или более измеренных значений (например, тока, напряжения и/или температуры) в цифровые считанные данные, которые могут обрабатываться вторичным процессором 356. В некоторых вариантах осуществления ADC может выполнять ADC преобразование за 2,33 мкс. В этом случае в некоторых вариантах осуществления, когда вторичный процессор требует дополнительные 10 мкс для обработки принятого сообщения и в худшем случае имеет время задержки на установку, равное 5 мкс, это увеличивает общий период времени до 50 мкс для обработки полезных данных, удовлетворяя требованию непрерывной передачи полезных данных в течение 200 мкс. Кроме того, как первичный процессор 310, так и вторичный процессор 356 могут включать в себя универсальный асинхронный приемник/передатчик (UART) при скоростях передачи и приема данных до 50 кбит/с. Физические установочные значения связи для осуществления связи между первичным процессором 310 и вторичным процессором 356 могут соответствовать приведенным выше в таблице 1. Дополнительно полагается, что к осветительной системе 300 предъявляется требование непрерывной передачи полезных данных в течение 200 мкс.

В этом случае скорость передачи данных 500 кбит/с означает, что максимальная длина сообщения составляет 10 байтов (исходя из предположения, что один стартовый байт и один стоповый байт включены в состав каждого 8-битового байта).

Имея в виду эти приведенные в качестве примера значения, теперь будет описан симметричный протокол связи, основанный на обмене сообщениями, который может быть использован первичным процессором 310 и вторичным процессором 356 для удовлетворения этих требований к связи.

На Фиг. 5 представлен один вариант осуществления формата 500 сообщения для одного варианта осуществления протокола связи, основанного на обмене сообщениями. Как показано на Фиг. 5, каждое сообщение от первичного процессора 310 к вторичному процессору 356 (то есть “прямое командное сообщение”) и от вторичного процессора 356 к первичному процессору 310 (то есть “обратное/возвращаемое сообщение”) имеют один и тот же формат 500 сообщения. Каждое сообщение может рассматриваться как кадр передачи данных, и термины “сообщение” и “кадр” могут использоваться здесь как взаимозаменяемые.

Формат 500 сообщения является следующим:

[SOF/MSGL]-[CMD/RESP]-([DATA(0)]…[DATA(x)]) -[CRC2]-[(CRC1/2)/EOF],

где символы в квадратных скобках означают один байт. Если, как объяснялось в приведенном выше примере, максимальная длина сообщения составляет 10 байтов, тогда из Фиг. 5 следует, что максимальная длина полезных данных ([DATA(0)]…[DATA(x)]) составляет шесть (6) байтов.

На Фиг. 5 SOF является полем 510 начала кадра, которое указывает начало сообщения; MSLG является полем 520 длины сообщения, которое указывает число байтов в текущем сообщении (включая сюда поле SOF, поле MSGL, поле CRC1/2 и поле EOF); CMD является полем 530 команд, которое указывает конкретную команду из набора разрешенных команд; RESP является полем 540 откликов, которое указывает конкретный ожидаемый отклик; DATA является полем 550 данных, содержащим от нуля до шести байтов полезных данных, связанных с конкретной командой или откликом; CRC является полем 560 CRC, которое включает в себя младшие 8 битов 16-битового значения циклического контроля избыточности для сообщения; CRC1/2 является другим полем CRC, которое включает в себя половину старших 8 битов 16-битового значения циклического контроля избыточности для сообщения; и EOF является полем 580 конца кадра, которое указывает конец сообщения.

В приводимом в качестве примера варианте осуществления поле SOF имеет длину в четыре бита и имеет заданное значение 0х01; поле MSGL имеет длину в четыре бита и может иметь значения в пределах от 1 до 8; поле CMD имеет длину в четыре бита, поддерживая до 16 разных команд; поле RESP имеет длину в четыре бита, поддерживая до 16 разных откликов; поле DATA является полем переменной длины от нуля до шести байтов, которое может включать в себя полезные данные и которое может включать в себя старшие четыре бита значения циклического контроля избыточности для сообщения; поле CRC2 является 8-битовым полем; CRC1/2 является полем из четырех битов; и поле EOF также является полем из четырех битов.

Практически значимо, что при формате 500 сообщения, как только процессор принимает сообщение и проверяет поле MSGL, процессор может легко определить, где начинаются и заканчиваются все другие поля в пределах сообщения. Кроме того, исследуя поле CMD и поле RESP, процессор может определить характер данных, включенных в состав поля DATA.

Как можно увидеть на Фиг. 5, в соответствии с симметричным протоколом связи, основанным на обмене сообщениями, при сообщениях, соответствующих формату 500 сообщения, каждое сообщение включает в себя поле CMD для передачи команд и поле RESP, которое может передавать отклик, ожидаемый на команду. Поле CMD может включать в себя команду, выбранную из набора разрешенных команд, соответствующих протоколу связи. Приведенная ниже таблица 2 является таблицей команд, представляющей набор разрешенных команд, которые могут быть включены в состав поля CMD сообщения согласно варианту осуществления протокола связи. При поле CMD из четырех битов набор разрешенных команд может включать в себя до шестнадцати разных команд.

команд

[SOF/MSGL]-[CMD/RESP]-DATA[0-x]-CRC2-[(CRC1/2)/EOF]:

Полезная нагрузка до 6 байтов

4-битовое значение состояния процессора.

Значения состояний:

0: Активное состояние вторичного процессора - Все события во вторичном процессоре активны, и вся подлежащая мониторингу информация передается в первичный процессор.

1: Состояние ожидания вторичного процессора - Ничего не отправляется в первичный процессор.

2: Мониторинг только критичных данных - В первичный процессор отправляются только значения Iout1 и Iout2.

3: Выключение электропитания - Ожидание отключения

электропитания, осуществление программного останова.

4: Сброс - Выполнение программного сброса.

Примечание: при вычислении CRC эти 4 старшие бита должны быть установлены на 0.

4 младшие бита указывают состояние вторичного процессора, которое должно быть установлено.

Значения состояний вторичного процессора могут быть {0,…,4}.

Расширяемы до 0xF.

Установка активного состояния

Вторичного процессора

[1,3]-[2,RESP]-[Z,0]- CRC2-[Z’,4]

[SOF/MSGL]=0x13→SOF=0x1,MSGL=0x3

[CMD/RESP]=0x0R→CMD= 0x2,RESP=0xR,

где R={0x0,…,0xF}.

[((CRC1)/2),DATA[0]]=0xZ0→ (CRC1)/2=0xZ,

DATA[0] =0x0,

где Z = старшие 4 бита CRC1 и Z’ - младшие 4 бита.

CRC2=0xYY→где 0xYY младшие 8 битов CRC16.

[(CRC1/2)/EOF]=0xW4 → (CRC1)/2=0xW,EOF=0x4,

где W = младшие 4 бита CRC1.

Возврат запрошенного отклика (RESP). См. перечень откликов в таблице откликов (Таблица 3).

Примечание: при вычислении CRC эти 4 старшие бита должны быть установлены на 0.

Младшие 4 бита устанавливаются на канал (PWMx, ADCx и т.п.) или устанавливаются на 0, если не используются.

Начало всех операций вторичного процессора и ожидание включения электропитания

Примечание:

предлагаемый RESP следующий: “Считывание всех сброшенных ADC” (см. ниже Таблицу 3)

Это даст всю необходимую информацию перед изменением состояния вторичного процессора от состояния ожидания до активного состояния посредством команды “Установка состояния вторичного процессора” (см. выше)

[SOF/MSGL]=0x13 → SOF=0x1,MSGL=0x3

[CMD/RESP]=0x1R → CMD = 0x1,RESP=0xR,

где R = {0x0,…0xF}

[((CRC1)/2,DATA[0])=0xZ0→ (CRC1)/2=0xZ,DATA[0]=0x0

(нет необходимых данных, устанавливаются на 0 для простоты),

где Z = 4 старшие бита CRC1 и Z' - 4 младшие бита CRC1.

CRC2=0xYY → где 0xYY - 8 младших битов CRC16.

[(CRC1/2)/EOF]=0xW4 → (CRC1)/2=0xW,EOF=0x4,

где W = 4 младшие бита CRC1.

Возврат запрошенного отклика (RESP). См. перечень откликов в таблице откликов (Таблица 3).

(Входящий отклик на ранее посланную команду)

Это отклик, который должен обрабатываться в соответствии с таблицей откликов (Таблица 3).

Возврат (входящий) запрошенного отклика (RESP) на посланную исходящую команду (CMD). См. перечень откликов в таблице откликов (Таблица 3). Протокол позволяет получать любые допустимые типы откликов (RESP) на все без исключения допустимые команды (CMD).

Примечание: наиболее частым кадром или сообщением является ответное сообщение. CMD поле=0 было выбрано, чтобы облегчить вычисление CRC и исключить дополнительные требования к функциям управления для электроники.

Примечание: при вычислении CRC эти 4 старшие бита должны быть установлены на 0.

Младшие 4 бита указывают номер PWM, который должен быть установлен. Номера PWM могут быть следующими: 0, 1, 2, 3.

Дистанционная установка PWM1 на 0х2345

(Обеспечивается поддержка для 16-битовой PWM)

[SOF/MSGL]=0x15→SOF=0x1,MSGL=0x5

[CMD/RESP]=0xDR→CMD=0xD,RESP=0xR,

где R={0x0,…,0xF}.

[((CRC1)/2),DATA[0]]=0xZ1→ (CRC1)/2=0xZ,DATA[0]=

0x1(PWM=1),

где Z = 4 старшие бита CRC1 и Z' - 4 младшие бита.

D1=0x23=35

D2=0x45=69

CRC2=0xYY → где 0xYY - младшие 8 битов CRC16.

[(CRC1/2/EOF]=0xW4 → (CRC1)/2=0xW,EOF=0x4,

где W = 4 младшие бита CRC1.

Возврат запрошенного отклика (RESP). См. перечень откликов в таблице откликов (Таблица 3).

Примечание: при вычислении CRC эти 4 старшие бита должны быть установлены на 0.

Младшие 4 бита указывают номер входа/выхода, состояние которого должно быть установлено. Номера входов/выходов могут быть следующими: 0, 1, 2, 3. Расширяемы до 15 входов/выходов.

Дистанционная установка состояния I/O[2]=Hi (высокий уровень)

[SOF/MSGL]=0x14→SOF=0x1,MSGL=0x4

[CMD/RESP]=0xDR→CMD=0xD,RESP=0xR,

где R={0x0,…0xF}.

[((CRC1)/2),DATA[0]]=0xZ1→ (CRC1)/2=0xZ,DATA[0]=

0x2(I/O=2),

где Z = старшие 4 бита CRC1 и Z' - младшие 4 бита.

D1=0x01=1

CRC2= 0xYY→где 0xYY младшие 8 битов CRC16.

[(CRC1/2)/EOF]=0xW4→ (CRC1)/2=0xW,EOF=0x4,

где W = 4 младшие бита CRC1.

Возврат запрошенного отклика (RESP). См. перечень откликов в таблице откликов (Таблица 3).

демонстрационного режима

4-битовое значение

Значения демонстрационного режима:

0: Demo Stop - Возвращение в нормальный режим работы

1: Demo(1) - Определяется пользователем

2: Demo(2) - Определяется пользователем

3: Demo(3) - Определяется пользователем

Примечание: при вычислении CRC эти 4 старшие бита должны быть установлены на 0.

4 младшие бита указывают значение демонстрационного режима, которое должно быть установлено.

Значения состояний вторичного процессора могут быть следующими: 0, 1, 2, 3. Расширяемы до 0xF.

Установка демонстрационного режима 3

[SOF/MSGL]=0x13→SOF=0x1,MSGL=0x3

[CMD/RESP]=0x3R→CMD=0x3,RESP=0xR,

где R={0x0,…0xF}.

[((CRC1)/2),DATA[0]]=0xZ3→ (CRC1)/2=0xZ,

DATA[0]=0x3.

где Z = 4 старшие бита CRC1 и Z' - 4 младшие бита.

CRC2=0xYY → где 0xYY младшие 8 битов CRC16.

[(CRC1/2)/EOF]=0xW4 → (CRC1)/2=0xW,EOF=0x4,

где W = 4 младшие бита CRC1.

Возврат запрошенных ответных данных (RESP). См. перечень откликов в таблице откликов (Таблица 3).

[(CRC1/2)/EOF]

Примечание: при вычислении CRC эти 4 старшие бита должны быть установлены на 0.

4 младшие бита устанавливаются на канал (PWMx, ADCx, и т.п.) или устанавливаются на 0, если не используются.

Получение отклика “Считывание значений ADC” {Iout1, Iout2}

[SOF/MSGL]=0x12→SOF=0x1,MSGL=0x2

[CMD/RESP]=0x30→CMD=0x3,RESP=0x0

[((CRC1)/2,DATA[0]]=0xZ0→ (CRC1)/2=0xZ,

DATA[0]=0x0,

где Z = 4 старшие бита CRC1 и Z' - 4 младшие бита.

CRC2=0xYY → где 0xYY младшие 8 битов CRC16.

[(CRC1/2)/EOF]=0xW4 → (CRC1)/2=0xW,EOF=0x4,

где W = 4 младшие бита CRC1.

Возврат запрошенных ответных данных (RESP). См. перечень откликов в таблице откликов (Таблица 3).

Поле откликов (RESP) может включать в себя отклик, выбранный из набора разрешенных откликов, соответствующих протоколу связи. Приведенная ниже таблица 3 является таблицей откликов, в которой представлен набор разрешенных откликов, которые могут быть включены в поле откликов (RESP) сообщения согласно варианту осуществления протокола связи. При поле RESP из четырех битов набор разрешенных откликов может включать в себя до шестнадцати разных откликов.

откликов

(RESP)

[SOF/MSGL]-[CMD/RESP]-DATA[0-x]-CRC2-[(CRC1/2)/EOF]:

(Полезная нагрузка 6 байтов)

Примечания:

a) SOF занимает 4 старшие бита, а MSGL занимает 4 младшие бита. Это возможно, поскольку максимальная длина кадра составляет 16 байтов.

b) CMD занимает 4 старшие бита, а RESP занимает 4 младшие бита. Это будет ограничивать числом 16 максимальное количество как команд, так и откликов.

c) Поскольку значение Iout[1,2] всегда будет включаться в Data[0,…,3], используются 24 бита для тока и дополнительные 4 бита для четырех старших битов CRC1. Кроме того, EOF занимает 4 бита, и дополнительные 4 бита используются для 4 младших битов CRC1.

Может использоваться как указание “готовности к работе вторичного процессора”.

Примечание:

знаком для ACK является 0х06. Мы будем использовать 0х6 в целях оптимизации.

Прием ACK кадра

[SOF/MSGL]=0x13→SOF=0x1,MSGL=0x3

[CMD/RESP]=0x03→CMD=0x0,RESP=0x3

[((CRC1)/2),DATA[0]]=0xZ6 → (CRC1)/2=0xZ,

DATA[0]=0x6=(ACK),

где Z=4 старшие бита CRC1 и Z' - 4 младшие бита.

CRC2=0xYY→где 0xYY младшие 8 битов CRC16.

[(CRC1/2)/EOF]=0xW → (CRC1)/2=0xW,EOF=0x4,

где W = 4 младшие бита CRC1.

Rset{1,2,3}

Макс. 12 битов каждое

DATA[1]-DATA[2]-DATA[3]-DATA[4]-DATA[5]-CRC2-

[((CRC1)/2,EOF]

Rset1=1023=0x3FF

Rset2= 23=0x017

Rset3= 910=0x38E

[Z'4] →

0x18-0x01-0xZ3-0xFF-0x00-0x17-0x03-0x8E-CRC2-0xZ’4

[SOF/MSGL]=0x18 → SOF=0x1,MSGL=0x8

[CMD/RESP]=0x01 → CMD=0x0,RESP=0x1

[((CRC1)/2,DATA[0]=0xZ3 → (CRC1)/2=0xZ,

где Z = 4 старшие бита CRC1 и Z' - 4 младшие бита.

Rset1=0x3FF → DATA[0]=0x3,DATA[1]=0xFF

Rset2=0x017 → DATA[2]=0x00,DATA[3]=0x17

Rset3=0x38E → DATA[4]=0x03,DATA[5]=0x8E

CRC2=0xYY → где 0xYY младшие 8 битов CRC16.

[(CRC1/2)/EOF]=0xW4 → (CRC1)/2=0xW,EOF=0x4,

где W = 4 младшие бита CRC1.

{Iout1, Iout2, Vout1}

DATA[1]-DATA[2]-DATA[3]-CRC2-[((CRC1)/2),EOF]

Iout1=1023=0x3FF

Iout2= 910=0x38E

→

0x16-0x00-0xZ3-0xFF-0x03-0x8E-CRC2-0xZ’4

[SOF/MSGL]=0x16 → SOF=0x1,MSGL=0x6

[CMD/RESP]=0x00 → CMD=0x0,RESP=0x0

[((CRC1)/2,DATA[0]]=0xZ3 → (CRC1)/2=0xZ,

где Z = 4 старшие бита CRC1 и Z' - 4 младшие бита.

Iout1=0x3FF → DATA[0]=0x3,DATA[1]=0xFF

Iout2=0x38E → DATA[4]=0x03,DATA[5]=0x8E

CRC2=0xYY → где 0xYY младшие 8 битов CRC16.

[(CRC1/2)/EOF]=0xW4 → (CRC1)/2=0xW,EOF=0x4,

где W = 4 младшие бита CRC1.

{Iout1, Iout2, Vout1}

DATA[1]-DATA[2]-DATA[3]-DATA[4]-DATA[5]-CRC2-[((CRC1)/2),EOF]

Iout1=1023=0x3FF

Iout2= 23=0x017

Vout1= 910=0x38E

[SOF/MSGL]=0x18 → SOF=0x1,MSGL=0x8

[CMD/RESP]=0x04 → CMD=0x0,RESP=0x4

[((CRC1)/2),DATA[0]]=0xZ3 → (CRC1)/2=0xZ,

где Z = 4 старшие бита CRC1 и Z' - 4 младшие бита.

Iout1=0x3FF → DATA[0]=0x3,DATA[1]=0xFF

Iout2=0x017 → DATA[2]=0x00,DATA[3]=0x17

Vout1=0x38E → DATA[4]=0x03,DATA[5]=0x8E

CRC2=0xYY → где 0xYY младшие 8 битов CRC16.

[(CRC1/2)/EOF]=0xW4 → (CRC1)/2=0xW,EOF=0x4,

где W = 4 младшие бита CRC1.

{Iout1, Iout2, Vout2}

DATA[1]-DATA[2]-DATA[3]-DATA[4]-DATA[5]-CRC2-[((CRC1)/2),EOF]

Iout1=1023=0x3FF

Iout2= 23=0x017

Vout2= 910=0x38E

[SOF/MSGL]=0x18 → SOF=0x1,MSGL=0x8

[CMD/RESP]=0x05 → CMD=0x0,RESP=0x5

[((CRC1)/2),DATA[0]]=0xZ3 → (CRC1)/2=0xZ,

где Z = 4 старшие бита CRC1 и Z' - 4 младшие бита.

Iout1=0x3FF → DATA[0]=0x3,DATA[1]=0xFF

Iout2=0x017 → DATA[2]=0x00,DATA[3]=0x17

Vout2=0x38E → DATA[4]=0x03,DATA[5]=0x8E

CRC2=0xYY → где 0xYY младшие 8 битов CRC16.

[(CRC1/2)/EOF]=0xW4 → (CRC1)/2=0xW,EOF=0x4,

где W = 4 младшие бита CRC1.

{Iout1, Iout2, TC (температура)}

DATA[1]-DATA[2]-DATA[3]-DATA[4]-DATA[5]-CRC2-[((CRC1)/2),EOF]

Iout1=1023=0x3FF

Iout2= 23=0x017

TC = 910=0x38E

[SOF/MSGL]=0x18 → SOF=0x1,MSGL=0x8

[CMD/RESP]=0x06 → CMD=0x0,RESP=0x6

[((CRC1)/2),DATA[0]]=0xZ3 → (CRC1)/2=0xZ,

где Z = 4 старшие бита CRC1 и Z' - 4 младшие бита.

Iout1=0x3FF → DATA[0]=0x3,DATA[1]=0xFF

Iout2=0x017 → DATA[2]=0x00,DATA[3]=0x17

TC=0x38E → DATA[4]=0x03,DATA[5]=0x8E

CRC2=0xYY → где 0xYY младшие 8 битов CRC16.

[(CRC1/2)/EOF]=0xW4 → (CRC1)/2=0xW,EOF=0x4,

где W = 4 младшие бита CRC1.

{Iout1, Iout2, ADC#}

DATA[1]-DATA[2]-DATA[3]-DATA[4]-DATA[5]-CRC2-[((CRC1)/2),EOF]

Iout1=1023=0x3FF

Iout2= 23=0x017

ADC2= 910=0x38E

ADC номер 2 для считывания

[SOF/MSGL]=0x18 → SOF=0x1,MSGL=0x8

[CMD/RESP]=0x07 → CMD=0x0,RESP=0x7

[((CRC1)/2),DATA[0]]=0xZ3 → (CRC1)/2=0xZ,

где Z = 4 старшие бита CRC1 и Z' - 4 младшие бита.

Iout1=0x3FF → DATA[0]=0x3,DATA[1]=0xFF

Iout2=0x017 → DATA[2]=0x00,DATA[3]=0x17

ADC2=0x38E → DATA[4]=0x23,DATA[5]=0x8E

4 старшие бита являются номером ADC.

CRC2=0xYY → где 0xYY младшие 8 битов CRC16.

[(CRC1/2)/EOF]=0xW4 → (CRC1)/2=0xW,EOF=0x4,

где W = 4 младшие бита CRC1.

{Iout1, Iout2, PWM#}

12 битов максимум

DATA[1]-DATA[2]-DATA[3]-DATA[4]-DATA[5]-CRC2-[((CRC1)/2),EOF]

Iout1=1023=0x3FF

Iout2= 23=0x017

PWM4= 910=0x38E

PWM номер 4 для считывания

[SOF/MSGL]=0x18 → SOF=0x1,MSGL=0x8

[CMD/RESP]=0x08 → CMD=0x0,RESP=0x8

[((CRC1)/2),DATA[0]]=0xZ3 → (CRC1)/2=0xZ,

где Z = 4 старшие бита CRC1 и Z' - 4 младшие бита.

Iout1=0x3FF → DATA[0]=0x3,DATA[1]=0xFF

Iout2=0x017 → DATA[2]=0x00,DATA[3]=0x17

PWM4=0x38E → DATA[4]=0x43,DATA[5]=0x8E

4 старшие бита являются номером PWM.

CRC2=0xYY → где 0xYY младшие 8 битов CRC16.

[(CRC1/2)/EOF]=0xW4 → (CRC1)/2=0xW,EOF=0x4,

где W = 4 младшие бита CRC1.

{Iout1, Iout2, I/O#}

DATA[1]-DATA[2]-DATA[3]-DATA[4]-CRC2-[((CRC1)/2,EOF]

Iout1=1023=0x3FF

Iout2= 23=0x017

Уровень принимаемого сигнала на I/O 3 высокий

0: низкий уровень

1: высокий уровень

2: PWM

3: ADC

5: ошибка

Ответным сообщением по умолчанию является “ошибка” для входа/ выхода, не поддерживаемого приложением

[SOF/MSGL]=0x17 → SOF=0x1,MSGL=0x7

[CMD/RESP]=0x09 → CMD=0x0,RESP=0,9

[((CRC1)/2),DATA[0]=0xZ3 → (CRC1)/2=0xZ,

где Z = 4 старшие бита CRC1 и Z' - 4 младшие бита.

Iout1=0x3FF → DATA[0]=0x3,DATA[1]=0xFF

Iout2=0x017 → DATA[2]=0x00,DATA[3]=0x17

DATA[4]=0x31 → I/O номер =0x3, I/O состояние=0x1.

4 старшие бита являются номером I/O.

CRC2=0xYY → где 0xYY младшие 8 битов CRC16.

[(CRC1/2)EOF]=0xW4 → (CRC1)/2=0xW,EOF=0x4,

где W = 4 младшие бита CRC1.

[информация о версии состоит из: версия старшая (major), младшая (minor), исправленная (revision), версия протокола (protocol version)]

DATA[1]-DATA[2]-DATA[3]-DATA[4]-DATA[5]-DATA[6]-CRC2-[((CRC1)/2),EOF]

ПРИМЕЧАНИЕ: этот RESP=0xA не должен использоваться при нахождении в режиме выборки Iout. По этой причине допустим один дополнительный байт полезной нагрузки.

Major=0x03

Minor=0x0046

Revision=0x002D

Protocol revision=0x01

[SOF/MSGL]=0x19 → SOF=0x1,MSGL=0x9

[CMD/RESP]=0x0A → CMD=0x0,RESP=0xA

[((CRC1)/2),RESERVED]=0xZ0 → (CRC1)/2=0xZ,

где Z = 4 старшие бита CRC1 и Z' - 4 младшие бита.

DATA[0]=Reserved=0

Major=0x03 → DATA[1]=0x03

Minor=ox0046 → DATA[2]=0x00,DATA[3]=0x46

Revision=0x002D → DATA[4]=0x00,DATA[5]=0x2D

Protocol revision=0x01 → DATA[6]=0x01

CRC2=0xYY → где 0xYY младшие 8 битов CRC16.

[(CRC1/2)/EOF]=0xW4 → (CRC1)/2=0xW,EOF=0x4,

где W = 4 младшие бита CRC1.

Как отмечалось выше, каждое сообщение/кадр проверяется с помощью 16-битового (2 байта) циклического избыточного кода (CRC).

В некоторых вариантах осуществления процессор (например, первичный процессор или вторичный процессор, описанные выше), который передает сообщение/кадр, может вычислять CRC для сообщения/кадра в реальном времени согласно алгоритму, представленному ниже в таблице 4.

{

//NOTE: CRC-CCITT (XModem)

unsigned long int crc;

unsigned short c;

unsigned int crc_rtn;

int i=0;

unsigned long int data[32]={0};

crc=0;

i=o;

for (i=count-1; i >= 0; i--)

{

data[i]= (( unsigned long int ) *ptr++ & 0x00FF);

}

while(--count >= 0)

{

crc = crc ^ (data[count] << 8);

i=8;

do

{

c = ((unsigned short) i) << 8;

if( (crc ^ c) & 0x8000)

{

}

else

{

crc = ( crc << 1 ) ;

}while(--i);

}

crc_rtn = ((unsigned int) crc & 0xFFFF );

return (crc_rtn);

}

В некоторых вариантах осуществления принимающий процессор (например, первичный процессор или вторичный процессор, как описано выше), который принимает сообщение/кадр, может осуществлять контроль CRC для принимаемого сообщения/кадра в реальном времени согласно алгоритму, представленному ниже в таблице 5.

unsigned int CRC_calc=0;

CRC_calc = Calc_CRC ( &data[SOF+2], sizeof(data)-3);

if(((CRC_calc & 0x00FF) == CRC2) && (((CRC_calc & 0xFF00) >> 8 )== CRC1))

{

CRC_valid = TRUE;

}

else

{

CRC_valid = FALSE;

}

Хотя протокол связи, обсуждаемый выше, был подробно описан применительно к осветительной системе с LED осветительными блоками, этот протокол связи имеет более широкое применение для осуществления связи между встроенными процессорами, в частности, в электронных системах электропитания, например в осветительных системах, которые используют пускорегулирующие устройства или драйверы, включая сюда системы с газоразрядными источниками света высокой интенсивности (HID), люминесцентными источниками света, источниками света на основе полупроводников, и т.п.

Хотя здесь были описаны и проиллюстрированы несколько вариантов осуществления, специалисты в данной области техники легко представят себе множество других средств и/или структур для выполнения функционального назначения, и/или для достижения результатов и/или одного или более преимуществ, описанных здесь, и каждое их этих множеств и/или модификаций будет укладываться в объем вариантов осуществления изобретения, описанных здесь. В более общем смысле специалисты в данной области техники без труда поймут, что все параметры, размеры, материалы и конфигурации, описанные здесь, приводятся в качестве примера, и что реальные параметры, размеры, материалы и/или конфигурации будут зависеть от конкретного применения или применений, в которых используются относящиеся к изобретению технические средства. Специалисты в данной области техники осознают или смогут установить, используя всего лишь обычное экспериментальное исследование, многие эквиваленты конкретным вариантам осуществления изобретения, описанным здесь. Поэтому должно быть понятно, что приведенные выше варианты осуществления представлены только в качестве примера и что, не отклоняясь от объема прилагаемых пунктов формулы изобретения и их эквивалентов, варианты осуществления изобретения могут быть практически осуществлены другим образом, чем конкретно описанный и заявленный. Варианты осуществления изобретения в настоящем описании направлены на каждый отдельный признак, систему, предмет, материал, комплект или способ, описанные здесь. Кроме того, любое сочетание двух или более таких признаков, систем, предметов, материалов, комплектов и/или способов, если такие признаки, системы, предметы, материалы, комплекты и/или способы взаимно не противоречат друг другу, включается в объем изобретения по настоящему описанию.

Следует также понимать, что если четко не оговорено иное, в любых способах, заявленных здесь, которые включают в себя более одного этапа или действия, порядок этих этапов или действий в данном способе не обязательно ограничивается тем порядком, в котором изложены этапы и действия способа.

Кроме того, в пунктах формулы изобретения заключенные в круглые скобки цифровые позиционные обозначения, если таковые имеются, приведены всего лишь для удобства и никоим образом не должны рассматриваться как ограничивающие.

В пунктах формулы изобретения, так же как и в изложенном выше описании, все переходные выражения, такие как “содержащий”, “включающий в себя”, “несущий”, “имеющий”, “вовлекающий”, “удерживающий”, “составленный из”, и т.п., должны пониматься как допускающие возможность расширения, то есть означать включение чего-то в себя, но не ограничение этим. Только переходные выражения “состоящий из” и “состоящий исключительно из” будут закрытыми или полузакрытыми переходными выражениями, соответственно.

Изобретение относится в целом к обмену информацией между встроенными процессорами в осветительной системе. Техническим результатом является обеспечение обратной связи и управления в электронных системах электропитания и более конкретно в осветительных системах. Результат достигается тем, что система (100, 200, 300) включает в себя осветительный блок (120, 220, 320), оптический изолятор (230, 330) и первичный процессор (110, 210, 310). Осветительный блок включает в себя осветительный модуль (250, 350) и драйвер (240, 340) освещения, подающий электропитание на осветительный модуль. Осветительный модуль включает в себя: один или более источников (252-1/252-2, 352-1/352-2) света, один или более датчиков (254, 354) для считывания данных, включающих в себя один или более рабочих параметров осветительного модуля, и вторичный процессор (156, 256, 356), принимающий считанные данные. Первичный процессор и вторичный процессор связываются друг с другом через оптический изолятор в соответствии с протоколом связи, основанным на обмене сообщениями, в котором каждое сообщение, пересылаемое между первичным процессором и вторичным процессором, имеет идентичный формат (500) сообщения и включает в себя поле (530) команд и поле откликов, причем поле (550) откликов обеспечено для указания отклика на команду. 2 н. и 18 з.п. ф-лы, 5 ил.

1. Система (100, 200, 300), которая содержит:

осветительный блок (120, 220, 320), включающий в себя:

драйвер (240, 340) освещения, и

осветительный модуль (250, 350), запитываемый электропитанием от драйвера освещения, причем упомянутый осветительный модуль включает в себя

- один или более источников (252-1/252-2, 352-1/352-2) света,

- один или более датчиков (254, 354) для считывания данных, указывающих один или более рабочих параметров осветительного модуля, и

- вторичный процессор (156, 256, 356), выполненный с возможностью приема считанных данных, указывающих один или более рабочих параметров осветительного модуля;

оптический изолятор (220,320); и

первичный процессор (110, 210, 310), выполненный с возможностью мониторинга одного или более рабочих параметров осветительного модуля,

причем первичный процессор и вторичный процессор связываются друг с другом через оптический изолятор в соответствии с протоколом связи, основанным на обмене сообщениями, в котором каждое сообщение, пересылаемое между первичным процессором и вторичным процессором, имеет идентичный формат (500) сообщения и включает в себя поле (530) команд и поле (550) откликов, причем поле откликов обеспечено для указания отклика на команду.

2. Система (100, 200, 300) по п. 1, в которой каждое сообщение дополнительно включает в себя:

поле (510) начала кадра;

поле (580) конца кадра;

поле (520) длины сообщения; и

биты циклического контроля избыточности (CRC) для полного соответствия сообщения контрольной сумме за исключением самих битов CRC и полей начала кадра, конца кадра и длины сообщения.

3. Система (100, 200, 300) по п. 1, в которой один или более рабочих параметров включают в себя ток, подаваемый по меньшей мере в один из одного или более источников света, напряжение, подаваемое по меньшей мере на один из одного или более источников света, и рабочую температуру осветительного модуля.

4. Система (100, 200, 300) по п. 3, в которой один или более источников света включают в себя по меньшей мере два источника света.

5. Система (100, 200, 300) по п. 1, в которой поле команд включает в себя команду, выбранную из набора разрешенных команд, причем упомянутый набор разрешенных команд включает в себя: установку состояния вторичного процессора на одно из набора назначенных состояний; запрос подтверждения от вторичного процессора, указывающего, готов ли к работе осветительный модуль; установку значения широтно-импульсной модуляции для широтно-импульсного модулятора (342/344-1/344-2), включенного в состав осветительного блока, и запрос на передачу вторичным процессором выбранного набора считанных данных из группы назначенных наборов считанных данных.

6. Система (100, 200, 300) по п. 5, в которой набор разрешенных команд дополнительно включает в себя установку осветительного модуля в демонстрационный режим.

7. Система (100, 200, 300) по п. 5, в которой набор назначенных состояний включает в себя активное состояние, состояние ожидания, состояние сброса, состояние сбережения электроэнергии и состояние мониторинга только тока.

8. Система (100, 200, 300) по п. 5, в которой один или более источников света включают в себя по меньшей мере первый и второй источники света и в которой назначенные наборы считанных данных включают в себя: первый и второй токи, подаваемые в первый и второй источники света; первый и второй токи, подаваемые в первый и второй источники света, и первое напряжение, подаваемое на первый источник света; первый и второй токи, подаваемые в первый и второй источники света, и второе напряжение, подаваемое на второй источник света; первый и второй токи, подаваемые в первый и второй источники света, и температуру осветительного модуля; и первый и второй токи, подаваемые в первый и второй источники света, и значение широтно-импульсной модуляции для широтно-импульсного модулятора (342/344-1/344-2), включенного в состав осветительного блока.

9. Система (100, 200, 300) по п. 1, в которой формат сообщения является следующим:

[SOF/MSGL]-[CMD/RESP]-([DATA(0)]…[DATA(x)])-[CRC2]-[(CRC1/2)/EOF],

где:

SOF указывает начало сообщения, MSLG указывает длину сообщения, CMD указывает конкретную команду, RESP указывает

конкретный ожидаемый отклик, DATA указывает данные, связанные с конкретной командой или откликом, CRC2 указывает младшие 8 битов 16-битового значения циклического контроля избыточности для сообщения, CRC1/2 указывает половину старших 8 битов 16-битового значения циклического контроля избыточности для сообщения и EOF указывает конец сообщения.

10. Система (100, 200, 300) по п. 1, в которой осветительный блок дополнительно включает в себя широтно-импульсный модулятор (342/344-1/344-2) для регулировки выходного уровня драйвера освещения, причем один или более рабочих параметров включают в себя значение широтно-импульсной модуляции для широтно-импульсного модулятора.

11. Система по п. 1, в которой осветительный блок дополнительно включает в себя второй оптический изолятор (324), выполненный с возможностью подачи сигнала обратной связи от осветительного модуля к драйверу освещения.

12. Система по п. 1, в которой как вторичный процессор, так и первичный процессор включают в себя универсальный асинхронный приемник/передатчик для связи друг с другом.

13. Способ (400), который содержит:

во вторичном процессоре (156, 256, 356), встроенном в осветительный модуль (250, 350), который включает в себя один или более источников (252-1/252-2, 352-1/352-2) света, прием (410) от первичного процессора (210, 310) первого сообщения, переданного согласно протоколу связи, основанному на обмене сообщениями, в котором каждое сообщение, пересылаемое между первичным процессором и вторичным процессором, имеет идентичный формат (500) сообщения и включает в себя поле (530) команд и поле (550) откликов, причем поле откликов обеспечено для указания отклика на команду;

выполнение (420) первой операции в осветительном модуле в ответ на первую команду, включенную в поле команд первого сообщения; и

отправку (430) от вторичного процессора первичному процессору второго сообщения согласно протоколу связи, основанному на обмене сообщениями, причем упомянутое второе сообщение включает в себя, в поле откликов, первый отклик на первую команду, принятую в первом сообщении.

14. Способ (400) по п. 13, в котором первая команда содержит запрос вторичному процессору на отправку в первичный процессор выбранных данных, считанных в осветительном модуле, указывающих один или более рабочих параметров осветительного модуля.

15. Способ (400) по п. 14, в котором выполнение первой операции в осветительном модуле включает в себя считывание выбранных данных и в котором второе сообщение дополнительно включает в себя упомянутые выбранные данные.

16. Способ (400) по п. 13, в котором формат сообщения является следующим:

[SOF/MSGL]-[CMD/RESP]-([DATA(0)]…[DATA(x)])-[CRC2]-[(CRC1/2)/EOF],