Изобретение относится к области вычислительной техники, предназначено для построения систем цифровой обработки сигналов в реальном масштабе времени.

Разработанное техническое решение основано на использовании шины (I-Bus), соединяющей между собой устройства, участвующие в приеме, ретрансляции, обработке информации в реальном масштабе времени. Через указанную шину происходит распределение первичных или предобработанных данных для дальнейшей обработки. Данные передают в формате PCI-Express пакетов.

Известна система TSPANU, предназначенная для обработки сигналов в гидроакустических комплексах. Ее описание приведено в статье Н.М. South и др. Tecnologies for Sonar Processing JOHNS HOPKINS APL Technical Digest, VOLUME 19, NUMBER 4, 1998.

Известен (RU, патент 2207620, опубл. 27.06.2003) цифровой вычислительный комплекс (ЦВК) для обработки сигналов в гидроакустических системах.

Цифровой вычислительный комплекс (ЦВК) для обработки сигналов в гидроакустических системах в реальном масштабе времени представляет собой модульную, реконфигурируемую архитектуру, содержащий группу индивидуальных процессоров, объединенных одной высокоскоростной шиной, схемой управления и общей памятью. При этом указанные индивидуальные процессоры выполнены на базе двухпортовых сигнальных микропроцессоров. ЦВК содержит несколько групп индивидуальных процессоров, причем группы индивидуальных процессоров объединены в один или несколько модулей программируемых процессоров (ППС). В ЦВК введены также один или несколько модулей ЭВМ, выполненных на базе универсальных микропроцессоров, и модулей пульта, включающего один или два монитора, пультовую ЭВМ, клавиатуру и манипулятор, ко входам модулей ППС, являющимся входами ЦВК, и между модулями ППС включены радиальные каналы передачи обрабатываемых сигналов, в ЦВК введены две сети Ethernet, при этом модули ППС объединены с модулями ЭВМ одной, а модули ЭВМ объединены с модулями пультов другой сетью Ethernet, в ЦВК введены две магистральные шины последовательного интерфейса типа Манчестер-2 для обмена данными и управляющими воздействиями с внешними системами, причем все модули ППС соединены с одной, а модули ЭВМ и модули пультов с другой магистральной шиной интерфейса Манчестер-2.

Недостатком известных технических решений следует признать непригодность их для достижения нижеуказанного технического результата.

TSPANU, в частности, не оптимальна для обработки данных в реальном масштабе времени, при этом имеет относительно невысокую производительность, а вышеперечисленный ЦВК не отвечает требованиям современного комплекса распределения данных. А именно: ЦВК обладает кольцевыми входными и выходными шинами, что означает ограниченную максимальную пропускную способность шины, и при наличии необходимости обработать поток данных большего объема мы упираемся в ограничение архитектуры комплекса.

В I-Bus же используют распределение потоков через неблокирующие коммутаторы в контроллере I-Bus и неблокирующие коммутаторы PCI-Express, поэтому добавление дополнительного контроллера I-Bus и соответствующее наращивание входного потока данных не влияет существенно на производительность остальных устройств. Архитектура I-Bus и решетка (lattice) в I-Bus контроллере оптимизированы под количественное распределение поступающего потока данных, то есть внутри потока не выделяются/разделяются данные по каким-либо отличительным признакам, а происходит равномерное распределение данных по контроллерам.

Техническая задача, решаемая посредством разработанного способа, состоит в разработке нового способа передачи информации между физическими объектами.

Технический результат, достигаемый при реализации разработанного способа, состоит в использовании формата пакетов стандарта PCI-Express для передачи как по последовательным, так и по параллельным шинам, позволяя использовать существующее оборудование (где отсутствуют последовательные приемопередатчики), а также упрощения конфигурации системы в целом, что позволяет уменьшить энергопотребление.

Для достижения указанного технического результата предложено использовать разработанный способ передачи информации между физическими объектами. Согласно разработанному способу информацию в формате PCI-Express пакетов передают как по последовательным высокоскоростным каналам связи, так и по параллельной шине и, в зависимости от адреса в пакете, осуществляют перенаправление данных либо внутрь контроллера, либо на внешнюю шину PCI-Express и далее через коммутатор PCI-Express на и другие контроллеры I-Bus, при этом коммутатор PCI-Express выполнен с возможностью передавать пакет одновременно нескольким контроллерам, контроллер I-Bus выполнен с возможностью работы в режиме удвоенной скорости обработки потока, причем предварительно проводят определение количества необходимых оконечных станций и коммутаторов с определением необходимой топологии каналов связи между ними, с использованием пропускания через используемые каналы связи конфигурационных пакетов, настраивают используемые коммутаторы и оконечные устройства для приема/передачи информации, передаваемую информацию разбивают на пакеты для передачи по стандарту PCI-Express размером полезных данных не свыше 4 килобайт, при этом каждый пакет состоит из заголовка и поля данных, предназначенного в том числе и для записи передаваемой информации, при этом заголовок содержит информацию о типе пакета, адрес отправителя пакета и адрес приемника, в качестве формата обмена данными используют уровни PCI-Express, а именно: Physical Layer, Data Link Layer, Transaction Layer.

Разработанный способ основан на следующих положениях:

- Пакеты PCI-Express передают как по последовательным, так и по параллельным шинам;

- Используют упрощенную систему конфигурирования PCI-Express;

- Используют передачу пакетов одновременно нескольким абонентам (multicast) с упрощенным конфигурированием этого механизма;

- I-Bus контроллер имеет режим удвоенной скорости обработки потока.

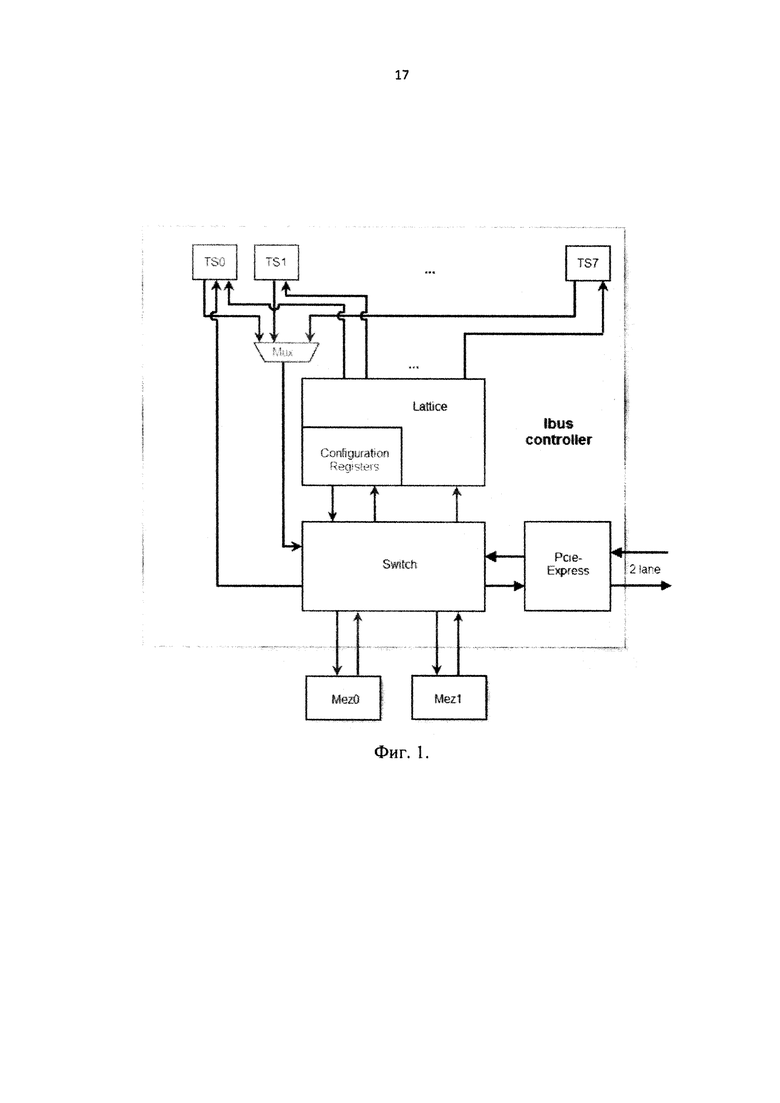

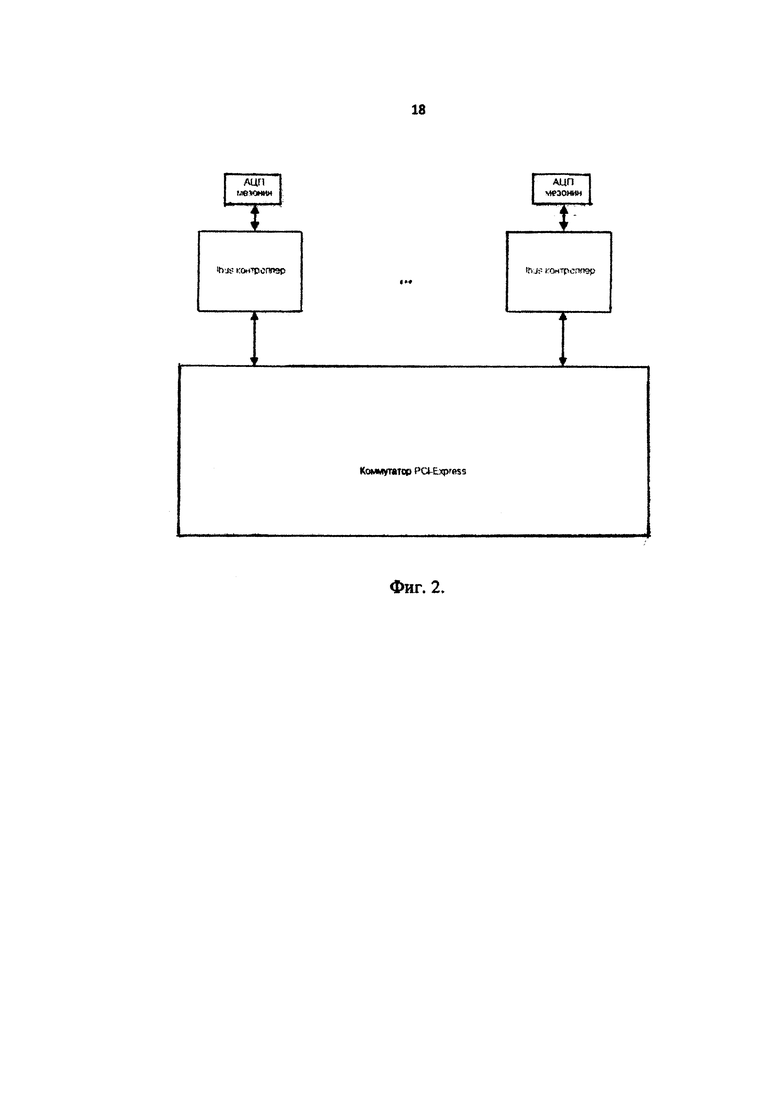

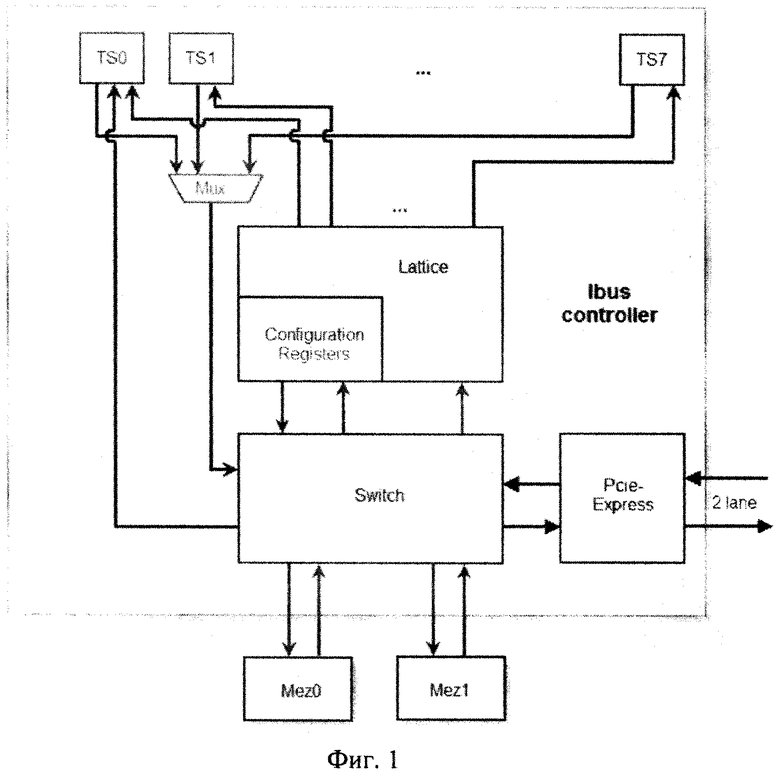

Схема I-Bus контроллера приведена на фиг. 1. На фиг. 2 представлена схема конфигурации I-Bus контроллера.

Первичные данные поступают с мезонинов (Mez1 и Mez2), далее по параллельной шине направляются в I-Вus контроллер, где в зависимости от адреса в пакете происходит перенаправление данных:

- либо на внешнюю шину PCI-Express и далее через коммутатор PCI-Express на другие контроллеры I-Bus;

- либо во внутренний обработчик данных (Lattice) и далее в сигнальные процессоры TS0…TS7;

- либо напрямую в процессор TS0.

Внутренний обработчик данных контроллера в соответствии со своей конфигурацией распределяет данные по восьми сигнальным процессорам TS0…TS7.

Ширина шины PCI-Expressy контроллера и коммутатора равна 2lane.

Коммутатор PCI-Express имеет возможность передавать пакет одновременно нескольким контроллерам (групповая рассылка). Признаком того, что пакет адресован нескольким абонентам, является соответствующий бит в адресе. По сравнению со стандартом PCI-Express в шине I-Bus групповая рассылка реализована проще, следовательно, не нужны дополнительные ресурсы микросхем.

Мезонин АЦП передает по параллельной шине информацию в формате PCI-Express пакетов в I-Bus-контроллер. В зависимости от адреса в пакете, I-Bus-контроллер направляет пакет либо в коммутатор PCI-Express, либо в обработчики пакетов в I-Bus-контроллере. Связь между I-Bus-контроллером и коммутатором PCI-Express осуществляют по последовательной шине PCI-Express со скоростью 2.5 Гигабит/сек.

В I-Bus все данные передают в пакетном базисе стандарта PCI-Express. Существуют следующие основные типы обращений (передачи и запросы на передачу данных):

- Конфигурационные обращения. Конфигурационная запись и конфигурационное чтение.

- Обращения типа MemoryWrite (запись данных).

- Обращение типа MemoryRead (чтение данных).

В свою очередь, обращения типа MemoryWrite или MemoryRead могут быть 32- или 64-разрядными. В первом случае используют пакеты с заголовком, состоящим из 3-х слов (3DW), во втором - с заголовком, состоящим из 4-х слов (4DW).

Ниже приведены типы пакетов, используемые для обмена между устройствами комплекса по шине I-Bus.

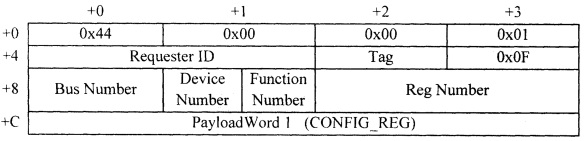

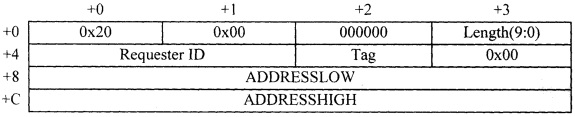

Формат пакета Configuration Туре 0 Write.

Данный пакет используют для записи конфигурационных регистров устройства на шине I-Bus.

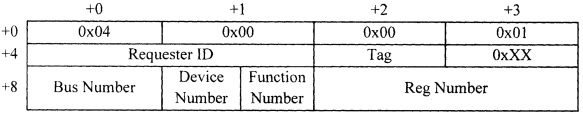

RequesterID - идентификатор устройства, инициировавшего запись.

BusNumber - номер шины.

DeviceNumber - номер устройства.

FunctionNumber – номер функции.

Формат пакета Configuration Type 0 Read.

Пакет Configuration Type 0 Read служит для чтения конфигурационных регистров устройства на шине I-Bus.

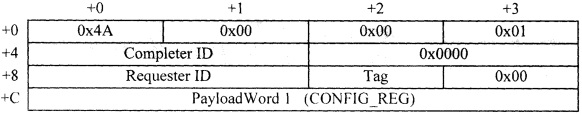

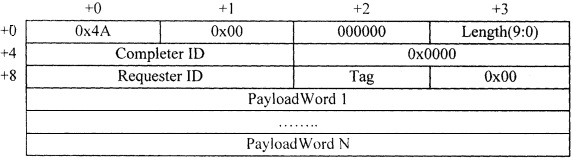

Формат пакета Completion для Configuration Read

Пакет Completion для Configuration Read является ответом на запрос чтения конфигурационного регистра соответствующего модуля I-Bus. Пакет отправляется модулем I-Bus в ответ на запрос со стороны модуля инициировавшего запрос Configuration Read. В качестве Completer ID подставляется значение Device ID, присвоенное устройству. Requester ID и Tag копируются из соответствующих полей запроса Configuration Read.

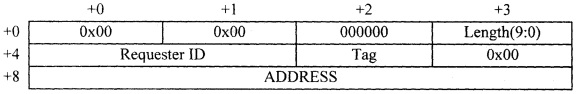

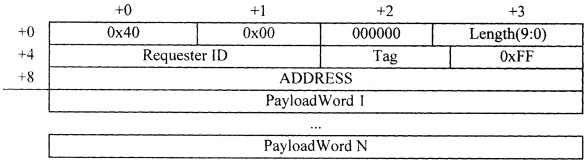

Формат пакета Memory Read 3DW.

Формат пакета Memory Read 4DW.

Пакеты типа Memory Read служат для чтения информации из устройства на шине I-Bus. Поле Address пакета содержит адрес устройства, с которого необходимо прочесть информацию. Соответственно пакеты типа Memory Read 3 DW используют 32-битную адресацию, а пакеты типа Memory Read 4 DW используют 64-битную адресацию.

Пакеты типа Memory Read не имеют Payload. Поле Length первого слова данных пакетов означает длину Payload, которую должен иметь ожидаемый пакет Completion (ответ на чтение).

Формат пакета Completion для Memory Read.

Пакет Completion является пакетом ответа на запрос чтения MemoryRead.

Для пакетов Completion и Memory Write биты 9:0 первого слова пакета означают длину поля данных (Payload) пакета.

Если указано «0000000000», это интерпретируется как «10000000000», то есть длина Payload пакета в этом случае составляет 1024 слова.

1024 слова - это максимально возможная длина Payload пакета типа Completion и Memory Write.

Формат пакета Memory Write 3DW.

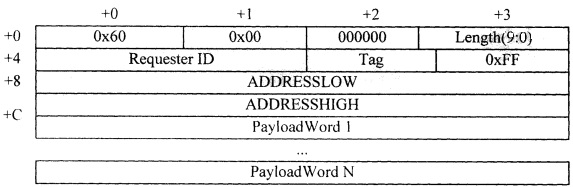

Формат пакета Memory Write 4DW.

Пакеты типа MemoryWrite служат для записи информации в устройство на шине I-Bus. Поле Address пакета содержит адрес устройства, в которое необходимо записать информацию. Соответственно пакеты типа MemoryWrite 3 DW используют 32-битную адресацию, а пакеты типа MemoryWrite 4 DW используют 64-битную адресацию.

Данные передают пакетами в структуре кадра. Структура кадра представляет собой набор пакетов или один пакет (в том случае, если количество передаваемых данных не больше максимально возможной длины пакета по данным (Payload) с учетом служебных слов). При этом первый пакет кадра должен содержать признак начала кадра, а последний пакет - признак конца кадра. Также каждый пакет в структуре кадра содержит поле цвета, которое определяет источник поступающих данных, или, в конечном счете, место назначения данных данного кадра. Таким образом, благодаря полю цвета, устройство на шине I-Bus может дифференцировать передачу или прием до 1024 различных массивов данных. Ниже показана структура кадра в пакетном базисе.

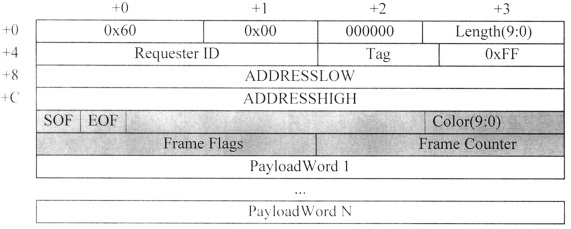

Формат пакета Memory Write 4DW. Frame structure.

Пакет «Memory Write 4DW. Framestructure» («передача данных в структуре кадра») отличается от обычного пакета «Memory Write 4DW» тем, что после заголовка идут два служебных слова. Эти 2 слова относятся не к заголовку пакета, а к его Payload, поэтому длина Payload (Length в битах 9:0 первого слова пакета) указывается, считая эти служебные слова.

Первое служебное слово содержит:

Признак начала кадра SOF - 31-й разряд - 1 - пакет является первым пакетом кадра, 0 - пакет не является первым пакетом кадра.

Признак конца кадра EOF - 30-й разряд - 1 - пакет является последним пакетом кадра, 0 - пакет не является последним пакетом кадра.

Если весь кадр передается одним пакетом, то в этом пакете оба признака - SOF и EOF - должны иметь значение '1'.

Color - 10-ти разрядный цвет данных в данном пакете данного кадра.

Второе служебное слово содержит:

Frame Flags - опциональное поле с флагами ошибок и статусными битами, зависящими от конкретной реализации системы. Поле Frame Flags позволяет контролировать приходящие кадры с данными на предмет целостности и актуальности содержащихся в принимаемых кадрах данных. Благодаря этому полю устройство может диагностировать ту или иную неисправность, возникшую при работе. Наиболее типично использование следующих флагов:

- Flag Padding - если флаг содержит 1, это означает, что данный кадр был добит нулями, т.е. в ожидаемое время прихода кадра не было принято необходимого количества слов.

- Flag Cutting - если флаг содержит 1, это означает, что данный кадр был обрезан, т.е. в ожидаемое время прихода кадра было принято больше необходимого числа слов.

- Flag Frame Missing - если флаг содержит 1, это означает, что данный кадр содержит нули, т.е. в ожидаемое время прихода кадра не было принято ни одно слово.

- Flag Frame Structure Error - если флаг содержит 1, это означает, что при приеме данного кадра не было пакета с признаком EOF, но пришел очередной пакет с признаком SOF.

Frame Counter - 15-разрядный счетчик кадров.

Инкрементируется по каждому принятому кадру с данными.

Использование полей Frame Flags и FrameCounter является опциональным и определяется конфигурационными регистрами устройства на шине I-Bus.

Для групповой рассылки используют пакеты Memory Write 4DW co значением ADDRESSLOW(31:28)="0111". При этом значения адреса ADDRESSLOW c 15 по 0 бит используют в качестве битовой маски для определения того, в какие устройства пойдет пакет групповой рассылки.

Узким местом в плане пропускной способности является решетка (lattice) I-Bus контроллера, поэтому в случае, когда соседние 32-битные слова в пакете адресованы одному процессору (например, при 64 битной разрядности поступающих данных), то второе слово можно записывать в процессор в обход решетки. То есть процессор получит вначале первое слово, прошедшее через решетку, а затем второе слово прошедшее в обход решетки.

Для режима удвоенной скорости обработки потока также используют пакеты Memory Write 4DW, а контроллер переводят в режим удвоения путем записи управляющего бита в конфигурационный регистр I-Bus-контроллера. Суть режима заключается в том, что данные "Payload WordK" и "Payload WordK+1" (где K=1, 3, 5, … N-1) являются связанными, и обработку в Lattice проходит только слово "Payload WordK", a "Payload WordK+1", минуя обработчик, записывается в тот же процессор, что и слово "Payload WordK". Таким образом, за один такт обработки слова данных теперь процессорам передается два слова данных, а не одно.

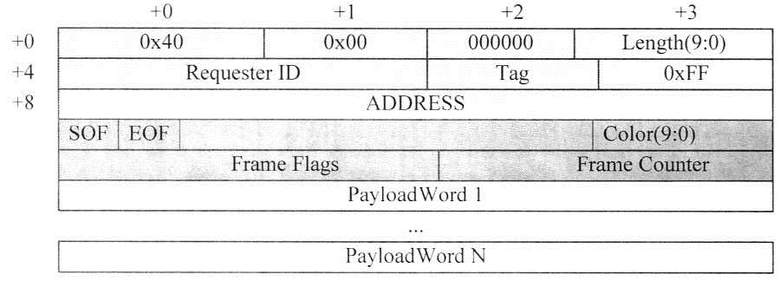

Формат пакета Memory Write 3DW. Frame structure.

Для пакетов «Memory Write 3DW. Frame structure» использование структуры кадра аналогично описанному выше для пакетов «Memory Write 4DW» с единственным отличием: второе служебное слово (с Frame Flags и Frame_Counter) присутствует только в первом пакете кадра (отмеченном признаком SOF='1'), все остальные пакеты кадра содержат только одно служебное слово (с SOF, EOF и Color).

Применение структуры кадра в передаваемых пакетах данных позволит иметь привязку данных к определенному кадру (временному отсчету), что актуально для устройств, передающих информацию в реальном времени. Модуль на шине I-Bus, выставляя биты SOF и EOF, а также сопровождая поток номером кадра, определяет, где начинаются и где заканчиваются данные данного временного интервала, были ли пропуски кадров в ходе работы.

Все конечные приемные и передающие устройства должны иметь контроль структуры кадра на предмет ошибок в структуре. Необходимо проверять следующие ситуации:

- Наличие EOF, если был SOF. Приход пакета с признаком SOF при условии, что не было пакета с признаком EOF, должен считаться ошибочной ситуацией, при которой должен быть сформирован кадр с признаками ошибки (поле Flags).

- Проверка необходимого числа данных, которые должны быть приняты в данном кадре. Если пришло меньше заданного количества слов данных, кадр должен быть дополнен, чтобы сохранить структуру обрабатываемой информации, при этом будет выставлен флаг Flag Padding в поле Flags. Если пришло больше заданного количества слов данных, кадр должен быть обрезан, при этом будет выставлен флаг Flag Cutting в поле Flags.

- Проверка поступления данных. Если в заданный интервал времени не пришло ни одного пакета с данными, должен быть сформирован «пустой» кадр с наполнением нулями заданного размера, при этом будет выставлен флаг Flag Frame Missing в поле Flags.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ПЕРЕДАЧИ ИНФОРМАЦИИ ПО КАНАЛУ Fast Channel МЕЖДУ ФИЗИЧЕСКИМИ УСТРОЙСТВАМИ | 2014 |

|

RU2574842C2 |

| СПОСОБ ПЕРЕДАЧИ ИНФОРМАЦИИ В РЕАЛЬНОМ ВРЕМЕНИ С ИСПОЛЬЗОВАНИЕМ ЛОКАЛЬНЫХ СЕТЕЙ ОГРАНИЧЕННОГО РАЗМЕРА НА БАЗЕ МОДИФИКАЦИИ ПРОТОКОЛА FC-AE-ASM | 2013 |

|

RU2536659C1 |

| ЦИФРОВАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 2013 |

|

RU2547216C1 |

| КЛАСТЕРНАЯ СИСТЕМА С ПРЯМОЙ КОММУТАЦИЕЙ КАНАЛОВ | 2011 |

|

RU2461055C1 |

| Способ организации прямого доступа в память при передаче информации между физическими объектами | 2016 |

|

RU2638781C2 |

| СИСТЕМА УПРАВЛЕНИЯ СВЯЗЬЮ, КОММУТАЦИОННЫЙ УЗЕЛ И СПОСОБ УПРАВЛЕНИЯ СВЯЗЬЮ | 2012 |

|

RU2584449C2 |

| КОМПЬЮТЕРНАЯ СИСТЕМА | 2014 |

|

RU2579949C2 |

| СЪЕМНЫЙ НОСИТЕЛЬ ИНФОРМАЦИИ С ПОВЫШЕННОЙ СКОРОСТЬЮ ДОСТУПА | 2011 |

|

RU2473142C1 |

| Способ передачи информации в реальном времени с повышенной помехозащищенностью по локальной сети aRTnet | 2017 |

|

RU2667387C1 |

| УПРАВЛЯЮЩИЙ МОДУЛЬ | 2014 |

|

RU2569576C1 |

Изобретение относится к области вычислительной техники и предназначено для построения систем цифровой обработки сигналов в реальном масштабе времени. Технический результат заключается в обеспечении использования формата пакетов стандарта PCI-Express для передачи как по последовательным, так и по параллельным шинам. Способ передачи информации характеризуется тем, что информацию в формате PCI-Express пакетов передают как по последовательным высокоскоростным каналам связи, так и по параллельной шине и, в зависимости от адреса в пакете, осуществляют перенаправление данных либо внутрь контроллера I-Bus, либо на внешнюю шину PCI-Express и далее через коммутатор РCI-Express и на другие контроллеры I-Bus. При этом коммутатор PCI-Express выполнен с возможностью передавать пакет одновременно нескольким контроллерам I-Bus, а контроллер I-Bus выполнен с возможностью работы в режиме удвоенной скорости обработки потока. Предварительно проводят определение количества необходимых оконечных станций и коммутаторов с определением необходимой топологии каналов связи между ними, настраивают используемые коммутаторы и оконечные устройства для приема/передачи информации, передаваемую информацию разбивают на пакеты для передачи по стандарту PCI-Express размером полезных данных не свыше 4 килобайт. 2 ил.

Способ передачи информации, характеризуемый тем, что информацию в формате PCI-Express пакетов передают как по последовательным высокоскоростным каналам связи, так и по параллельной шине и, в зависимости от адреса в пакете, осуществляют перенаправление данных либо внутрь контроллера I-Bus, либо на внешнюю шину PCI-Express и далее через коммутатор PCI-Express и на другие контроллеры I-Bus, при этом коммутатор PCI-Express выполнен с возможностью передавать пакет одновременно нескольким контроллерам I-Bus, контроллер I-Bus выполнен с возможностью работы в режиме удвоенной скорости обработки потока, причем предварительно проводят определение количества необходимых оконечных станций и коммутаторов с определением необходимой топологии каналов связи между ними, с использованием пропускания через используемые каналы связи конфигурационных пакетов, настраивают используемые коммутаторы и оконечные устройства для приема/передачи информации, передаваемую информацию разбивают на пакеты для передачи по стандарту PCI-Express размером полезных данных не свыше 4 килобайт, при этом каждый пакет состоит из заголовка и поля данных, предназначенного в том числе и для записи передаваемой информации, при этом заголовок содержит информацию о типе пакета, адрес отправителя пакета и адрес приемника, в качестве формата обмена данными используют уровни PCI-Express, а именно: Physical Layer, Data Link Layer, Transaction Layer.

| RU 2014125183 A, 23.06.2014 | |||

| ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНЫЙ КОМПЛЕКС ДЛЯ ОБРАБОТКИ СИГНАЛОВ В ГИДРОАКУСТИЧЕСКИХ СИСТЕМАХ | 2001 |

|

RU2207620C2 |

| US 5367701 A, 22.11.1994 | |||

| US 2012017026 A1, 19.01.2012. | |||

Авторы

Даты

2018-01-24—Публикация

2016-09-05—Подача