Настоящее изобретение в целом касается электрического питания нагрузки, такой как лампа, через двухпроводной электрический регулятор.

В частности, объектом изобретения является электрический регулятор, содержащий:

- две единых соединительных клеммы, в том числе входную клемму, соединяемую с местной электрической сетью, и выходную клемму, соединяемую с электрической нагрузкой,

- силовой блок, подключенный между указанными соединительными клеммами, для периодического ограничения части электрического напряжения, подаваемого на указанную выходную клемму,

- блок управления, выполненный с возможностью управления указанным силовым блоком с целью изменения продолжительности ограничения электрического напряжения, подаваемого на указанную выходную клемму, и

- блок синхронизации блока управления.

Электрический регулятор является прибором, как правило, устанавливаемым на стене жилого помещения для использования потребителями с целью изменения силы света одной или нескольких ламп.

Электрическая сеть выдает периодическое переменное напряжение, которое характеризуется «полупериодом». Электрический регулятор выполнен таким образом, чтобы передавать на лампу только часть каждого полупериода переменного напряжения, выдаваемого электрической сетью. В этом случая говорят, что он «ограничивает» переменное напряжение.

Понятно, что это ограничение должно быть точно синхронизировано по переменному напряжению, выдаваемому электрической сетью, чтобы сила тока, передаваемого на нагрузку, оставалась постоянной от одного полупериода к другому.

В настоящее время известны два типа электрических регуляторов: так называемые «двухпроводные» регуляторы и так называемые «трехпроводные» регуляторы.

Трехпроводные регуляторы содержат входную клемму, соединенную с местной электрической сетью, выходную клемму, соединенную с нагрузкой, и клемму, соединенную с нейтралью. При этом использование нейтрали обеспечивает хорошую синхронизацию ограничения по переменному напряжению, выдаваемому электрической сетью, так как на электрический регулятор не влияют колебания напряжения, наводимые нагрузкой.

Двухпроводные регуляторы содержат только входную клемму, соединенную с местной электрической сетью, и выходную клемму, соединенную с нагрузкой. Таким образом, они соединены с нагрузкой последовательно, что упрощает их монтаж, в частности, в случае замены старого выключателя на электрический регулятор. С другой стороны, их синхронизация является более сложной, поскольку они не соединены с нейтралью.

Из документа FR 2802360 известен двухпроводной электрический регулятор, охарактеризованный во вступительной части, в котором блок синхронизации позволяет синхронизировать блок управления по переменному напряжению, выдаваемому электрической сетью, передавая на этот блок управления сигнал синхронизации каждый раз, когда переменное напряжение проходит через 0.

Можно отметить отличную работу этого электрического регулятора, когда нагрузка характеризуется поведением резистивного типа (лампа накаливания,…), но, с другой стороны, наблюдается мигание нагрузки, когда она характеризуется поведением нерезистивного типа (люминесцентная лампа, энергосберегающая лампа,…). Отмечается также, что проблема мигания проявляется тем сильнее, чем больше число нерезистивных ламп в нагрузке.

Заявитель заметил, что эта проблема мигания возникает по причине электронных схем, установленных в нерезистивных лампах. Действительно, эти электронные схемы создают эффект затягивания (то есть остаточное напряжение на контактах каждой лампы), что приводит к деформации электрического напряжения, от которого отталкивается блок синхронизации, чтобы синхронизировать блок управления.

Поскольку синхронизация блока управления основана на непериодическом сигнале, ее осуществляют произвольно. Таким образом, понятно, что управление силовым блоком регулятора происходит нестабильно, что приводит к случайному ограничению переменного напряжения и, следовательно, к колебаниям тока, передаваемого на нагрузку, которые и являются причиной мигания.

Чтобы устранить вышеупомянутый недостаток известных решений, изобретением предлагается электрический регулятор, блок синхронизации в котором не подвержен влиянию эффекта затягивания.

В частности, изобретением предлагается электрический регулятор, охарактеризованный во вступительной части, в котором указанный блок синхронизации содержит:

- нестабилизированный каскад, который выполнен с возможностью выдачи нестабилизированного сигнала синхронизации, синхронизируемого по электрическому напряжению, поступающему на указанную входную клемму,

- стабилизированный каскад, содержащий буферный фильтр, за которым следует стабилизирующий фильтр, и выполненный с возможностью выдачи периодического стабилизированного сигнала синхронизации, который синхронизируют по электрическому напряжению, поступающему на указанную входную клемму, и который затем фильтруют при помощи указанных буферного фильтра и стабилизирующего фильтра, и

- избирательный каскад для выбора одного или другого из указанных стабилизированного и нестабилизированного сигналов синхронизации.

Стабилизирующий фильтр выполнен с возможностью преобразования «электрического напряжения, подаваемого на входную клемму» (которое отличается от напряжения на клеммах местной электрической сети) таким образом, чтобы оно стало периодическим, на частоте, равной частоте напряжения на клеммах местной электрической сети. Буферный фильтр позволяет избегать деформации стабилизирующим фильтром «электрического напряжения, подаваемого на входную клемму».

Таким образом, стабилизированный каскад позволяет выдавать стабилизированный и периодический сигнал, который позволяет блоку управления управлять силовым блоком таким образом, чтобы нагрузка не мигала.

Что касается нестабилизированного каскада, то он позволяет синхронизировать блок управления в конкретные моменты (в частности, когда пользователь изменяет силу света нагрузки при помощи кнопки управления) аналогично тому, как это происходит в известных решениях.

Таким образом, благодаря стабилизированному каскаду, синхронизация блока управления работает независимо от типа нагрузки, подключенной к электрическому регулятору, и независимо от того, создает она или не создает эффекты затягивания.

Кроме того, следует отметить, что стабилизированный каскад генерирует стабилизированный сигнал синхронизации на основе напряжения, поступающего на входную клемму, поэтому синхронизация работает при любом местном напряжении (110, или 220, или 230 В) и при любой местной частоте (50 или 60 Гц).

Другими предпочтительными и неограничительными признаками электрического регулятора в соответствии с изобретением являются:

- указанный буферный фильтр имеет большое входное сопротивление, по меньшей мере, превышающее 106 Ом;

- указанный буферный фильтр содержит операционный усилитель, работающий по схеме следящего устройства;

- указанный буферный фильтр содержит операционный усилитель, работающий по схеме фильтра нижних частот;

- указанная схема фильтра нижних частот является фильтром второго порядка;

- на входе указанного буферного фильтра указанный стабилизированный каскад содержит пассивный фильтр нижних частот первого порядка;

- указанный стабилизирующий фильтр выдает первый периодический сигнал, и указанный стабилизированный каскад содержит, с одной стороны, генератор сигнала, который выдает второй сигнал, и, с другой стороны, компаратор, который генерирует указанный стабилизированный сигнал синхронизации в зависимости от указанного первого сигнала и от указанного второго сигнала;

- указанный блок управления содержит микроконтроллер, при этом указанный компаратор интегрирован в указанный микроконтроллер;

- указанный генератор сигнала содержит пассивный фильтр нижних частот первого порядка, вход которого принимает первый сигнал и выход которого генерирует второй сигнал;

- указанный нестабилизированный каскад содержит, по меньшей мере, один транзистор;

- указанный транзистор имеет коэффициент усиления, превышающий 100;

- предусмотрен командный блок, который приводится в действие пользователем и который выполнен с возможностью передачи командного сигнала на указанный блок управления;

- указанный блок управления управляет указанным избирательным каскадом для выбора нестабилизированного сигнала синхронизации, когда приводят в действие указанный командный блок;

- указанный блок управления управляет указанным избирательным каскадом для выбора нестабилизированного сигнала синхронизации в течение заранее определенного времени, после того как перестают действовать на указанный командный блок, затем для выбора стабилизированного сигнала синхронизации, пока указанный командный блок опять не приводят в действие;

- указанный блок управления содержит средства измерения запаздывания стабилизированного сигнала синхронизации по отношению к нестабилизированному сигналу синхронизации;

- указанный блок управления содержит микроконтроллер, при этом указанный избирательный каскад интегрирован в указанный микроконтроллер;

- предусмотрен каскад ослабления, установленный между, с одной стороны, указанной входной клеммой и, с другой стороны, каждым из нестабилизированного и стабилизированного каскадов;

- указанный каскад ослабления содержит пассивный фильтр нижних частот первого порядка.

Изобретение и его реализация будут более очевидны из нижеследующего описания не ограничительного примера выполнения со ссылками на прилагаемые чертежи, на которых:

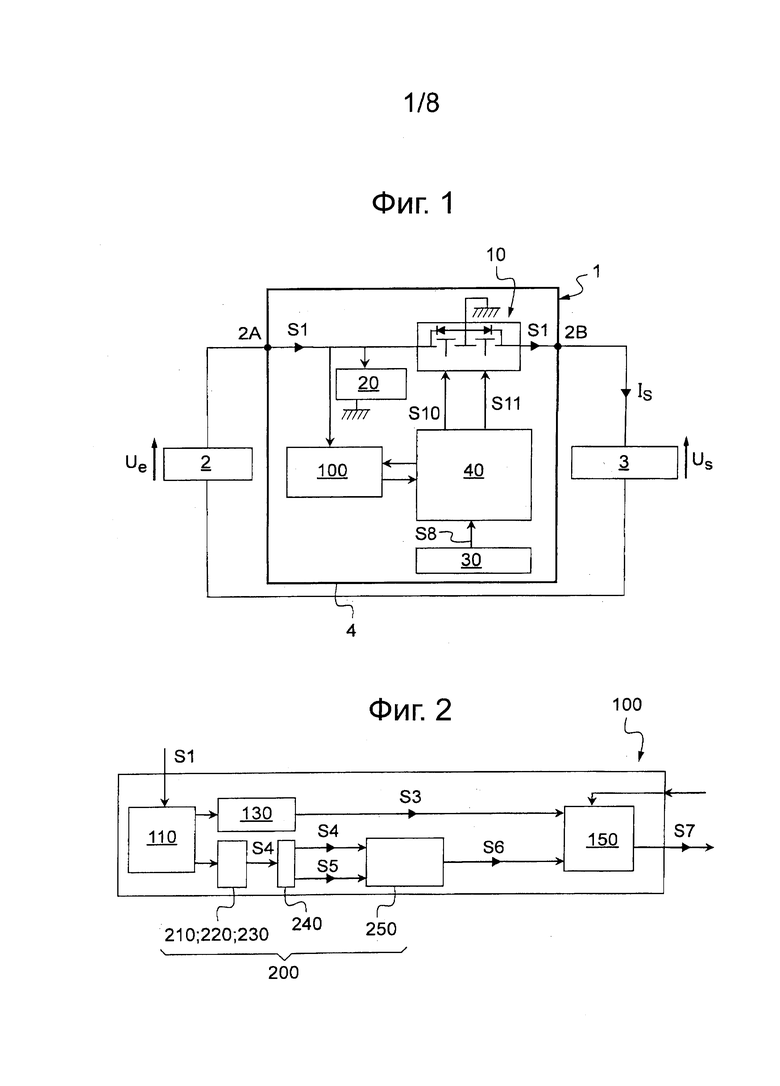

фиг.1 - электрическая схема электрического регулятора в соответствии с изобретением;

фиг.2 - схематичный вид блока синхронизации электрического регулятора, показанного на фиг.1;

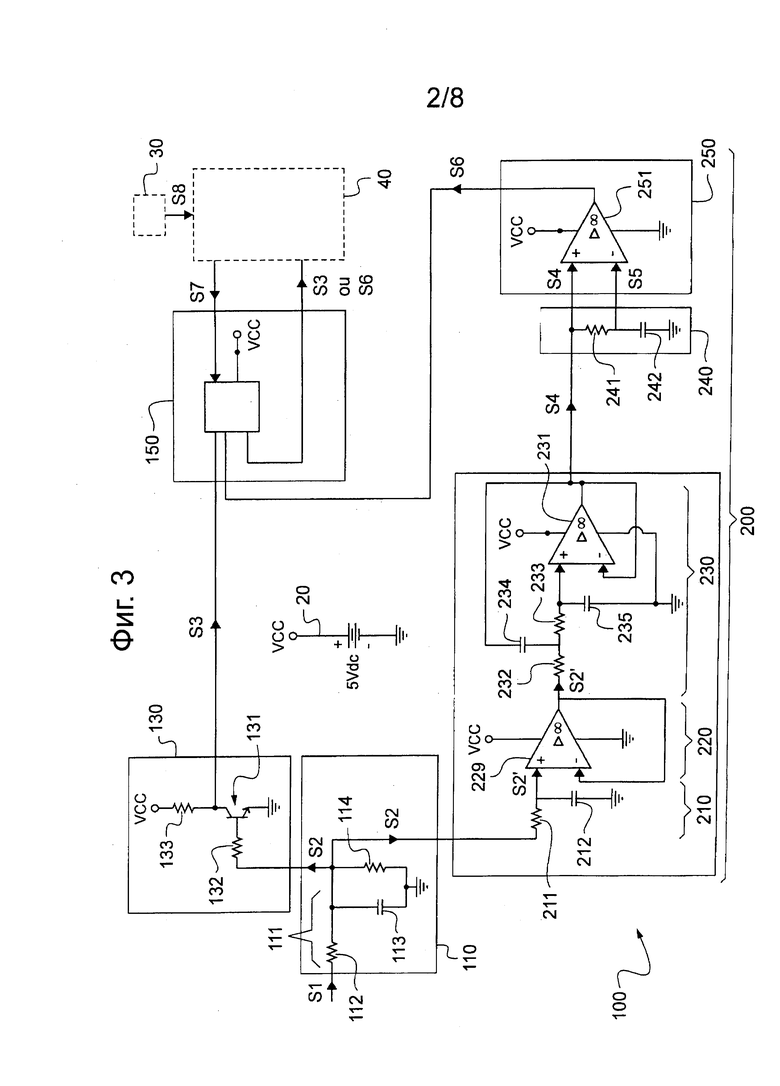

фиг.3 - электрическая схема блока синхронизации, показанного на фиг.2;

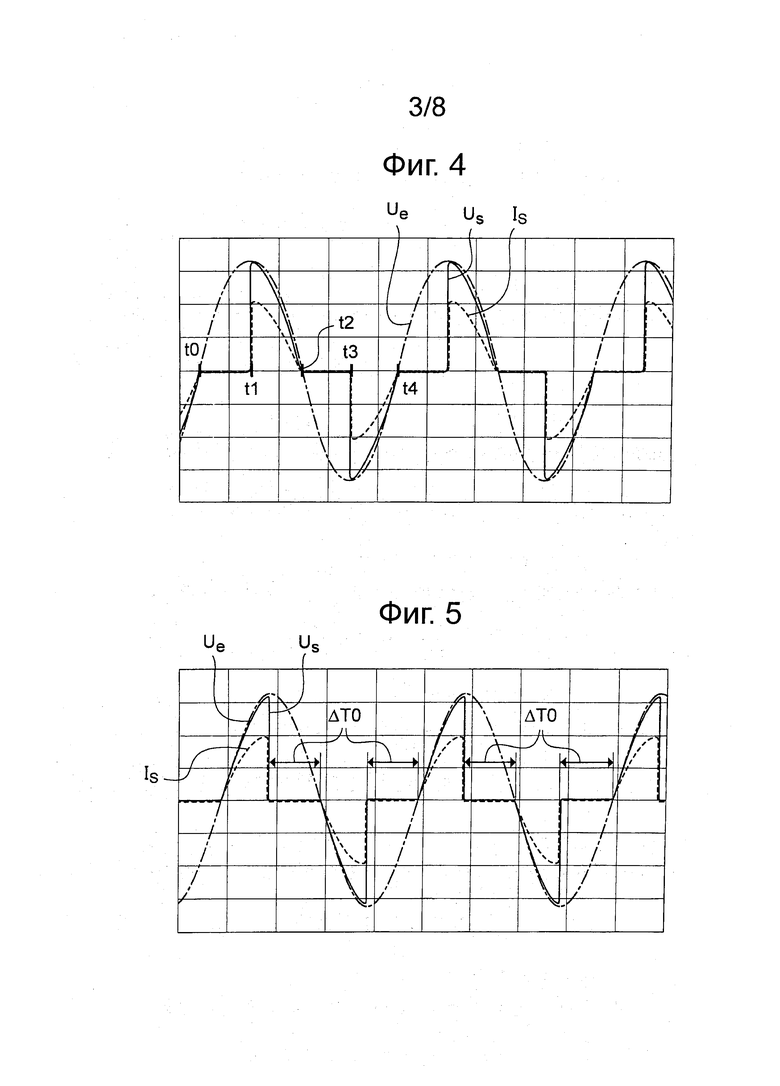

фиг.4 - график, иллюстрирующий изменения входного и выходного напряжений и выходного тока в зависимости от времени для лампы накаливания, управляемой в индуктивном режиме;

фиг.5 - график, иллюстрирующий изменения входного и выходного напряжений и выходного тока в зависимости от времени для лампы накаливания, управляемой в емкостном режиме;

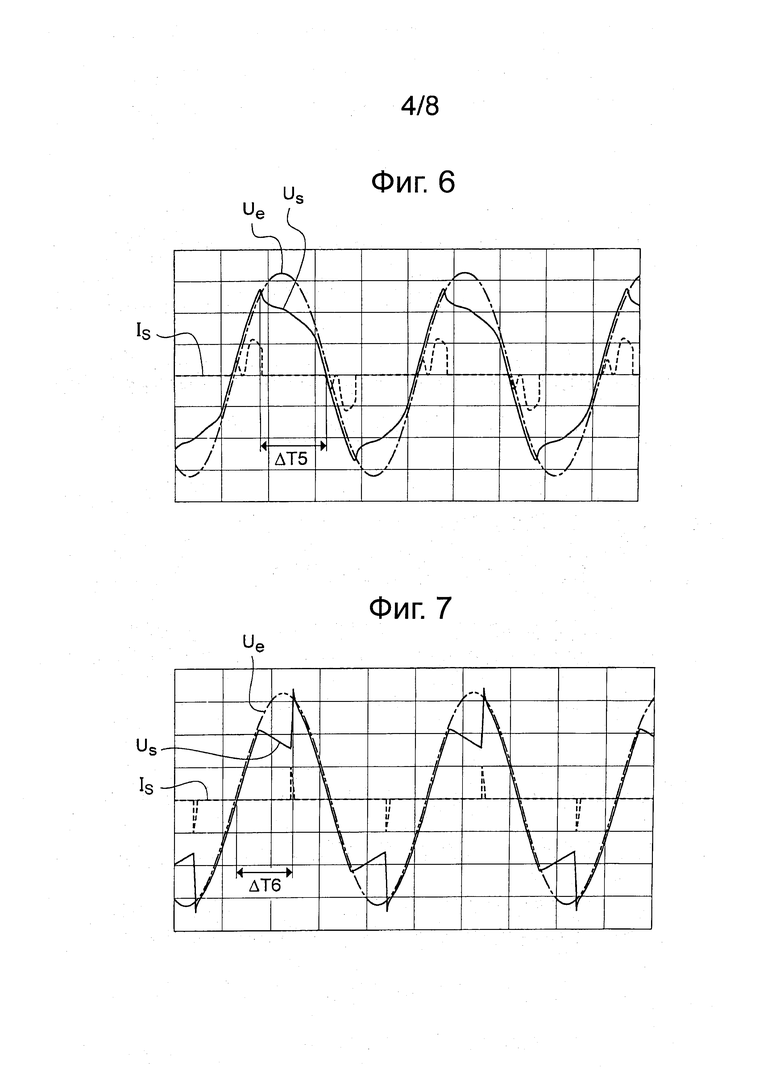

фиг.6 - график, иллюстрирующий изменения входного и выходного напряжений и выходного тока в зависимости от времени для энергосберегающей лампы, управляемой в емкостном режиме;

фиг.7 - график, иллюстрирующий изменения входного и выходного напряжений и выходного тока в зависимости от времени для люминесцентной лампы, управляемой в индуктивном режиме;

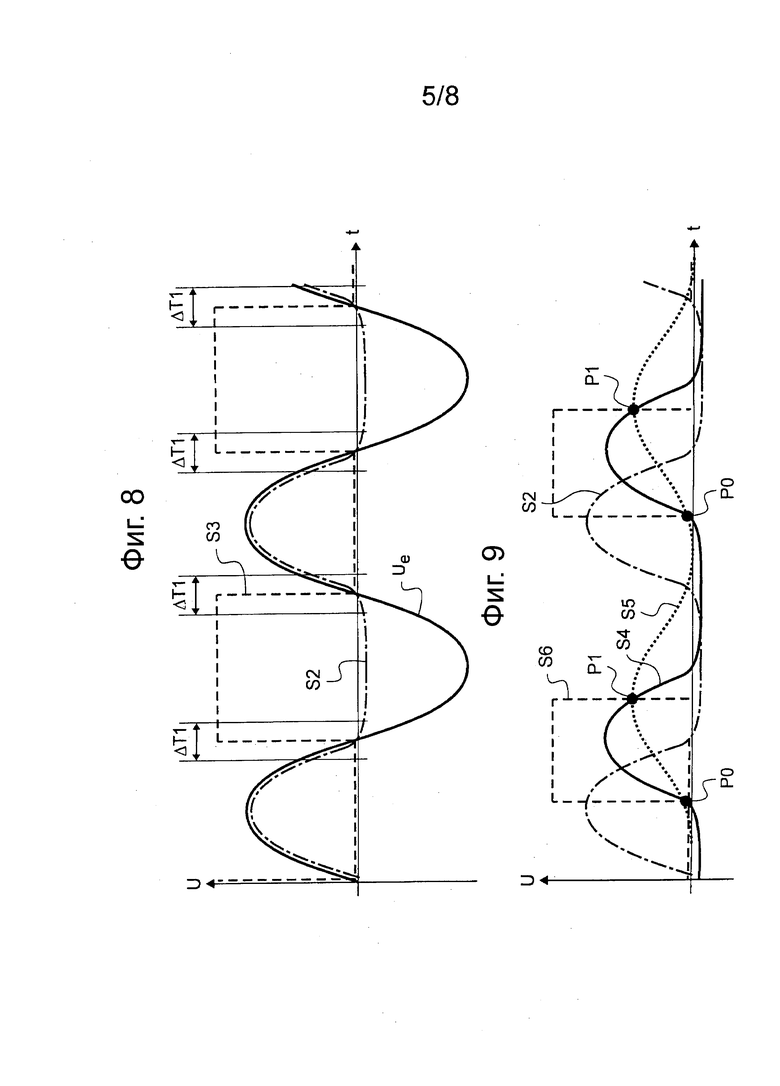

фиг.8 - график, иллюстрирующий изменения входного напряжения, ослабленного сигнала и нестабилизированного сигнала синхронизации в зависимости от времени (напряжения и сигналы показаны не в масштабе);

фиг.9 - график, иллюстрирующий изменения ослабленного сигнала, фильтрованного сигнала и восстановленного сигнала в зависимости от времени;

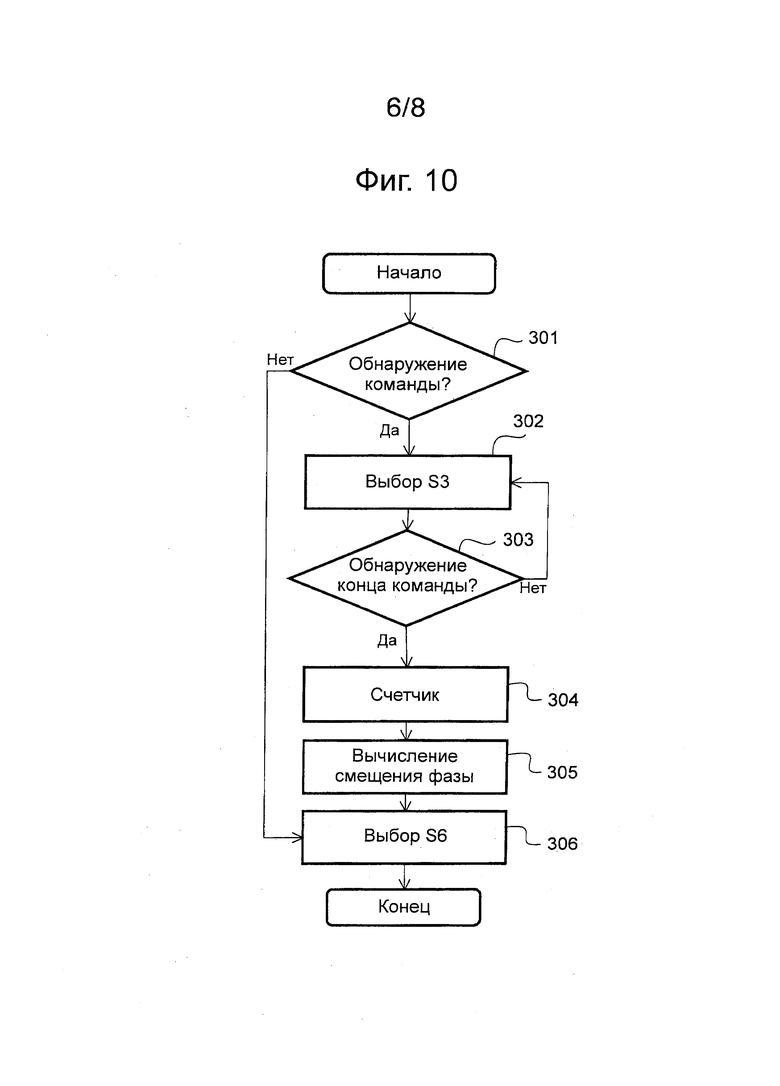

фиг.10 - алгоритм работы блока управления электрического регулятора, показанного на фиг.1, в индуктивном режиме;

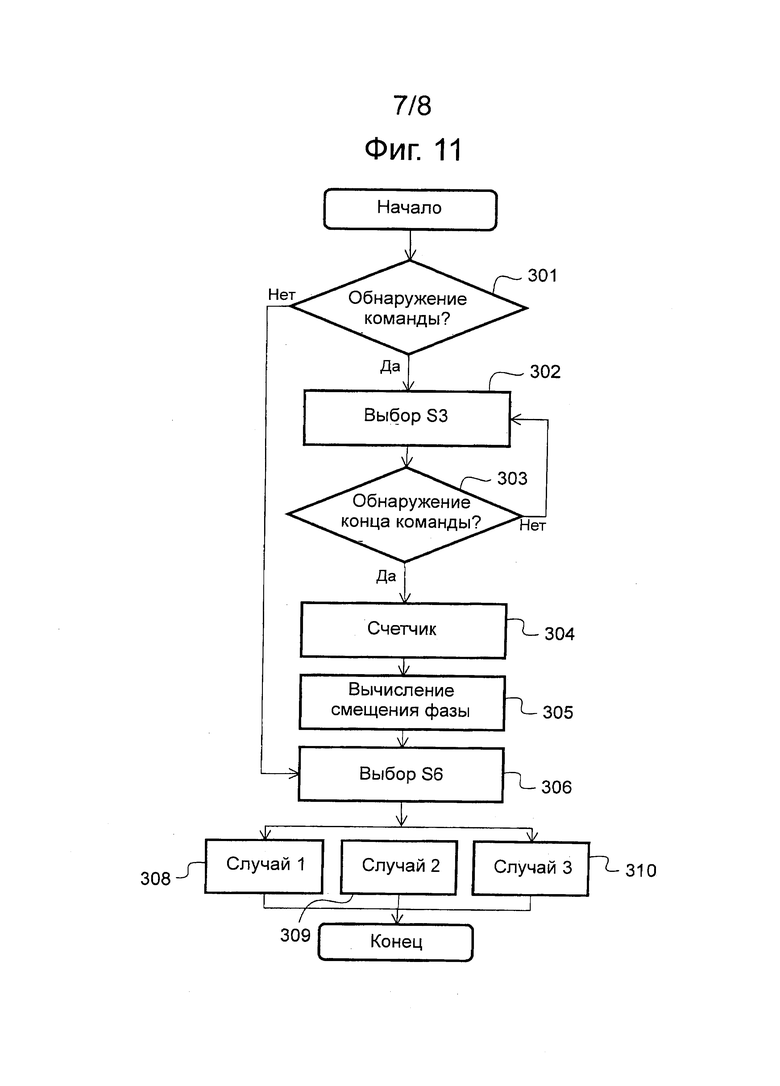

фиг.11 - алгоритм работы блока управления электрического регулятора, показанного на фиг.1, в емкостном режиме;

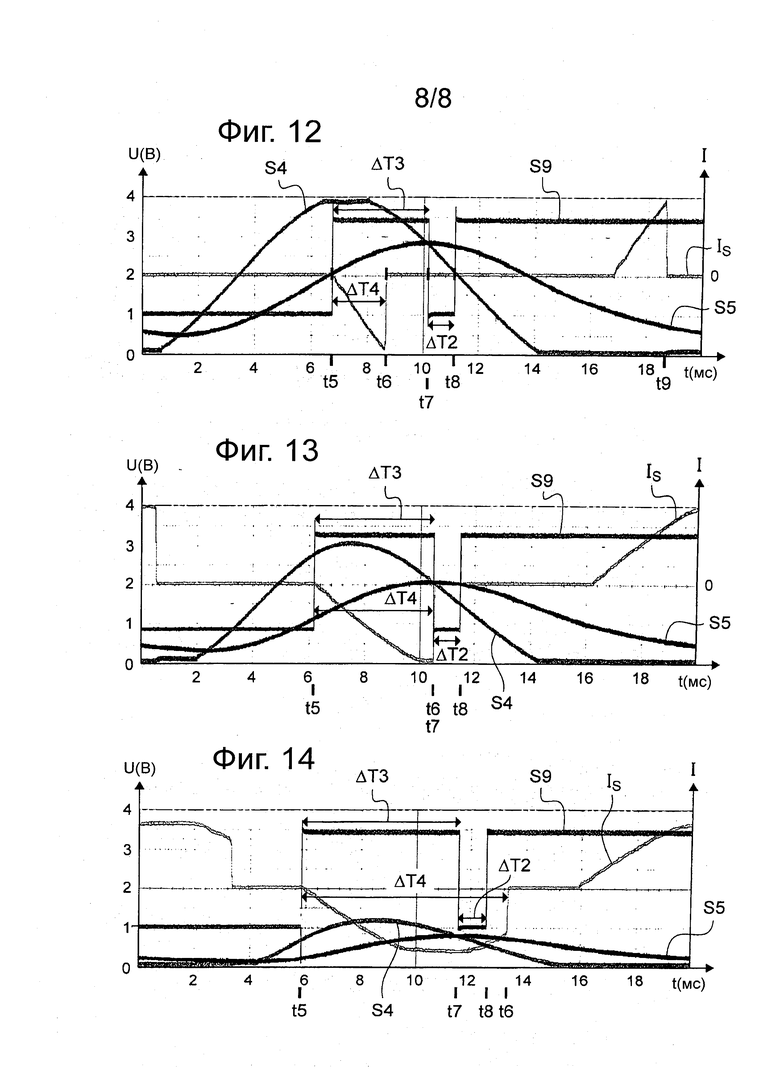

фиг.11-14 - графики, иллюстрирующие изменения фильтрованного сигнала, восстановленного сигнала и стабилизированного сигнала синхронизации в зависимости от времени в емкостном режиме.

На фиг.1 показана нагрузка 3, подключенная к сети 2 электрического питания через электрический регулятор 1.

Сеть 2 электрического питания выдает на его клеммы переменное напряжение, называемое входным напряжением Ue.

Это входное напряжение Ue является периодическим. Каждый из его периодов состоит из положительного полупериода и отрицательного полупериода.

Частота и амплитуда этого входного напряжения Ue различаются от одной страны к другой. Так, его частота может быть равна 50 или 60 Гц. Само напряжение может быть равно 110, 220, 230 или 240 В.

Нагрузка 3 может включать в себя одну или несколько ламп, соединенных последовательно или параллельно.

В данном случае различают три типа нагрузок 3: нагрузки резистивного поведения (такие как лампы накаливания), нагрузки индуктивного поведения и нагрузки емкостного поведения (такие как лампы на LED, то есть на «электролюминесцентных диодах», и энергосберегающие лампы, то есть «компактные флуоресцентные лампы»). Эти различия в поведении объясняются, в частности, различиями между установленными в них электронными схемами.

Напряжение на клеммах нагрузки 3 называют выходным напряжением Us. Ток, проходящий в этой нагрузке 3, называют выходным током Is.

В данном случае электрический регулятор 1 предпочтительно предусмотрен для подключения к проводу фазы, который соединяет сеть 2 электрического питания с нагрузкой 3. Таким образом, его называют «двухпроводным регулятором», так как он содержит только две клеммы электрического соединения, в том числе входную клемму 2А, соединенную с сетью 2 электрического питания, и выходную клемму 2В, соединенную с нагрузкой 3.

Этот электрический регулятор 1 содержит электронную плату 4, закрытую облицовочной крышкой (не показана), из которой выступает командный орган (не показан), приводимый в действие потребителем.

Этот командный орган может быть выполнен в разных видах, в частности в виде поворотного колесика или в виде двух кнопок, на которых соответственно показаны две стрелки, одна из которых направлена вверх, а другая - вниз. Потребитель использует его, когда ему необходимо уменьшить или увеличить силу света, развиваемую нагрузкой 3.

Как показано на фиг.1, электронная плата 4 содержит четыре основных блока, в том числе:

- силовой блок 10, вход которого напрямую соединен с входной клеммой 2А регулятора и выход которого напрямую соединен с выходной клеммой 2В регулятора,

- блок 40 управления, выполненный с возможностью управления силовым боком 10,

- командный блок 30, который позволяет обнаруживать любое движение командного органа, задаваемое потребителем, и который выполнен с возможностью передачи в блок управления 40 командного сигнала S8, связанного с этим движением,

- блок 100 синхронизации блока 40 управления, и

- блок 20 питания, который, с одной стороны, образует массу и, с другой стороны, отбирает часть тока, проходящего между входной 2А и выходной 2В клеммами электрического регулятора 1, с целью питания различных компонентов электронной платы 4 электрического регулятора 1 при напряжении питания Vcc.

Силовой блок 10 предназначен для уменьшения количества тока, передаваемого на нагрузку 3, чтобы она развивала силу света, задаваемую потребителем.

Этот силовой блок 10, который собственно не является объектом настоящего изобретения, содержит для этого транзисторную схему, которая может ограничивать входное напряжение Ue, поступающее от сети 2 электрического питания.

Как показано, например, на фиг.5, каждый положительный и отрицательный полупериод выходного напряжения Us оказывается частично усеченным в течение времени ограничения ΔТ0, поэтому средний ток, поступающий на нагрузку 3, уменьшается.

В данном случае этот силовой блок 10 содержит два управляемых выключателя с двумя устойчивыми состояниями, таких как транзисторы БТИЗ.

Этот принцип сам по себе известен, и его описание опускается.

Блок 40 управления выполнен, в частности, с возможностью управления переключением этих транзисторов БТИЗ.

В установившемся режиме, то есть, когда на командный орган не действуют, блок 40 управления позволяет равномерно открывать и закрывать транзисторы БТИЗ с частотой, равной частоте входного напряжения Ue и синхронно с этим напряжением, чтобы сила выходного тока Is, проходящего через нагрузку 3, оставалась одинаковой от одного полупериода к другому.

В переходном периоде, то есть, когда пользователь решает изменить силу света, излучаемого нагрузкой 3, блок 40 управления позволяет менять продолжительность ограничения ΔТ0 для регулирования силы выходного тока Is, проходящего через нагрузку 3.

В данном случае этот блок 40 управления выполнен в виде микроконтроллера, передающего сигналы управления S10, S11 в транзисторы БТИЗ для их переключения.

Он выполнен с возможностью управления обоими транзисторами БТИЗ в двух разных режимах в зависимости от того, является ли поведение нагрузки 3 индуктивным или емкостным. Если нагрузка 3 характеризуется резистивным поведением, ею можно управлять в том или ином из этих двух режимов.

Для этого, как известно (см., например, документ FR 2802360), блок 40 управления содержит память, в которой записывают информацию о типе нагрузки 3, которую стирают каждый раз, когда нагрузку 3 отключают от электрического регулятора 1, и которую опять записывают каждый раз, когда нагрузку 3 подключают к электрическому регулятору 1 (при этом специальные датчики позволяют определять тип нагрузки 3).

Как показано на фиг.4, если нагрузка является лампой накаливания и выбранный режим управления является индуктивным, выходное напряжение Us ограничивают в начале каждого полупериода. В этом случае говорят об управлении «по закрытию фазы».

Как показано на фиг.5, если нагрузка является лампой накаливания и выбранный режим управления является емкостным, выходное напряжение Us ограничивают в конце каждого полупериода. В этом случае говорят об управлении «по открытию фазы».

Как показано на фиг.6, где нагрузка 3 является люминесцентной лампой, управляемой в емкостном режиме, отмечается, что выходное напряжение Us деформируется в течение продолжительности ΔТ5 остаточным напряжением, связанным с электроникой, установленной в нагрузке (при этом говорят об эффекте затягивания).

Этот же эффект затягивания показан на фиг.7, где нагрузка 3 является энергосберегающей лампой, управляемой в индуктивном режиме, так как выходное напряжение Us деформируется здесь в течение продолжительности АТ6.

Электрический сигнал, который проходит между двумя клеммами, входной 2А и выходной 2В, и который в дальнейшем будет называться «входным сигналом S1», искажается этим эффектом затягивания, поэтому он сам по себе больше не является достаточно надежной базой для синхронизации ограничения выходного напряжения Us по отношению к входному напряжению Ue.

Блок 100 синхронизации выполнен в этом случае с возможностью устранения искажений, порождаемых этим эффектом затягивания.

Согласно предпочтительному отличительному признаку изобретения, как показано на фиг.2, этот блок 100 синхронизации для этого содержит:

- нестабилизированный каскад 130, выполненный с возможностью выдачи нестабилизированного сигнала S3 синхронизации, синхронизированного по частоте с входным сигналом S1,

- стабилизированный каскад 200, который содержит буферный фильтр 220, за которым следует стабилизирующий фильтр 230, для фильтрации поступающего в него сигнала, и который выполнен с возможностью выдачи периодического стабилизированного сигнала S6 синхронизации, синхронизированного с фильтрованным сигналом, и

- избирательный каскад 150 для выбора одного или другого из указанных стабилизированного S6 и нестабилизированного S3 сигналов синхронизации.

Предпочтительно этот блок 100 синхронизации содержит также каскад 110 ослабления, установленный, с одной стороны, между входной клеммой 2А и, с другой стороны, каждым из нестабилизированного 130 и стабилизированного 200 каскадов.

Как показано на фиг.3, этот каскад 110 ослабления образует вход блока 100 синхронизации и для этого соединен с электрическим проводом, который соединяет входную клемму 2А с силовым блоком 10 электрического регулятора 1.

Этот каскад 110 ослабления содержит пассивный фильтр нижних частот 111 первого порядка, содержащий входной резистор 112, через который поступает входной сигнал S1, и соединенный с массой конденсатор 113. Этот каскад 110 ослабления содержит также резистор 114, параллельно подключенный к конденсатору 113.

В данном случае резистор 112 имеет сопротивление 440 Ом.

Конденсатор 113 имеет емкость 220 пФ.

Резистор 114 имеет сопротивление 47 кОм.

Этот каскад 110 ослабления выдает на выходе ослабленный сигнал S2, который синхронизируют по входному напряжению Ue и который является монопериодическим в том смысле, что имеет только положительные полупериоды, синхронизированные по положительным полупериодам входного напряжения Ue (см. фиг.8, где входное напряжение Ue показано в масштабе, отличном от ослабленного сигнала).

Благодаря этому каскаду 110 ослабления ослабленный сигнал S2 имеет напряжение, меньшее напряжения питания Vcc, которое в данном случае равно примерно 2,5 В, если входное напряжение Ue равно 230 В.

Таким образом, этот каскад 110 ослабления позволяет избегать насыщения буферного фильтра 220 при любом входном напряжении Ue (110, 220, 230 или 240 В). Он позволяет также устранять искажения входного напряжения Ue и ограничивать электрическое потребление блока 100 синхронизации.

Как показано на фиг.3, нестабилизированный каскад 130 принимает на входе этот ослабленный сигнал S2.

В данном случае он содержит биполярный транзистор 131, управляемым в пропускающем или открытом состоянии ослабленным сигналом S2.

Таким образом, этот биполярный транзистор 131 имеет базу, соединенную с выходом каскада 110 ослабления через резистор 132, коллектор, соединенный с электрическим питанием Vcc через резистор 133, и эмиттер, соединенный с массой.

Этот биполярный транзистор 131 имеет повышенный коэффициент усиления, по меньшей мере, превышающий 100 и предпочтительно превышающий 400, для быстрого переключения на высокой частоте, превышающей 120 Гц.

Резистор 132 имеет сопротивление 5,6 кОм.

Резистор 133 имеет сопротивление 100 кОм.

Таким образом, этот нестабилизированный каскад 130 позволяет генерировать нестабилизированный сигнал S3 в виде строб-импульсов (см. фиг.8) при любом входном напряжении (110, 220, 230 или 240 В) и при любой частоте (50 или 60 Гц) сети 2 электрического питания.

Этот нестабилизированный сигнал S3 является периодическим, если нагрузка 3 является резистивной (в этом случае нагрузка не создает эффекта затягивания). Его спады при этом формируются с постоянной частотой, правильно отрегулированной по отношению к входному напряжению Ue.

С другой стороны, этот нестабилизированный сигнал S3 не является периодическим, если нагрузка 3 является нагрузкой емкостного иди индуктивного типа. Как показано на фиг.8, фронты и спады нестабилизированного сигнала S3 могут при этом смещаться по причине эффектов затягивания на интервал времени ATI примерно в 1 мс.

Как показано на фиг.3, стабилизированный каскад 200 тоже принимает на входе ослабленный сигнал S2.

Этот стабилизированный каскад 200 выполнен с возможностью обработки этого ослабленного сигнала S2 таким образом, чтобы генерировать стабилизированный сигнал S6 синхронизации, который является периодическим при любом типе нагрузки 3.

Для этого дополнительно к буферному фильтру 200 и к стабилизирующему фильтру 230, он содержит генератор 240 сигнала и компаратор 250.

Входной фильтр 210 является пассивным фильтром нижних частот первого порядка, который принимает ослабленный сигнал S2 и который передает интегрированный сигнал S2’.

Он содержит резистор 211, через который поступает ослабленный сигнал S2, и конденсатор 212, соединенный с массой.

В данном случае резистор 211 имеет сопротивление 100 кОм.

Конденсатор 113 имеет емкость 1 нанофарад.

При этом входной фильтр 210 имеет частоту отсечки 1,6 кГц, которая позволяет ему удалять из ослабленного сигнала практически все помехи с частотами, превышающими эту частоту отсечки.

Буферный фильтр 220 находится между этим входным фильтром 210 и стабилизирующим фильтром 230, поэтому стабилизирующий фильтр 230 не возмущает ослабленный сигнал S2 и не забивает нестабилизированный сигнал синхронизации S3.

Для этого буферный фильтр 220 выбирают таким образом, чтобы он имел большое входное сопротивление, по меньшей мере, превышающее 1 МОм.

Он содержит операционный усилитель 221, работающий по схеме следящего устройства, который принимает на своем положительном входе интегрированный сигнал S2’ и отрицательный вход которого соединен с его выходом. Эта монтажная схема имеет коэффициент усиления, по существу равный 1, поэтому сигнал на выходе этого операционного усилителя 221 является по существу таким же, как и интегрированный сигнал S2’.

Как показано на фиг.3, стабилизирующий фильтр 230 находится на выходе этого буферного фильтра 220 и предназначен для преобразования интегрированного сигнала S2’ в периодический сигнал с частотой, равной частоте входного напряжения Ue при любом типе нагрузки 3.

Для этого он содержит операционный усилитель 231, работающий по схеме фильтра нижних частот второго порядка, частоту осечки которого выбирают слегка превышающей максимальную частоту сетей электрического питания, встречающуюся во всех странах мира, то есть слегка превышающей 60 Гц.

Отрицательный вход этого операционного усилителя 231 соединен с его выходом. Положительный вход этого операционного усилителя 231 соединен с выходом буферного фильтра 220 через два резистора 232, 233. Он также соединен с массой через конденсатор 235. Он также соединен с его выходом через указанный резистор 233 и конденсатор 234.

В данном случае резистор 232 имеет сопротивление 22 кОм.

Резистор 233 имеет сопротивление 82 кОм.

Конденсатор 234 имеет емкость 220 нанофарад.

Конденсатор 235 имеет емкость 22 нанофарад.

Частота отсечки этого операционного усилителя 231 в данном случае равна 63 Гц.

Этот стабилизирующий фильтр 230 значительно интегрирует интегрированный сигнал S2’ сверх этой частоты отсечки, что позволяет устранить из интегрированного сигнала S2’ возмущения, связанные с эффектом затягивания. Таким образом, он генерирует на выходе фильтрованный сигнал S4 с периодом, равным периоду входного напряжения Ue, но смещенный по фазе относительно этого напряжения (см. фиг.9).

На этой стадии отмечается, что запаздывание фильтрованного сигнала S4 относительно входного напряжения Ue зависит, в частности, от силы света, излучаемого нагрузкой 3 (то есть, от тока 13, проходящего в нагрузке 3), а также от напряжения (110, 220, 230 или 240 В) и от частоты (50 или 60 Гц) сети 2 электрического питания.

Генератор 240 сигнала и компаратор 250 предусмотрены для преобразования фильтрованного сигнала S4 в сигнал прямоугольной формы такой же частоты, называемый «стабилизированным сигналом S6 синхронизации».

При этом генератор 240 сигнала выполнен, в частности, с возможностью генерирования опорного сигнала, называемого в данном случае «восстановленным сигналом S5», пересечение которого с фильтрованным сигналом S4 происходит периодически наподобие метронома, отрегулированного по периоду входного напряжения Ue (с неизвестным запаздыванием).

Для этого он содержит пассивный фильтр нижних частот первого порядка, вход которого подключен к выходу стабилизирующего фильтра 230 для приема фильтрованного сигнала S4. Он содержит резистор 241, через который поступает фильтрованный сигнал S4, и соединенный с массой конденсатор 242.

В данном случае резистор 241 имеет сопротивление 100 кОм.

Конденсатор 242 имеет емкость 47 нанофарад.

Что касается компаратора 250, то он содержит операционный усилитель 251, работающий по схеме компаратора, положительный вход которого подключен к выходу стабилизирующего фильтра 230 и отрицательный вход которого подключен к выходу генератора 240 сигнала.

Стабилизированный сигнал S6 синхронизации, генерируемый на выходе этого компаратора 250, имеет прямоугольную форму (см. фиг.9). Его фронты соответствуют первым пересечениям Р0 фильтрованного сигнала S4 и восстановленного сигнала S5, тогда как его спады соответствуют вторым пересечениям Р1 фильтрованного сигнала S4 и восстановленного сигнала S5, чередующимся с указанными первыми пересечениями Р0.

На этой фиг.9 видно, что положения вторых пересечений являются гораздо более четкими, чем положения первых пересечений Р0, где фильтрованный S4 и восстановленный S5 сигналы являются почти касательными. Таким образом, в данном случае именно спады стабилизированного сигнала S6 синхронизации обеспечивают синхронизацию блока 40 управления.

Кроме того, следует отметить, что фильтрованный S4 и восстановленный S5 сигналы будут изменяться одинаково при смене сети 2 электрического питания. Таким образом, напряжение (110, 220, 230 или 240 В) и частота (50 или 60 Гц) сети 2 электрического питания не будут влиять на синхронизацию, обеспечиваемую стабилизированным сигналом S6 синхронизации.

Как показано на фиг.3, избирательный каскад 150 принимает на входе два сигнала синхронизации, стабилизированный S6 и нестабилизированный S3. Им управляет сигнал S7, выдаваемый блоком 40 управления, для выбора того или иного из двух сигналов синхронизации, стабилизированного S6 и нестабилизированного S3.

В частности, этот избирательный каскад 150 интегрируют в микроконтроллер блока 40 управления.

В этом случае синхронизация блока 40 управления происходит непосредственно на основе выбранного сигнала S3, S6 (как это будет показано в индуктивном режиме) или на основе сигнала S9, получаемого из выбранного сигнала S3, S6 (как будет показано в емкостном режиме).

В индуктивном режиме выбор одного из двух сигналов синхронизации, стабилизированного S6 и нестабилизированного S3, в этом случае осуществляет блок 40 управления согласно алгоритму, представленному на фиг.10.

Как показано на фиг.10, при каждой очередной инициализации алгоритма блок 40 управления проверяет, получает ли он от командного блока 30 командный сигнал S8 (этап 301).

В отсутствие командного сигнала S8 блок 40 управления выбирает стабилизированный сигнал S6 для синхронизации переключения силового блока 10 по входному напряжению Ue (см. ниже этап 306).

И, наоборот, при наличии командного сигнала S8 (то есть, когда потребитель решил изменить силу света, излучаемого нагрузкой 3) блок 40 управления:

- изменяет управление переключением силового блока 10 таким образом, чтобы сила выходного тока 13, поступающего в нагрузку 3, увеличивалась или уменьшалась до значения, задаваемого потребителем, и

- одновременно выбирает нестабилизированный сигнал S3 синхронизации, чтобы синхронизировать ограничение входного напряжения Ue (этап 302).

Таким образом, во время регулирования силы света от нагрузки 3 синхронизация основана не на стабилизированном сигнале S6 синхронизации, а на нестабилизированном сигнале S3 синхронизации. Действительно, установлено, что запаздывание стабилизированного сигнала S6 синхронизации относительно входного напряжения Ue меняется в течение всей продолжительности регулирования, тогда как нестабилизированный сигнал S3 синхронизации остается более или менее в фазе с входным напряжением Ue (с периодом, который все же не является строго постоянным).

При этом блок 40 управления выжидает завершения регулирования силы света пользователем при помощи командного блока 30 (этап 303).

Затем, если регулирование завершено и командный сигнал S8 возвращается на ноль, блок 40 управления включает счетчик периодов (этап 304), который подсчитывает число периодов нестабилизированного сигнала S3 синхронизации таким образом, чтобы, когда счетчик достигает заранее определенного числа периодов, блок 40 управления выбирал стабилизированный сигнал S6 синхронизации (этап 306).

Заранее определенное число периодов выбирают превышающим или равным 2. В данном случае оно равно 4.

При этом счетчик периодов оставляет блоку 40 управления временной интервал, во время которого он измеряет стабилизированный сигнал S6 синхронизации по входному напряжению Ue (этап 305). Это измерение не осуществляют в течение только одного периода, а в течение этих четырех периодов по следующей причине.

Как было указано выше, запаздывание стабилизированного сигнала S6 синхронизации от входного напряжения Ue является постоянным (после завершения регулирования). Вместе с тем, его оценивают в зависимости от запаздывания, измеряемого между стабилизированным сигналом S6 синхронизации и нестабилизированным сигналом S3 синхронизации. Однако, как видно из фиг.8, этот нестабилизированный сигнал S3 синхронизации не имеет постоянного периода (см. изменения ΔT1). Таким образом, измеряемое запаздывание будет меняться от одного полупериода к другому. Следовательно, после завершения регулирования измеряют запаздывание стабилизированного сигнала S6 синхронизации относительно нестабилизированного сигнала S3 синхронизации в течение четырех последовательных периодов и вычисляют среднее значение этого запаздывания, чтобы оценить запаздывание стабилизированного сигнала S6 синхронизации относительно входного напряжения Ue.

По завершении этих четырех периодов блок 40 управления выбирает стабилизированный сигнал S6 синхронизации, затем смещает по фазе этот стабилизированный сигнал S6 синхронизации на усредненное запаздывание и, наконец, подает команду на силовой блок 10, чтобы ограничивать входное напряжение Ue синхронно с этим смещенным стабилизированным сигналом S6 синхронизации.

Таким образом, как показано на фиг.4, он может управлять переключением силового блока 10 в моменты t0, t2, t4 (соответствующие началам и концам каждого полу периода входного напряжения Ue) и в моменты t1 и t3, чтобы обеспечивать прохождение тока в нагрузку 3 между моментами t1 и t2 и между моментами t3 и t4 и блокировать ток в остальное время.

Таким образом, при установившемся режиме выходной ток I3, проходящий через нагрузку 3, остается исключительно стабильным от одного полпериода к другому, что позволяет избежать мигания нагрузки 3.

В емкостном режиме выбор того или иного из сигналов синхронизации, стабилизированного S6 и нестабилизированного S3 (этапы 301-306), осуществляют по существу так же, как и в индуктивном режиме, что видно из алгоритма, представленного на фиг.10.

Затем, в установившемся режиме, то есть когда выбранный сигнал является стабилизированным сигналом S6 синхронизации, блок 40 управления изменяет этот сигнал в конечный сигнал S9, обеспечивающий исключительно надежную синхронизацию.

Этот сигнал S9 является сигналом прямоугольной формы, имеющим для каждого полупериода входного напряжения Ue три среза, появляющихся последовательно следующим образом.

Как показано на фиг.12-14, конечный сигнал S9 имеет первый срез (фронт или спад) в начале каждого отрицательного полу периода (момент t5), второй срез (фронт или спад) на пересечении восстановленного S5 и фильтрованного S4 сигналов (момент t7) и третий срез (фронт или спад) после заранее определенного времени ΔТ2 (момент t8). На этих фигурах видно что момент t6 соответствует моменту, когда подается команда на ограничение выходного напряжения Us.

Поскольку на каждом полупериоде сигнал S9 имеет нечетное число срезов (три), то первый срез (момент t5), второй срез (момент t7) и третий срез (момент t8) поочередно будут фронтами и спадами.

Второй срез (момент t7) является срезом, который управляет синхронизацией блока 40 управления. Таким образом, он появляется на каждом пересечении восстановленного S5 и фильтрованного S4 сигналов, где сигнал S4 является уменьшающимся. Действительно именно на этих пересечениях восстановленный S5 и фильтрованный S4 сигналы является наименее касательными, что обеспечивает высокую точность при обнаружении второго среза.

Первый срез (момент t5) при этом выбирают таким образом, чтобы после момента t5 первое пересечение восстановленного S5 и фильтрованного S4 сигналов было пересечением, где фильтрованный сигнал S4 понижается. В данном случае, в частности, он появляется при каждом фронте нестабилизированного сигнала S3 синхронизации.

Третий срез (момент t8) появляется после второго среза (момент t7) по истечении заранее определенного времени ΔТ2, что позволяет избежать любого несвоевременного появления других срезов в течение этого времени. Таким образом, благодаря этому третьему срезу, если восстановленный S5 и фильтрованный S4 сигналы пересекаются несколько раз за небольшой промежуток времени (по причине неточности измерения и/или по причине их касательных положений и/или по причине шума), в течение этого заранее определенного времени ΔТ2 не появляются ни первый, ни второй срез.

Для обеспечения реализации этой функции заранее определенное время ΔТ2 предпочтительно превышает 0,5 мс. Предпочтительно его выбирают меньшим 2 мс. В данном случае оно равно 1 мс.

Как показано соответственно на фиг.12-14, второй срез (момент t7) и команда ограничения (момент t6) могут происходить один перед другой (случай 1), одновременно (случай 2) или один после другой (случай 3).

При этом цикл управления транзисторами БТИЗ будет отличаться в зависимости от случая.

Следовательно, как показано на фиг.11, при переходе в устоявшийся режим (по завершении этапа 305) микроконтроллер блока 40 управления вычисляет время ΔТ3, разделяющее моменты t5 и t7, а также время ΔТ4, разделяющее моменты t5 и t6.

При этом он сравнивает эти два промежутка времени ΔТ3, ΔТ4 для определения соответствующего случая, в котором он находится.

В частности, если время ΔТ3 превышает время ΔТ4, блок управления 40 определяет, что он находится в случае 1 (этап 308 и фиг.12). В этом случае он запрограммирован таким образом, чтобы первое событие, которое он задает после второго среза (момент t7), было ограничением положительного полупериода (момент t9).

Если же время ΔТ3 меньше времени ΔТ4, блок 40 управления переходит в случай 3 (этап 310 и фиг.14). В этом случае он запрограммирован таким образом, чтобы первое событие, которое он задает после второго среза (момент t7), было ограничением отрицательного полупериода (момент t6).

Наконец, если время ΔТ3 равно времени ΔТ4, блок 40 управления переходит в случай 2 (этап 309 и фиг.13). При этом он запрограммирован таким образом, чтобы задавать ограничение отрицательного полупериода (момент t6) в момент второго среза (момент t7). Поскольку моменты t6 и t7 происходят в одно время, команда является моментальной.

Настоящее изобретение ни в коем случае не ограничено описанными и представленными вариантами выполнения, и специалист может вносить в них свои версии.

В частности, в индуктивном режиме можно предусмотреть, чтобы блок управления изменял стабилизированный сигнал синхронизации на конечный сигнал типа показанного на фиг.12 для обеспечения исключительно надежной синхронизации.

Согласно другой версии, можно предусмотреть, чтобы компаратор (250) был интегрирован в микроконтроллер блока управления.

Кроме того, можно предусмотреть, чтобы нестабилизированный каскад (130) содержал два биполярных транзистора, расположенных в виде каскада, чтобы снизить его электрическое потребление и увеличить его коэффициент усиления.

Еще в одной версии можно предусмотреть, чтобы сигнал, выдаваемый генератором сигнала (240), был постоянным сигналом. Однако в этой версии сигнал, выдаваемый генератором сигнала, не будет автоматически меняться вместе с фильтрованным сигналом (S4) в зависимости от силы выходного тока или от входного напряжения (110, 220, 230 или 240 В). Поэтому предпочтительно адаптировать значение постоянного напряжения в зависимости от силы выходного тока и от входного напряжения таким образом, чтобы фильтрованный сигнал и постоянный сигнал пересекались, причем в момент, когда крутизна среза фильтрованного сигнала является максимальной.

Объектом изобретения является электрический регулятор (1), содержащий: две единых соединительных клеммы (2А, 2В), силовой блок (10), блок (40) управления указанным силовым блоком (10) и блок (100) синхронизации блока (40) управления. Согласно изобретению указанный блок (100) синхронизации содержит: нестабилизированный каскад, который выполнен с возможностью выдачи нестабилизированного сигнала синхронизации, синхронизируемого по электрическому напряжению, поступающему на указанную входную клемму; стабилизированный каскад, содержащий буферный фильтр, за которым следует стабилизирующий фильтр, и выполненный с возможностью выдачи периодического стабилизированного сигнала синхронизации, который синхронизируется по электрическому напряжению, поступающему на указанную входную клемму, и который затем фильтруется при помощи буферного фильтра и стабилизирующего фильтра; и избирательный каскад для выбора одного или другого из указанных стабилизированного и нестабилизированного сигналов синхронизации. Технический результат – обеспечение стабильной работы регулятора независимо от типа нагрузки. 16 з.п. ф-лы, 8 ил.

1. Электрический регулятор (1), содержащий:

две единые соединительные клеммы (2А, 2В), в том числе входную клемму (2А), соединяемую с местной электрической сетью (2), и выходную клемму (2В), соединяемую с электрической нагрузкой (3),

силовой блок (10), подключенный между указанными соединительными клеммами (2А, 2В), для периодического ограничения части электрического напряжения, подаваемого на указанную выходную клемму (2В),

блок (40) управления, выполненный с возможностью управления указанным силовым блоком (10) таким образом, чтобы изменять продолжительность ограничения электрического напряжения, подаваемого на указанную выходную клемму (2В), и

блок (100) синхронизации блока (40) управления,

отличающийся тем, что указанный блок (100) синхронизации содержит:

нестабилизированный каскад (130), выполненный с возможностью выдачи нестабилизированного сигнала (S3) синхронизации, синхронизируемого по электрическому напряжению, поступающему на указанную входную клемму (2А),

стабилизированный каскад (200), содержащий буферный фильтр (220), за которым следует стабилизирующий фильтр (230), причем стабилизированный каскад (200) выполненный с возможностью выдачи периодического стабилизированного сигнала (S6) синхронизации, синхронизированного по электрическому напряжению, которое поступает на указанную входную клемму (2А) и фильтруется посредством указанных буферного фильтра (220) и стабилизирующего фильтра (230), и

избирательный каскад (150) для выбора одного или другого из указанных стабилизированного (S6) и нестабилизированного (S3) сигналов синхронизации.

2. Электрический регулятор (1) по п.1, отличающийся тем, что указанный буферный фильтр (220) имеет большое входное сопротивление, по меньшей мере, превышающее 1 МОм.

3. Электрический регулятор (1) по п.2, отличающийся тем, что указанный буферный фильтр (220) содержит операционный усилитель (221), работающий по схеме следящего устройства.

4. Электрический регулятор (1) по п.1, отличающийся тем, что указанный стабилизирующий фильтр (230) содержит операционный усилитель (231), работающий по схеме фильтра нижних частот.

5. Электрический регулятор (1) по п.4, отличающийся тем, что указанная схема фильтра нижних частот является фильтром второго порядка.

6. Электрический регулятор по п.1, отличающийся тем, что указанный стабилизированный каскад (200) содержит на входе указанного буферного фильтра (220) пассивный фильтр (210) нижних частот первого порядка.

7. Электрический регулятор по п.1, отличающийся тем, что указанный стабилизирующий фильтр (230) выдает первый периодический сигнал (S4), и указанный стабилизированный каскад (200) содержит:

генератор (240) сигнала, который выдает второй сигнал (S5), и

компаратор (250), который генерирует указанный стабилизированный сигнал (S6) синхронизации в зависимости от указанного первого сигнала (S4) и от указанного второго сигнала (S5).

8. Электрический регулятор по п.7, отличающийся тем, что указанный блок (40) управления содержит микроконтроллер, а указанный компаратор (250) интегрирован в указанный микроконтроллер.

9. Электрический регулятор по п.7 или 8, отличающийся тем, что указанный генератор (240) сигнала содержит пассивный фильтр нижних частот первого порядка, вход которого принимает первый сигнал (S4), а выход генерирует второй сигнал (S5).

10. Электрический регулятор (1) по п.1, отличающийся тем, что указанный нестабилизированный каскад (130) содержит по меньшей мере один транзистор (131).

11. Электрический регулятор по п.10, в котором указанный транзистор (131) имеет коэффициент усиления, превышающий 100.

12. Электрический регулятор по п.1, отличающийся тем, что содержит командный блок (30), который приводится в действие пользователем и выполнен с возможностью передачи командного сигнала (S8) на указанный блок (40) управления, при этом указанный блок (40) управления управляет указанным избирательным каскадом (150) для выбора нестабилизированного сигнала (S3) синхронизации, когда приводится в действие указанный командный блок (30).

13. Электрический регулятор (1) по п.12, отличающийся тем, что указанный блок (40) управления выполнен с возможностью управлять указанным избирательным каскадом (150) таким образом, что:

выбирается нестабилизированный сигнал (S3) синхронизации в течение заранее определенного времени после прекращения действия на указанный командный блок (30), а затем выбирается стабилизированный сигнал (S6) синхронизации, пока указанный командный блок (30) опять не приводится в действие.

14. Электрический регулятор (1) по п.13, отличающийся тем, что указанный блок (40) управления содержит средства измерения запаздывания стабилизированного сигнала (S6) синхронизации по отношению к нестабилизированному сигналу (S3) синхронизации.

15. Электрический регулятор по п.1, отличающийся тем, что указанный блок (40) управления содержит микроконтроллер, а указанный избирательный каскад (150) интегрирован в указанный микроконтроллер.

16. Электрический регулятор (1) по п.1, отличающийся тем, что содержит каскад (110) ослабления, установленный между, с одной стороны, указанной входной клеммой (2А) и, с другой стороны, нестабилизированным (130) и стабилизированным (200) каскадами.

17. Электрический регулятор (1) по п.16, отличающийся тем, что указанный каскад (110) ослабления содержит пассивный фильтр (111) нижних частот первого порядка.

| УСТРОЙСТВО ДЛЯ ОСУЩЕСТВЛЕНИЯ СПОСОБА РЕГУЛИРОВАНИЯ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ | 2009 |

|

RU2408129C1 |

| СХЕМА ВОЗБУЖДЕНИЯ ГАЗОРАЗРЯДНОЙ ЛАМПЫ | 1998 |

|

RU2237390C2 |

| Стыковочная станция, уборочное устройство и система для уборки | 2022 |

|

RU2802360C1 |

Авторы

Даты

2017-02-09—Публикация

2013-02-28—Подача