Изобретение относится к области микроминиатюризации и технологии радиоэлектронной аппаратуры и может быть использовано для контроля параметров микросхем при их производстве.

Известен способ для определения нагрузочной способности микросхем (Фролкин В.Т., Попов Л.Н. Импульсные и цифровые устройства: Учеб. пособие для вузов. - М.: Радио и связь, 1992. - 336 с.: ил. - с. 127), связанный с нахождением наибольшего числа входов логических элементов, которые можно подключить к выходу испытуемой микросхемы без ухудшения ее параметров.

Недостатками устройств, реализующих этот способ, являются низкие точность и достоверность определения нагрузочной способности.

Наиболее близким к предлагаемому изобретению является устройство для определения нагрузочной способности дискретных схем (авторское свидетельство СССР №836606, МПК G01R 31/28, опубл. 07.06.81. Бюл. №21), содержащее коммутатор, соединенный первыми входами с выходами контролируемых дискретных схем, последовательно соединенные первый генератор, усилитель, индикатор, дифференцирующий элемент и второй генератор, а также третий генератор, элемент И и блок памяти, триггер, первый и второй выходы которого соединены соответственно с первым входом элемента И и входом первого генератора, первый вход триггера также соединен с входом второго генератора, первый и второй выходы которого соединены со вторыми входами соответственно коммутатора и триггера, вход индикатора соединен также с выходом коммутатора.

Недостатками устройства являются низкие точность и достоверность определения нагрузочной способности.

В основу изобретения поставлена задача повысить точность и достоверность определения нагрузочной способности микросхем.

Данная задача решается в устройстве для определения нагрузочной способности микросхем, которое содержит генератор прямоугольного напряжения, элементы нагрузки, коммутатор, а также последовательно соединенные элемент И и счетчик импульсов, согласно изобретению, в него дополнительно введены рабочая микросхема, вход которой и входная клемма испытуемой микросхемы объединены и подключены к выходу генератора прямоугольного напряжения, вольтметр, сигнальный вход которого и сигнальный вход коммутатора объединены и подключены к выходной клемме испытуемой микросхемы, управляющие входы вольтметра и коммутатора, а также первый вход элемента И объединены и подключены к выходу рабочей микросхемы, последовательно соединенные источник опорного напряжения и компаратор, второй вход которого подключен к выходу вольтметра, а выход - ко второму входу элемента И, каждый из выходов коммутатора подключен к входу одноименного элемента нагрузки.

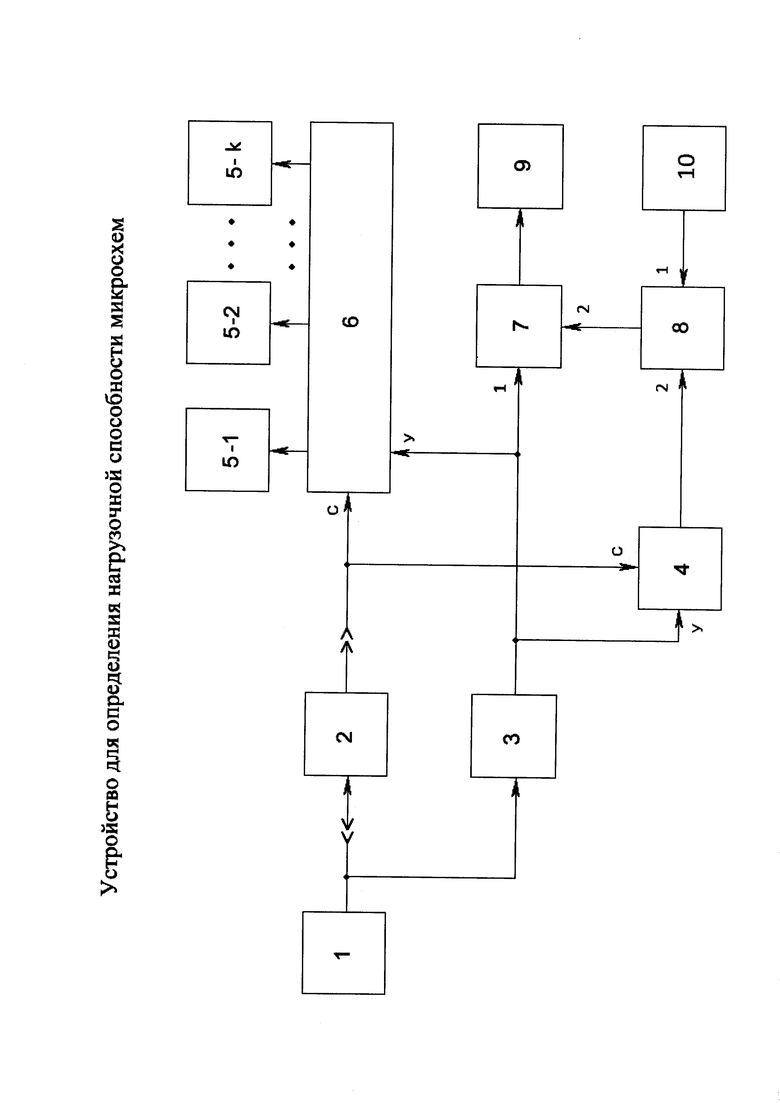

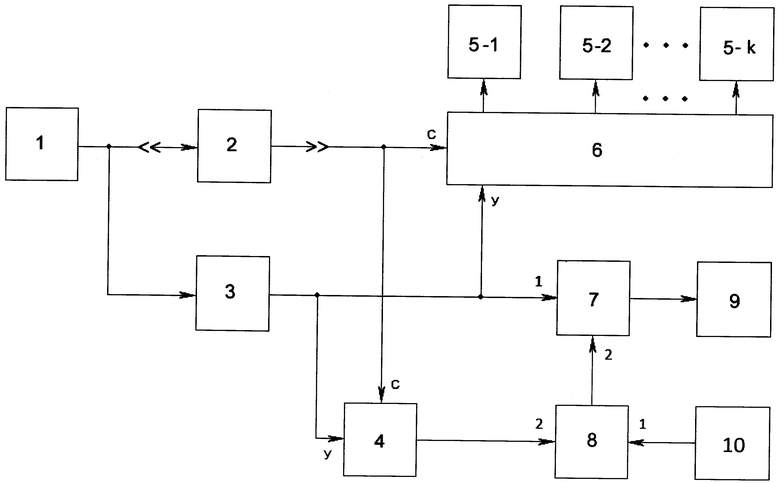

На чертеже представлена блок-схема предлагаемого устройства.

Устройство содержит генератор прямоугольного напряжения 1, испытуемую микросхему 2, рабочую микросхему 3, вольтметр 4, элементы нагрузки 5-1…5-k, коммутатор 6, элемент И 7, компаратор 8, счетчик импульсов 9 и источник опорного напряжения 10.

В устройстве последовательно соединены генератор прямоугольного напряжения 1, рабочая микросхема 3, элемент И 7 и счетчик импульсов 9, а также источник опорного напряжения 10 и компаратор 8. Входная клемма испытуемой микросхемы 2 также подключена к выходу генератора прямоугольного напряжения 1. Сигнальные входы вольтметра 4 и коммутатора 6 объединены и подключены к выходной клемме испытуемой микросхемы 2. Управляющие входы вольтметра 4 и коммутатора 6 объединены и также подключены к выходу рабочей микросхемы 3. Выход вольтметра 4 связан со вторым входом компаратора 8, выход которого подключен ко второму входу элемента И 7. Каждый из выходов коммутатора 6 подключен к входу одноименного элемента нагрузки 5-1…5-k.

Устройство позволяет определять нагрузочную способность испытуемой микросхемы 2 по изменению высокого уровня (первый режим) и по изменению низкого уровня (второй режим) ее выходного сигнала.

В соответствии с первым режимом устройство работает следующим образом. Генератор прямоугольного напряжения 1 формирует первый импульс, который одновременно поступает на входы идентичных испытуемой 2 и рабочей 3 микросхем. На выходе каждой из этих микросхем формируется по импульсу высокого уровня с одинаковой длительностью. Выходной сигнал испытуемой микросхемы 2 одновременно поступает на сигнальные входы вольтметра 4 и коммутатора 6. Последний выполнен на основе регистра сдвига и набора аналоговых ключей. Выходной сигнал рабочей микросхемы 3 одновременно поступает на управляющие входы вольтметра 4 и коммутатора 6, а также первый вход элемента И 7.

С приходом первого импульса высокого уровня на управляющий вход коммутатора 6 последний подключает свой сигнальный вход (выход испытуемой микросхемы 2) к входу первого элемента нагрузки 5-1.

На выходе вольтметра 4 в течение всего периода выходного сигнала рабочей микросхемы 3, совпадающего по времени с аналогичным периодом испытуемой микросхемы 2, поддерживается значение напряжения высокого уровня выходного сигнала последней. Компаратор 8 сравнивает значения выходных напряжений вольтметра 4 и источника опорного напряжения 10. Последнее совпадает с минимально допустимым значением напряжения высокого уровня выходного сигнала испытуемой микросхемы 2 при определении ее нагрузочной способности по первому режиму.

В случае использования исправной испытуемой микросхемы 2, нагруженной по выходу элементом 5-1, выходное напряжение вольтметра 4 превышает напряжение источника опорного напряжения 10 и на выходе компаратора 8 формируется логическая "1". Она поступает на второй вход элемента И 7, разрешая прохождению с его первого входа на выход импульса высокого уровня. При этом счетчик импульсов 9 фиксирует поступление на свой вход первой логической "1". Это означает, что нагрузочная способность испытуемой микросхемы 2 в результате первого рабочего цикла ее определения составляет число не менее единицы.

В течение действия последующих выходных импульсов генератора прямоугольного напряжения 1 устройство в целом работает аналогично ранее описанному. Отличие состоит лишь в том, что с приходом очередного импульса (высокого уровня) на управляющий вход коммутатора 6, последний подключает свой сигнальный вход (выход испытуемой микросхемы 2) к входу одноименного элемента нагрузки из имеющихся 5-2…5-k. Каждый из них включает в себя свой ряд (от одного до нескольких десятков) одинаковых логических элементов, число входов которых, объединенных друг с другом общим входом элемента нагрузки, совпадает с его номером. При этом с каждым новым переключением коммутатора 6 значение напряжения высокого уровня выходного сигнала испытуемой микросхемы 2, в связи с уменьшением сопротивления нагрузки (и возрастанием ее тока), уменьшается. До тех пор, пока это напряжение, измеряемое вольтметром 4, остается больше напряжения источника опорного напряжения 10 (в течение всех рабочих циклов), счетчик импульсов 9 фиксирует импульсы, производя тем самым запись числа (n), определяющего нагрузочную способность.

Для обеспечения второго режима работы устройства, позволяющего определять нагрузочную способность испытуемой микросхемы 2 по изменению низкого уровня ее выходного сигнала, необходимо:

- первый вход компаратора 8 подключить к выходу вольтметра 4, а второй вход - к выходу источника опорного напряжения 10,

- значение выходного напряжения источника опорного напряжения 10 установить равным максимально допустимому значению напряжения низкого уровня выходного сигнала испытуемой микросхемы 2.

При этом, с каждым новым переключением коммутатора 6, значение напряжения низкого уровня выходного сигнала испытуемой микросхемы 2 увеличивается. До тех пор, пока это напряжение, измеряемое вольтметром 4, остается меньше напряжения источника опорного напряжения 10 (в течение всех рабочих циклов), счетчик импульсов 9 фиксирует импульсы, производя тем самым определение нагрузочной способности (по второму режиму). В остальном работа всех блоков устройства в обоих режимах одинакова.

Введение рабочей микросхемы 3, идентичной испытуемой 2, позволило синхронизировать процесс управления вольтметром 4, коммутатором 6 и элементом И 7 с временными параметрами выходного сигнала испытуемой микросхемы 2, не подключая соответствующие входы указанных блоков к ее выходу. Это снизило влияние на процесс определения нагрузочной способности искажений выходных импульсов испытуемой микросхемы 2, возникающих при подключении к ее выходу большого числа входов логических элементов, входящих в состав элементов нагрузки 5-1…5-k. При этом неискаженный управляющий сигнал в те же моменты времени и той же длительности, что и у испытуемой микросхемы 2, стал поступать на управляющие входы вольтметра 4 и коммутатора 6, а также вход элемента И 7 с выхода рабочей микросхемы 3.

Кроме того, преимуществами устройства по сравнению с прототипом являются: возможность определения нагрузочной способности микросхем в двух режимах работы, не меняя состав его блоков, обеспечение автоматического режима работы и адаптированность к смене испытуемых микросхем 2 и элементов нагрузки 5-1…5-k.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ НАГРУЗОЧНОЙ СПОСОБНОСТИ МИКРОСХЕМ | 2015 |

|

RU2613573C1 |

| Устройство для определения нагрузочной способности микросхем | 2022 |

|

RU2793145C1 |

| Устройство для определения нагрузочной способности микросхем | 2019 |

|

RU2723968C1 |

| Устройство для определения нагрузочной способности микросхем | 2017 |

|

RU2649244C9 |

| Устройство для определения нагрузочной способности микросхем | 2023 |

|

RU2819099C1 |

| Универсальный время-импульсный интегрирующий преобразователь напряжения с четырьмя функциями широтно-импульсной модуляции | 2023 |

|

RU2822374C1 |

| УСТРОЙСТВО ДЛЯ СНЯТИЯ ФАЗОЧАСТОТНОЙ ХАРАКТЕРИСТИКИ УСИЛИТЕЛЕЙ | 2011 |

|

RU2480775C2 |

| УСТРОЙСТВО ДЛЯ СНЯТИЯ АМПЛИТУДНО-ЧАСТОТНОЙ И ФАЗОЧАСТОТНОЙ ХАРАКТЕРИСТИК УСИЛИТЕЛЕЙ | 2011 |

|

RU2476893C1 |

| УСТРОЙСТВО ДЛЯ ОТБРАКОВКИ ДВУХАНОДНЫХ СТАБИЛИТРОНОВ | 2010 |

|

RU2450281C1 |

| УСТРОЙСТВО ДЛЯ ОТБРАКОВКИ ДИОДОВ | 2009 |

|

RU2415447C1 |

Изобретение относится к области микроминиатюризации и технологии радиоэлектронной аппаратуры и может быть использовано для контроля параметров микросхем при их производстве. Технический результат: повышение точности и достоверности определения нагрузочной способности микросхем. Сущность: устройство содержит генератор прямоугольного напряжения 1, испытуемую микросхему 2, рабочую микросхему 3, вольтметр 4, элементы нагрузки 5-1…5-k, коммутатор 6, элемент И 7, компаратор 8, счетчик импульсов 9, источник опорного напряжения 10. В устройстве последовательно соединены генератор прямоугольного напряжения 1, рабочая микросхема 3, элемент И 7 и счетчик импульсов 9, а также источник опорного напряжения 10 и компаратор 8. Входная клемма испытуемой микросхемы 2 также подключена к выходу генератора прямоугольного напряжения 1. Сигнальные входы вольтметра 4 и коммутатора 6 объединены и подключены к выходной клемме испытуемой микросхемы 2. Управляющие входы вольтметра 4 и коммутатора 6 объединены и также подключены к выходу рабочей микросхемы 3. Выход вольтметра 4 связан со вторым входом компаратора 8, выход которого подключен ко второму входу элемента И 7. Каждый из выходов коммутатора 6 подключен к входу одноименного элемента нагрузки 5-1…5-k. 1 ил.

Устройство для определения нагрузочной способности микросхем, содержащее генератор прямоугольного напряжения, элементы нагрузки, коммутатор, а также последовательно соединенные элемент И и счетчик импульсов, отличающееся тем, что в него дополнительно введены рабочая микросхема, вход которой и входная клемма испытуемой микросхемы объединены и подключены к выходу генератора прямоугольного напряжения, вольтметр, сигнальный вход которого и сигнальный вход коммутатора объединены и подключены к выходной клемме испытуемой микросхемы, управляющие входы вольтметра и коммутатора, а также первый вход элемента И объединены и подключены к выходу рабочей микросхемы, последовательно соединенные источник опорного напряжения и компаратор, второй вход которого подключен к выходу вольтметра, а выход - ко второму входу элемента И, каждый из выходов коммутатора подключен к входу одноименного элемента нагрузки.

| Устройство для определения нагрузочнойСпОСОбНОСТи диСКРЕТНыХ CXEM | 1979 |

|

SU836606A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| УСТРОЙСТВО для КОНТРОЛЯ НАГРУЗОЧНОЙ СНОСОБНОСТИ ПОРОГОВЫХ СХЕМ | 0 |

|

SU266945A1 |

| JPS 63122973 А, 26.05.1988. | |||

Авторы

Даты

2017-03-17—Публикация

2015-12-14—Подача