Изобретение относится к измерительной технике и может быть использовано для контроля параметров микросхем при их производстве.

Известен способ для определения нагрузочной способности микросхем (Фролкин В.Т., Попов Л.Н. Импульсные и цифровые устройства: Учеб. пособие для вузов. - М.: Радио и связь, 1992. - 336 с: ил. - с. 127), связанный с нахождением наибольшего числа входов логических элементов, которые можно подключить к выходу испытуемой микросхемы без ухудшения ее параметров.

Недостатками устройств, реализующих этот способ, являются низкие точность и производительность определения нагрузочной способности.

Наиболее близким к предлагаемому изобретению является устройство для определения нагрузочной способности микросхем (патент на изобретение РФ №2723968, МПК G01R 31/28, опубл. 18.06.2020. Бюл. №17), содержащее источник опорного напряжения, генератор прямоугольного напряжения, испытуемую микросхему, повторитель, компаратор, элемент И, одновибратор, элементы нагрузки, коммутатор, реверсивный счетчик импульсов, дешифратор и индикатор.

Недостатками устройства являются низкие точность и производительность определения нагрузочной способности.

В основу изобретения поставлена задача повысить точность и производительность определения нагрузочной способности микросхем.

Данная задача решается в устройстве для определения нагрузочной способности микросхем, которое содержит элементы нагрузки, коммутатор, каждый из выходов которого подключен к входу одноименного элемента нагрузки, индикатор, повторитель, вход которого и сигнальный вход коммутатора объединены и подключены к выходной клемме испытуемой микросхемы, последовательно соединенные источник опорного напряжения и компаратор, второй вход которого подключен к выходу повторителя, согласно изобретению в него дополнительно введен микроконтроллер, имеющий две группы выходов, причем каждый из выходов первой и второй групп подключен к одноименному входу коммутатора и индикатора соответственно, вход микроконтроллера подключен к выходу компаратора.

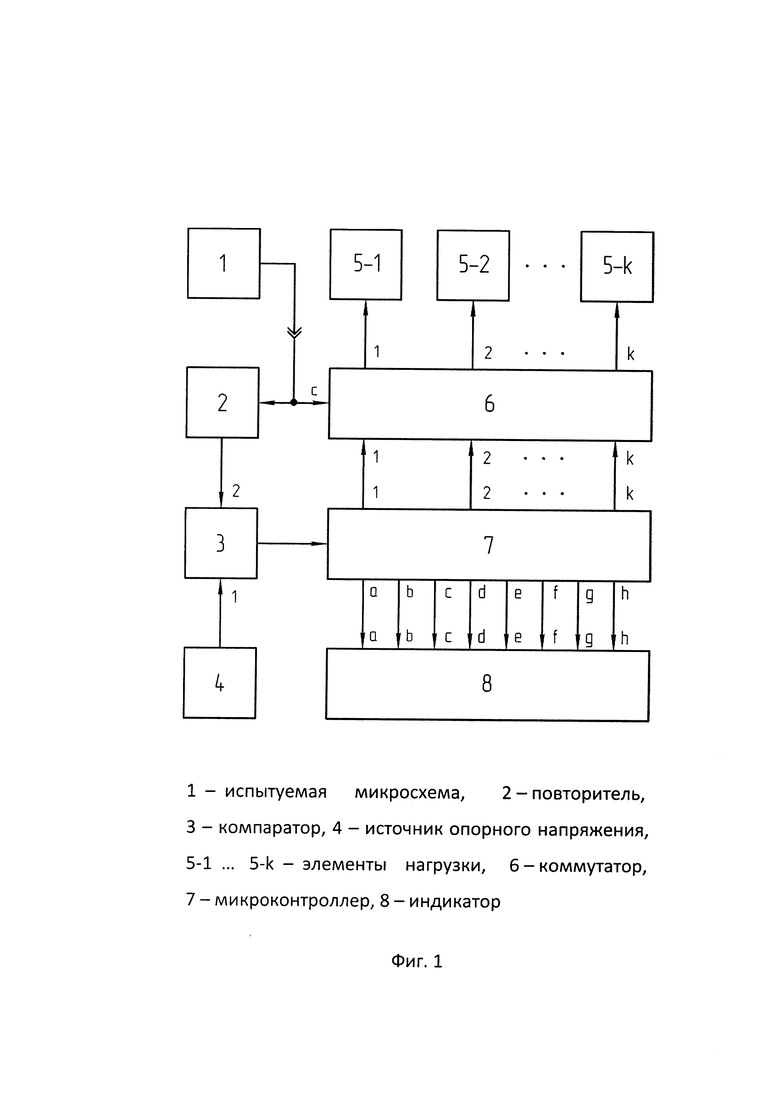

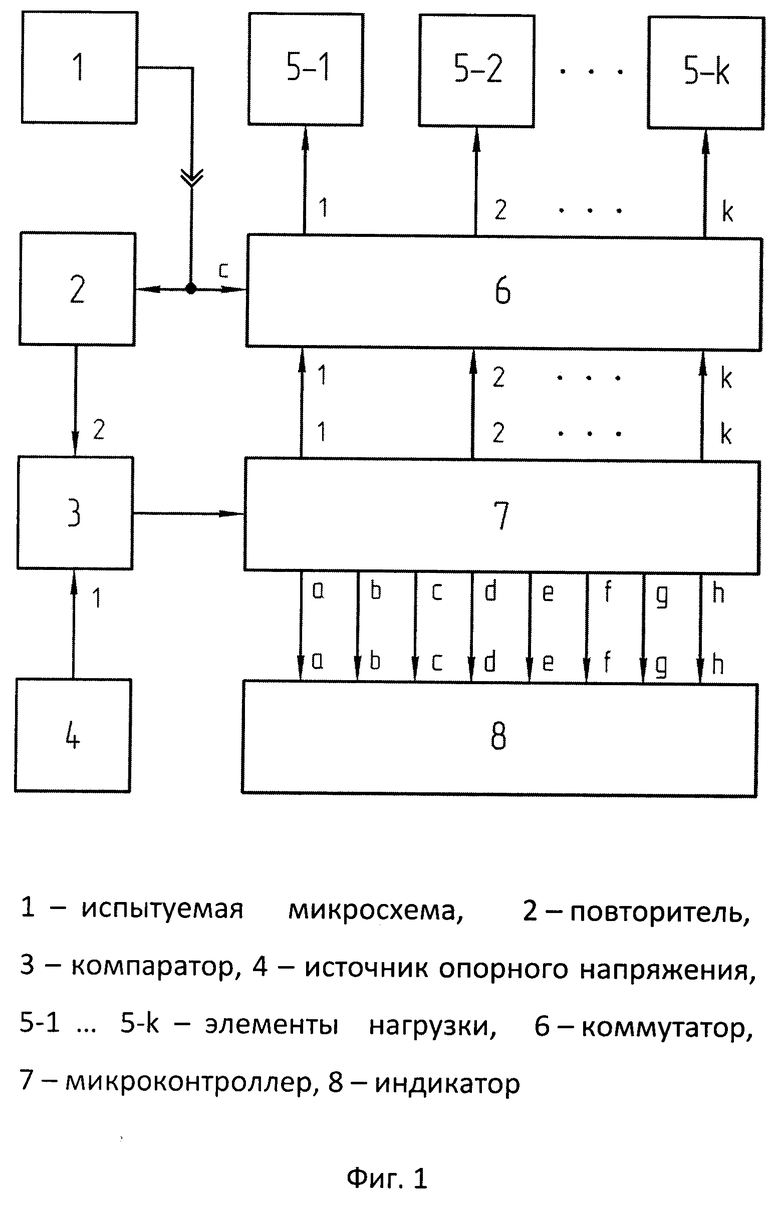

На чертеже представлена блок-схема предлагаемого устройства.

Устройство содержит испытуемую микросхему 1, повторитель 2, компаратор 3, источник опорного напряжения 4, элементы нагрузки 5-1…5-k, коммутатор 6, микроконтроллер 7 и индикатор 8.

Вход повторителя 2 и сигнальный вход коммутатора 6 объединены и подключены к выходной клемме испытуемой микросхемы 1. Вход каждого из элементов нагрузки 5-1…5-k подключен к одноименному выходу коммутатора 6. Первый и второй входы компаратора 3 подключены соответственно к выходу источника опорного напряжения 4 и повторителя 2. Выход компаратора 3 подключен ко входу микроконтроллера 7. Каждый из выходов первой группы микроконтроллера 7 подключен к одноименному входу коммутатора 6. Каждый из выходов второй группы микроконтроллера 7 подключен к одноименному входу индикатора 8.

Устройство позволяет определять нагрузочную способность испытуемой микросхемы 1 по изменению высокого уровня (первый режим) и по изменению низкого уровня (второй режим) ее выходного сигнала.

В соответствии с первым режимом устройство работает следующим образом. Выходное напряжение испытуемой микросхемы 1 поступает на вход повторителя 2 и сигнальный вход коммутатора 6.

Микроконтроллер 7 на своих выходах первой группы формирует управляющий код для коммутатора 6, в соответствии с которым последний подключает к выходу испытуемой микросхемы 1 необходимые элементы нагрузки из числа 5-1…5-k. Сигнал с каждого из выходов первой группы микроконтроллера 7 поступает на одноименный вход коммутатора 6. «Вес» каждого из выходов (разрядов) первой группы микроконтроллера 7, начиная со второго, в два раза выше предыдущего. «Весовые» соотношения элементов нагрузки 5-1…5-k совпадают с «весовыми» соотношениями одноименных выходов (разрядов) первой группы микроконтроллера 7. Каждый из элементов нагрузки 5-1…5-k имеет в своем составе логические элементы, число входов которых соответствует его «весу». Входы логических элементов во всех элементах нагрузки 5-1…5-k, кроме первого (в нем необходим один вход логического элемента), объединены в общий вход.

Работа микроконтроллера 7 производится в соответствии с методом половинного деления (дихотомией) интервала поиска значения нагрузочной способности микросхемы.

Первоначально (в ходе первой итерации) управляющий код микроконтроллера 7 задает исходное число входов логических элементов (n), входящих в состав элементов нагрузки 5-1…5-k, подключаемых с помощью коммутатора 6 к выходу испытуемой микросхемы 1. Оно соответствует нагрузочной способности, превышающей половину ее максимального справочного значения, и выбирается из ряда чисел: 2, 4, 8, 16, 32 и т.д. (для удобства работы в двоичной системе).

Так, например, если испытуемая микросхема 1 изготовлена по КМОП-технологии и имеет максимальное справочное значение нагрузочной способности n макс.справ.=50, то первоначальный управляющий код микроконтроллера 7 будет соответствовать n=32.

Компаратор 3 сравнивает значения выходных напряжений повторителя 2 и источника опорного напряжения 4. Первое из них практически совпадает со значением выходного напряжения испытуемой микросхемы 1, а второе равно минимально допустимому значению напряжения высокого уровня (логической «1») выходного сигнала испытуемой микросхемы 1. На выходе компаратора 3 формируется логическая «1», если первое из сравниваемых напряжений превышает второе, в противном случае - логический «0». Выходное напряжение компаратора 3 поступает на вход микроконтроллера 7 и управляет его работой.

Если, после подключения нагрузки к выходу испытуемой микросхемы 1 в соответствии с первоначальным управляющим кодом микроконтроллера 7, на выходе компаратора 3 формируется логическая «1», это означает, что определяемая нагрузочная способность испытуемой микросхемы 1 численно не меньше значения, задаваемого этим кодом (для испытуемой микросхемы 1 в приводимом примере n≥32).

В этом случае для дальнейшего определения нагрузочной способности испытуемой микросхемы 1 первоначальный управляющий код микроконтроллера 7 должен быть изменен с учетом увеличения n на половину от предыдущего значения интервала поиска (для испытуемой микросхемы 1 в приводимом примере новое n=32+16=48).

Если, после подключения нагрузки к выходу испытуемой микросхемы 1 в соответствии с первоначальным управляющим кодом микроконтроллера 7, на выходе компаратора 3 формируется логический «0», это означает, что определяемая нагрузочная способность испытуемой микросхемы 1 численно меньше значения, задаваемого этим кодом (для испытуемой микросхемы 1 в приводимом примере n<32 и лежит в пределах от 0 до 31).

В этом случае для дальнейшего определения нагрузочной способности испытуемой микросхемы 1 первоначальный управляющий код микроконтроллера 7 должен быть изменен с учетом уменьшения n на половину от предыдущего значения интервала поиска (для испытуемой микросхемы 1 в приводимом примере новое n=32-16=16).

По завершению первой итерации управляющий код микроконтроллера 7, формируемый на его выходах первой группы, задает новое число входов логических элементов, входящих в состав элементов нагрузки 5-1…5-k, которые должны быть подключены с помощью коммутатора 6 к выходу испытуемой микросхемы 1, для проведения второй итерации. Для испытуемой микросхемы 1 в приводимом примере новое число входов логических элементов n будет составлять 48 или 16, в зависимости от того, что присутствовало на выходе компаратора 3 (входе микроконтроллера 7) в ходе первой итерации, соответственно логические «1» или «0».

Далее в ходе каждой последующей итерации процессы

- установки управляющего кода микроконтроллера 7,

- подключения (в соответствии с этим кодом) коммутатором 6 к выходу испытуемой микросхемы 1 необходимых элементов нагрузки из числа 5-1…5-k,

- сравнения компаратором 3 значений выходных напряжений повторителя 2 и источника опорного напряжения 4,

- введения (по результатам этого сравнения) корректив, аналогичных проводимым в ходе первой итерации, изменяющих управляющий код микроконтроллера 7, используя метод половинного деления интервала поиска значения нагрузочной способности микросхемы, повторяются до тех пор, пока не будет найдено наибольшее число входов логических элементов, входящих в состав элементов нагрузки 5-1…5-k, с которыми значение напряжения высокого уровня выходного сигнала испытуемой микросхемы 1 остается больше значения выходного напряжения источника опорного напряжения 4. Данные по каждой итерации сохраняются в памяти контроллера 7.

Так, нагрузочная способность испытуемой микросхемы 1 в приводимом примере, характеризуемая числом 41, может быть найдена за шесть итераций. При этом, управляющий код микроконтроллера 7 поочередно будет задавать такое число входов логических элементов, входящих в состав элементов нагрузки 5-1…5-k, подключаемых с помощью коммутатора 6 к выходу испытуемой микросхемы 1, которое выбирается из приближающей последовательности: 32 (+32), 48 (+16), 40 (-8), 44 (+4), 42 (-2), 41 (-1), в скобках указаны приращения (интервалы поиска) для каждой итерации.

Таким образом, появляется выигрыш в производительности (W) при определении нагрузочной способности по методу половинного деления интервала поиска ее значения по сравнению с методом (используемом в прототипе), когда происходит равномерное наращивание числа входов логических элементов, подключаемых к выходу испытуемой микросхемы. В приводимом примере число итераций, за которое может быть определена нагрузочная способность, по первому методу составляет шесть, а по второму - сорок одна (W=41/6 ≈ 6,83).

Сигнал с каждого из выходов второй группы микроконтроллера 7 поступает на одноименный вход индикатора 8.

Микроконтроллер 7, задавая управляющий код для коммутатора 6, одновременно формирует на своих выходах второй группы входной код для индикатора 8. Последний отображает число n1, определяющее нагрузочную способность по первому режиму.

Для обеспечения второго режима работы устройства, позволяющего определять нагрузочную способность испытуемой микросхемы 1 по изменению низкого уровня ее выходного сигнала, необходимо:

- первый вход компаратора 3 подключить к выходу повторителя 2, а второй вход - к выходу источника опорного напряжения 4,

- значение выходного напряжения источника опорного напряжения 4 установить равным максимально допустимому значению напряжения низкого уровня (логического «0») выходного сигнала испытуемой микросхемы 1.

Работа всех блоков устройства в первом и втором режимах в целом одинакова. Отличие состоит, лишь, в том, что процессы в ходе каждой итерации во втором режиме повторяются до тех пор, пока не будет найдено наибольшее число входов логических элементов, входящих в состав элементов нагрузки 5-1…5-k, с которыми значение напряжения низкого уровня выходного сигнала испытуемой микросхемы 1 остается меньше значения выходного напряжения источника опорного напряжения 4.

Индикатор 8 отображает число n2, определяющее нагрузочную способность по второму режиму.

Кроме этого, устройство может работать (не меняя блок-схемы) по программе с равномерным или иным управляемым изменением числа входов логических элементов, подключаемых к выходу испытуемой микросхемы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения нагрузочной способности микросхем | 2019 |

|

RU2723968C1 |

| Устройство для определения нагрузочной способности микросхем | 2017 |

|

RU2649244C9 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ НАГРУЗОЧНОЙ СПОСОБНОСТИ МИКРОСХЕМ | 2015 |

|

RU2613568C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ НАГРУЗОЧНОЙ СПОСОБНОСТИ МИКРОСХЕМ | 2015 |

|

RU2613573C1 |

| Устройство для определения нагрузочной способности микросхем | 2022 |

|

RU2793145C1 |

| СИСТЕМА ФУНКЦИОНАЛЬНОГО ТЕСТИРОВАНИЯ КОРПУСИРОВАННЫХ МИКРОСХЕМ ОПЕРАТИВНО ЗАПОМИНАЮЩИХ УСТРОЙСТВ | 2009 |

|

RU2438164C2 |

| Способ тестирования микросхем энергонезависимой памяти и устройство для его осуществления | 2023 |

|

RU2821349C1 |

| Способ локализации дефектов короткого замыкания выводов микросхем JTAG интерфейсом и устройство для его осуществления | 2018 |

|

RU2703493C1 |

| УСТРОЙСТВО ДЛЯ СИГНАЛИЗАЦИИ ОДНОФАЗНОГО ЗАМЫКАНИЯ НА ЗЕМЛЮ В ЭЛЕКТРИЧЕСКОЙ СЕТИ ПЕРЕМЕННОГО ТОКА | 1995 |

|

RU2101826C1 |

| СПОСОБ РЕГУЛИРОВАНИЯ МОЩНОСТИ ПЕРЕДАЧИ ЗЕМНЫХ СТАНЦИЙ СЕТИ СПУТНИКОВОЙ СВЯЗИ, УСТРОЙСТВО РЕГУЛИРОВАНИЯ МОЩНОСТИ ПЕРЕДАЧИ ЗЕМНОЙ СТАНЦИИ И ФОРМИРОВАТЕЛЬ УПРАВЛЯЮЩЕГО СИГНАЛА | 2001 |

|

RU2214682C2 |

Устройство для определения нагрузочной способности микросхем относится к измерительной технике и может быть использовано для контроля параметров микросхем при их производстве. Устройство содержит испытуемую микросхему 1, повторитель 2, компаратор 3, источник опорного напряжения 4, элементы нагрузки 5-1…5-k, коммутатор 6, микроконтроллер 7 и индикатор 8. Техническим результатом при реализации заявленного решения является повышение точности и производительности определения нагрузочной способности микросхем. 1 ил.

Устройство для определения нагрузочной способности микросхем, содержащее элементы нагрузки, коммутатор, каждый из выходов которого подключен к входу одноименного элемента нагрузки, индикатор, повторитель, вход которого и сигнальный вход коммутатора объединены и подключены к выходной клемме испытуемой микросхемы, последовательно соединенные источник опорного напряжения и компаратор, второй вход которого подключен к выходу повторителя, отличающееся тем, что в него дополнительно введен микроконтроллер, имеющий две группы выходов, причем каждый из выходов первой и второй групп подключен к одноименному входу коммутатора и индикатора соответственно, вход микроконтроллера подключен к выходу компаратора.

| Устройство для определения нагрузочной способности микросхем | 2019 |

|

RU2723968C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ НАГРУЗОЧНОЙ СПОСОБНОСТИ МИКРОСХЕМ | 2015 |

|

RU2613573C1 |

| Статья: "Устройство для определения нагрузочной способности микросхем", Ж | |||

| Труды МАИ | |||

| Приспособление для останова мюля Dobson аnd Barlow при отработке съема | 1919 |

|

SU108A1 |

| Устройство для измерения статических параметров цифровых интегральных микросхем | 1977 |

|

SU718813A1 |

| FR 3009086 A1, 30.01.2015 | |||

| CN 101059550 A, 24.10.2007. | |||

Авторы

Даты

2024-05-14—Публикация

2023-09-19—Подача