ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

[0001] Настоящее изобретение относится к устройству кодирования изображения, способу кодирования изображения и программе, а также к устройству декодирования изображения, способу декодирования изображения и программе. В частности, настоящее изобретение относится к способу кодирования параметра качества изображения и к способу декодирования, относящемуся к вычислению параметра качества изображения и вставке кода в кодирование изображения.

ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

[0002] H.264/Усовершенствованное кодирование видеоданных (AVC) стандарта экспертной группы по вопросам движущегося изображения (MPEG)-4, далее в настоящем документе именуемое H.264, известен как способ записи движущегося изображения со сжатием. H.264 широко используется в односегментном цифровом наземном вещании и других применениях. H.264 характеризуется тем, что обеспечивает множество возможностей внутреннего предсказания, используя целочисленные преобразования в модулях размером 4x4 пикселей в дополнение к традиционным схемам кодирования (смотри ISO/IEC 14496-10: 2004 Information technology -- Coding of audio-visual objects -- Part 10: Advanced Video Coding, ITU-T H.264 Advanced video coding for generic audiovisual services).

[0003] Схемы кодирования с использованием ортогонального преобразования и квантования, представленные в стандарте MPEG-2 и H.264, выполняют ортогональное преобразование и квантование предварительно заданных разделенных на блоки изображений с целью генерирования данных коэффициента квантования. Для управления качеством изображения квантование выполняется посредством использования параметра управления качеством изображения, называемого параметром квантования. В конкретном плане квантование с использованием малого значения параметра квантования позволяет получить улучшенное качество изображения, но с большим объемом кода. Квантование с большим значением параметра квантования позволяет получить низкое качество изображения с уменьшенным объемом кода. В соответствии с целевым объемом кода для осуществления кодирования выбираются оптимальные значения параметра квантования. Такое управление именуется управлением скоростью. Были описаны различные способы управление скоростью, включая TM5. После осуществления квантования, с целью генерирования кодированных данных коэффициента, данные коэффициента квантования подвергаются кодированию переменной длины (с переменной длиной кода).

[0004] Кодирование параметров квантования также осуществляется с целью генерирования кода параметров квантования. Например, H.264 использует значение разности между параметром квантования, используемым для квантования блока, предшествующего целевому блоку, и параметром квантования, используемым для квантования целевого блока. Упомянутое значение разности именуется разностью параметров квантования (QP_DELTA). Вычисленная QP_DELTA кодируется в код QP_DELTA посредством кодирования Голомба или арифметического кодирования. Например, кодек кода QP_DELTA с использованием кодирования Голомба позволяет получить один бит кода, даже если значение разности составляет 0. Сгенерированные таким образом кодированные данные коэффициента и код параметров квантования передаются на декодер. Декодер осуществляет декодирование кодированных данных коэффициента и кода параметров квантования с целью генерирования данных коэффициента квантования и параметров квантования. Декодер затем выполняет обратное квантование и обратное ортогональное преобразование данных коэффициента квантования посредством использования параметров квантования, генерируя, тем самым, декодированное изображение.

[0005] Одиночный модуль обработки в стандартах MPEG-2 и H.264 называется макроблоком. Макроблоки представляют собой сетчатые блоки размером 16x16 пикселей, на которые делится изображение в сетчатой структуре. С точки зрения пикселей блоки, подлежащие ортогональному преобразованию в стандарте MPEG-2, имеют размер 8×8 пикселей, а в стандарте H.264 – размер 8×8 пикселей или 4×4 пикселя. То есть один макроблок включает в себя множество блоков ортогонального преобразования. Стандарты MPEG-2 и H.264 могут управлять (управление скоростью) параметрами квантования в модулях (единицах) макроблоков. Квантование блоков ортогонального преобразования, включенных в один и тот же самый макроблок, осуществляется с помощью одного и того же параметра квантования. В соответствии с улучшенной техникой стандарта H.264, изображение делится в сетчатой структуре на сетчатые блоки, называемые наибольшими блоками дерева кодирования (LCTB). Блок LCTB имеет размер 64×64 пикселя. Блоки LCTB делятся на блоки меньших размеров, называемые блоками дерева кодирования (CTB), посредством использования структуры дерева квадрантов, разбивающего пространство. Для осуществления поиска или ввода/вывода данных, структурированных по типу дерева, необходимо конкретизировать порядок сканирования. Блок CTB включает в себя блоки ортогонального преобразования, называемые модулями преобразования (TU). Модули TU также могут делиться на меньшие размеры посредством использования структуры дерева квадрантов, разбивающего пространство. Каждый модуль имеет флаг разделения. Блок, имеющий флаг разделения «истина», структурируется с возможностью включать в себя четыре разделительных блока, имеющих размер 1/2 по высоте и ширине. Блок, имеющий флаг разделения «ложь», не включает в себя ни одного разделительного блока и содержит вместо этого реальные данные по блоку. Иными словами, только неразделенные модули TU содержат данные коэффициента по блокам изображения. Блок LCTB (сетчатый блок) включает в себя множество иерархически структурированных блоков различных размеров ортогонального преобразования. Определение необходимости деления блока может определяться посредством различных способов. Один из способов определения описан в выложенной заявке на патент Японии № 2005-191706, включающей в себя использование множителей Лагранжа с целью вычисления стоимостей блока и выбора способа деления блока по более низкой стоимости.

[0006] Предположим, что способ кодирования изображения включает в себя кодирование изображения в модулях сетчатых блоков, на которые делится изображение в сетчатой структуре. Если данные сетчатые блоки являются большими по размеру, а управление качеством изображения выполняется в модулях сетчатых блоков, границы между блоками с разным качеством изображения могут становиться заметными.

[0007] Параметры качества изображения кодируются и передаются независимо от того, меняется ли параметр качества изображения. Если, для управления качеством изображения, сетчатые блоки подразделяются на меньшие модули, существует проблема непроизводительных затрат, вызываемых кодом параметра качества изображения.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

[0008] Настоящее изобретение направлено на устройство кодирования изображения, обеспечивающее возможность управления качеством изображения в модулях соответствующих блоков и способное уменьшать границы блоков с целью генерирования изображения, в котором данные границы являются менее заметными.

[0009] В соответствии с одним аспектом настоящего изобретения, устройство кодирования изображения, сконфигурированное с возможностью деления изображения на разделительные блоки множества размеров и выполнения кодирования упомянутого изображения при осуществлении управления качеством изображения в соответствии со значением параметра в модулях разделительных блоков, включает в себя модуль, сконфигурированный с возможностью получения размера блока для подлежащего кодированию целевого блока; модуль, сконфигурированный с возможностью получения минимального размера блока, используемого для управления упомянутым значением параметра; модуль, сконфигурированный с возможностью получения состояния разделения упомянутого целевого блока; модуль, сконфигурированный с возможностью получения значения параметра; модуль, сконфигурированный с возможностью определения, является ли целевой блок разделенным в соответствии с упомянутым состоянием разделения целевого блока; модуль, сконфигурированный с возможностью определения, является ли размер блока для целевого блока большим чем или равным минимальному размеру блока; модуль, сконфигурированный с возможностью определения, является ли размер блока для целевого блока равным минимальному размеру блока; и модуль, сконфигурированный с возможностью кодирования полученного значения параметра.

[0010] В соответствии с одним иллюстративным вариантом осуществления настоящего изобретения, возможно осуществлять управление качеством изображения в модулях соответствующих блоков и делать границы блоков меньше с целью генерирования изображения, где данные границы являются менее заметными. Поскольку нет необходимости вставлять код параметра управления качеством изображения во все ортогонально преобразованные блоки, объем кода параметров квантования не будет увеличиваться сверх необходимого.

[0011] Дополнительные признаки и аспекты настоящего изобретения станут очевидными из нижеследующего подробного описания иллюстративных вариантов осуществления со ссылкой на прилагаемые чертежи.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

[0012] Сопроводительные чертежи, включенные в и составляющие часть данной спецификации, иллюстрируют иллюстративные варианты осуществления, признаки, а также аспекты упомянутого изобретения и, вместе с описанием, служат для пояснения принципов упомянутого изобретения.

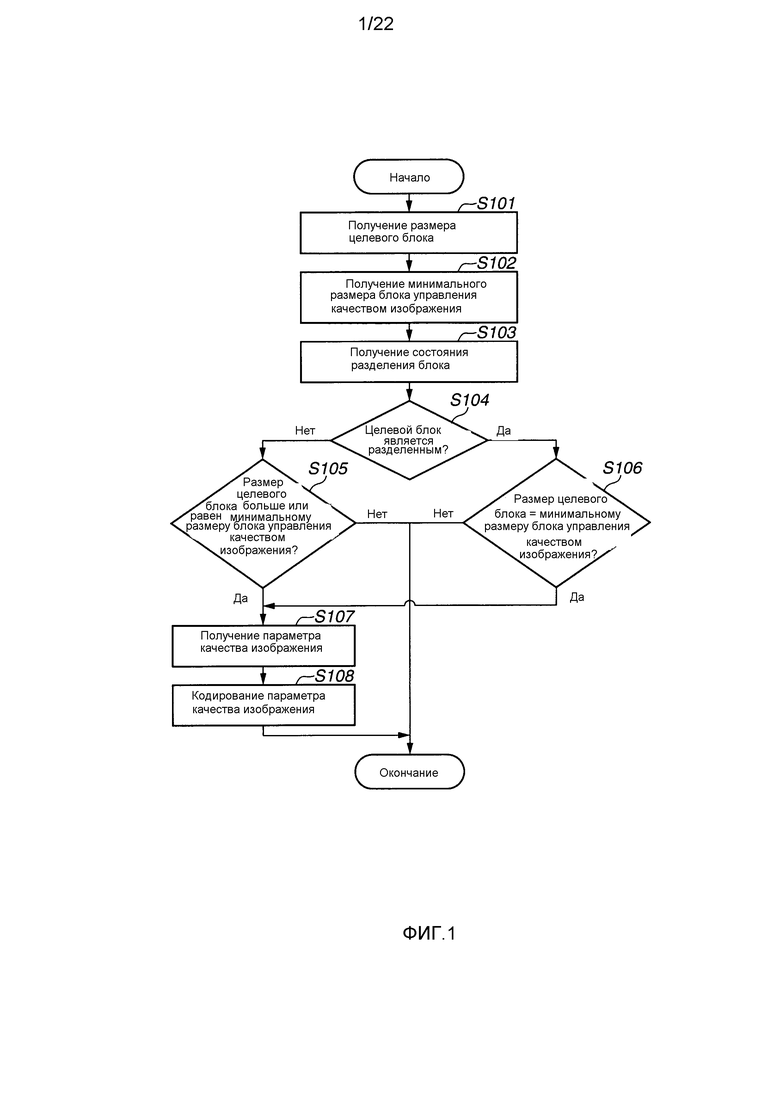

[0013] Фиг. 1 представляет собой блок-схему последовательности операций, иллюстрирующую способ кодирования параметра качества изображения в соответствии с первым иллюстративным вариантом осуществления настоящего изобретения.

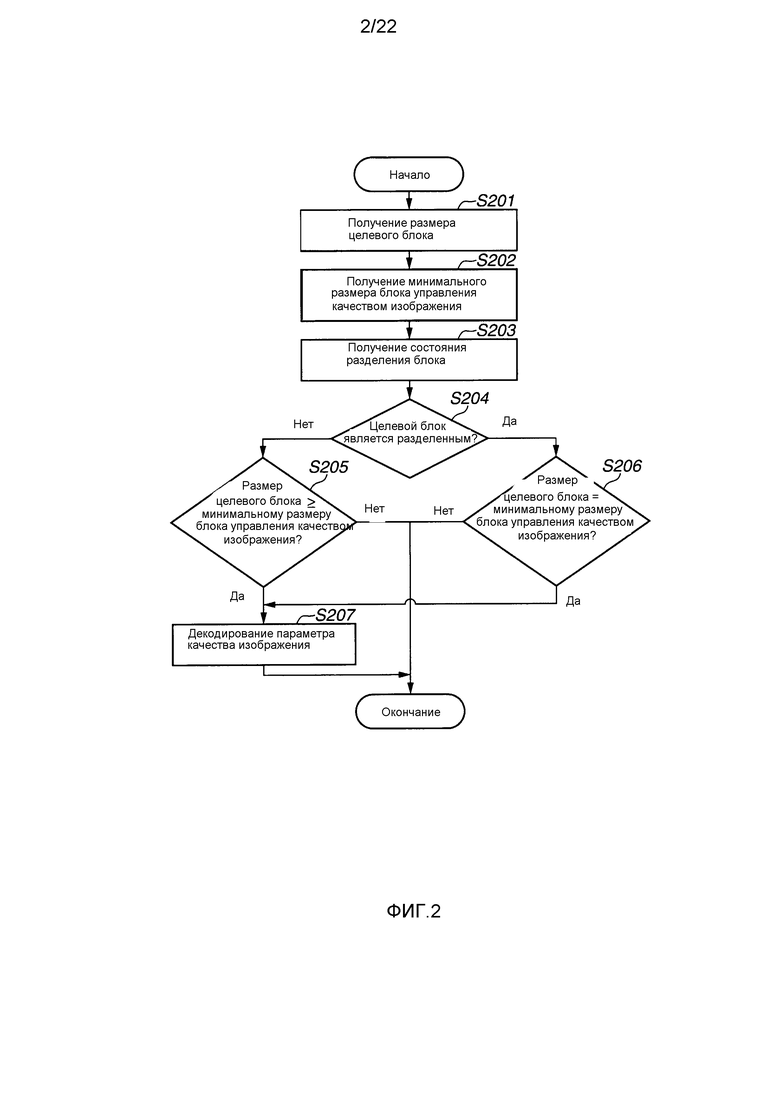

Фиг. 2 представляет собой блок-схему последовательности операций, иллюстрирующую способ декодирования параметра качества изображения в соответствии со вторым иллюстративным вариантом осуществления настоящего изобретения.

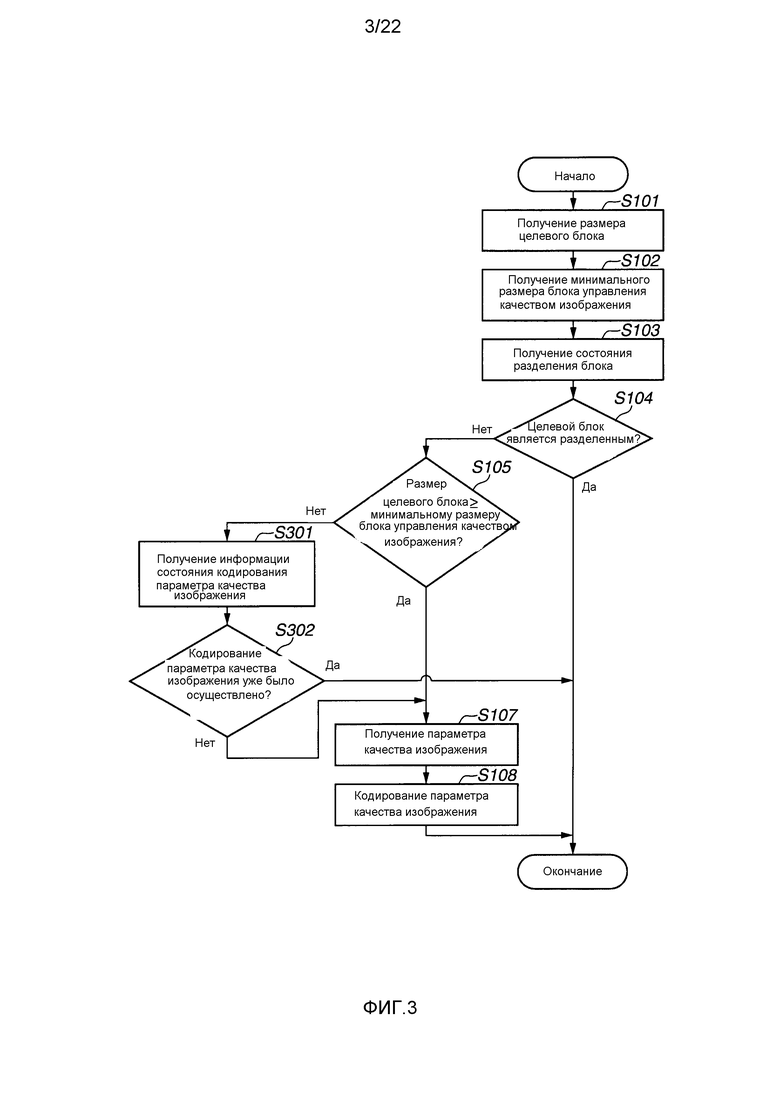

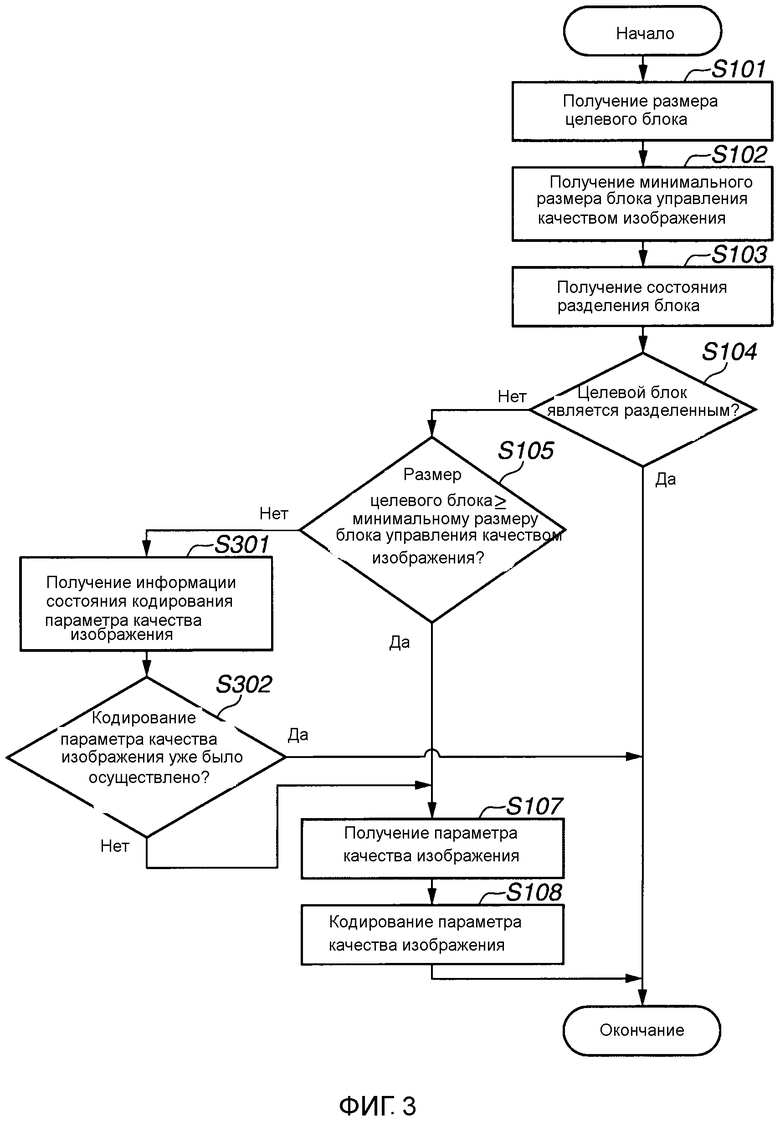

Фиг. 3 представляет собой блок-схему последовательности операций, иллюстрирующую способ кодирования параметра качества изображения в соответствии с третьим иллюстративным вариантом осуществления настоящего изобретения.

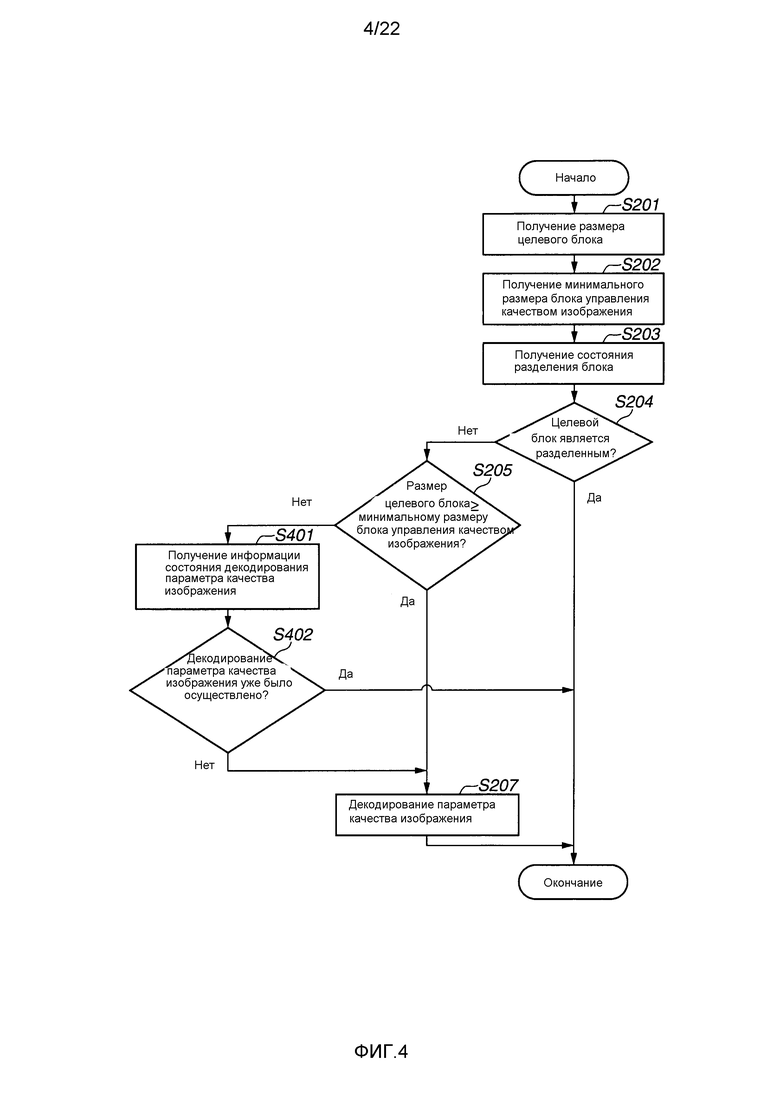

Фиг. 4 представляет собой блок-схему последовательности операций, иллюстрирующую способ декодирования параметра качества изображения в соответствии с четвертым иллюстративным вариантом осуществления настоящего изобретения.

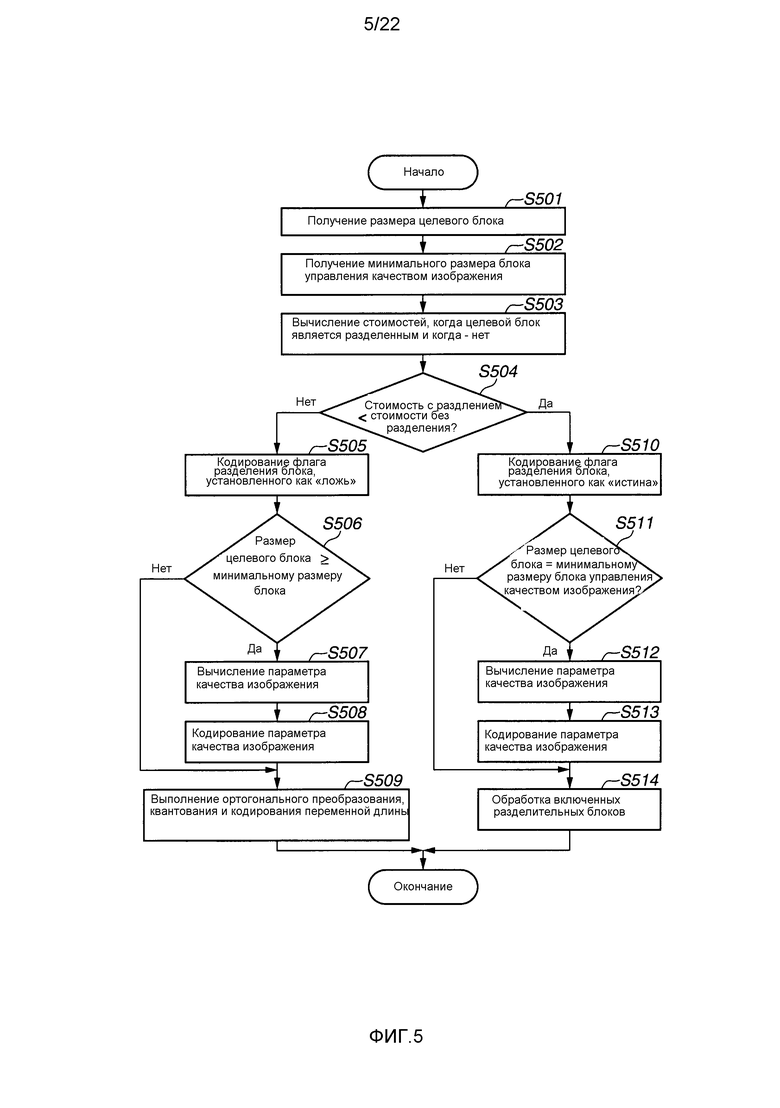

Фиг. 5 представляет собой блок-схему последовательности операций, иллюстрирующую способ кодирования параметра качества изображения в соответствии с пятым иллюстративным вариантом осуществления настоящего изобретения.

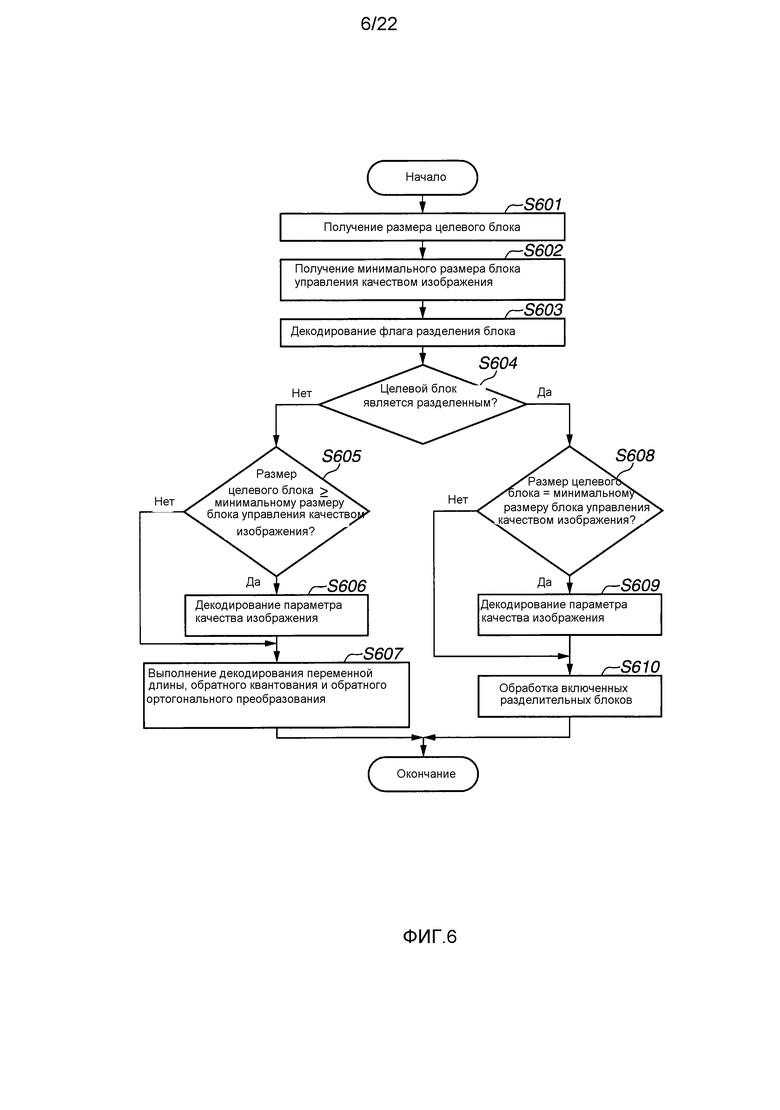

Фиг. 6 представляет собой блок-схему последовательности операций, иллюстрирующую способ декодирования параметра качества изображения в соответствии с шестым иллюстративным вариантом осуществления настоящего изобретения.

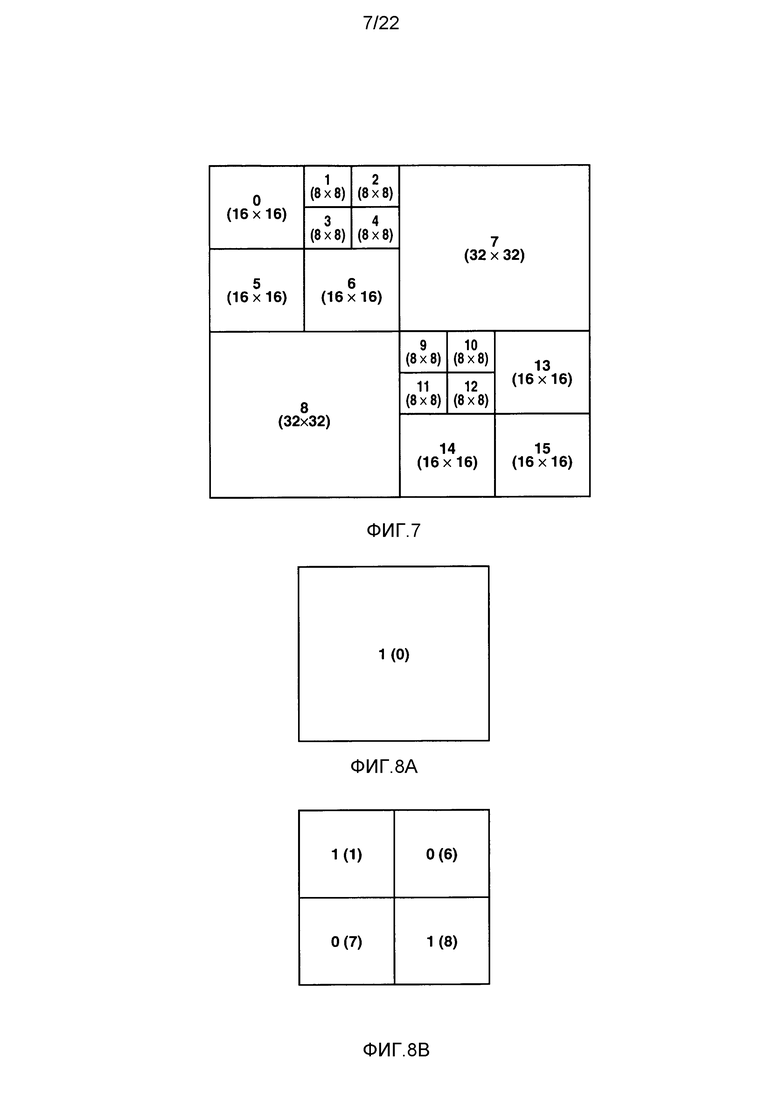

Фиг. 7 представляет собой диаграмму, иллюстрирующую пример разделенного сетчатого блока.

Фиг. 8A представляет собой диаграмму, иллюстрирующую пример разделения сетчатого блока и флаг разделения.

Фиг. 8B представляет собой диаграмму, иллюстрирующую пример разделения сетчатого блока и флаги разделения.

Фиг. 8C представляет собой диаграмму, иллюстрирующую пример разделения сетчатого блока и флаги разделения.

Фиг. 8D представляет собой диаграмму, иллюстрирующую пример разделения сетчатого блока и флаги разделения.

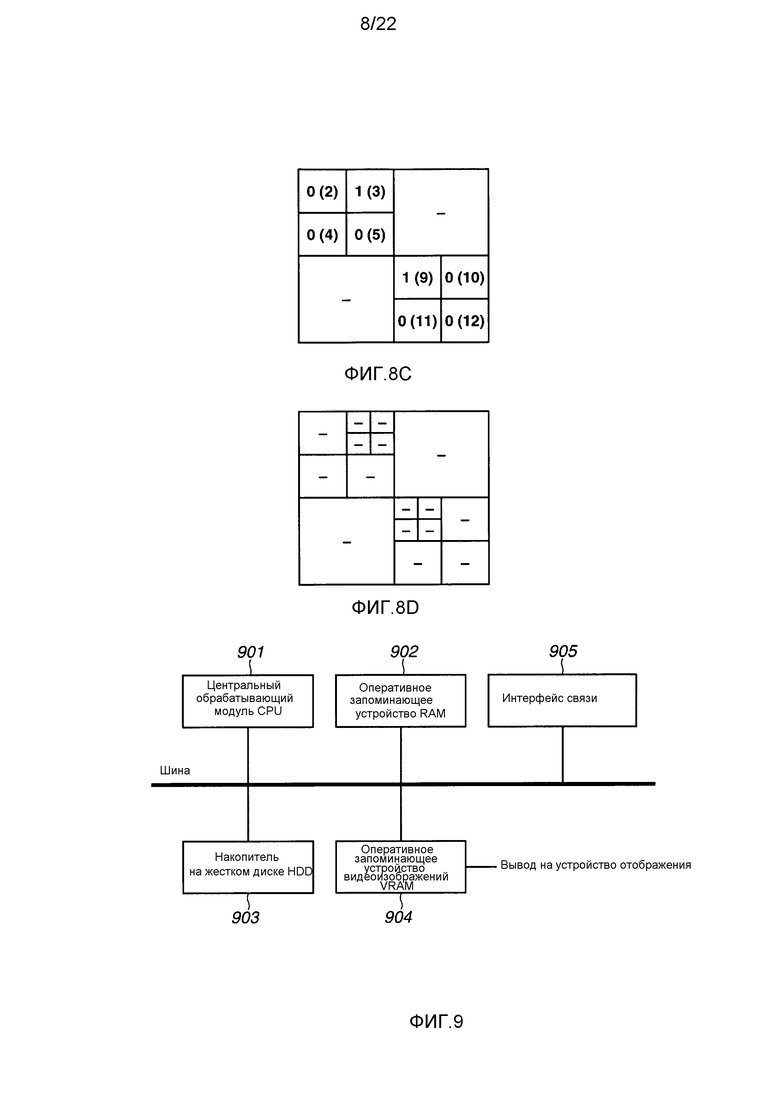

Фиг. 9 представляет собой диаграмму, иллюстрирующую пример конфигурации аппаратного оборудования для выполнения способа кодирования и способа декодирования в соответствии с одним иллюстративным вариантом осуществления настоящего изобретения.

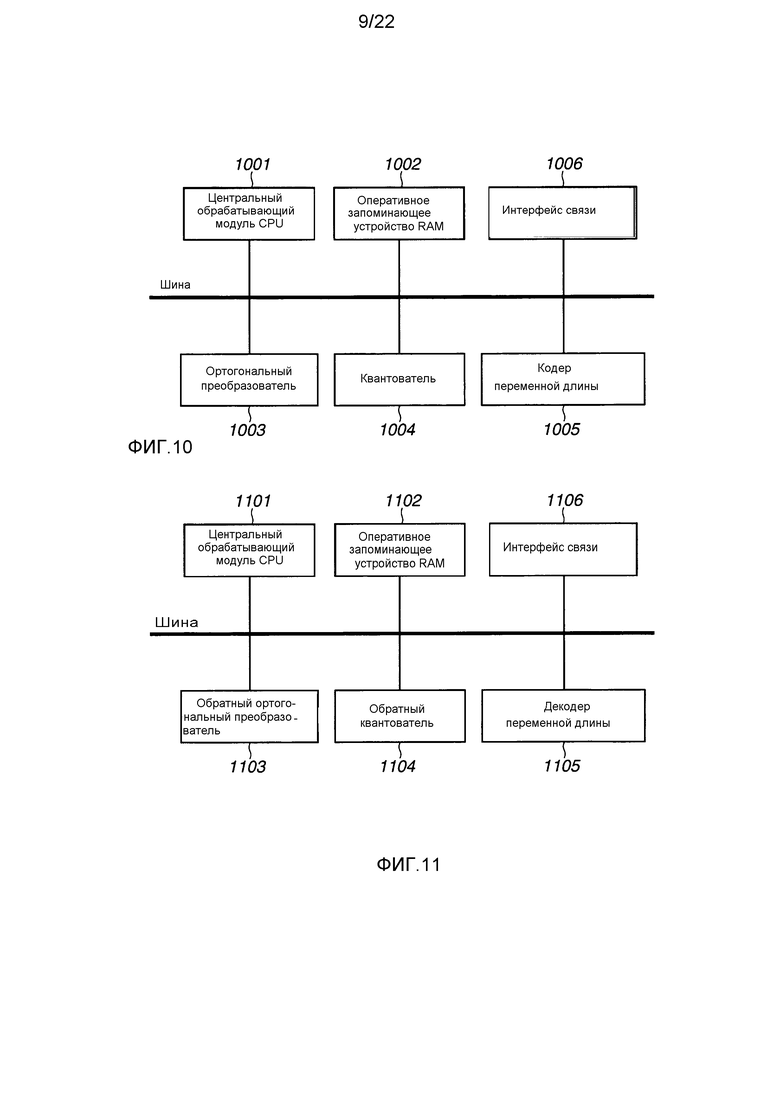

Фиг. 10 представляет собой диаграмму, иллюстрирующую пример конфигурации аппаратного оборудования для выполнения способа кодирования в соответствии с одним иллюстративным вариантом осуществления настоящего изобретения.

Фиг. 11 представляет собой диаграмму, иллюстрирующую пример конфигурации аппаратного оборудования для выполнения способа декодирования в соответствии с одним иллюстративным вариантом осуществления настоящего изобретения.

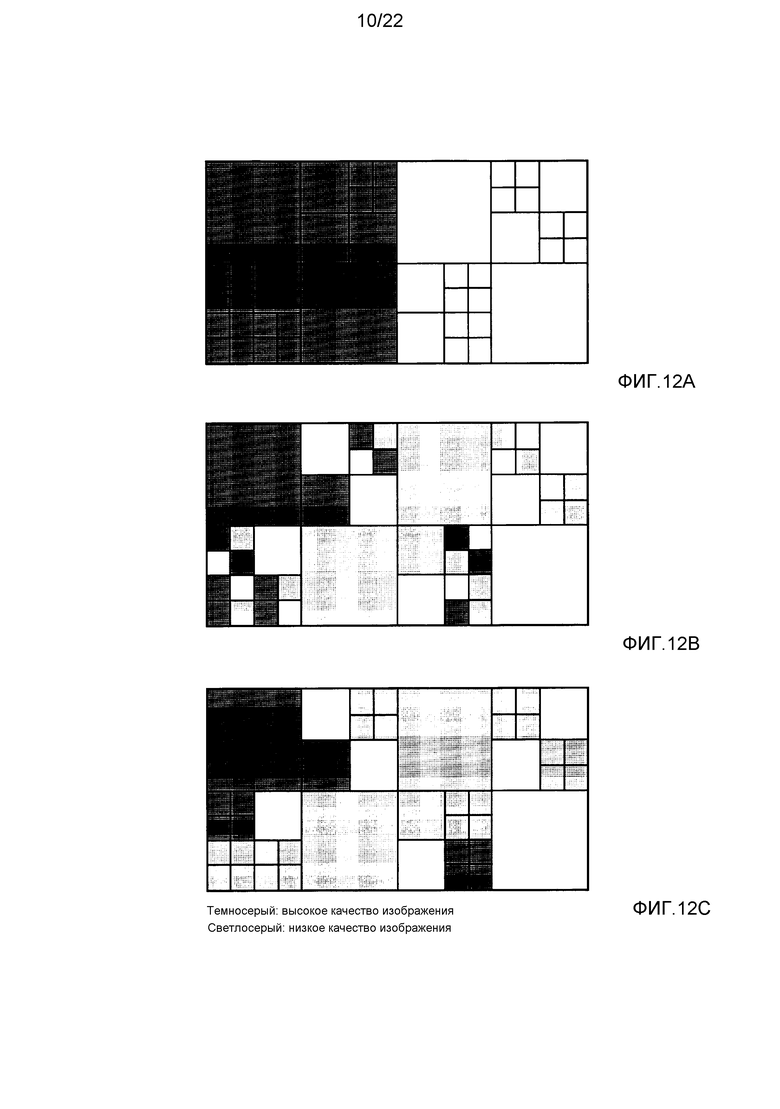

Фиг. 12A представляет собой диаграмму, иллюстрирующую пример управления качеством изображения в разделительных блоках.

Фиг. 12B представляет собой диаграмму, иллюстрирующую пример управления качеством изображения в разделительных блоках.

Фиг. 12C представляет собой диаграмму, иллюстрирующую пример управления качеством изображения в разделительных блоках.

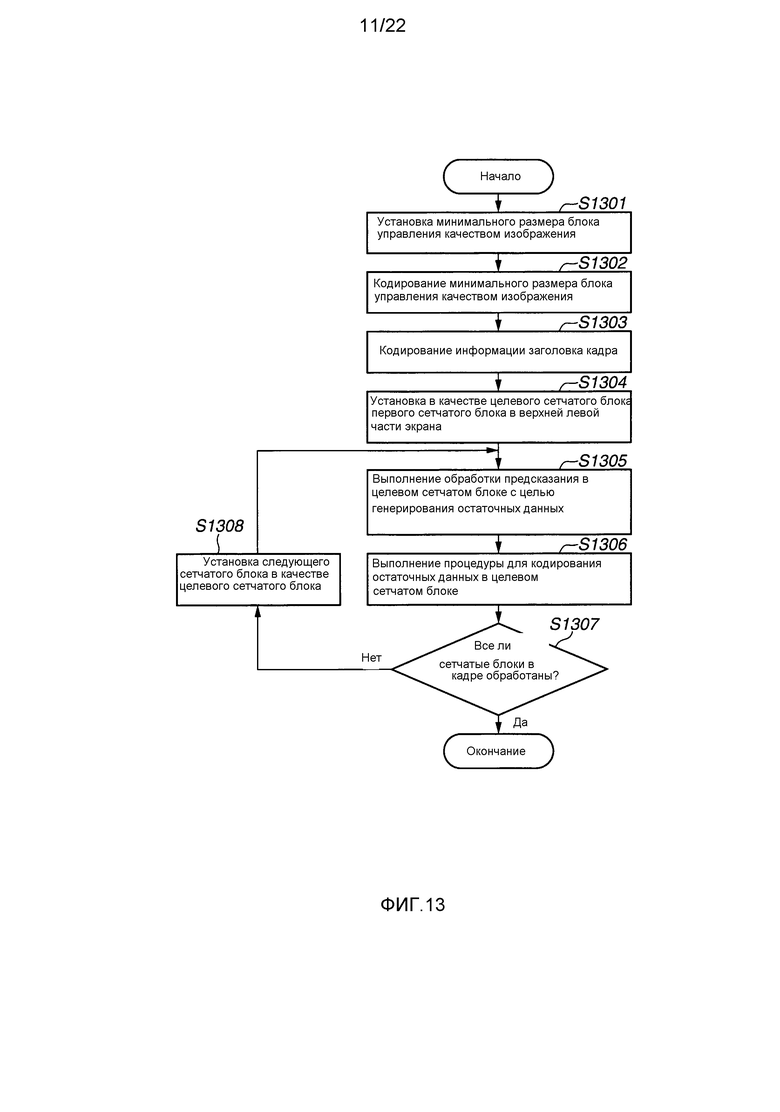

Фиг. 13 представляет собой блок-схему последовательности операций, иллюстрирующую способ обработки кодирования в кадре.

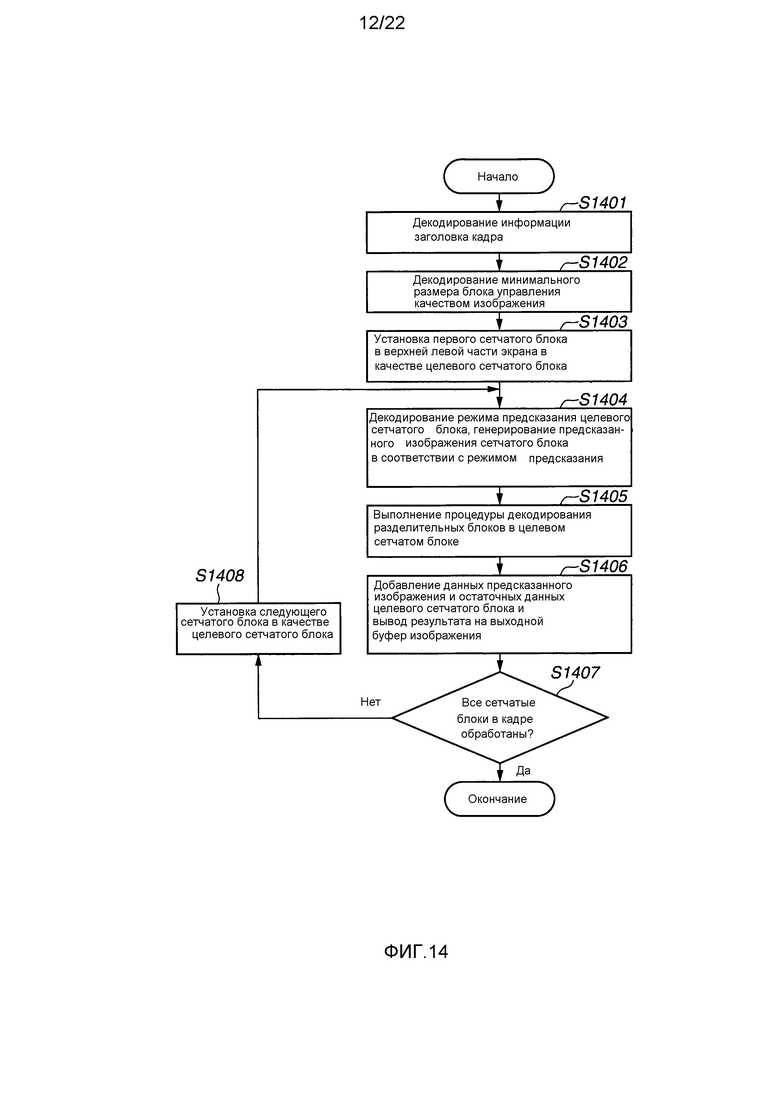

Фиг. 14 представляет собой блок-схему последовательности операций, иллюстрирующую способ обработки декодирования в кадре.

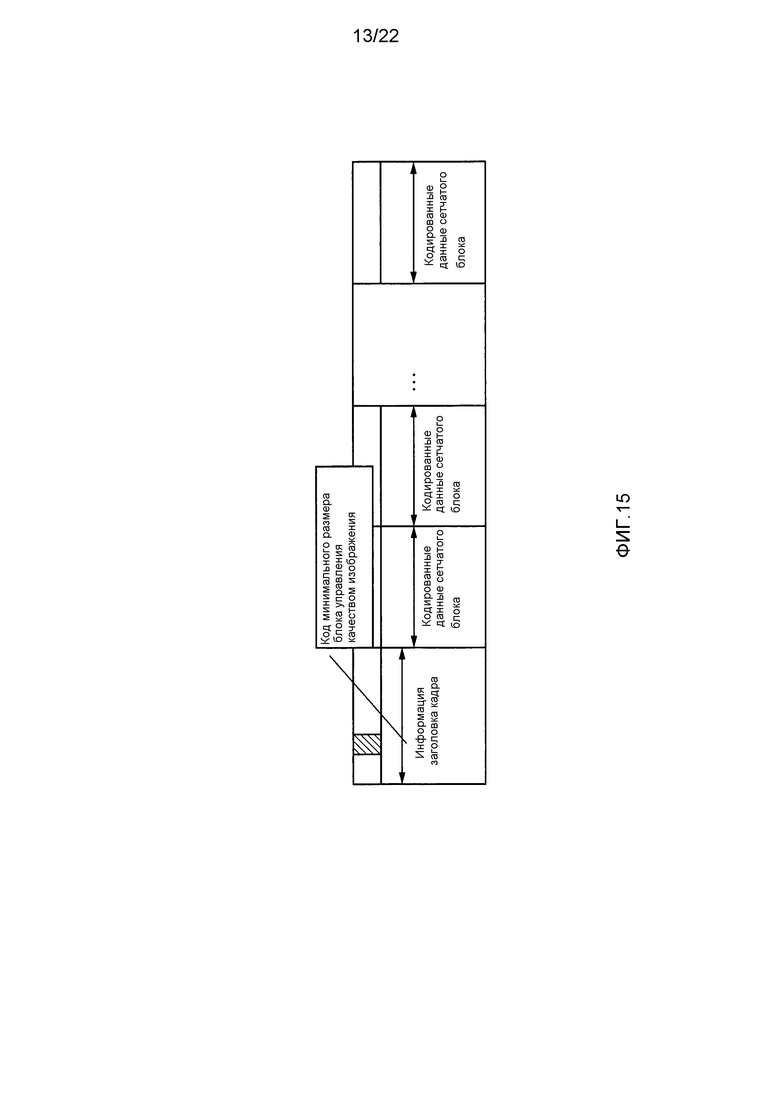

Фиг. 15 представляет собой диаграмму, иллюстрирующую структуру данных кодированного кадра.

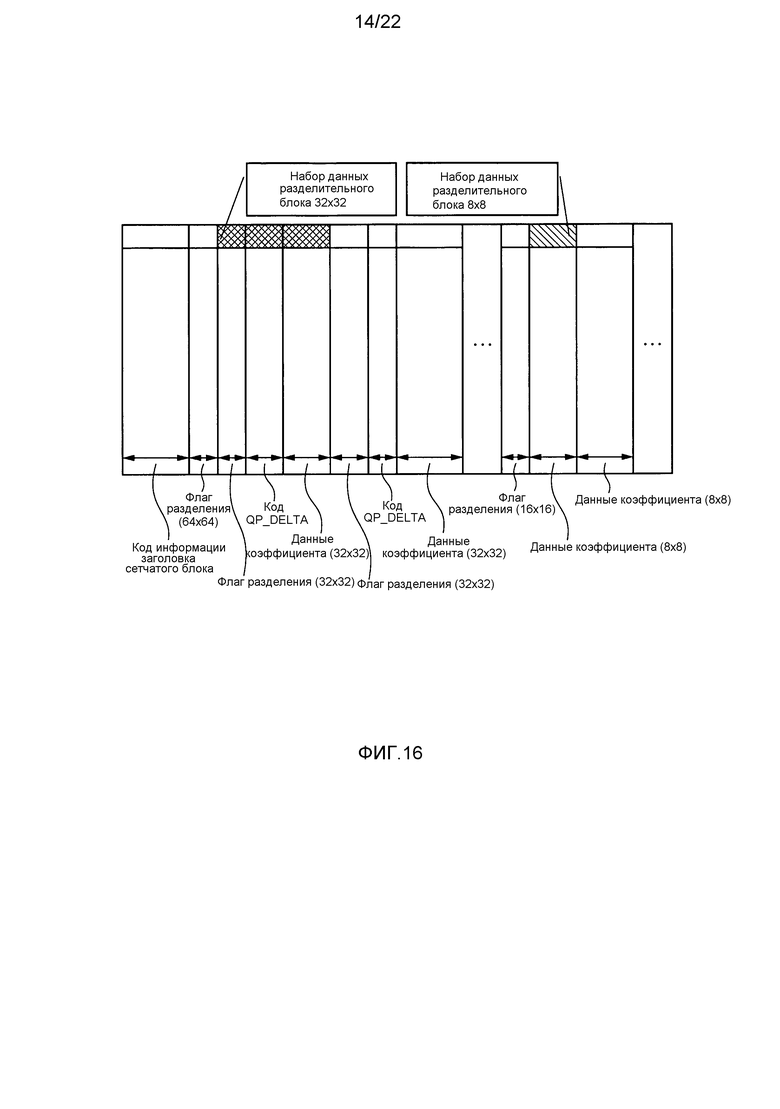

Фиг. 16 представляет собой диаграмму, иллюстрирующую структуру данных для кодированных данных в сетчатом блоке.

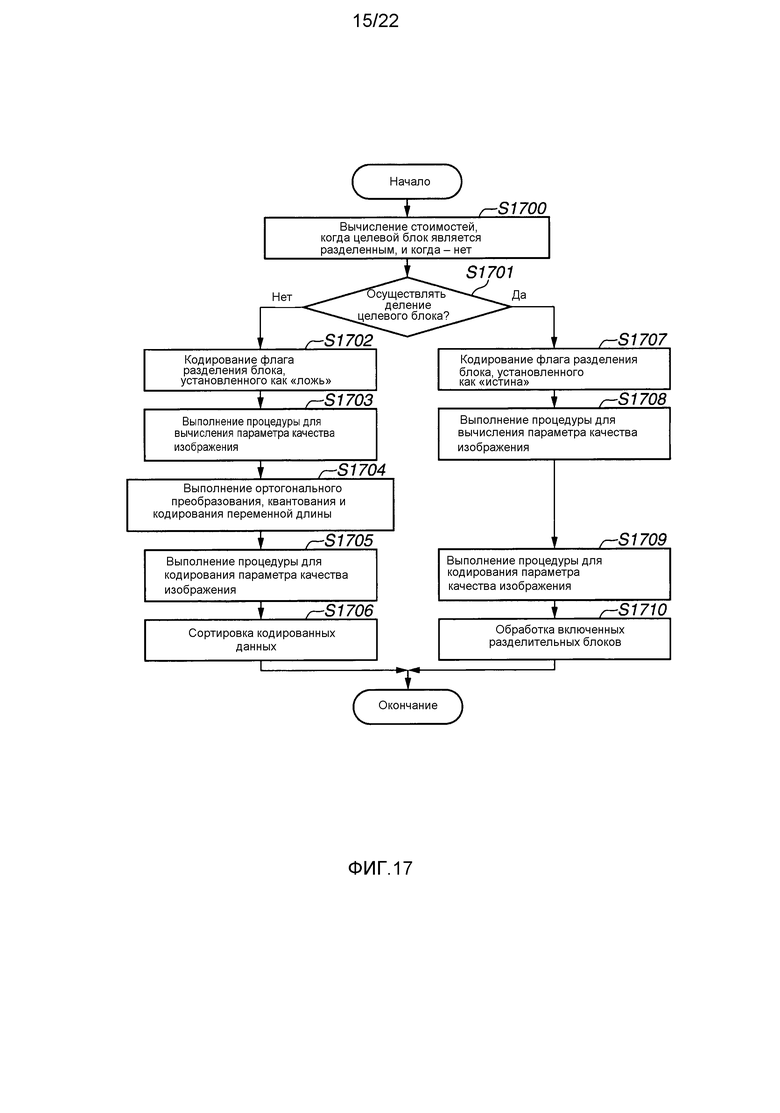

Фиг. 17 представляет собой блок-схему последовательности операций, иллюстрирующую подробности способа кодирования разделительных блоков.

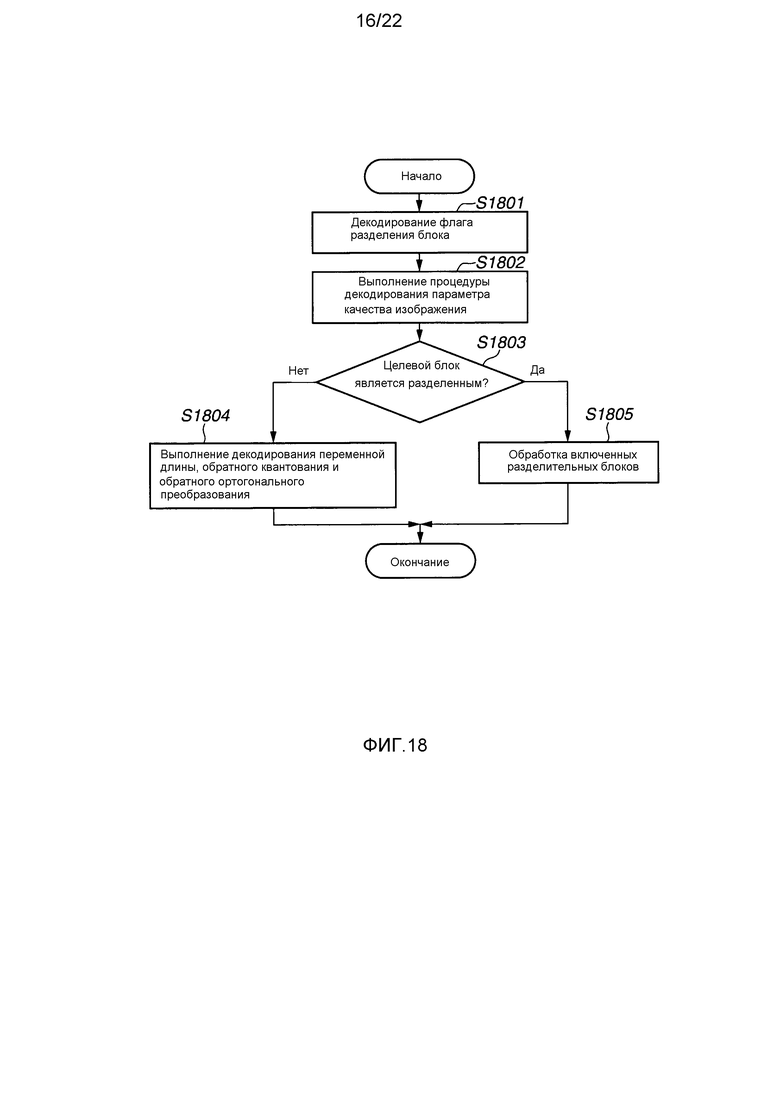

Фиг. 18 представляет собой блок-схему последовательности операций, иллюстрирующую подробности способа декодирования разделительных блоков.

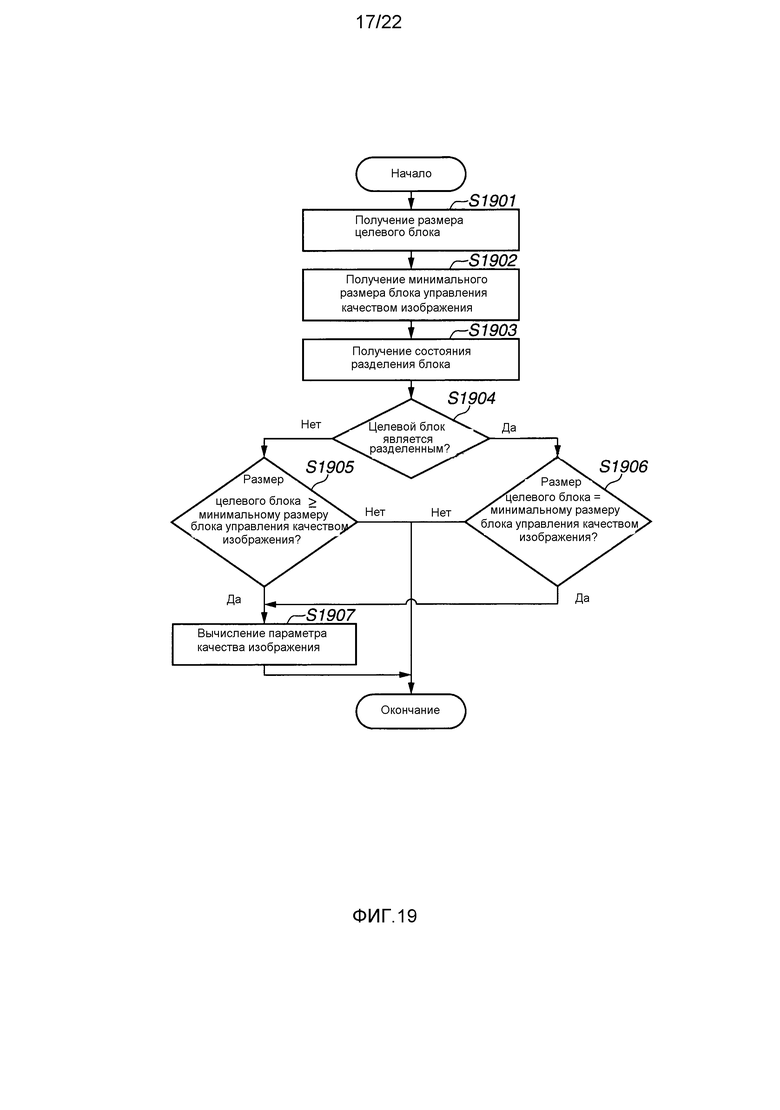

Фиг. 19 представляет собой блок-схему последовательности операций, иллюстрирующую способ вычисления параметра качества изображения в соответствии с первым иллюстративным вариантом осуществления.

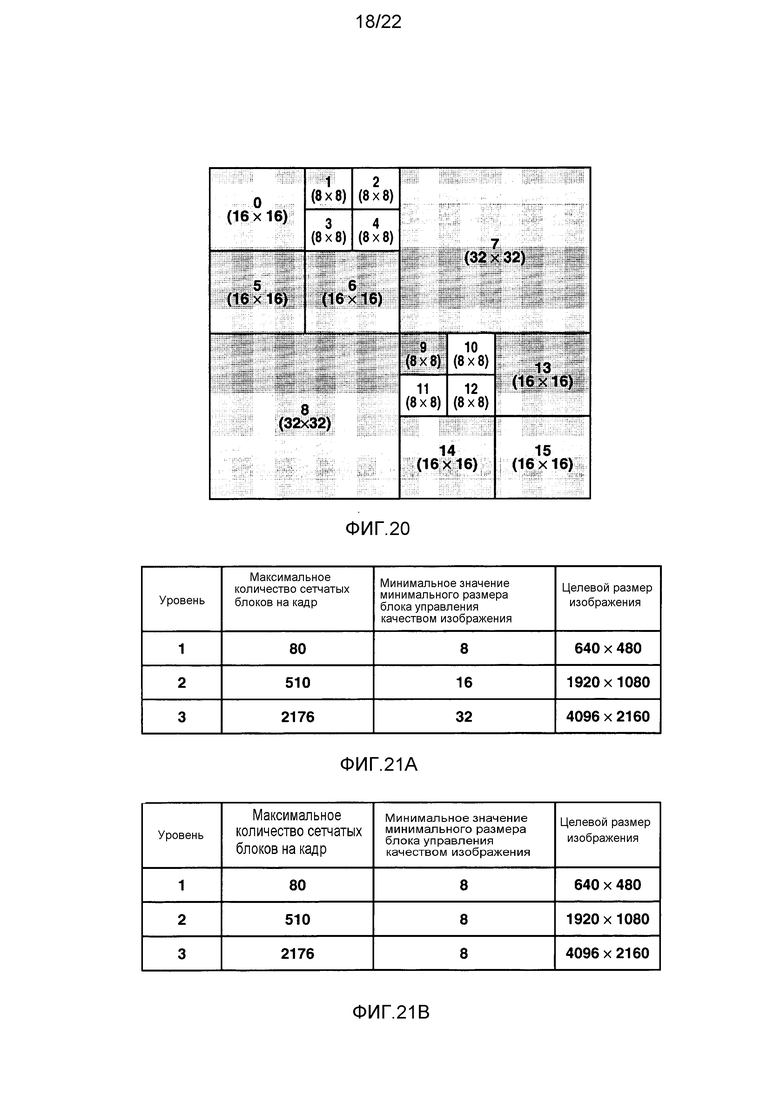

Фиг. 20 представляет собой диаграмму, иллюстрирующую разделительные блоки, подлежащие сопровождению посредством параметров квантования.

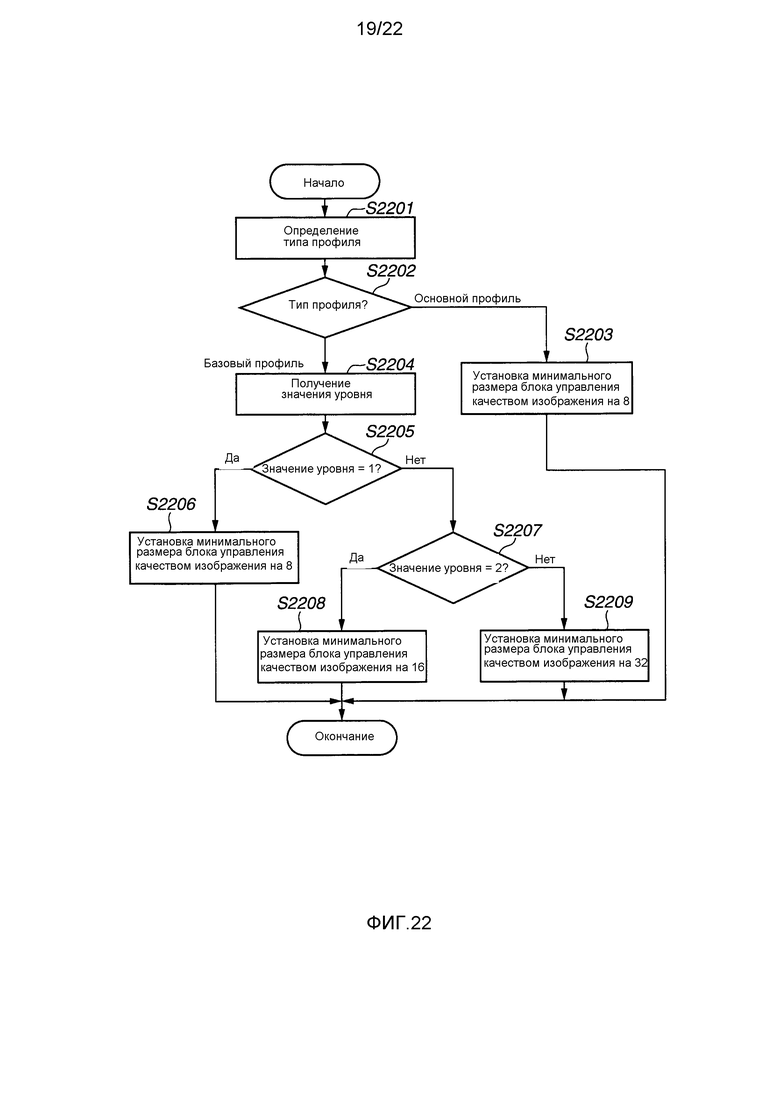

Фиг. 21A представляет собой диаграмму, иллюстрирующую отношение между профилем, уровнем и минимальным размером блока управления качеством изображения.

Фиг. 21B представляет собой диаграмму, иллюстрирующую отношение между профилем, уровнем и минимальным размером блока управления качеством изображения.

Фиг. 22 представляет собой блок-схему последовательности операций, иллюстрирующую процедуру для вычисления минимального размера блока управления качеством изображения.

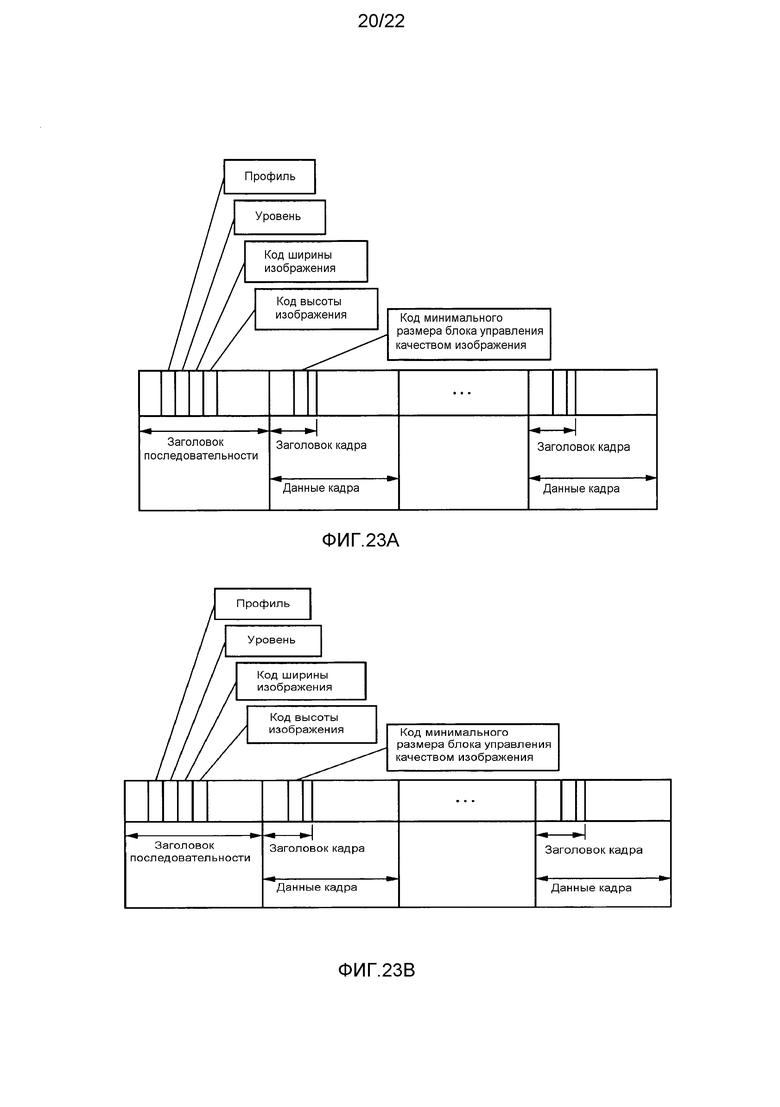

Фиг. 23A представляет собой диаграмму, иллюстрирующую структуру кодированных данных последовательности.

Фиг. 23B представляет собой диаграмму, иллюстрирующую структуру кодированных данных последовательности.

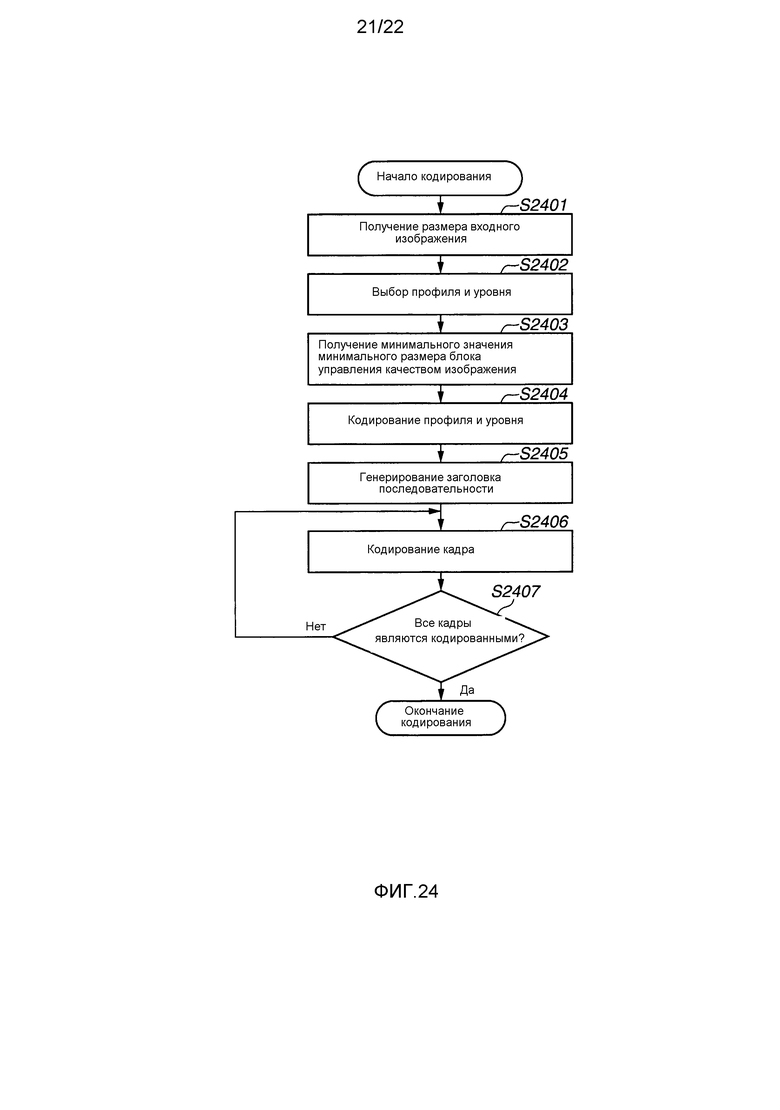

Фиг. 24 представляет собой блок-схему последовательности операций, иллюстрирующую способ кодирования изображения в соответствии с седьмым иллюстративным вариантом осуществления настоящего изобретения.

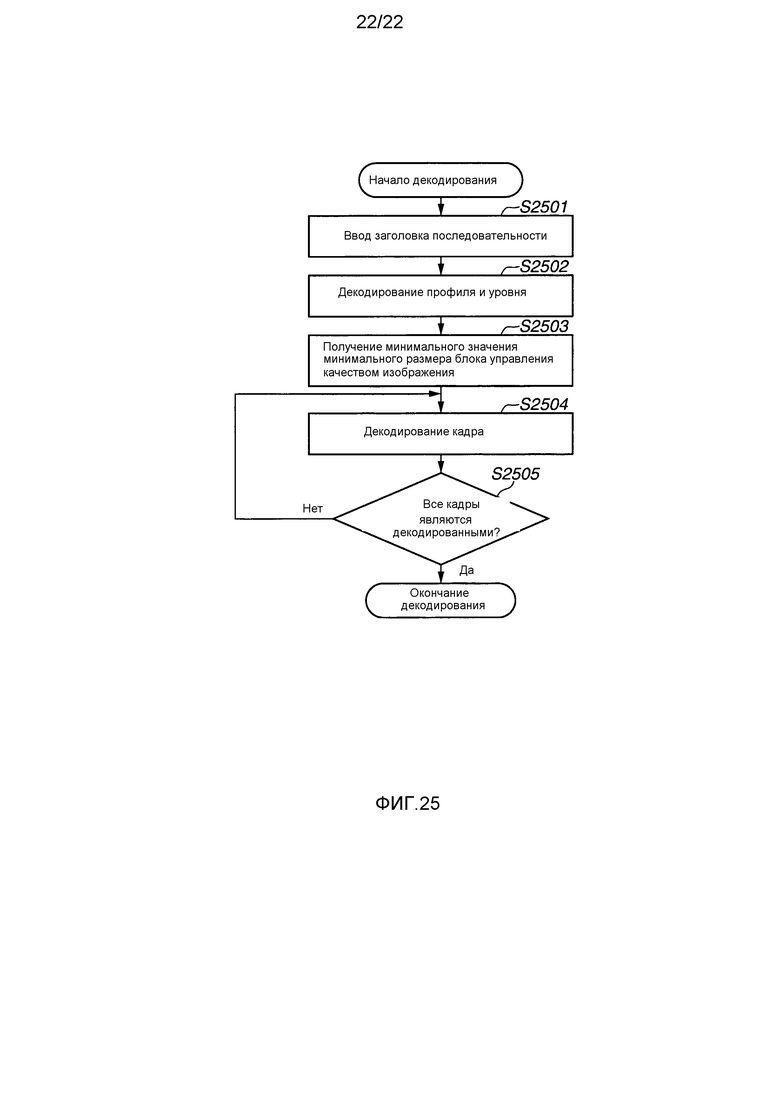

Фиг. 25 представляет собой блок-схему последовательности операций, иллюстрирующую способ декодирования изображения в соответствии с восьмым иллюстративным вариантом осуществления настоящего изобретения.

ПОДРОБНОЕ ОПИСАНИЕ ВАРИАНТОВ ОСУЩЕСТВЛЕНИЯ

[0014] Ниже, со ссылкой на чертежи, будут подробно описаны различные иллюстративные варианты осуществления, признаки, а также аспекты настоящего изобретения.

[0015] Способ кодирования разделительных блоков в соответствии с первым иллюстративным вариантом осуществления настоящего изобретения будет описан со ссылкой на фиг. 1, фиг. 9, фиг. 13, фиг. 17 и фиг. 19.

[0016] Фиг. 9 иллюстрирует конфигурацию для выполнения программы кодирования, включающей в себя способ кодирования в соответствии с настоящим иллюстративным вариантом осуществления. Данная программа кодирования записана на накопителе 903 на жестком диске (далее в настоящем документе, сокращенно указываемом как HDD). При активации программа кодирования загружается в оперативное запоминающее устройство (ОЗУ, RAM) 902. Центральный обрабатывающий модуль 901 (CPU) выполняет этапы, которые будут описаны ниже, с целью выполнения обработки кодирования изображения. В настоящем иллюстративном варианте осуществления входные данные изображения сохраняются в и считываются из накопителя 903 HDD. Выходные данные записываются на накопителе 903 HDD.

[0017] Далее будет описана операция кодирования по вышеизложенной конфигурации. Фиг. 13 представляет собой блок-схему последовательности операций, иллюстрирующую процедуру для кодирования всего кадра. Настоящий иллюстративный вариант осуществления рассматривает случай, когда экраны каждый делятся в сетчатой структуре на сетчатые блоки размером 64x64 пикселей и последовательно обрабатываются в модулях сетчатых блоков. Сетчатые блоки внутри экрана обрабатываются в растровом порядке сканирования. Следует отметить, что размер сетчатых блоков не ограничивается до 64.

[0018] На этапе S1301 модуль 901 CPU устанавливает минимальный размер блока управления качеством изображения. На этапе S1302 модуль 901 CPU осуществляет кодирование минимального размера блока управления качеством изображения. На этапе S1303 модуль 901 CPU осуществляет кодирование информации заголовка кадра. На этапе S1304 модуль 901 CPU устанавливает в качестве целевого сетчатого блока первый сетчатый блок в верхней левой части экрана. На этапе S1305 модуль 901 CPU выполняет обработку предсказания в целевом сетчатом блоке с целью генерирования остаточных данных. На этапе S1306 модуль 901 CPU выполняет процедуру для кодирования остаточных данных в целевом сетчатом блоке. На этапе S1307 модуль 901 CPU определяет, все ли сетчатые блоки в кадре обработаны. На этапе S1308 модуль 901 CPU устанавливает следующий сетчатый блок в качестве целевого сетчатого блока.

[0019] Ниже будет описана процедура этапов. На этапе S1301 модуль 901 CPU устанавливает параметр, называемый минимальным размером блока управления качеством изображения. Настоящий иллюстративный вариант осуществления будет описан с допущением, что управление качеством изображения осуществляется посредством параметра квантования, используемого для квантования коэффициентов ортогонального преобразования. Минимальный размер блока управления качеством изображения составляет 16x16 пикселей, так что информация минимального размера блока управления качеством изображения имеет значение 16. Однако упомянутое значение не ограничивается до 16. Разработчик программы может встраивать в программу фиксированное значение. Пользователь может специфицировать значение через посредство интерфейса пользователя программы. Сама программа может вычислять и устанавливать оптимальное значение. Программа может вычислять оптимальные значения в зависимости от входных изображений. Например, если входное изображение составляет более 640×480 пикселей, программа может устанавливать минимальный размер блока управления качеством изображения на значение, такое большое как 16. Если разрешение является более низким, чем или равным 640×480 пикселей, программа может устанавливать минимальный размер блока управления качеством изображения на значение, такое малое как 8.

[0020] На этапе S1302 модуль 901 CPU осуществляет кодирование минимального размера блока управления качеством изображения, установленного на этапе S1301 с целью генерирования кода минимального размера блока управления качеством изображения. Например, модуль 901 CPU может обеспечивать индекс, выражающий информацию минимального размера блока управления качеством изображения 64 как «0», и, схожим образом, информацию 32, 16 и 8 как, соответственно, «1», «2» и «3». Затем модуль 901 CPU может генерировать код фиксированной длины, представляющий собой индекс.

[0021] На этапе S1303 модуль 901 CPU осуществляет генерирование и кодирование информации заголовка кадра. Модуль 901 CPU включает в себя код минимального размера блока управления качеством изображения, сгенерированный на этапе S1302, как часть информации заголовка кадра. Следует отметить, что, в то время как настоящий иллюстративный вариант осуществления рассматривает случай, в котором код минимального размера блока управления качеством изображения включен в заголовок кадра, это не является ограничением. Код минимального размера блока управления качеством изображения может быть включенным в последовательность, в картинку, срез или блок наиболее высокого иерархического уровня.

[0022] На этапе S1304 модуль 901 CPU устанавливает сетчатый блок в верхней левой части экрана в качестве первого целевого сетчатого блока, назначенного к обработке.

[0023] На этапе S1305 модуль 901 CPU генерирует предсказанное изображение посредством использования внутрикадрового предсказания и предсказания компенсации движения, а также генерирует остаточные данные из пикселей целевого сетчатого блока. Внутрикадровое предсказание включает в себя генерирование предсказанного изображения посредством обращения к зоне в окрестности целевого сетчатого блока. Предсказание компенсации движения включает в себя генерирование предсказанного изображения посредством обращения к пикселям в других кадрах. Примеры включают в себя внутреннее предсказание и предсказание компенсации движения, принятые в упомянутой ранее схеме кодирования стандарта H.264. Модуль 901 CPU осуществляет кодирование режима внутрикадрового предсказания, и/или сгенерированных векторов движения, и выдает результат на выходной буфер в качестве кода информации заголовка сетчатого блока.

[0024] На этапе S1306 модуль 901 CPU выполняет, в целевом сетчатом блоке, процедуру для кодирования остаточных данных в блоке, которая будет описана в совокупности с фиг. 17. Фиг. 17 будет подробно описана ниже.

[0025] На этапе S1307 модуль 901 CPU определяет, все ли сетчатые блоки в кадре обработаны. Если обработаны все сетчатые блоки («ДА» на этапе S1307), модуль 901 CPU заканчивает обработку кодирования во всем кадре. Если еще не все сетчатые блоки обработаны («НЕТ» на этапе S1307), модуль 901 CPU выполняет этап S1308.

[0026] На этапе S1308 модуль 901 CPU устанавливает следующий сетчатый блок в растровом порядке сканирования в качестве целевого сетчатого блока и возвращается к этапу S1305.

[0027] Фиг. 17 представляет собой подробную блок-схему последовательности операций этапа S1306. На этапе S1306 модуль 901 CPU осуществляет кодирование множества иерархически структурированных блоков ортогонального преобразования различных размеров с целью генерирования кодированных данных, включающих в себя код параметра управления качеством изображения. В конкретном плане модуль 901 CPU выполняет деление блока, ортогональное преобразование, а также квантование на основе минимального размера блока управления качеством изображения, данных размера блока, а также остаточных данных в блоках. Блок-схема последовательности операций также иллюстрирует обработку для кодирования разделительных блоков с целью генерирования кода флага разделения блока, кодированных данных коэффициента, а также кода QP_DELTA, относящегося к обновлению параметра качества изображения. Настоящий иллюстративный вариант осуществления использует, для иерархического структурирования, структуру дерева квадрантов, разбивающего пространство. Блоки на наиболее высоком иерархическом уровне представляют собой сетчатые блоки размером 64×64 пикселей. По мере того, как уровень снижается посредством обработки разделения, могут обрабатываться блоки размером 32×32 пикселей, 16×16 пикселей и такие малые, как блоки размером 8×8 пикселей. Структура деления блока на основе дерева квадрантов, разбивающего пространство, может передаваться на сторону декодера посредством флагов разделения блока, встраиваемых в поток.

[0028] На этапе S1700 модуль 901 CPU вычисляет стоимости, когда целевой блок является разделенным и когда - нет. На этапе S1701 модуль 901 CPU определяет, осуществлять ли деление целевого блока. На этапе S1702 модуль 901 CPU осуществляет кодирование флага разделения блока, установленного как «ложь», и выдает результат. На этапе S1703 модуль 901 CPU выполняет процедуру для вычисления параметра качества изображения. На этапе S1704 модуль 901 CPU выполняет ортогональное преобразование, квантование, а также кодирование переменной длины. На этапе S1705 модуль 901 CPU выполняет процедуру для кодирования параметра качества изображения. На этапе S1706 модуль 901 CPU сортирует кодированные данные и выдает результат на выходной буфер. На этапе S1707 модуль 901 CPU осуществляет кодирование флага разделения блока, установленного как «истина», и выдает результат. На этапе S1708 модуль 901 CPU выполняет процедуру для вычисления параметра качества изображения. На этапе S1709 модуль 901 CPU выполняет процедуру для кодирования параметра качества изображения. На этапе S1710 модуль 901 CPU осуществляет обработку включенных разделительных блоков.

[0029] Ниже будет описана процедура этапов. На этапе S1700 модуль 901 CPU вычисляет стоимости, когда целевой блок является разделенным и когда - нет. Данные стоимости могут вычисляться посредством использования упомянутых выше множителей Лагранжа, а также характеристик изображения, статистических данных и предсказанных длин кода.

[0030] На этапе S1701 модуль 901 CPU сравнивает стоимости с делением и без деления, вычисленные на этапе S1700. Если стоимость с делением блока является более низкой, чем стоимость без деления блока («ДА» на этапе S1701), модуль 901 CPU определяет сравнение как «истина». Если нет («НЕТ» на этапе S1701), модуль 901 CPU определяет сравнение как «ложь». Если результат определения на этапе S1701 составляет «ложь» («НЕТ» на этапе S1701), модуль 901 CPU выполняет этапы от S1702 по этап S1706. Если результат определения на этапе S1701 составляет «истина» («ДА» на этапе S1701), модуль 901 CPU выполняет этапы от S1707 по этап S1710.

[0031] Вначале будет дано описание случая, когда стоимость является более низкой без деления блока. На этапе S1702 модуль 901 CPU осуществляет кодирование флага разделения блока, установленного как «ложь». Модуль 901 CPU обычно назначает и кодирует, хотя неограниченно, однобитовое значение 0.

[0032] На этапе S1703 модуль 901 CPU выполняет процедуру вычисления параметра качества изображения, проиллюстрированную на фиг. 19, с целью вычисления параметра качества изображения. Фиг. 19 будет подробно описана ниже.

[0033] На этапе S1704 модуль 901 CPU выполняет ортогональное преобразование, квантование, а также кодирование переменной длины остаточных данных с целью генерирования кодированных данных коэффициента. Ортогональное преобразование осуществляется посредством дискретного косинусного преобразования (ДКП, DCT). Квантование выполняется посредством использования параметра качества изображения, вычисленного на этапе S1703. Модуль 901 CPU выполняет квантование посредством использования такого же самого значения параметра качества изображения, что и значение, использованное для предыдущего квантования, если, посредством процедуры вычисления параметра качества изображения, проиллюстрированной на фиг. 19, назначенной к описанию ниже, не является вычисленным никакой новый параметр качества изображения. Для кодирования переменной длины модуль 901 CPU может использовать кодирование по алгоритму Хаффмана и арифметическое кодирование. Такие методы кодирования могут осуществляться посредством использования способов, схожих со способами стандарта H.264, упомянутыми ранее.

[0034] На этапе S1705 модуль 901 CPU выполняет процедуру кодирования параметра качества изображения. Процедура кодирования параметра качества изображения будет подробно описана ниже со ссылкой на фиг. 1.

[0035] На этапе S1706 модуль 901 CPU осуществляет сортировку кода флага разделения блока, кода QP_DELTA, а также кодированных данных коэффициента, и выдает результат на выходной буфер в этом порядке. Если для выдачи в наличии не имеется кодированных данных, модуль 901 CPU осуществляет сортировку и выдает только существующие кодированные данные. Фиг. 16 иллюстрирует пример порядка кода.

[0036] Далее будет дано описание случая, когда стоимость является более низкой с делением блока. На этапе S1707 модуль 901 CPU осуществляет кодирование флага разделения блока, установленного как «истина». Модуль 901 CPU обычно назначает и кодирует, хотя не ограниченно, однобитовое значение 1.

[0037] На этапе S1708 модуль 901 CPU выполняет процедуру вычисления параметра качества изображения, проиллюстрированную на фиг. 19, назначенную к описанию ниже, вычисляя тем самым параметр качества изображения.

[0038] На этапе S1709 модуль 901 CPU выполняет процедуру кодирования параметра качества изображения как на этапе S1705. Процедура кодирования параметра качества изображения будет подробно описана ниже со ссылкой на фиг. 1.

[0039] На этапе S1710 модуль 901 CPU рекурсивно выполняет настоящую процедуру во всех включенных разделительных блоках, то есть в четырех разделительных блоках (верхнем слева, верхнем справа, нижнем слева и нижнем справа), включенных в иерархически последовательный уровень. Данные разделительные блоки каждый имеют размер 1/2 от размера исходного целевого блока как по высоте, так и по ширине. Размер целевого блока уменьшается от разделения к разделению. Рекурсивная обработка может выполняться вплоть до блока такого малого размера, как 8×8 пикселей. Посредством такой рекурсивной обработки сетчатый блок успешно делится на структуру дерева квадрантов, разбивающего пространство. Например, предположим, что сетчатый блок является разделенным как проиллюстрировано на фиг. 7. Флаг разделения для обозначения наличия или отсутствия деления блока будет обозначаться посредством 1, когда соответствующий блок является разделенным, и 0, когда нет. Флаги разделения в соответствующих разделительных блоках затем выражаются как проиллюстрировано на фиг. 8A, фиг. 8B, фиг. 8C и фиг. 8D. Фиг. 8A, фиг. 8B, фиг. 8C и фиг. 8D иллюстрируют уровни и блоки размером 64×64 пикселей, 32×32 пикселя, 16×16 пикселей и 8×8 пикселей, соответственно. Цифры обозначают флаги разделения. «-» обозначает, что нет необходимости ни в одном флаге. Цифры в скобках обозначают структурный порядок. В настоящем иллюстративном варианте осуществления структурным порядком именуется порядок верхнего слева, верхнего справа, нижнего слева и нижнего справа с точки зрения блоков. С точки зрения уровней, структурным порядком именуется порядок сканирования вперед структуры дерева квадрантов, разбивающего пространство. Наборы из кода флага разделения, кода QP_DELTA и кодированных данных коэффициента сохраняются в структурном порядке. В блоках размером 8×8 пикселей не устанавливается никакого флага разделения, поскольку такие блоки далее делиться не будут. Блок, имеющий флаг разделения 1, сам не содержит никаких данных коэффициента, поскольку такой блок подразделяется на разделительные блоки меньших размеров, содержащие данные коэффициента. Как проиллюстрировано на фиг. 16, назначенной к описанию ниже, поток имеет такую структуру данных, что части кодированной информации в соответствующих разделительных блоках располагаются в структурном порядке. Часть кодированной информации по каждому разделительному блоку включает в себя набор из кода флага разделения, кода QP_DELTA и/или данных коэффициента по разделительному блоку.

[0040] Фиг. 1 представляет собой подробную блок-схему последовательности операций процедуры кодирования параметра качества изображения, выполняемой на этапе S1705 и на этапе S1709. На этапе S101 модуль 901 CPU получает размер целевого блока. На этапе S102 модуль 901 CPU получает минимальный размер блока управления качеством изображения. На этапе S103 модуль 901 CPU получает состояние разделения блока. На этапе S104 модуль 901 CPU определяет, является ли целевой блок разделенным. На этапе S105 модуль 901 CPU определяет, является ли размер целевого блока большим, чем или равным минимальному размеру блока управления качеством изображения. На этапе S106 модуль 901 CPU определяет, является ли размер целевого блока равным минимальному размеру блока управления качеством изображения. На этапе S107 модуль 901 CPU получает параметр качества изображения. На этапе S108 модуль 901 CPU осуществляет кодирование параметра качества изображения.

[0041] Ниже будет описана процедура этапов. На этапе S101 модуль 901 CPU получает размер целевого блока. Сразу же после того, как настоящая процедура запускается от процедуры по фиг. 17, назначенный к обработке целевой блок сам по себе представляет собой сетчатый блок. Значение размера целевого блока, таким образом, составляет 64. По мере того, как уровень структуры дерева квадрантов, разбивающего пространство, последовательно снижается по причине рекурсивных вызовов, значение размера изменяется на 32, 16 и 8.

[0042] На этапе S102 модуль 901 CPU получает минимальный размер блока управления качеством изображения, установленный извне. В настоящем иллюстративном варианте осуществления значение минимального размера блока управления качеством изображения составляет 16. Является ли подлежащий кодированию целевой блок разделенным, было определено на этапе S1700 и на этапе S1701 по фиг. 17. На этапе S103 модуль 901 CPU получает информацию состояния разделения, обозначающую результат определения разделения.

[0043] На этапе S104 модуль 901 CPU обращается к полученному состоянию разделения целевого блока и определяет, является ли целевой блок разделенным. Если целевой блок является разделенным («ДА» на этапе S104), модуль 901 CPU выполняет этап S106. Если целевой блок не является разделенным («НЕТ» на этапе S104), модуль 901 CPU выполняет этап S105.

[0044] На этапе S105 модуль 901 CPU определяет, является ли размер целевого блока большим чем или равным минимальному размеру блока управления качеством изображения. Если размер целевого блока определяется как являющийся большим или равным («ДА» на этапе S105), модуль 901 CPU выполняет этап S107 и последующий этап. Если нет («НЕТ» на этапе S105), модуль 901 CPU заканчивает обработку кодирования параметра качества изображения.

[0045] На этапе S106 модуль 901 CPU определяет, является ли размер целевого блока равным минимальному размеру блока управления качеством изображения. Если размер целевого блока определяется как являющийся равным минимальному размеру блока управления качеством изображения («ДА» на этапе S106), модуль 901 CPU выполняет этап S107 и этап S108. Если нет («НЕТ» на этапе S108), модуль 901 CPU заканчивает обработку кодирования параметра качества изображения.

[0046] На этапе S107 модуль 901 CPU получает параметр качества изображения. Упомянутый параметр качества изображения представляет собой параметр, определенный на этапе S1703 или на этапе S1708 по фиг. 17. На этапе S108 модуль 901 CPU осуществляет кодирование параметра качества изображения. В настоящем иллюстративном варианте осуществления модуль 901 CPU определяет значение разности между параметром качества изображения, использованным для кодирования предыдущего блока, и параметром качества изображения, полученным на этапе S107, как значение QP_DELTA. Модуль 901 CPU осуществляет кодирование, посредством кодирования Голомба, определенного значения QP_DELTA в код QP_DELTA, представляющий собой код параметра качества изображения. В настоящем иллюстративном варианте осуществления кодирование QP_DELTA осуществляется посредством кодирования Голомба. Однако это не является ограничением. Кодирование QP_DELTA может осуществляться посредством арифметического кодирования или другого кодирования переменной длины. Параметр качества изображения используется для вычисления следующего значения QP_DELTA.

[0047] Фиг. 19 представляет собой подробную блок-схему последовательности операций процедуры вычисления параметра качества изображения, выполняемой на этапе S1703 и на этапе S1708.

[0048] На этапе S1901 модуль 901 CPU получает размер целевого блока. На этапе S1902 модуль 901 CPU получает минимальный размер блока управления качеством изображения. На этапе S1903 модуль 901 CPU получает состояние разделения блока. На этапе S1904 модуль 901 CPU определяет, является ли целевой блок разделенным. На этапе S1905 модуль 901 CPU определяет, является ли размер целевого блока большим, чем или равным минимальному размеру блока управления качеством изображения. На этапе S1906 модуль 901 CPU определяет, является ли размер целевого блока равным минимальному размеру блока управления качеством изображения. На этапе S1907 модуль 901 CPU вычисляет параметр качества изображения.

[0049] Ниже будет описана процедура этапов. На этапе S1901 модуль 901 CPU получает размер целевого блока. Сразу же после того, как настоящая процедура запускается от процедуры по фиг. 17, назначенный к обработке целевой блок сам по себе представляет собой сетчатый блок. Значение размера целевого блока, таким образом, составляет 64. По мере того, как уровень структуры дерева квадрантов, разбивающего пространство, последовательно снижается по причине рекурсивных вызовов, значение размера изменяется на 32, 16 и 8.

[0050] На этапе S1902 модуль 901 CPU получает минимальный размер блока управления качеством изображения, установленный извне. В настоящем иллюстративном варианте осуществления минимальный размер блока управления качеством изображения составляет 16 по значению.

[0051] Является ли подлежащий кодированию целевой блок разделенным, было определено на этапе S1700 и на этапе S1701 по фиг. 17. На этапе S1903 модуль 901 CPU получает информацию состояния разделения, обозначающую результат определения разделения.

[0052] На этапе S1904 модуль 901 CPU обращается к полученному состоянию разделения целевого блока и определяет, является ли целевой блок разделенным. Если целевой блок является разделенным («ДА» на этапе S1904), модуль 901 CPU выполняет этап S1906. Если целевой блок не является разделенным («НЕТ» на этапе S1904), модуль 901 CPU выполняет этап S1905.

[0053] На этапе S1905 модуль 901 CPU определяет, является ли размер целевого блока большим, чем или равным минимальному размеру блока управления качеством изображения. Если размер целевого блока определяется как являющийся большим или равным («ДА» на этапе S1905), модуль 901 CPU выполняет этап S1907. Если нет («НЕТ» на этапе S1905), модуль 901 CPU заканчивает обработку вычисления параметра качества изображения.

[0054] На этапе S1906 модуль 901 CPU определяет, является ли размер целевого блока равным минимальному размеру блока управления качеством изображения. Если размер целевого блока определяется как являющийся равным минимальному размеру блока управления качеством изображения («ДА» на этапе S1906), модуль 901 CPU выполняет этап S1907. Если нет («НЕТ» на этапе S1906), модуль 901 CPU заканчивает обработку вычисления параметра качества изображения.

[0055] На этапе S1907 модуль 901 CPU выполняет обработку управления скоростью с целью вычисления параметра качества изображения для кодирования целевого блока. Например, как в случае использования TM5, модуль 901 CPU осуществляет предсказание объема кода целевого блока и вычисляет оптимальный параметр квантования. Если целевой блок является разделенным, все включенные разделительные блоки подвергаются управлению скоростью. Кодирование включенных разделительных блоков осуществляется с помощью одного и того же параметра качества изображения.

[0056] Способ кодирования в соответствии с настоящим иллюстративным вариантом осуществления используется для вывода данных, имеющих структуру данных, проиллюстрированную на фиг. 15 и на фиг. 16. Касательно фиг. 15, информация заголовка кадра включает в себя код минимального размера блока управления качеством изображения, встроенный на этапе S1303 по фиг. 13. Все сетчатые блоки внутри кадра находятся под управлением кода. Касательно фиг. 16, за флагом разделения в сетчатом блоке, или в блоке размером 64×64 пикселей, следует флаг разделения в верхнем слева блоке размером 32×32 пикселя на последующем уровне. Если блок размером 32×32 пикселя не является разделенным, следует код параметра качества изображения или код QP_DELTA этого блока, сопровождаемый кодом данных коэффициента по остаточным 32×32 пикселям. Далее следует флаг разделения по верхнему справа блоку размером 32×32 пикселя. Как упомянуто выше, если блок размером 32×32 пикселя является разделенным на блоки размером 16×16 пикселей, следует флаг разделения для обозначения состояния разделения. Если блок не является разделенным дополнительно, следуют код QP_DELTA и код данных коэффициента. Минимальный размер блока управления качеством изображения составляет 16. Если блок является разделенным на блоки, меньшие, чем 16×16 пикселей, флаг разделения и код данных коэффициента следуют без кода QP_DELTA, добавляемого к блокам меньшего размера.

[0057] Как описано выше, размер целевого блока сравнивается с минимальным размером блока управления качеством изображения, и управление решением, осуществлять или нет кодирование значения QP_DELTA, осуществляется в зависимости от результата сравнения. Обеспечение такого механизма обеспечивает возможность управления качеством изображения в модулях блоков, на которые делится изображение в сетчатой структуре. Управление качеством изображения может выполняться в модулях с более высоким разрешением (фиг. 12C), чем в традиционном случае, когда код QP_DELTA является встроенным в модули сетчатых блоков (фиг. 12A). Это может сужать границы между блоками с разным качеством изображения и делать различия по качеству изображения менее заметными. В одном другом традиционном случае управление качеством изображения выполняется, и код QP_DELTA является встроенным, в модулях блоков ортогонального преобразования (фиг. 12B). В отличие от такого случая, объем кода не будет увеличиваться сверх необходимого, поскольку модуль управления качеством изображения может выбираться, и нет необходимости встраивать код QP_DELTA в каждый блок ортогонального преобразования. Процедура вычисления параметра качества изображения выполняется только, если сохраняется то же самое условие, что и условие для вставки параметра качества изображения. Таким образом, также предотвращается увеличение сверх необходимого вычисления параметра качества изображения.

[0058] В настоящем иллюстративном варианте осуществления блоки определяются как квадратные блоки. Будет вполне понятным, что блоки могут быть прямоугольными, такими как блоки размером 8x4 пикселей. В то время как сканирование структуры дерева квадрантов, разбивающего пространство, осуществляется посредством использования рекурсивной обработки, для осуществления сканирования могут использоваться структуры с циклами.

[0059] Как проиллюстрировано на фиг. 10, способ кодирования в соответствии с настоящим иллюстративным вариантом осуществления может выполняться посредством конфигурации, включающей в себя выделенное аппаратное обеспечение, такое как ортогональный преобразователь 1003, квантователь 1004, а также кодер 1005 переменной длины. Модуль 1001 CPU не будет выполнять ортогональное преобразование, квантование, а также этап кодирования переменной длины, но побуждает вышеизложенные модули выполнять соответствующие части обработки. В других отношениях процедура является такой же самой, что и процедура, проиллюстрированная на фиг. 17.

[0060] Настоящий иллюстративный вариант осуществления рассмотрел случай, когда кодированные данные являются записанными на накопителе 903 HDD. Однако это не является ограничением. Кодированные данные могут быть записанными на носителе записи, отличном от накопителя 903 на жестком диске. Будет в полной мере понятным, что кодированные данные могут передаваться в цепь связи через посредство интерфейса 905 связи. В целях осуществления записи кодированных данных на переносном носителе записи информации может подсоединяться внешнее записывающее устройство.

[0061] Настоящий иллюстративный вариант осуществления также рассмотрел случай, когда программные приложения являются записанными на накопителе 903 на жестком диске. Однако это не является ограничением. Программные приложения могут быть записанными на элементе аппаратного оборудования, таком как постоянное запоминающее устройство (ПЗУ, ROM). Будет в полной мере понятным, что программные приложения могут быть записанными на переносном носителе записи информации, таком как карта памяти и магнитный диск.

[0062] Настоящий иллюстративный вариант осуществления также рассмотрел случай, когда, с целью получения кода, обозначающего размер минимального блока управления качеством изображения, кодируется количество разделения. Однако это не является ограничением. Поскольку максимальный размер блока составляет размер сетчатого блока, размер минимального блока управления качеством изображения может выражаться посредством шестибитового кода фиксированной длины. Минимальный блок управления качеством изображения не ограничивается до квадратной конфигурации. Минимальные блоки управления качеством изображения для горизонтальной и вертикальной конфигураций могут обеспечиваться отдельно. Например, горизонтальные или горизонтально примыкающие блоки могут группироваться вместе, и управление параметрами качества изображения может осуществляться в модулях групп блоков. В таком случае, размеры минимальных блоков управления качеством изображения могут эффективно устанавливаться для горизонтальной и вертикальной конфигураций отдельно.

[0063] Способ декодирования изображения в соответствии со вторым иллюстративным вариантом осуществления настоящего изобретения будет описан со ссылкой на фиг. 2, фиг. 9, фиг. 14 и фиг. 18.

[0064] Фиг. 9 иллюстрирует конфигурацию для выполнения программы декодирования, включающую в себя способ декодирования в соответствии с настоящим иллюстративным вариантом осуществления. Программа записи записана на накопителе 903 HDD. Программа декодирования загружается в запоминающее устройство 902 RAM, и модуль 901 CPU выполняет этапы назначенной к описанию ниже процедуры для обработки декодирования. Входные кодированные данные считываются из накопителя 903 HDD. Декодированное изображение выводится на устройство отображения через посредство выходного буфера изображения, обеспеченного в оперативном запоминающем устройстве 904 видеоизображений (VRAM). Модуль 901 CPU выполняет обработку декодирования блок за блоком. Декодирование каждого блока осуществляется с целью получения декодированного изображения блока, которое копируется в соответствующее положение в кадре при выводе на выходной буфер изображения. Когда завершается обработка декодирования блоков вплоть до одного кадра, кадр изображения выводится на выходной буфер. Нижеследующее описание будет дано при допущении, что входные кодированные данные представляют собой кодированные данные, сгенерированные в первом иллюстративном варианте осуществления.

[0065] Фиг. 14 иллюстрирует процедуру для декодирования входных кодированных данных. Декодирование сетчатых блоков осуществляется в растровом порядке сканирования. На этапе S1401 модуль 901 CPU осуществляет декодирование и получает информацию заголовка кадра. Настоящий иллюстративный вариант осуществления рассматривает случай, когда данная информация заголовка кадра включает в себя минимальный размер блока управления качеством изображения. Однако это не является ограничением. В соответствии с предварительно заданным форматом данных, минимальный размер блока управления качеством изображения может быть получен из информации заголовка последовательности, картинки, среза или блока наиболее высокого иерархического уровня. На этапе S1402 модуль 901 CPU осуществляет декодирование и получает минимальный размер блока управления качеством изображения. На этапе S1403 модуль 901 CPU осуществляет установку так, чтобы результат декодирования кодированных данных в первую очередь сохранялся в первый целевой сетчатый блок. На этапе S1404 модуль 901 CPU осуществляет декодирование режима предсказания целевого сетчатого блока и генерирует предсказанное изображение в соответствии с режимом предсказания. На этапе S1405 модуль 901 CPU выполняет процедуру декодирования разделительных блоков в целевом сетчатом блоке. На этапе S1406 модуль 901 CPU добавляет данные предсказанного изображения и остаточные данные целевого сетчатого блока и выдает результат на выходной буфер изображения. На этапе S1407 модуль 901 CPU определяет, все ли сетчатые блоки в кадре обработаны. На этапе S1408 модуль 901 CPU устанавливает следующий сетчатый блок в качестве целевого сетчатого блока.

[0066] Ниже будет описана процедура этапов. На этапе S1401 модуль 901 CPU получает параметр, называемый минимальным размером блока управления качеством изображения, из информации заголовка блока наиболее высокого порядка с точки зрения последовательностей, картинок, кадров, срезов, а также иерархической структуры.

[0067] На этапе S1402 модуль 901 CPU осуществляет декодирование и получает минимальный размер блока управления качеством изображения. В соответствии с первым иллюстративным вариантом осуществления, минимальный размер блока управления качеством изображения кодируется как индекс. Минимальный размер блока управления качеством изображения составляет 16. На этапе S1403 модуль 901 CPU устанавливает, в качестве целевого сетчатого блока, сетчатый блок в верхней левой части экрана.

[0068] На этапе S1404 модуль 901 CPU осуществляет декодирование кодированных данных в целевом сетчатом блоке. Модуль 901 CPU тем самым осуществляет декодирование режима внутрикадрового предсказания и/или векторов движения, сгенерированных в первом иллюстративном варианте осуществления. С помощью внутреннего кодирования, модуль 901 CPU обращается к смежным декодированным пикселям и генерирует данные предсказанного изображения на основе декодированного режима внутрикадрового предсказания. С помощью интеркодирования, модуль 901 CPU выполняет компенсацию движения с целью генерирования данных предсказанного изображения на основе векторов движения.

[0069] На этапе S1405 модуль 901 CPU выполняет, в сетчатом блоке, процедуру декодирования разделительных блоков, которая будет описана ниже в совокупности с фиг. 18. Поскольку декодирование разделительных блоков является иерархически структурированным, модуль 901 CPU осуществляет декодирование флагов разделения в блоках и, при выполнении декодирования, определяет состояния разделительных блоков. Модуль 901 CPU тем самым генерирует параметры качества изображения и остаточные данные в отношении предсказаний.

[0070] На этапе S1406 модуль 901 CPU добавляет данные предсказанного изображения, сгенерированные на этапе S1404, и остаточные данные, сгенерированные на этапе S1405, с целью генерирования декодированного изображения целевого сетчатого блока. Модуль 901 CPU выводит декодированное изображение на выходной буфер изображения.

[0071] На этапе S1407 модуль 901 CPU определяет, все ли сетчатые блоки в кадре обработаны для декодирования. Например, модуль 901 CPU подсчитывает количество декодированных сетчатых блоков. Если не все сетчатые блоки обработаны для декодирования («НЕТ» на этапе S1407), модуль 901 CPU переходит к этапу S1408. Если декодированными являются все сетчатые блоки («ДА» на этапе S1407), модуль 901 CPU заканчивает обработку декодирования в кадре.

[0072] На этапе S1408 модуль 901 CPU устанавливает результат декодирования, идущий следом в растровом порядке сканирования, в качестве следующего целевого сетчатого блока.

[0073] Фиг. 18 представляет собой подробную блок-схему последовательности операций этапа S1405, иллюстрирующую процедуру для декодирования множества иерархически структурированных блоков ортогонального преобразования различных размеров. В конкретном плане фиг. 18 иллюстрирует процедуру для выполнения, с целью генерирования остаточных данных, декодирования переменной длины, обратного ортогонального преобразования, а также обратного квантования кодированных данных коэффициента переменной длины на основе кода флага разделения блока и кода QP_DELTA. Настоящий иллюстративный вариант осуществления использует структуру дерева квадрантов, разбивающего пространство, для иерархического структурирования. Блок наиболее высокого уровня (первый целевой блок, назначенный к обработке) представляет собой сетчатый блок размером 64x64 пикселя.

[0074] На этапе S1801 модуль 901 CPU осуществляет декодирование флага разделения блока в целевом блоке. На этапе S1802 модуль 901 CPU выполняет процедуру декодирования параметра качества изображения. На этапе S1803 модуль 901 CPU определяет, является ли целевой блок, назначенный для декодирования, разделенным. На этапе S1804 модуль 901 CPU выполняет декодирование переменной длины, обратное квантование, а также обратное ортогональное преобразование. На этапе S1805 модуль 901 CPU рекурсивно выполняет обработку декодирования во включенных разделительных блоках.

[0075] Ниже будет описана процедура этапов. На этапе S1801 модуль 901 CPU осуществляет декодирование флага разделения блока, такого как флаг, проиллюстрированный на фиг. 16, с целью получения информации касательно того, является ли целевой блок дополнительно разделенным. Декодирование выполняется в соответствии с иерархической структурой дерева квадрантов. Модуль 901 CPU может тем самым получать состояние разделения блоков.

[0076] На этапе S1802 модуль 901 CPU выполняет процедуру декодирования параметра качества изображения, назначенную к описанию ниже в совокупности с фиг. 2. Модуль 901 CPU тем самым осуществляет декодирование параметра качества изображения, используемого при обратном квантовании для декодирования целевого блока.

[0077] На этапе S1803 модуль 901 CPU обращается к декодированному флагу разделения блока с целью определения, является ли целевой блок разделенным. Если целевой блок определяется как не являющийся разделенным («НЕТ» на этапе S1803), модуль 901 CPU выполняет этап S1804. Если целевой блок определяется как являющийся разделенным («ДА» на этапе S1803), модуль 901 CPU выполняет этап S1805.

[0078] На этапе S1804 модуль 901 CPU выполняет декодирование переменной длины, обратное квантование, а также обратное ортогональное преобразование кодированных данных коэффициента целевого блока, генерируя тем самым остаточные данные. Для осуществления декодирования переменной длины, модуль 901 CPU выполняет декодирование в соответствии со схемой кодирования, используемой в первом иллюстративном варианте осуществления. Модуль 901 CPU тем самым получает данные коэффициента квантования, включенные в блок. Для обратного квантования, модуль 901 CPU использует параметр качества изображения, декодированный на этапе S1802. Если на этапе S1802 ни одного нового параметра качества изображения не декодировано, модуль 901 CPU выполняет обратное квантование посредством просто использования параметра качества изображения, декодированного ранее. Модуль 901 CPU выполняет обратное ортогональное преобразование данных коэффициента, результирующих из обратного квантования, генерируя тем самым остаточные данные.

[0079] На этапе S1805 модуль 901 CPU рекурсивно выполняет обработку на этапах от S1801 по этап S1805 до тех пор, пока декодированный флаг разделения блока обозначает наличие иерархически последовательного уровня. Модуль 901 CPU тем самым восстанавливает остаточные данные до тех пор, пока не будет достигнут минимальный размер разделительного блока.

[0080] Далее, со ссылкой на фиг. 2, будет подробно описан этап S1802, назначенный для осуществления декодирования параметра качества изображения.

[0081] Фиг. 2 иллюстрирует процедуру для декодирования параметра качества изображения множества иерархически структурированных блоков ортогонального преобразования различных размеров. На этапе S201 модуль 901 CPU получает размер целевого блока. На этапе S202 модуль 901 CPU получает минимальный размер блока управления качеством изображения. На этапе S203 модуль 901 CPU получает состояние разделения блока. На этапе S204 модуль 901 CPU определяет, является ли целевой блок разделенным. На этапе S205 модуль 901 CPU определяет, является ли размер целевого блока большим, чем или равным минимальному размеру блока управления качеством изображения. На этапе S206 модуль 901 CPU определяет, является ли размер целевого блока равным минимальному размеру блока управления качеством изображения. На этапе S207 модуль 901 CPU осуществляет декодирование параметра качества изображения.

[0082] Ниже будет описана процедура этапов. На этапе S201 модуль 901 CPU получает размер целевого блока. Сразу же после того, как настоящая процедура запускается от процедуры по фиг. 18, назначенный к обработке целевой блок сам по себе представляет собой сетчатый блок. Значение размера целевого блока, таким образом, составляет 64. По мере того как флаги разделения последовательно декодируются, значение размера изменяется на 32, 16 и 8 соответственно.

[0083] На этапе S202 модуль 901 CPU получает минимальный размер блока управления качеством изображения. В настоящем иллюстративном варианте осуществления модуль 901 CPU получает минимальный размер блока управления качеством изображения, декодированный на этапе S1402 по фиг. 14. На этапе S203 модуль 901 CPU получает состояние разделения блока. В настоящем иллюстративном варианте осуществления модуль 901 CPU получает флаг разделения блока, декодированный на этапе S1801 по фиг. 18.

[0084] На этапе S204 модуль 901 CPU определяет значение флага разделения блока. Используя такое же самое присвоение кода, что и присвоение, описанное в первом иллюстративном варианте осуществления, флаг разделения блока, имеющий значение «0», обозначает, что блок не является разделенным. Флаг разделения блока, имеющий значение «1», обозначает, что блок является разделенным. Если значение флага разделения блока составляет «0» («НЕТ» на этапе S204), модуль 901 CPU выполняет этап S205. Если значение составляет «1» («ДА» на этапе S204), модуль 901 CPU выполняет этап S206.

[0085] На этапе S205 модуль 901 CPU определяет, является ли размер целевого блока большим, чем или равным минимальному размеру блока управления качеством изображения. Если размер целевого блока больше, чем или равен минимальному размеру блока управления качеством изображения («ДА» на этапе S205), модуль 901 CPU выполняет этап S207. Если нет («НЕТ» на этапе S205), модуль 901 CPU заканчивает обработку.

[0086] На этапе S206 модуль 901 CPU определяет, является ли размер целевого блока равным минимальному размеру блока управления качеством изображения. Если размер целевого блока является равным минимальному размеру блока управления качеством изображения («ДА» на этапе S206), модуль 901 CPU выполняет этап S207. Если нет («НЕТ» на этапе S206), модуль 901 CPU заканчивает обработку.

[0087] На этапе S207, модуль 901 CPU осуществляет декодирование кода параметра качества изображения. В настоящем иллюстративном варианте осуществления, модуль 901 CPU осуществляет декодирование кода QP_DELTA в значение QP_DELTA посредством декодирования Голомба. В настоящем иллюстративном варианте осуществления, декодирование QP_DELTA осуществляется посредством декодирования Голомба. Однако это не является ограничением. Декодирование QP_DELTA может осуществляться посредством арифметического декодирования или другого декодирования переменной длины в зависимости от предварительно заданного формата данных. Модуль 901 CPU затем добавляет значение QP_DELTA к параметру качества изображения, используемому для кодирования предыдущего блока, генерируя тем самым параметр качества изображения.

[0088] В настоящем иллюстративном варианте осуществления управление решением, осуществлять или нет декодирование параметра качества изображения, осуществляется в зависимости от того же самого условия, что и условие для сравнения размера целевого блока, в котором осуществляется кодирование параметра качества изображения, и минимального размера блока управления качеством изображения. Это обеспечивает возможность декодирования потока, генерируемого посредством способа кодирования, описанного в первом иллюстративном варианте осуществления.

[0089] Как проиллюстрировано на фиг. 11, способ декодирования в соответствии с настоящим иллюстративным вариантом осуществления может выполняться посредством конфигурации, включающей в себя, вместо конфигурации, проиллюстрирован на фиг. 9, выделенное аппаратное обеспечение, такое как обратный ортогональный преобразователь 1103, обратный квантователь 1104 и декодер 1105 переменной длины. Модуль 1101 CPU не будет выполнять обратное ортогональное преобразование, обратное квантование, а также этап декодирования переменной длины, но побуждает вышеизложенные модули выполнять соответствующие части обработки. В других отношениях, процедура является такой же самой, что и процедура, проиллюстрированная на фиг. 18.

[0090] Настоящий иллюстративный вариант осуществления рассмотрел случай, когда кодированные данные являются записанными на накопителе 903 на жестком диске. Однако это не является ограничением. Кодированные данные могут приниматься из цепи связи через посредство интерфейса 1006 связи. В целях осуществления ввода кодированных данных от переносного носителя записи информации может подсоединяться внешнее записывающее устройство.

[0091] Настоящий иллюстративный вариант осуществления также рассмотрел случай, когда программные приложения являются записанными на накопителе 903 на жестком диске. Однако это не является ограничением. Программные приложения могут быть записанными на элементе аппаратного оборудования, таком как постоянное запоминающее устройство (ПЗУ, ROM). Будет в полной мере понятным, что программные приложения могут быть записанными на переносном носителе записи информации, таком как карта памяти и магнитный диск.

[0092] Способ кодирования параметра качества изображения в соответствии с третьим иллюстративным вариантом осуществления настоящего изобретения будет описан со ссылкой на фиг. 3. Если только это не специфицировано иным образом, конфигурация для выполнения способа кодирования и функционирование этапов являются такими же самыми, как в первом иллюстративном варианте осуществления. В настоящем иллюстративном варианте осуществления блок, включающий в себя целевой блок и имеющий такой же самый размер, что и минимальный размер блока управления качеством изображения, будет определяться как минимальный блок управления качеством изображения. Информация, обозначающая, осуществляется ли кодирование параметра качества изображения в минимальном блоке управления качеством изображения, будет определяться как информация состояния кодирования параметра качества изображения. Данная информация состояния кодирования параметра качества изображения является эквивалентной информации, обозначающей, осуществляется ли кодирование параметра качества изображения первого разделительного блока в минимальном блоке управления качеством изображения.

[0093] Фиг. 3 иллюстрирует процедуру для кодирования параметра качества изображения. Фиг.3 представляет собой подробную блок-схему последовательности операций процедуры кодирования параметра качества изображения, назначенной к выполнению на этапе S1705 и на этапе S1709 по фиг. 17. Эта процедура выполняется вместо процедуры кодирования параметра качества изображения, проиллюстрированной на фиг. 1. На этапе S301 модуль 901 CPU получает информацию состояния кодирования параметра качества изображения. На этапе S302 модуль 901 CPU обращается к информации состояния кодирования параметра качества изображения и определяет, было ли уже осуществлено кодирование параметра качества изображения в минимальном блоке управления качеством изображения.

[0094] Ниже будет описана процедура этапов. На этапе S104, как в первом иллюстративном варианте осуществления, модуль 901 CPU обращается к полученному состоянию разделения целевого блока, то есть к тому, является ли целевой блок дополнительно разделенным посредством дерева квадрантов. Если целевой блок определяется как являющийся разделенным («ДА» на этапе S104), модуль 901 CPU заканчивает обработку, в отличие от первого иллюстративного варианта осуществления. Если целевой блок определяется как не являющийся разделенным («НЕТ» на этапе S104), модуль 901 CPU выполняет этап S105, как в первом иллюстративном варианте осуществления.

[0095] На этапе S105, как в первом иллюстративном варианте осуществления, модуль 901 CPU определяет, является ли размер целевого блока большим, чем или равным минимальному размеру блока управления качеством изображения. Если размер целевого блока определяется как являющийся большим или равным («ДА» на этапе S105), модуль 901 CPU выполняет этап S107 и этап S108, как в первом иллюстративном варианте осуществления. Если нет («НЕТ» на этапе S105), модуль 901 CPU выполняет обработку этапа S301 и этапа S302.

[0096] На этапе S301 модуль 901 CPU получает информацию состояния кодирования параметра качества изображения. В настоящем иллюстративном варианте осуществления минимальный размер блока управления качеством изображения составляет 16. Если целевой блок представляет собой верхний слева блок размером 8×8 пикселей, за этим следует, что модуль 901 CPU получает информацию, что не осуществляется кодирование ни одного параметра качества изображения. Если целевой блок представляет собой верхний справа, нижний слева или нижний справа блок размером 8×8 пикселей, кодирование параметра качества изображения уже было осуществлено в верхнем слева блоке размером 8×8 пикселей. В таком случае, модуль 901 CPU получает информацию, что кодирование параметра качества изображения осуществляется.

[0097] На этапе S302 модуль 901 CPU обращается к информации состояния кодирования параметра качества изображения и определяет, было ли уже осуществлено кодирование параметра качества изображения в минимальном блоке управления качеством изображения. Если определяется, что не было осуществлено кодирование ни одного параметра качества изображения («НЕТ» на этапе S302), модуль 901 CPU выполняет этап S107 и этап S108. Если определяется, что кодирование параметра качества изображения было осуществлено («ДА» на этапе S302), модуль 901 CPU заканчивает обработку кодирования параметра качества изображения.

[0098] Далее будут описаны различия между настоящим иллюстративным вариантом осуществления и первым иллюстративным вариантом осуществления. В первом иллюстративном варианте осуществления код QP_DELTA встраивается в качестве данных, сопровождающих целевой блок (набор разделительных блоков), если «целевой блок является разделенным и размер целевого блока является равным минимальному размеру блока управления качеством изображения». В настоящем иллюстративном варианте осуществления код QP_DELTA добавляется к верхнему слева блоку, представляющему собой первый блок в целевом блоке, если «целевой блок является разделенным и размер целевого блока является равным минимальному размеру блока управления качеством изображения». В настоящем иллюстративном варианте осуществления минимальный размер блока управления качеством изображения составляет 16. Предположим, что блоки, разделенные, как проиллюстрировано на фиг. 20, составляют поток. В таком случае, код QP_DELTA вставляется в непосредственно предшествующие части кодированных данных коэффициента переменной длины, соответствующие заштрихованным блокам с номерами 0, 1, 7, 5, 6, 8, 9, 13, 14 и 15. Иными словами, код QP_DELTA сопровождает блоки размером 16×16 пикселей или более. Если блок размером 16×16 пикселей является разделенным, код QP_DELTA сопровождает верхний слева блок размером 8×8 пикселей, то есть первый дополнительно разделенный блок в блоке размером 16×16 пикселей.

[0099] Настоящий иллюстративный вариант осуществления может, таким образом, обеспечивать такие же самые эффекты, что и эффекты по первому иллюстративному варианту осуществления, в то время как процедуры и структуры данных имеют другие идеи. В одной другой возможной конфигурации не осуществляется кодирование ни одного параметра качества изображения, если только коэффициенты квантования не имеют ненулевое значение. Если верхний слева блок в целевом блоке не включает в себя ни одного коэффициента квантования с ненулевым значением, параметр качества изображения прикрепляется к структурно-последующему первому разделительному блоку, в котором коэффициент квантования имеет ненулевое значение. На этапе S301 настоящего иллюстративного варианта осуществления модуль 901 CPU вычисляет и получает информацию состояния кодирования параметра качества изображения из размера и положения целевого блока, подлежащего кодированию. Однако это не является ограничением. Например, может обеспечиваться флаг, обозначающий, осуществляется ли кодирование параметра качества изображения в минимальном размере блока управления качеством изображения. Упомянутый флаг повторно устанавливается каждый раз, когда выполняется обработка разделения минимального блока управления качеством изображения, и устанавливается каждый раз, когда осуществляется кодирование параметра качества изображения. Для получения информации состояния кодирования параметра качества изображения модуль 901 CPU обращается к флагу. Если флаг является повторно установленным, модуль 901 CPU получает информацию, что не осуществляется кодирование ни одного параметра качества изображения. Если флаг является установленным, модуль 901 CPU получает информацию, что кодирование параметра качества изображения осуществляется.

[0100] Способ декодирования параметра качества изображения в соответствии с четвертым иллюстративным вариантом осуществления настоящего изобретения будет описан со ссылкой на фиг. 4. Если только это не специфицировано иным образом, конфигурация для выполнения способа декодирования и функционирование этапов являются такими же самыми, как во втором иллюстративном варианте осуществления. В настоящем иллюстративном варианте осуществления блок, включающий в себя целевой блок и имеющий такой же самый размер, что и минимальный размер блока управления качеством изображения, будет определяться как минимальный блок управления качеством изображения. Информация, обозначающая, осуществляется ли декодирование параметра качества изображения в минимальном блоке управления качеством изображения, будет определяться как информация состояния декодирования параметра качества изображения.

[0101] Фиг. 4 иллюстрирует процедуру для декодирования параметра качества изображения. Фиг. 4 представляет собой подробную блок-схему последовательности операций для процедуры декодирования параметра качества изображения, назначенной к выполнению на этапе S1802 по фиг. 18. Данная процедура выполняется вместо процедуры декодирования параметра качества изображения, проиллюстрированной на фиг. 2. На этапе S401 модуль 901 CPU получает информацию состояния декодирования параметра качества изображения. На этапе S402 модуль 901 CPU обращается к информации состояния декодирования параметра качества изображения и определяет, было ли уже осуществлено декодирование параметра качества изображения в минимальном блоке управления качеством изображения.

[0102] Ниже будет описана процедура этапов. На этапе S204 модуль 901 CPU определяет значение флага разделения блока. Если значение флага разделения блока составляет «0», что обозначает, что блок не является разделенным («НЕТ» на этапе S204), модуль 901 CPU выполняет этап S205, как во втором иллюстративном варианте осуществления. Если значение флага разделения блока составляет «1», что обозначает, что блок является разделенным («ДА» на этапе S204), модуль 901 CPU заканчивает обработку декодирования параметра качества изображения, в отличие от второго иллюстративного варианта осуществления.

[0103] На этапе S205, как во втором иллюстративном варианте осуществления, модуль 901 CPU определяет, является ли размер целевого блока большим, чем или равным минимальному размеру блока управления качеством изображения. Если размер целевого блока определяется как являющийся большим или равным («ДА» на этапе S205), модуль 901 CPU переходит к этапу S207. На этапе S207 модуль 901 CPU осуществляет декодирование параметра качества изображения, как во втором иллюстративном варианте осуществления. Если нет («НЕТ» на этапе S205), модуль 901 CPU выполняет этап S401 и этап S402.

[0104] На этапе S401 модуль 901 CPU получает информацию состояния декодирования параметра качества изображения. В настоящем иллюстративном варианте осуществления минимальный размер блока управления качеством изображения составляет 16. Если целевой блок представляет собой верхний слева блок размером 8×8 пикселей, за этим следует, что модуль 901 CPU получает информацию, что не осуществляется декодирование ни одного параметра качества изображения. Если целевой блок представляет собой верхний справа, нижний слева или нижний справа блок размером 8x8 пикселей, декодирование параметра качества изображения уже было осуществлено в верхнем слева блоке размером 8×8 пикселей. В таком случае, модуль 901 CPU получает информацию, что декодирование параметра качества изображения осуществляется.

[0105] На этапе S402 модуль 901 CPU обращается к информации состояния декодирования параметра качества изображения и определяет, было ли уже осуществлено декодирование параметра качества изображения в минимальном блоке управления качеством изображения. Если не было осуществлено декодирование ни одного параметра качества изображения («НЕТ» на этапе S402), модуль 901 CPU выполняет этап S207. Если декодирование параметра качества изображения было осуществлено («ДА» на этапе S402), модуль 901 CPU заканчивает обработку декодирования параметра качества изображения.

[0106] В настоящем иллюстративном варианте осуществления управление решением, осуществлять или нет декодирование параметра качества изображения в действительности, осуществляется на основе условия для сравнения размера целевого блока, в котором осуществляется кодирование параметра качества изображения, и минимального размера блока управления качеством изображения; а также на основе условия определения для определения, было ли уже осуществлено декодирование параметра качества изображения в минимальном блоке управления качеством изображения. Такой режим обеспечивает возможность декодирования потока, генерируемого посредством способа кодирования, описанного в третьем иллюстративном варианте осуществления. Способ кодирования может использовать конфигурацию, такую что не осуществляется кодирование ни одного параметра качества изображения, если только коэффициенты квантования не имеют ненулевое значение. В таком случае, способ декодирования может использовать схожую конфигурацию. Если верхний слева блок в целевом блоке не включает в себя ни одного коэффициента квантования с ненулевым значением, декодирование параметра качества изображения осуществляется в структурно-последующем первом разделительном блоке, в котором коэффициент квантования имеет ненулевое значение.

[0107] На этапе S401 по фиг. 4, в соответствии с настоящим иллюстративным вариантом осуществления, модуль 901 CPU вычисляет и получает информацию состояния декодирования параметра качества изображения из размера и положения целевого блока, подлежащего декодированию. Однако это не является ограничением. Например, может обеспечиваться флаг, обозначающий, осуществляется ли декодирование параметра качества изображения внутри минимального размера блока управления качеством изображения. Упомянутый флаг повторно устанавливается каждый раз, когда выполняется обработка разделения минимального блока управления качеством изображения, и устанавливается каждый раз, когда осуществляется декодирование параметра качества изображения. В целях получения информации состояния декодирования параметра качества изображения, модуль 901 CPU обращается к флагу. Если флаг является повторно установленным, модуль 901 CPU получает информацию, что не осуществляется декодирование ни одного параметра качества изображения. Если флаг является установленным, модуль 901 CPU получает информацию, что декодирование параметра качества изображения осуществляется.

[0108] Процедура для кодирования остаточных данных в блоке будет описана со ссылкой на фиг. 5. Данная процедура относится к способу кодирования параметра качества изображения в соответствии с пятым иллюстративным вариантом осуществления настоящего изобретения. Если только это не специфицировано иным образом, конфигурация для выполнения способа кодирования и функционирование этапов являются такими же самыми, как в первом иллюстративном варианте осуществления.

[0109] Фиг. 5 иллюстрирует процедуру для кодирования параметра качества изображения и кодирования остаточных данных. Данная процедура осуществляет обработку, проиллюстрированную на фиг. 17 и фиг. 1. Процедура запускается от этапа S1306 по фиг. 13. На этапе S501 модуль 901 CPU получает размер целевого блока. На этапе S502 модуль 901 CPU получает минимальный размер блока управления качеством изображения. На этапе S503 модуль 901 CPU вычисляет стоимости, когда целевой блок является разделенным и когда - нет, соответственно. На этапе S504 модуль 901 CPU определяет, осуществлять ли деление целевого блока. На этапе S505 модуль 901 CPU выдает флаг разделения блока, установленный в значении «ложь». На этапе S506 модуль 901 CPU определяет, является ли размер целевого блока большим, чем или равным минимальному размеру блока управления качеством изображения. На этапе S507 модуль 901 CPU вычисляет параметр качества изображения. На этапе S508 модуль 901 CPU выполняет процедуру кодирования параметра качества изображения. На этапе S509 модуль 901 CPU выполняет предсказание и выполняет ортогональное преобразование, квантование, а также кодирование переменной длины. На этапе S510 модуль 901 CPU выдает флаг разделения блока, установленный в значении «истина». На этапе S511 модуль 901 CPU определяет, является ли размер целевого блока равным минимальному размеру блока управления качеством изображения. На этапе S512 модуль 901 CPU вычисляет параметр качества изображения. На этапе S513 модуль 901 CPU осуществляет кодирование параметра качества изображения. На этапе S514 модуль 901 CPU осуществляет обработку включенных разделительных блоков.

[0110] Процедура обработки будет конкретизировано описана ниже. На этапе S501 модуль 901 CPU получает размер целевого блока. Сразу же после того, как настоящая процедура запускается от процедуры по фиг. 13, назначенный к обработке целевой блок сам по себе представляет собой сетчатый блок. В настоящем иллюстративном варианте осуществления значение размера целевого блока составляет, хотя не ограничивается до этого, 64. По мере того, как уровень структуры дерева квадрантов, разбивающего пространство, последовательно снижается по причине рекурсивных вызовов, значение размера изменяется на 32, 16 и 8. Следует отметить, что количество уровней не ограничивается до упомянутого количества.

[0111] На этапе S502 модуль 901 CPU получает минимальный размер блока управления качеством изображения, установленный извне. В настоящем иллюстративном варианте осуществления значение минимального размера блока управления качеством изображения составляет, хотя не ограничивается до этого, 16.

[0112] На этапе S503 модуль 901 CPU вычисляет стоимости, когда, соответственно, целевой блок является разделенным и когда – нет. Стоимости вычисляются посредством использования упомянутых выше множителей Лагранжа, а также характеристик изображения, статистических данных и предсказанных длин кода.

[0113] На этапе S504 модуль 901 CPU сравнивает стоимости с делением и без деления, вычисленные на этапе S503. Если стоимость с делением блока является более низкой, чем стоимость без деления блока («ДА» на этапе S504), модуль 901 CPU выполняет этапы от S510 по этап S514. Если нет («НЕТ» на этапе S504), модуль 901 CPU выполняет этапы от S505 по этап S509.

[0114] На этапе S505 модуль 901 CPU выдает флаг разделения блока, установленный в значении «ложь». На этапе S506 модуль 901 CPU определяет, является ли размер целевого блока большим, чем или равным минимальному размеру блока управления качеством изображения. Если размер целевого блока больше или равен («ДА» на этапе S506), модуль 901 CPU выполняет этапы от S507 по этап S509. Если нет («НЕТ» на этапе S506), модуль 901 CPU выполняет этап S509 без выполнения этапа S507 и этапа S508.