ОБЛАСТЬ ТЕХНИКИ

Настоящее изобретение относится к области техники, связанной с аппаратным обеспечением терминалов, в частности, к терминалу с поддержкой множества режимов и к способу хэндовера для терминала с поддержкой множества режимов.

УРОВЕНЬ ТЕХНИКИ

В настоящее время некоторые телекоммуникационные операторы обслуживают множество сетей, поддерживающих различные режимы, например, China Unicom поддерживает сеть GSM (Global System for Mobile Communications, глобальная система для мобильной связи) и сеть WCDMA (Wideband Code Division Multiple Access, широкополосный множественный доступ с кодовым разделением), China Mobile поддерживает сеть GSM, сеть TD-SCDMA (Time Division Synchronous Code Division Multiple Access, множественный доступ с разделением по времени и с синхронным кодовым разделением) и сеть TD-LTE (time division long-term evolution, технология долгосрочного развития с использованием передачи данных с разделением по времени). В настоящий момент для предоставления голосовой услуги в сети LTE используется технология CSFB (Circuit Switched FallBack, возврат к сети с коммутацией каналов) для голосового вызова, согласно которой терминал с поддержкой LTE в сети LTE должен возвратиться в сеть GSM или любую другую сеть, предоставляющую голосовые услуги, вследствие чего терминалу LTE требуется поддерживать режим LTE и другие режимы, а также быстро переключаться между режимом LTE и другими режимами.

Кроме того, терминалу LTE в сети LTE требуется совместно передавать данные PS (Packet Switched, с коммутацией пакетов) и данные CS (Circuit Switched, с коммутацией каналов), а также одновременно поддерживать работу в режиме LTE и в других режимах. В настоящее время мобильные терминалы пользователей оснащены несколькими картами USIM (Universal Subscriber Identity Module, универсальный модуль идентификации абонента)/SIM (модуль идентификации абонента), при этом различные карты работают в различных сетях, или каждая карта USIM/SIM соответствует различной сети, что требует от мобильного терминала поддержки множества режимов для одной карты и множества состояний ожидания для множества карт.

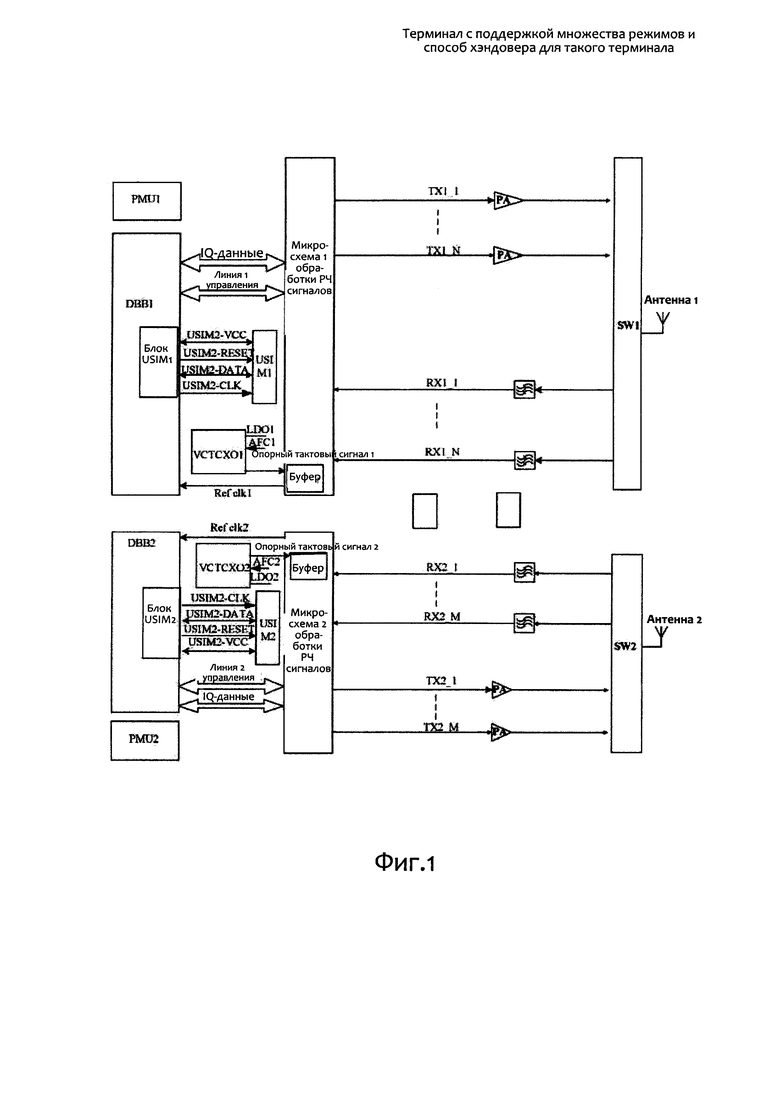

На фиг. 1 показана блок-схема архитектуры радиочастотного блока стандартного терминала, поддерживающего два состояния ожидания с двумя режимами, который содержит две независимые микросхемы управления питанием (PMU, power management), две независимые микросхемы обработки радиочастотных (РЧ) сигналов, две независимые микросхемы обработки цифровых сигналов основной полосы, два независимых гнезда для SIM-карты и два независимых источника тактовых сигналов. Поскольку применяются две независимые микросхемы обработки цифровых сигналов основной полосы и две независимые микросхемы управления питанием, для монтажа требуется большее пространство. Хотя в устройстве имеются два независимых гнезда для SIM-карт, две SIM-карты с поддержкой различных режимов не могут произвольно размещаться в любом из этих гнезд, в то время как с USIM/SIM-карты в любом гнезде можно считывать данные или записывать на нее данные, благодаря чему реализуется множество состояний ожидания с множеством режимов (multi-mode multi-standby), однако не осуществляется переход к функционированию с одним состоянием ожидания и множеством режимов (multi-mode single-standby).

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

Для решения указанной выше технической проблемы согласно варианту осуществления настоящего изобретения предложен терминал с поддержкой множества режимов и способ хэндовера для терминала с поддержкой множества режимов, позволяющие реализовать функционирование с множеством состояний ожидания и множеством режимов и с одним состоянием ожидания и множеством режимов.

Для решения вышеупомянутой технической проблемы терминал с поддержкой множества режимов в соответствии с вариантом осуществления настоящего изобретения содержит: микросхему управления питанием, микросхему обработки цифровых сигналов основной полосы, первую микросхему обработки радиочастотных сигналов, вторую микросхему обработки радиочастотных сигналов, первое гнездо для карты, второе гнездо для карты, первый источник тактовых сигналов и второй источник тактовых сигналов, при этом:

микросхема управления питанием подключена к микросхеме обработки цифровых сигналов основной полосы, первому гнезду для карты и второму гнезду для карты для подачи питания на микросхему обработки цифровых сигналов основной полосы, первое гнездо для карты и второе гнездо для карты;

микросхема обработки цифровых сигналов основной полосы также подключена к первому гнезду для карты и второму гнезду для карты и соответственно подключена к первой микросхеме обработки радиочастотных сигналов и второй микросхеме обработки радиочастотных сигналов через линию синфазных/квадратурных (I/Q, in-phase/quadrature) сигналов и линию управления для передачи, приема и обработки I/Q-сигналов с использованием поддерживаемых режимов, а также для управления линиями передачи и линиями приема в поддерживаемых режимах;

первый источник тактовых сигналов подключен к первой микросхеме обработки радиочастотных сигналов для формирования опорного тактового сигнала для первой микросхемы обработки радиочастотных сигналов; второй источник тактовых сигналов подключен ко второй микросхеме обработки радиочастотных сигналов для формирования опорного тактового сигнала для второй микросхемы обработки радиочастотных сигналов, при этом линия передачи тактовых сигналов также соединяет первую микросхему обработки радиочастотных сигналов и вторую микросхему обработки радиочастотных сигналов, причем первая микросхема обработки радиочастотных сигналов по линии передачи тактовых сигналов подает для второй микросхемы обработки радиочастотных сигналов выходной тактовый сигнал, служащий в качестве опорного тактового сигнала для второй микросхемы обработки радиочастотных сигналов.

В альтернативном варианте микросхема обработки цифровых сигналов основной полосы содержит блок обработки данных карты модуля идентификации абонента (SIM), при этом блок обработки данных SIM-карты содержит первый блок обработки данных SIM-карты, второй блок обработки данных SIM-карты и мультиплексор (MUX), поддерживающий взаимнооднозначное соответствие каждого контакта первого гнезда для карты и второго гнезда для карты, при этом с одной стороны MUX подключен к соответствующему контакту, а с другой стороны соответственно подключен к функциональным выводам первого блока обработки данных SIM-карты и второго блока обработки данных SIM-карты, которые соответствуют упомянутым контактам.

В альтернативном варианте микросхема обработки цифровых сигналов основной полосы содержит блок обработки тактовых сигналов, содержащий блок обработки системных тактовых сигналов, мультиплексор выбора тактового сигнала, схему автоматической фазовой подстройки частоты (PLL, phase lock loop), первый модуль тактовых сигналов поддерживаемого режима, второй модуль тактовых сигналов поддерживаемого режима, первый вывод входа тактового сигнала, второй вывод входа тактового сигнала и третий вывод входа тактового сигнала, при этом:

первый вывод входа тактового сигнала подключен к блоку обработки системных тактовых сигналов для формирования рабочего тактового сигнала для блока обработки системных тактовых сигналов;

первый вывод входа тактового сигнала совместно со вторым выводом входа тактового сигнала также подключен к входному выводу MUX выбора тактового сигнала, выходной вывод MUX выбора тактового сигнала подключен к входному выводу PLL, и выходной вывод PLL подключен к первому модулю тактовых сигналов поддерживаемого режима, что обеспечивает формирование рабочего тактового сигнала для первого модуля тактовых сигналов поддерживаемого режима;

второй вывод входа тактового сигнала также непосредственно подключен к первому модулю тактовых сигналов поддерживаемого режима для формирования рабочего тактового сигнала для первого модуля тактовых сигналов поддерживаемого режима;

третий вывод входа тактового сигнала подключен ко второму модулю тактовых сигналов поддерживаемого режима для формирования рабочего тактового сигнала для второго модуля тактовых сигналов поддерживаемого режима.

В альтернативном варианте первый вывод входа тактового сигнала также подключен к буферу тактовых сигналов в первой микросхеме обработки радиочастотных сигналов; второй вывод входа тактового сигнала также подключен к схеме автоматической фазовой подстройки частоты тактового сигнала (PLL) в первой микросхеме обработки радиочастотных сигналов; третий вывод входа тактового сигнала также подключен ко второй микросхеме обработки радиочастотных сигналов.

В альтернативном варианте вторая микросхема обработки радиочастотных сигналов содержит блок выбора тактового сигнала, включающий мультиплексор и буфер тактовых сигналов, при этом входной вывод мультиплексора подключен к линии передачи тактовых сигналов и второму источнику тактовых сигналов, выходной вывод мультиплексора подключен к входному выводу буфера тактовых сигналов, при этом выходной сигнал буфера тактовых сигналов служит в качестве опорного тактового сигнала второй микросхемы обработки радиочастотных сигналов.

В альтернативном варианте микросхема обработки цифровых сигналов основной полосы содержит блок обработки l/Q-данных, который включает первый модем и второй модем, при этом первый модем подключен к первой микросхеме обработки радиочастотных сигналов через первую линию IQ-данных, вторую линию IQ-данных и первую интерфейсную линию тактового сигнала дискретизации; второй модем подключен ко второй микросхеме обработки радиочастотных сигналов через третью линию IQ-данных и вторую интерфейсную линию тактового сигнала дискретизации.

В альтернативном варианте микросхема обработки цифровых сигналов основной полосы содержит блок однокристальной системы (SOC, system-on-chip), который содержит множество центральных процессоров (CPU, central processing unit) и блоков обработки цифровых сигналов (DSP, digital signal processing), при этом множество CPU и DSP взаимодействуют через коммутационную матрицу, множество модемов с поддержкой различных режимов подключены к портам коммутационной матрицы через матрицу межсоединений, при этом множество модемов с поддержкой различных режимов также подключены к первому модему или второму модему.

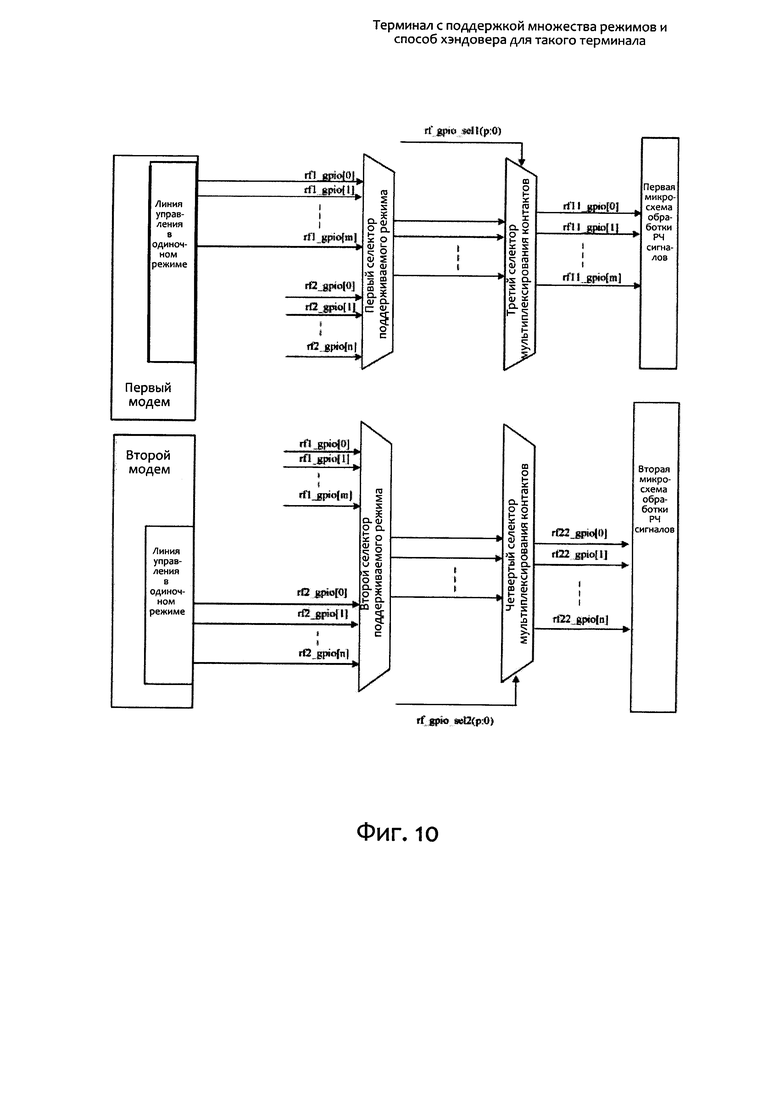

В альтернативном варианте микросхема обработки цифровых сигналов основной полосы содержит блок управления радиочастотными сигналами, который включает блок управления радиочастотным последовательным периферийным интерфейсом (SPI, serial peripheral interface), при этом блок управления радиочастотным интерфейсом SPI содержит первый селектор одного/двух режимов, второй селектор одного/двух режимов, первый селектор мультиплексирования контактов и второй селектор мультиплексирования контактов, при этом SPI первого модема соответственно подключен к первому селектору одного/двух режимов и второму селектору одного/двух режимов, SPI второго модема соответственно подключен к первому селектору одного/двух режимов и второму селектору одного/двух режимов, первый селектор одного/двух режимов подключен к контакту SPI первой микросхемы обработки радиочастотных сигналов через первый селектор мультиплексирования контактов, второй селектор одного/двух режимов подключен к контакту SPI второй микросхемы обработки радиочастотных сигналов через второй селектор мультиплексирования контактов.

В альтернативном варианте микросхема обработки цифровых сигналов основной полосы содержит блок управления радиочастотными сигналами, который включает универсальный блок управления вводом/выводом радиочастотного сигнала (GPIO, general purpose input output), при этом блок управления GPIO радиочастотного сигнала содержит первый селектор режима, второй селектор режима, третий селектор мультиплексирования контактов и четвертый селектор мультиплексирования контактов, при этом линия управления первого модема соответственно подключена к первому селектору режима и второму селектору режима, линия управления второго модема соответственно подключена к первому селектору режима и второму селектору режима, первый селектор режима подключен к контакту GPIO первой микросхемы обработки радиочастотных сигналов через третий селектор мультиплексирования контактов, и второй селектор режима подключен к контакту GPIO второй микросхемы обработки радиочастотных сигналов через четвертый селектор мультиплексирования контактов.

Способ хэндовера для терминала с поддержкой множества режимов включает:

управление второй микросхемой обработки радиочастотных сигналов, осуществляемое микросхемой обработки цифровых сигналов основной полосы, для выбора второго источника тактовых сигналов в качестве опорного тактового сигнала;

выполнение микросхемой обработки цифровых сигналов основной полосы соответствующего независимого управления модемами с поддержкой различных режимов;

управление первым селектором одного/двух режимов, осуществляемое микросхемой обработки цифровых сигналов основной полосы, для выбора последовательного периферийного интерфейса (SPI) первого модема, при этом первый селектор одного/двух режимов подключен к контакту SPI первой микросхемы обработки радиочастотных сигналов через первый селектор мультиплексирования контактов, и управление вторым селектором одного/двух режимов для выбора SPI второго модема, при этом второй селектор одного/двух режимов подключен к контакту SPI второй микросхемы обработки радиочастотных сигналов через второй селектор мультиплексирования контактов;

управление первым селектором режима, осуществляемое микросхемой обработки цифровых сигналов основной полосы, для выбора универсального интерфейса ввода/вывода (GPIO) первого модема, при этом первый селектор режима подключен к контакту GPIO первой микросхемы обработки радиочастотных сигналов через третий селектор мультиплексирования контактов, и управление вторым селектором режима для выбора GPIO второго модема, при этом второй селектор режима подключен к контакту GPIO второй микросхемы обработки радиочастотных сигналов через четвертый селектор мультиплексирования контактов.

Способ хэндовера для терминала с поддержкой множества режимов включает:

управление второй микросхемой обработки радиочастотных сигналов, осуществляемое микросхемой обработки цифровых сигналов основной полосы, для выбора выходного тактового сигнала первой микросхемы обработки радиочастотных сигналов в качестве опорного тактового сигнала;

выполнение микросхемами обработки цифровых сигналов основной полосы соответствующего независимого управления модемами с поддержкой различных режимов;

управление первым селектором одного/двух режимов, осуществляемое микросхемой обработки цифровых сигналов основной полосы, для выбора последовательного периферийного интерфейса (SPI) первого модема или SPI второго модема, при этом первый селектор одного/двух режимов подключен к контакту SPI первой микросхемы обработки радиочастотных сигналов через первый селектор мультиплексирования контактов, и управление вторым селектором одного/двух режимов для выбора SPI первого модема или SPI второго модема, при этом второй селектор одного/двух режимов подключен к контакту SPI второй микросхемы обработки радиочастотных сигналов через второй селектор мультиплексирования контактов;

управление первым селектором режима, осуществляемое микросхемой обработки цифровых сигналов основной полосы, для выбора универсального интерфейса ввода/вывода (GPIO) первого модема или GPIO второго модема, при этом первый селектор режима подключен к контакту GPIO первой микросхемы обработки радиочастотных сигналов через третий селектор мультиплексирования контактов, и управление вторым селектором режима для выбора GPIO первого модема или GPIO второго модема, при этом второй селектор режима подключен к контакту GPIO второй микросхемы обработки радиочастотных сигналов через четвертый селектор мультиплексирования контактов.

В целом терминал с поддержкой множества режимов согласно варианту осуществления настоящего изобретения может выполнять такие функции, как поддержка одного состояния ожидания и множества режимов, поддержка двух состояний ожидания и множества режимов, поддержка множества режимов с использованием одной карты и поддержка двух состояний ожидания с использованием двух карт, что позволяет удовлетворять текущие требования мобильных операторов и пользователей мобильных терминалов. Две SIM-карты, поддерживающие различные режимы, могут произвольно располагаться в любом гнезде для карт, и USIM/SIM-карта, находящаяся в любом из гнезд для карт, может быть доступна для чтения и записи данных в любом режиме, благодаря чему можно обеспечить функционирование не только с поддержкой множества состояний ожидания и множества режимов, но и переключение в режим поддержки одного состояния ожидания и множества режимов не только при функционировании с двумя состояниями ожидания для двух карт, но также с двумя состояниями ожидания для одной карты.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

На фиг. 1 показана блок-схема архитектуры радиочастотного блока стандартного терминала, поддерживающего два состояния ожидания и два режима.

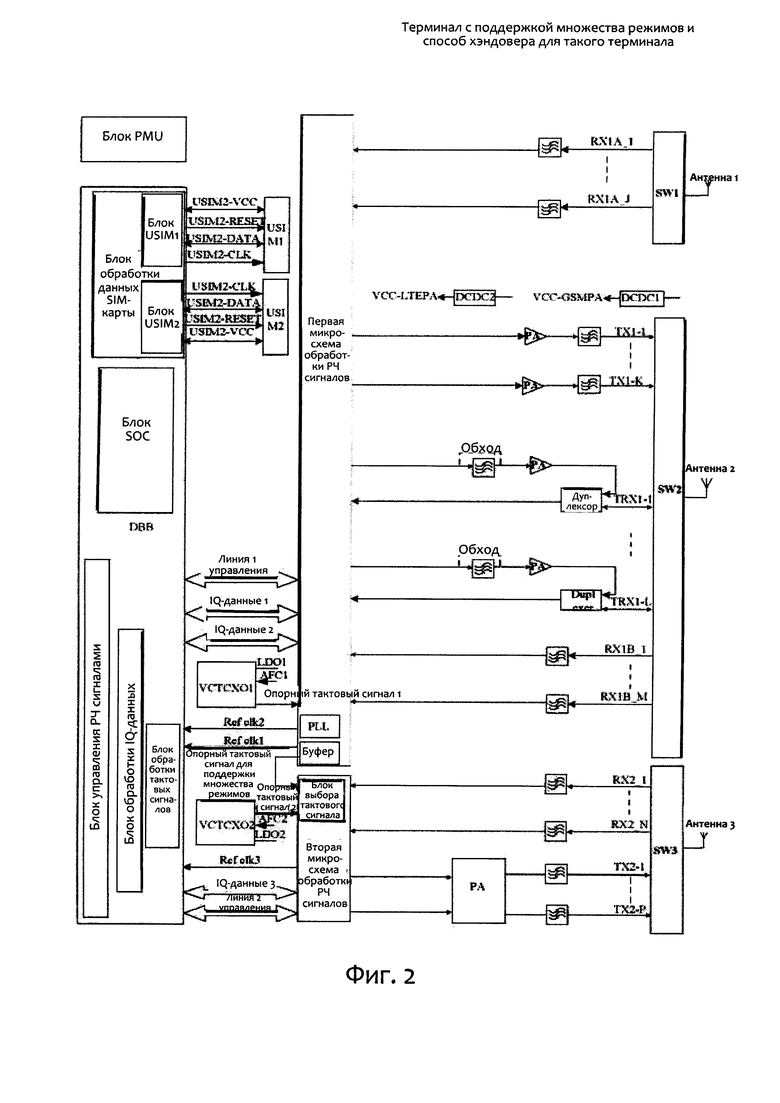

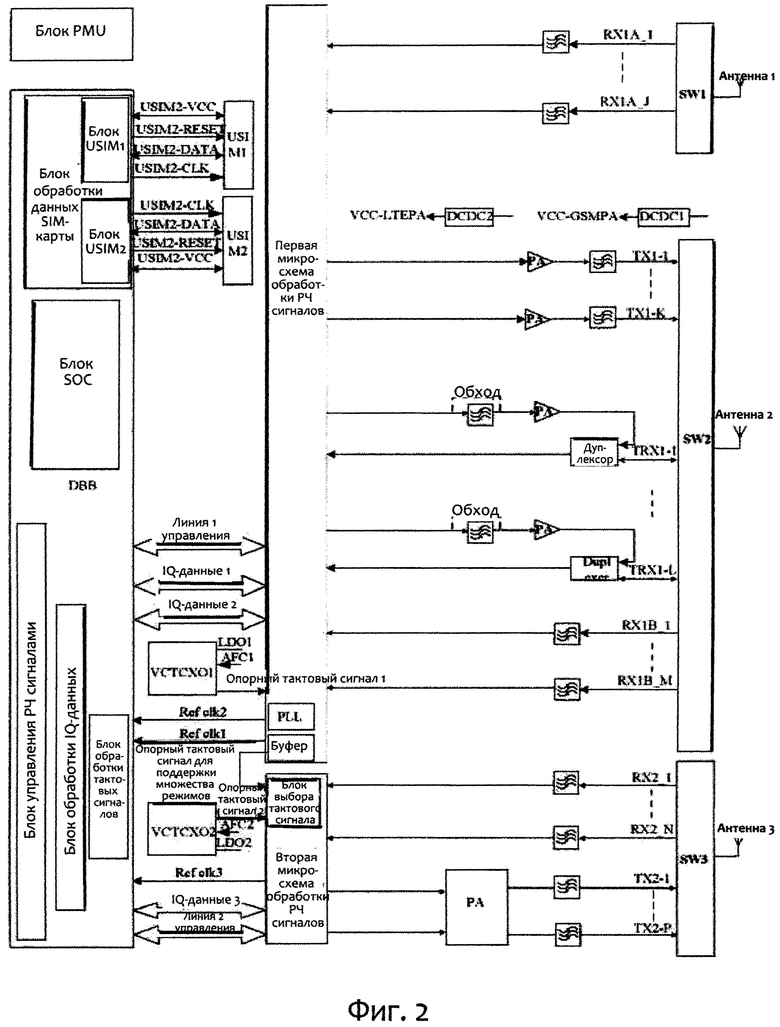

На фиг. 2 показана блок-схема архитектуры радиочастотного блока терминала с поддержкой множества режимов в соответствии с вариантом осуществления настоящего изобретения.

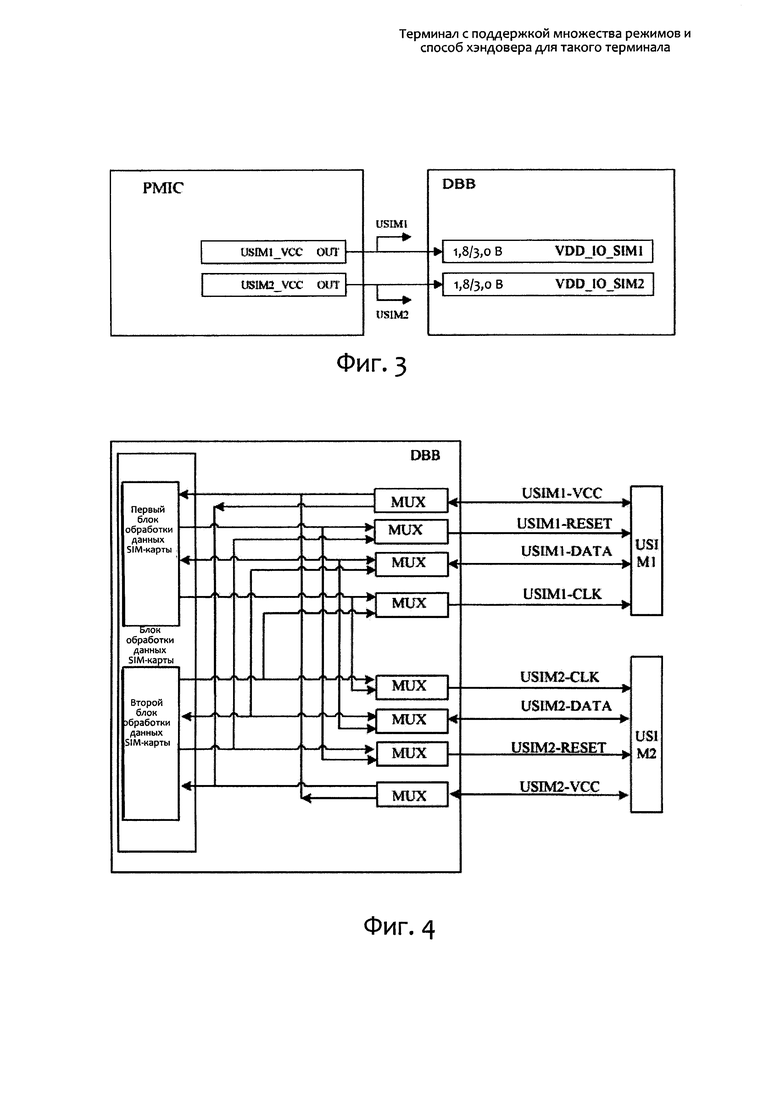

На фиг. 3 показано схематическое представление источника питания в соответствии с вариантом осуществления настоящего изобретения.

На фиг. 4 показана блок-схема блока обработки данных SIM в соответствии с вариантом осуществления настоящего изобретения.

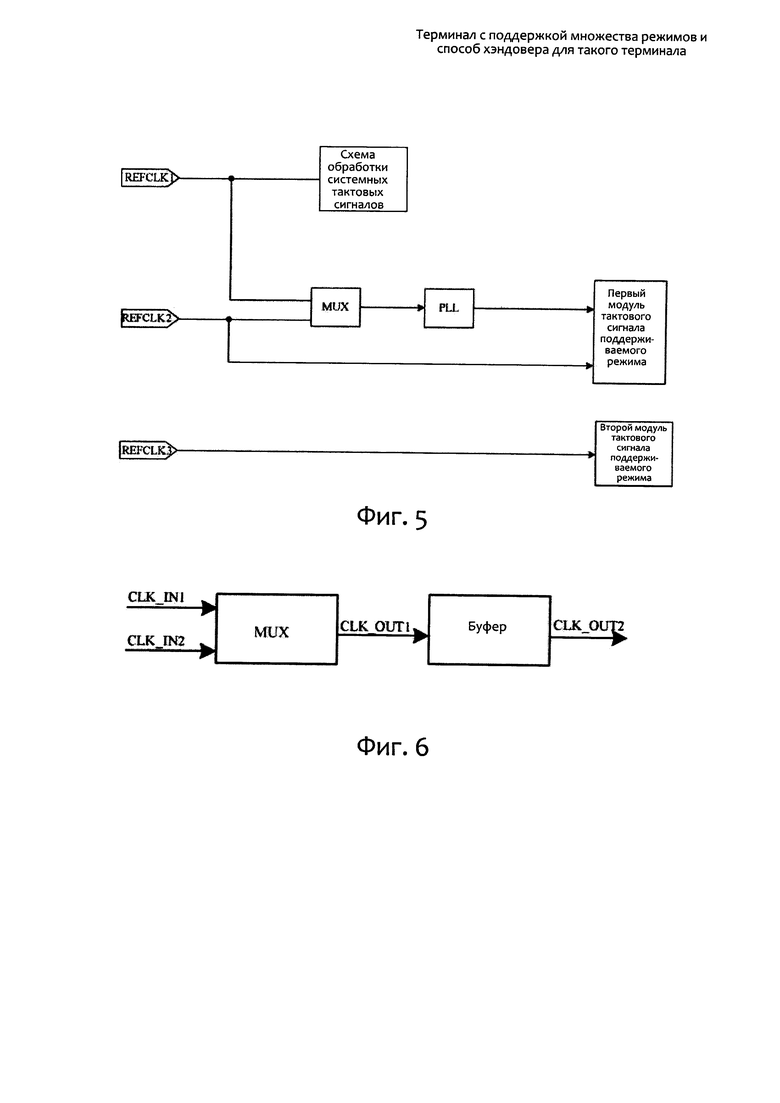

На фиг. 5 показана блок-схема блока обработки тактовых сигналов в соответствии с вариантом осуществления настоящего изобретения.

На фиг. 6 показана блок-схема блока выбора тактового сигнала в соответствии с вариантом осуществления настоящего изобретения.

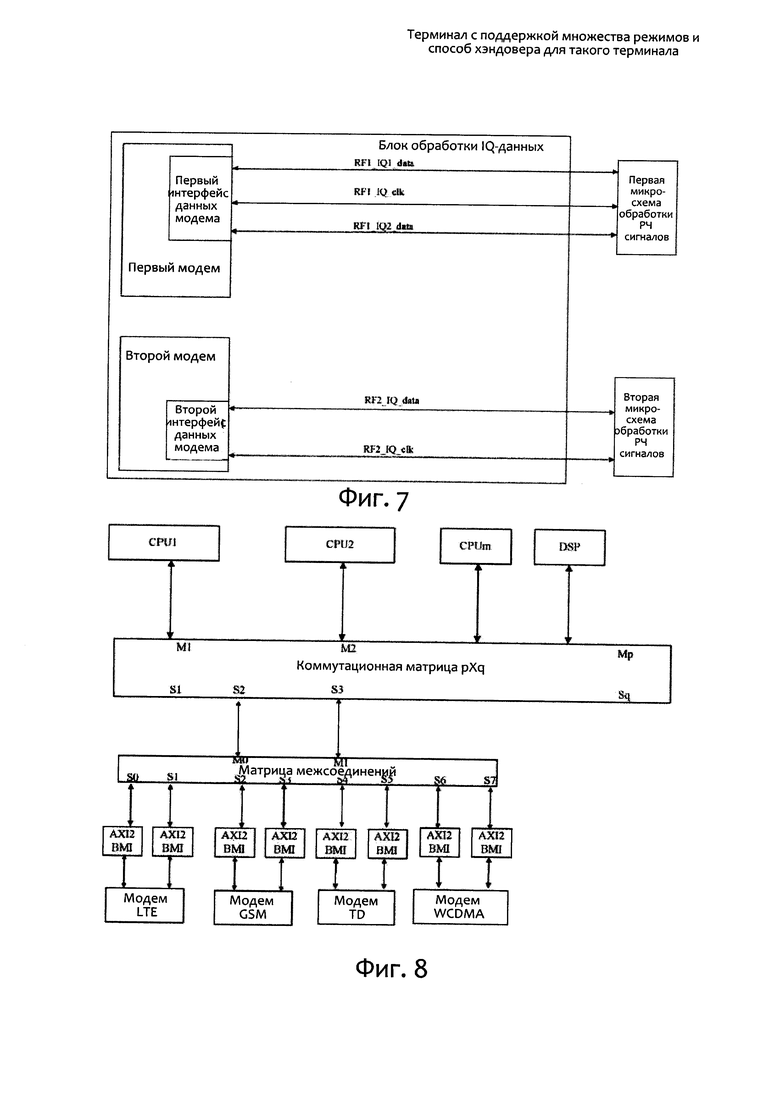

На фиг. 7 показана блок-схема блока обработки IQ-данных в соответствии с вариантом осуществления настоящего изобретения.

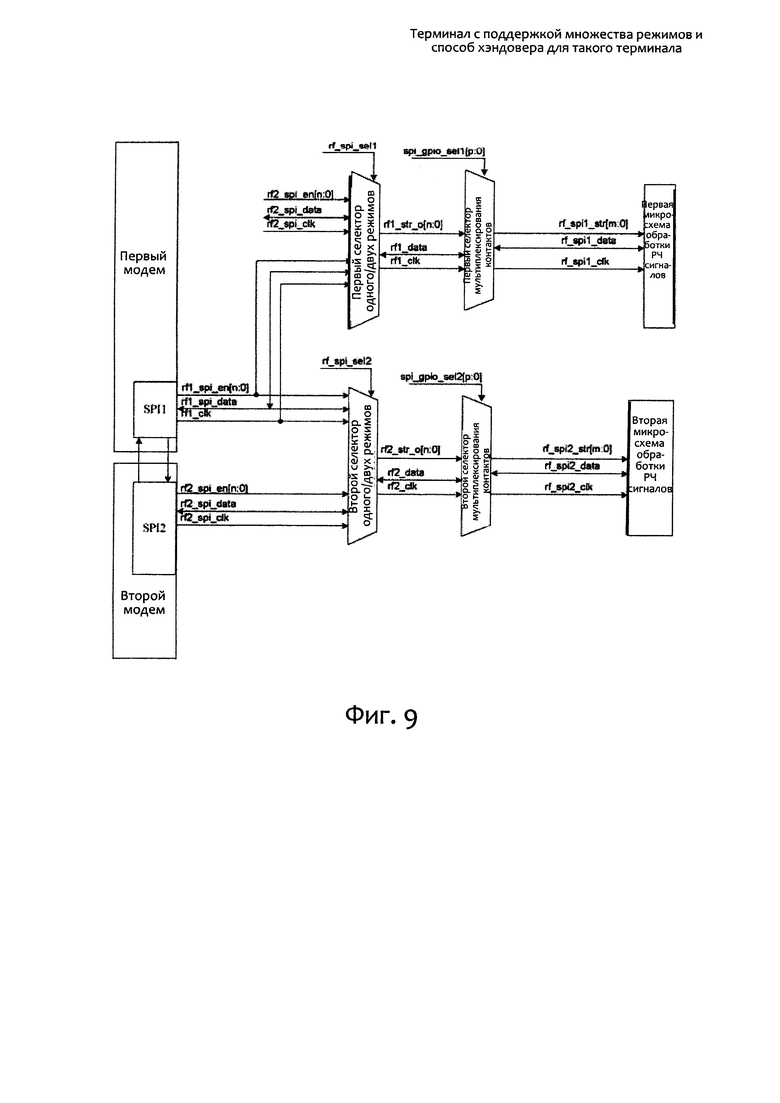

На фиг. 8 показана блок-схема блока SOC в соответствии с вариантом осуществления настоящего изобретения.

На фиг. 9 показана блок-схема блока управления радиочастотным SPI в соответствии с вариантом осуществления настоящего изобретения.

На фиг. 10 показана блок-схема блока управления радиочастотным GPIO в соответствии с вариантом осуществления настоящего изобретения.

ПРЕДПОЧТИТЕЛЬНЫЕ ВАРИАНТЫ ОСУЩЕСТВЛЕНИЯ НАСТОЯЩЕГО ИЗОБРЕТЕНИЯ

Согласно варианту осуществления настоящего изобретения предложен терминал с поддержкой множества режимов, обеспечивающий возможность функционирования с поддержкой множества состояний ожидания и множества режимов, например, с использованием двух состояний ожидания LTE и GSM, при этом терминал, поддерживающий одно состояние ожидания и множество режимов LTE выполняет функции поддержки множества режимов при наличии одной карты (USIM или SIM) и функции поддержки двух состояний ожидания при наличии двух карт.

Помимо отдельных управляемых по напряжению кварцевых генераторов с температурной компенсацией (соответственно, VCTCXO1 и VCTCXO2), расположенных в двух микросхемах обработки радиочастотных сигналов для формирования опорного тактового сигнала, добавлена линия передачи тактовых сигналов для подачи выходного тактового сигнала в качестве опорного сигнала из одной микросхемы обработки радиочастотных сигналов в другую микросхему обработки радиочастотных сигналов, благодаря чему при переключении из режима поддержки двух состояний ожидания с двумя режимами в режим поддержки одного состояния ожидания с двумя режимами две микросхемы обработки радиочастотных сигналов совместно используют один источник опорного тактового сигнала.

Контакты двух SIM-карт подключают к двум блокам обработки данных SIM-карт путем мультиплексирования портов, чтобы одна SIM-карта могла взаимодействовать с любым блоком обработки данных SIM-карт.

Микросхема обработки цифровых сигналов основной полосы (DBB, digital baseband chip) содержит множество центральных процессоров (CPU) и блоков обработки цифровых сигналов (DSP). CPU взаимодействуют с процессорами через коммутационную матрицу (CROSSBAR MATRIX). Модемы, такие как модем LTE, модем TD-SCDMA, модем GSM и модем WCDMA подключены к множеству портов коммутационной матрицы через матрицу межсоединений, благодаря чему любой из CPU может взаимодействовать с любым из модемов и любые два CPU могут одновременно взаимодействовать с двумя модемами.

Для независимого управления двумя микросхемами обработки радиочастотных сигналов в двух состояниях ожидания с двумя режимами и для осуществления унифицированного управления двумя микросхемами обработки радиочастотных сигналов в одном состоянии ожидания с двумя режимами блоки управления, такие как блок управления последовательным периферийным интерфейсом (SPI) и блок управления универсальным интерфейсом ввода/вывода (GPIO), используют селектор одного/двух режимов и селектор мультиплексирования.

Для более четкого изложения целей, технических решений и преимуществ вариантов осуществления настоящего изобретения далее эти варианты описываются более подробно со ссылкой на прилагаемые чертежи. Следует отметить, что варианты осуществления настоящего изобретения, изложенные в данной заявке, и их признаки могут произвольно комбинироваться друг с другом, если это не противоречит сути изобретения.

Как показано на фиг. 2, терминал с поддержкой множества режимов в соответствии с вариантом осуществления настоящего изобретения содержит: микросхему управления питанием (PMU), первую микросхему обработки радиочастотных сигналов, вторую микросхему обработки радиочастотных сигналов, микросхему обработки цифровых сигналов основной полосы, первое гнездо для карты, второе гнездо для карты, первый источник тактовых сигналов и второй источник тактовых сигналов. Использование одной микросхемы обработки цифровых сигналов основной полосы и одной микросхемы управления питанием позволяет сократить площадь, требуемую при монтаже печатной схемы. При использовании двух отдельных гнезд для SIM-карт две SIM-карты для различных режимов могут произвольно располагаться в любом из гнезд, что может не только обеспечить функционирование с поддержкой множества состояний ожидания и множества режимов, но и переключение в режим поддержки одного состояния ожидания и множества режимов.

Блок управления питанием (PMU, Power Management Unit) содержит по меньшей мере два линейных регулятора с малым падением напряжения (LDO, low dropout linear regulator), которые независимо обеспечивают выходное напряжение питания 1,8 В/3,0 В, соответственно, для питания первого и второго гнезд для карт, а также питания для микросхемы обработки цифровых сигналов основной полосы.

Микросхема обработки цифровых сигналов основной полосы используется для передачи и приема синфазных/квадратурных (I/Q, in-phase/quadrature) сигналов LTE, TD-SCDMA, GSM и WCDMA, а также других I/Q-сигналов, управления линиями приема и передачи данных LTE, TD-SCDMA, GSM, WCDMA и т.д. и одновременной обработки I/Q-сигналов LTE и GSM; l/Q-сигналов LTE и TD-SCDMA; I/Q-сигналов LTE и WCDMA и I/Q-сигналов TD-SCDMA и GSM; микросхема обработки цифровых сигналов основной полосы содержит блок обработки тактовых сигналов, блок обработки I/Q-данных, блок управления радиочастотными сигналами, блок обработки данных SIM-карт и блок однокристальной системы (SOC, system-on-chip).

Первая микросхема обработки радиочастотных сигналов по меньшей мере поддерживает прием и передачу радиочастотных сигналов LTE/TD-SCDMA/GSM и содержит буфер тактовых сигналов и схему автоматической фазовой подстройки частоты (PLL, phase lock loop) тактового сигнала; вторая микросхема обработки радиочастотных сигналов по меньшей мере поддерживает прием и передачу радиочастотных сигналов GSM/TD-SCDMA/WCDMA и содержит блок выбора тактового сигнала, в который по линии передачи тактовых сигналов поступает выходной сигнал из буфера тактовых сигналов первой микросхемы обработки радиочастотных сигналов.

Существуют три коммутатора радиочастотных сигналов; один из них используется для переключения между соответствующими частотными диапазонами приемного канала вторичной линии LTE, другой коммутатор используется для переключения между соответствующими частотными диапазонами приемопередающего канала первичной линии LTE, и еще один коммутатор используется для переключения между соответствующими частотными диапазонами другого режима приемопередающего радиочастотного канала.

Первый и второй источники тактовых сигналов соответственно вырабатывают опорные тактовые сигналы для первой и второй микросхем обработки радиочастотных сигналов.

Множество усилителей мощности (PA, power amplifier) усиливают радиочастотный сигнал, поступающий с выхода микросхем обработки радиочастотных сигналов.

Множество высокомощных резистивных фильтров используются для фильтрации внеполосных паразитных сигналов на выходе усилителя мощности.

Множество маломощных резистивных фильтров используются для фильтрации внеполосных паразитных сигналов в приемной линии.

Два преобразователя постоянного тока соответственно подают питание на усилители мощности.

Первое гнездо для карты и второе гнездо для карты могут соответственно независимо использоваться для установки USIM-карты/SIM-карты.

Как показано на фиг. 3, блок управления питанием (PMU) содержит по меньшей мере два независимых LDO, которые, соответствующим образом и независимо, обеспечивают выходное напряжение питания 1,8 В/3,0 В, соответственно для питания первого и второго гнезд для карт, а также питания для микросхемы обработки цифровых сигналов основной полосы.

Микросхема обработки цифровых сигналов основной полосы используется для передачи и приема I/Q-сигналов LTE, TD-SCDMA, GSM и WCDMA, а также других I/Q-сигналов и может управлять линиями приема и передачи LTE, TD-SCDMA, GSM, WCDMA и так далее и одновременно может обрабатывать I/Q-сигналы LTE и GSM; I/Q-сигналы LTE и TD-SCDMA; I/Q-сигналы LTE и WCDMA и I/Q-сигналы TD-SCDMA и GSM; микросхема обработки цифровых сигналов основной полосы содержит блок обработки тактовых сигналов, блок обработки I/Q-данных, блок управления радиочастотными сигналами, блок обработки данных SIM-карт и блок SOC.

Как показано на фиг. 4, блок обработки данных SIM-карт содержит отдельные первый блок обработки данных SIM-карт и второй блок обработки данных SIM-карт, при этом сигналы (USIM1_VCC, USIM1_RESET, USIM1_DATA, USIM1_CLK, USIM2_VCC, USIM2_RESET, USIM2_DATA, USIM2_CLK) на двух внешних USIM-картах/SIM-картах соответственно подаются на соответствующие контакты микросхемы обработки цифровых сигналов основной полосы, при этом один вывод мультиплексора (MUX, multiplexer) подключен к контакту SIM-карты, а другой вывод MUX соответственно подключен к соответствующим функциональным выводам первого блока обработки данных SIM-карты и второго блока обработки данных SIM-карты. Контакт SIM-карты выбирает подключенный блок управления USIM-картой/SIM-картой через MUX.

Как показано на фиг. 5, блок обработки тактовых сигналов содержит по меньшей мере три входных порта тактовых сигналов, блок обработки системных тактовых сигналов, мультиплексор MUX выбора тактового сигнала, схему автоматической фазовой подстройки частоты (PLL), первый модуль тактовых сигналов поддерживаемого режима, второй модуль тактовых сигналов поддерживаемого режима, первый входной вывод тактового сигнала (REFCLK1), второй входной вывод тактового сигнала (REFCLK2) и третий входной вывод тактового сигнала (REFCLK3), при этом первый и второй модули тактовых сигналов поддерживаемого режима могут представлять собой один из следующих модулей: модуль тактовых сигналов LTE, модуль тактовых сигналов TD-SCDMA, модуль тактовых сигналов GSM, модуль тактовых сигналов WCDMA и т.п., например, первый модуль тактовых сигналов поддерживаемого режима может представлять собой модуль тактовых сигналов LTE/TD-SCDMA/GSM, а второй модуль тактовых сигналов поддерживаемого режима может представлять собой модуль тактовых сигналов GSM/TD-SCDMA/WCDMA. Сигнал REFCLK1 подают в блок обработки системных тактовых сигналов, REFCLK1 совместно с REFCLK2 также подают на входной вывод мультиплексора MUX выбора тактового сигнала, выходной вывод MUX выбора тактового сигнала подключен к входному выводу PLL, выходной вывод PLL подключен к первому модулю тактовых сигналов поддерживаемого режима для формирования рабочего тактового сигнала для первого модуля тактовых сигналов поддерживаемого режима. Сигнал REFCLK2 служит в качестве произвольного тактового сигнала дискретизации и непосредственно подается в первый модуль тактовых сигналов поддерживаемого режима и обеспечивает тактовый сигнал для этого модуля. REFCLK3 обеспечивает рабочий тактовый сигнал для второго модуля тактовых сигналов поддерживаемого режима.

Как показано на фиг. 6, блок выбора тактового сигнала содержит мультиплексор (MUX) и буфер тактовых сигналов. Входной вывод MUX подключен к линии передачи тактовых сигналов и ко второму источнику тактовых сигналов, выходной вывод MUX подключен к входному выводу буфера тактовых сигналов, при этом выходной сигнал буфера тактовых сигналов служит в качестве опорного тактового сигнала для второй микросхемы обработки радиочастотных сигналов. Если терминал работает с поддержкой одного состояния ожидания и множества режимов, в качестве опорного тактового сигнала микросхемы 2 обработки радиочастотных сигналов выбирают сигнал CLKJN1 (подаваемый в линию передачи тактовых сигналов), а если терминал работает с поддержкой двух состояний ожидания и множества режимов, то в качестве опорного тактового сигнала микросхемы 2 обработки радиочастотных сигналов выбирают сигнал CLK_IN2 (подаваемый на второй источник тактовых сигналов).

Как показано на фиг. 7, блок обработки I/Q-данных содержит первый модем, второй модем, три группы интерфейсов IQ-данных и две группы тактовых сигналов дискретизации. Первая микросхема обработки радиочастотных сигналов подключена к первому модему через первую линию IQ-данных (RF1_IQ1_data), вторую линию IQ-данных (RF1_IQ2_data) и первую интерфейсную линию тактового сигнала дискретизации (RF1_IQ_clk), при этом первая микросхема обработки радиочастотных сигналов передает данные с использованием первого модема. Вторая микросхема обработки радиочастотных сигналов подключена ко второму модему через третью линию IQ-данных (RF2_IQ1_data) и вторую интерфейсную линию тактового сигнала дискретизации (RF2_IQ_clk) для передачи данных между второй микросхемой обработки радиочастотных сигналов и вторым модемом.

Как показано на фиг. 8, блок SOC выполняет такие функции, как планирование работы с поддержкой двух состояний ожидания и множества режимов и одного состояния ожидания и множества режимов, обработка данных в двух режимах и выполнение управления терминалом в целом. Этот блок содержит множество центральных процессоров (CPU) и блоков обработки цифровых сигналов (DSP), при этом CPU реализуют взаимодействие между процессорами через коммутационную матрицу (CROSSBAR MATRIX). Множество модемов с поддержкой различных режимов, такие как модем LTE, модем TD-SCDMA, модем GSM, модем WCDMA и т.п., подключены к множеству портов коммутационной матрицы через матрицу межсоединений таким образом, чтобы любой из CPU мог взаимодействовать с любым из модемов и любые два CPU могли одновременно взаимодействовать с двумя модемами. Множество модемов, поддерживающих различные режимы, работают в качестве первого или второго модема для соединения с первым или вторым модемом.

Как показано на фиг. 9, микросхема обработки цифровых сигналов основной полосы содержит блок управления радиочастотными сигналами, который включает блок управления радиочастотным SPI, который внутренне использует селектор мультиплексирования контактов и селектор одного/двух режимов. SPI первого модема разделен на две линии, одна из которых подключена к первому селектору одного/двух режимов, а другая - ко второму селектору одного/двух режимов. SPI второго модема разделен на две линии, одна из которых подключена к первому селектору одного/двух режимов, а другая - ко второму селектору одного/двух режимов. Первый селектор одного/двух режимов подключен к первому селектору мультиплексирования контактов, второй селектор одного/двух режимов подключен ко второму селектору мультиплексирования контактов, при этом первый селектор мультиплексирования контактов подключен к контакту SPI первой микросхемы обработки радиочастотных сигналов, а второй селектор мультиплексирования контактов подключен к контакту SPI второй микросхемы обработки радиочастотных сигналов.

Основное назначение такой структуры заключается в том, что два интерфейса SPI могут независимо управлять двумя радиочастотными модулями в случае поддержки двух состояний ожидания и множества режимов, а один SPI может управлять двумя радиочастотными модулями в случае поддержки одного состояния ожидания и множества режимов.

Как показано на фиг. 10, микросхема обработки цифровых сигналов основной полосы содержит блок управления радиочастотными сигналами, включающий блок управления радиочастотным GPIO, который внутренне использует два селектора мультиплексирования контактов (третий и четвертый селекторы мультиплексирования контактов) и два селектора режима (первый и второй селекторы режима). Линия управления первого модема разделена на две линии, одна из которых подключена к первому селектору режима, а другая подключена ко второму селектору режима.

Линия управления второго модема разделена на две линии, одна из которых подключена ко второму селектору режима, а другая подключена к первому селектору режима. Первый селектор режима подключен к третьему селектору мультиплексирования контактов, при этом третий селектор мультиплексирования контактов подключен к соответствующему контакту GPIO первой микросхемы обработки радиочастотных сигналов. Второй селектор режима подключен к четвертому селектору мультиплексирования контактов, при этом четвертый селектор мультиплексирования контактов подключен к соответствующему контакту GPIO второй микросхемы обработки радиочастотных сигналов.

По существу селектор режима представляет собой группу коммутируемых массивов блоков выбора. Основное назначение такой структуры заключается в том, что два набора GPIO могут независимо управлять двумя радиочастотными модулями в случае поддержки двух состояний ожидания и множества режимов, а один набор GPIO может управлять двумя радиочастотными модулями в случае поддержки одного состояния ожидания и множества режимов.

Алгоритм выполнения рабочей процедуры хэндовера при работе с поддержкой двух активных состояний и двух режимов:

шаг один: микросхема DBB управляет второй микросхемой обработки радиочастотных сигналов для выбора второго источника тактовых сигналов в качестве опорного тактового сигнала второй микросхемы обработки радиочастотных сигналов;

шаг два: центральный процессор DBB через коммутационную матрицу соответствующим образом независимо управляет модемами с одновременным использованием различных режимов,;

шаг три: микросхема DBB управляет первым селектором одного/двух режимов для выбора SPI первого модема, при этом первый селектор одного/двух режимов подключен к контактам SPI первой микросхемы обработки радиочастотных сигналов через первый селектор мультиплексирования контактов, и управляет вторым селектором одного/двух режимов для выбора SPI второго модема, при этом второй селектор одного/двух режимов подключен к контакту SPI второй микросхемы обработки радиочастотных сигналов через второй селектор мультиплексирования контактов;

шаг четыре: микросхема DBB управляет первым селектором режима для выбора GPIO первого модема, при этом первый селектор режима подключен к контакту GPIO первой микросхемы обработки радиочастотных сигналов через третий селектор мультиплексирования контактов, и управляет вторым селектором режима для выбора GPIO второго модема, при этом второй селектор режима подключен к контакту GPIO второй микросхемы обработки радиочастотных сигналов через четвертый селектор мультиплексирования контактов;

шаг пять: осуществляется обычное функционирование с поддержкой множества состояний ожидания, множества режимов и двух активных состояний.

Алгоритм выполнения рабочей процедуры хэндовера при работе с поддержкой одного состояния ожидания и двух режимов:

шаг один: микросхема DBB управляет второй микросхемой обработки радиочастотных сигналов для выбора выходного тактового сигнала первой микросхемы обработки радиочастотных сигналов в качестве опорного тактового сигнала второй микросхемы обработки радиочастотных сигналов;

шаг два: центральный процессор DBB через коммутационную матрицу соответствующим образом независимо управляет модемами с поддержкой различных режимов;

шаг три: микросхема DBB управляет первым селектором одного/двух режимов для выбора SPI первого модема или второго модема, при этом первый селектор одного/двух режимов подключен к контакту SPI первой микросхемы обработки радиочастотных сигналов через первый селектор мультиплексирования контактов, и управляет вторым селектором одного/двух режимов для выбора SPI первого или второго модема, при этом второй селектор одного/двух режимов подключен к контакту SPI второй микросхемы обработки радиочастотных сигналов через второй селектор мультиплексирования контактов;

шаг четыре: микросхема DBB управляет первым селектором режима для выбора GPIO первого или второго модема, при этом первый селектор режима подключен к контакту GPIO первой микросхемы обработки радиочастотных сигналов через третий селектор мультиплексирования контактов, и управляет вторым селектором режима для выбора GPIO первого или второго модема, при этом второй селектор режима подключен к контакту GPIO второй микросхемы обработки радиочастотных сигналов через четвертый селектор мультиплексирования контактов;

шаг пять: осуществляется обычное функционирование с поддержкой одного состояния ожидания и множества режимов.

Очевидно, что специалисту в этой области техники должно быть понятно, что соответствующие модули или шаги в рамках вариантов осуществления настоящего изобретения могут быть реализованы с использованием вычислительных устройств общего назначения, они могут быть интегрированы в отдельное вычислительное устройство или распределены в сети, формируемой множеством вычислительных устройств, в альтернативном варианте они могут быть реализованы посредством программных кодов, исполняемых вычислительными устройствами, таким образом, они могут храниться в запоминающих устройствах и выполняться вычислительными устройствами, или они могут быть выполнены в виде отдельных интегральных микросхем, либо некоторые из этих модулей или шагов могут быть встроены в одну интегральную микросхему для реализации соответствующих функций. Таким образом, настоящее изобретение не ограничено какой-либо конкретной комбинацией аппаратных средств и программного обеспечения.

Приведенное выше описание содержит только предпочтительные варианты осуществления настоящего изобретения и не предназначено для ограничения объема изобретения, и специалисты в этой области техники могут внести в настоящее изобретение различные изменения и модификации. Любые изменения, эквивалентные замены и усовершенствования, не противоречащие сущности и принципам вариантов осуществления настоящего изобретения, не должны выходить за рамки объема настоящего изобретения в соответствии с вариантами его осуществления.

ПРОМЫШЛЕННАЯ ПРИМЕНИМОСТЬ

Терминал с поддержкой множества режимов согласно варианту осуществления настоящего изобретения может выполнять такие функции, как поддержка одного состояния ожидания и множества режимов, поддержка двух состояний ожидания и множества режимов, поддержка множества режимов с использованием одной карты и поддержка двух состояний ожидания с использованием двух карт, что позволяет удовлетворять текущие требования мобильных операторов и пользователей мобильных терминалов. Две SIM-карты, поддерживающие различные режимы, могут произвольно располагаться в любом гнезде для карт, и USIM/SIM-карта, находящаяся в любом из гнезд, может быть доступна для чтения и записи данных в любом режиме, благодаря чему можно обеспечить функционирование не только с поддержкой множества состояний ожидания и множества режимов, но и переключение в режим поддержки одного состояния ожидания и множества режимов не только при функционировании с двумя состояниями ожидания для двух карт, но также с двумя состояниями ожидания для одной карты.

Изобретение относится к области беспроводной связи. Технический результат – функционирование терминала с множеством состояний ожидания и множеством режимов поддержки различных сетей связи и с одним состоянием ожидания и множеством режимов поддержки различных сетей связи. Для этого терминал содержит: микросхему управления питанием, микросхему обработки цифровых сигналов основной полосы, первую микросхему обработки радиочастотных сигналов, вторую микросхему обработки радиочастотных сигналов, первое гнездо для карты, второе гнездо для карты, первый источник тактовых сигналов и второй источник тактовых сигналов. Микросхема управления питанием подключена к микросхеме обработки цифровых сигналов основной полосы, первому гнезду для карты и второму гнезду для карты. Микросхема обработки цифровых сигналов основной полосы также подключена к первому гнезду для карты и второму гнезду для карты и подключена к первой микросхеме обработки радиочастотных сигналов и второй микросхеме обработки радиочастотных сигналов через линию синфазных/квадратурных (I/Q) данных и линию управления соответственно. 3 н. и 8 з.п. ф-лы, 10 ил.

1. Терминал с поддержкой множества режимов различных сетей беспроводной связи, содержащий: микросхему управления питанием, микросхему обработки цифровых сигналов основной полосы, первую микросхему обработки радиочастотных сигналов, вторую микросхему обработки радиочастотных сигналов, первое гнездо для карты, второе гнездо для карты, первый источник тактовых сигналов и второй источник тактовых сигналов, при этом:

микросхема управления питанием подключена к микросхеме обработки цифровых сигналов основной полосы, первому гнезду для карты и второму гнезду для карты для подачи питания на микросхему обработки цифровых сигналов основной полосы, первое гнездо для карты и второе гнездо для карты;

микросхема обработки цифровых сигналов основной полосы также подключена к первому гнезду для карты и второму гнезду для карты и соответственно подключена к первой микросхеме обработки радиочастотных сигналов и второй микросхеме обработки радиочастотных сигналов через линию синфазных/квадратурных (I/Q) сигналов и линию управления для передачи, приема и обработки I/Q-сигналов с использованием поддерживаемых режимов, а также для управления линиями передачи и линиями приема в поддерживаемых режимах;

первый источник тактовых сигналов подключен к первой микросхеме обработки радиочастотных сигналов для формирования опорного тактового сигнала для первой микросхемы обработки радиочастотных сигналов; второй источник тактовых сигналов подключен ко второй микросхеме обработки радиочастотных сигналов для формирования опорного тактового сигнала для второй микросхемы обработки радиочастотных сигналов, при этом линия передачи тактовых сигналов также соединяет первую микросхему обработки радиочастотных сигналов и вторую микросхему обработки радиочастотных сигналов, причем первая микросхема обработки радиочастотных сигналов по линии передачи тактовых сигналов подает для второй микросхемы обработки радиочастотных сигналов выходной тактовый сигнал, служащий в качестве опорного тактового сигнала для второй микросхемы обработки радиочастотных сигналов.

2. Терминал по п. 1, отличающийся тем, что микросхема обработки цифровых сигналов основной полосы содержит блок обработки данных карты модуля идентификации абонента (SIM), при этом блок обработки данных SIM-карты содержит первый блок обработки данных SIM-карты, второй блок обработки данных SIM-карты и мультиплексор (MUX), поддерживающий взаимно-однозначное соответствие каждого контакта первого гнезда для карты и второго гнезда для карты, при этом с одной стороны MUX подключен к соответствующему контакту, а с другой стороны соответственно подключен к функциональным выводам первого блока обработки данных SIM-карты и второго блока обработки данных SIM-карты, которые соответствуют упомянутым контактам.

3. Терминал по п. 1, отличающийся тем, что микросхема обработки цифровых сигналов основной полосы содержит блок обработки тактовых сигналов, который содержит блок обработки системных тактовых сигналов, мультиплексор выбора тактового сигнала, схему автоматической фазовой подстройки частоты (PLL), первый модуль тактовых сигналов поддерживаемого режима, второй модуль тактовых сигналов поддерживаемого режима, первый вывод входа тактового сигнала, второй вывод входа тактового сигнала и третий вывод входа тактового сигнала, при этом:

первый вывод входа тактового сигнала подключен к блоку обработки системных тактовых сигналов для формирования рабочего тактового сигнала для блока обработки системных тактовых сигналов;

первый вывод входа тактового сигнала совместно со вторым выводом входа тактового сигнала также подключен к входному выводу мультиплексора MUX выбора тактового сигнала, выходной вывод мультиплексора MUX выбора тактового сигнала подключен к входному выводу PLL и выходной вывод PLL подключен к первому модулю тактовых сигналов поддерживаемого режима, что обеспечивает формирование рабочего тактового сигнала для первого модуля тактовых сигналов поддерживаемого режима;

второй вывод входа тактового сигнала также непосредственно подключен к первому модулю тактовых сигналов поддерживаемого режима для формирования рабочего тактового сигнала для первого модуля тактовых сигналов поддерживаемого режима;

третий вывод входа тактового сигнала подключен ко второму модулю тактовых сигналов поддерживаемого режима для формирования рабочего тактового сигнала для второго модуля тактовых сигналов поддерживаемого режима.

4. Терминал по п. 3, отличающийся тем, что первый вывод входа тактового сигнала подключен к буферу тактовых сигналов в первой микросхеме обработки радиочастотных сигналов; второй вывод входа тактового сигнала также подключен к схеме автоматической фазовой подстройки частоты тактового сигнала (PLL) в первой микросхеме обработки радиочастотных сигналов; третий вывод входа тактового сигнала также подключен ко второй микросхеме обработки радиочастотных сигналов.

5. Терминал по п. 1, отличающийся тем, что вторая микросхема обработки радиочастотных сигналов содержит блок выбора тактового сигнала, содержащий мультиплексор и буфер тактовых сигналов, при этом входной вывод мультиплексора подключен к линии передачи тактовых сигналов и второму источнику тактовых сигналов, выходной вывод мультиплексора подключен ко входному выводу буфера тактовых сигналов, при этом выходной сигнал буфера тактовых сигналов служит в качестве опорного тактового сигнала второй микросхемы обработки радиочастотных сигналов.

6. Терминал по п. 1, отличающийся тем, что микросхема обработки цифровых сигналов основной полосы содержит блок обработки I/Q-данных, включающий первый модем и второй модем, при этом первый модем подключен к первой микросхеме обработки радиочастотных сигналов через первую линию IQ-данных, вторую линию IQ-данных и первую интерфейсную линию тактового сигнала дискретизации; второй модем подключен ко второй микросхеме обработки радиочастотных сигналов через третью линию IQ-данных и вторую интерфейсную линию тактового сигнала дискретизации.

7. Терминал по п. 6, отличающийся тем, что микросхема обработки цифровых сигналов основной полосы содержит блок однокристальной системы (SOC), который включает множество центральных процессоров (CPU) и блоков обработки цифровых сигналов (DSP), при этом множество CPU и DSP взаимодействуют через коммутационную матрицу, множество модемов с поддержкой различных режимов подключены к портам коммутационной матрицы через матрицу межсоединений, при это множество модемов с поддержкой различных режимов также подключены к первому модему или второму модему.

8. Терминал по п. 6, отличающийся тем, что микросхема обработки цифровых сигналов основной полосы содержит блок управления радиочастотными сигналами, включающий блок управления радиочастотным последовательным периферийным интерфейсом (SPI), при этом блок управления радиочастотным SPI содержит первый селектор одного/двух режимов, второй селектор одного/двух режимов, первый селектор мультиплексирования контактов и второй селектор мультиплексирования контактов, при этом интерфейс SPI первого модема соответственно подключен к первому селектору одного/двух режимов и второму селектору одного/двух режимов и интерфейс SPI второго модема соответственно подключен к первому селектору одного/двух режимов и второму селектору одного/двух режимов, причем первый селектор одного/двух режимов подключен к контакту SPI первой микросхемы обработки радиочастотных сигналов через первый селектор мультиплексирования контактов, а второй селектор одного/двух режимов подключен к контакту SPI второй микросхемы обработки радиочастотных сигналов через второй селектор мультиплексирования контактов.

9. Терминал по п. 6, отличающийся тем, что микросхема обработки цифровых сигналов основной полосы содержит блок управления радиочастотными сигналами, включающий универсальный блок управления вводом/выводом радиочастотного сигнала (GPIO), при этом блок управления GPIO радиочастотного сигнала содержит первый селектор режима, второй селектор режима, третий селектор мультиплексирования контактов и четвертый селектор мультиплексирования контактов, при этом линия управления первого модема соответственно подключена к первому селектору режима и второму селектору режима и линия управления второго модема соответственно подключена к первому селектору режима и второму селектору режима, при этом первый селектор режима подключен к контакту GPIO первой микросхемы обработки радиочастотных сигналов через третий селектор мультиплексирования контактов и второй селектор режима подключен к контакту GPIO второй микросхемы обработки радиочастотных сигналов через четвертый селектор мультиплексирования контактов.

10. Способ хэндовера для терминала с поддержкой множества режимов различных сетей беспроводной связи, включающий:

управление второй микросхемой обработки радиочастотных сигналов, осуществляемое микросхемой обработки цифровых сигналов основной полосы, для выбора второго источника тактовых сигналов в качестве опорного тактового сигнала;

выполнение микросхемой обработки цифрового сигнала основной полосы соответствующего независимого управления модемами с поддержкой различных режимов;

управление первым селектором одного/двух режимов, осуществляемое микросхемой обработки цифрового сигнала основной полосы, для выбора последовательного периферийного интерфейса (SPI) первого модема, при этом первый селектор одного/двух режимов подключен к контакту SPI первой микросхемы обработки радиочастотного сигнала через первый селектор мультиплексирования контактов, и управление вторым селектором одного/двух режимов для выбора SPI второго модема, при этом второй селектор одного/двух режимов подключен к контакту SPI второй микросхемы обработки радиочастотного сигнала через второй селектор мультиплексирования контактов;

управление первым селектором режима, осуществляемое микросхемой обработки цифровых сигналов основной полосы, для выбора универсального интерфейса ввода/вывода (GPIO) первого модема, при этом первый селектор режима подключен к контакту GPIO первой микросхемы обработки радиочастотных сигналов через третий селектор мультиплексирования контактов, и управление вторым селектором режима для выбора GPIO второго модема, при этом второй селектор режима подключен к контакту GPIO второй микросхемы обработки радиочастотных сигналов через четвертый селектор мультиплексирования контактов.

11. Способ хэндовера для терминала с поддержкой множества режимов различных сетей беспроводной связи, включающий:

управление второй микросхемой обработки радиочастотных сигналов, осуществляемое микросхемой обработки цифровых сигналов основной полосы, для выбора выходного тактового сигнала первой микросхемы обработки радиочастотных сигналов в качестве опорного тактового сигнала;

выполнение микросхемами обработки цифровых сигналов основной полосы соответствующего независимого управления модемами с поддержкой различных режимов;

управление первым селектором одного/двух режимов, осуществляемое микросхемой обработки цифрового сигнала основной полосы, для выбора последовательного периферийного интерфейса (SPI) первого модема или SPI второго модема, при этом первый селектор одного/двух режимов подключен к контакту SPI первой микросхемы обработки радиочастотного сигнала через первый селектор мультиплексирования контактов, и управление вторым селектором одного/двух режимов для выбора SPI второго модема, при этом второй селектор одного/двух режимов подключен к контакту SPI второй микросхемы обработки радиочастотного сигнала через второй селектор мультиплексирования контактов;

управление первым селектором режима, осуществляемое микросхемой обработки цифровых сигналов основной полосы, для выбора универсального ввода/вывода (GPIO) первого модема или GPIO второго модема, при этом первый селектор режима подключен к контакту GPIO первой микросхемы обработки радиочастотных сигналов через третий селектор мультиплексирования контактов, и управление вторым селектором режима для выбора GPIO первого модема или GPIO второго модема, при этом второй селектор режима подключен к контакту GPIO второй микросхемы обработки радиочастотных сигналов через четвертый селектор мультиплексирования контактов.

| СПОСОБ И УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ СТРУКТУРЫ КАДРА ДЛЯ ПОДДЕРЖКИ РАЗЛИЧНЫХ РЕЖИМОВ РАБОТЫ | 2008 |

|

RU2454040C2 |

| ВЫБОР РЕЖИМА ПЕРЕДАЧИ ВО ВРЕМЯ ПРОЦЕДУРЫ ПРОИЗВОЛЬНОГО ДОСТУПА | 2008 |

|

RU2450450C2 |

| CN 102209402 A, 05.10.2011 | |||

| CN 201663637 U, 01.12.2010 | |||

| Способ обработки целлюлозных материалов, с целью тонкого измельчения или переведения в коллоидальный раствор | 1923 |

|

SU2005A1 |

Авторы

Даты

2017-03-24—Публикация

2013-08-21—Подача