Изобретение относится к системам передачи данных, и в частности, к коммутаторам сетей быстрого Ethernet.

Известен декадный мультиплексор локальный сети (патент РФ №2159511 от 10.11.1999). Недостатком данного устройства является то, что оно имеет низкую скорость обработки пакетов в случае значительных длин очередей.

Наиболее близким по технической сущности к заявляемому устройству и выбранным в качестве прототипа является модульный масштабируемый коммутатор (патент РФ №2257678 от 27.07.2005). Изобретение содержит n портов, включающих гальваническое разделение посредством магнитной развязки в трансформаторе, с выходом к экранированной витой паре, соединенное с приемопередатчиком, связанным с блоком управления доступом к передающей среде (MAC), который содержит центральный процессорный элемент с сокращенным набором команд (RISC CPU), MAC+RISC CPU соединен с блоком, являющимся интерфейсом согласно протоколу RS-232, имеющим выход к ПЭВМ, MAC+RISC CPU связан через системную шину с двухпортовым оперативным запоминающим устройством (DPRAM), с динамическим оперативным запоминающим устройством (DRAM), которое взаимодействует с функциональным модулем прямого доступа к памяти (DMA), и со стираемым программным постоянным запоминающим устройством (EPROM), DPRAM взаимодействует с логикой распределения кадров, включающей быстродействующий арбитр, который с одной стороны связан с общей для всех портов скоростной шиной данных, а с другой стороны через быстродействующий арбитр - с общей для всех портов шиной арбитража и управления.

Недостатком прототипа является то, что он имеет низкую скорость обработки пакетов в случае значительных длин очередей, что обуславливается невозможностью агрегированной (совместной) обработки пакетов, передаваемых между идентичными портами.

Задачей изобретения является разработка модульного масштабируемого коммутатора Ethernet с агрегированием пакетов, позволяющего агрегировано (совместно) обрабатывать пакеты, передаваемые между идентичными портами, что приводит к увеличению скорости обработки пакетов в случае значительных длин очередей.

Эта задача решается тем, что модульный масштабируемый коммутатор Ethernet с агрегированием пакетов, содержащий n портов, включающих ФУ1 (магнитная развязка в трансформаторе), выход которого соединен с входом ФУ2 (приемопередатчик), выход которого соединен с входом ФУ11 (блок управления доступом к передающей среде (MAC)), ФУ11 содержит в себе ФУ10 (центральный процессорный элемент с сокращенным набором команд (RISC CPU)), выход ФУ11 соединен с входом ФУ9 (блок, являющийся интерфейсом согласно протоколу RS-232), а также с входом ФУ5 (двухпортовое оперативное запоминающие устройство (DPRAM)), с входом ФУ4 (динамическое оперативное запоминающие устройство (DRAM)), выход которого в свою очередь соединен с входом ФУ3 (модуль прямого доступа к памяти (DMA)), и с входом ФУ12 (стираемое программное постоянное запоминающие устройство (EPROM)), выход ФУ5 соединен с входом ФУ14 (логика распределения кадров), ФУ14 включает в себя ФУ15 (быстродействующий арбитр), выход ФУ14 соединен с входом ФУ16 (скоростная шина данных), а ФУ15 соединен с входом ФУ17 (шина арбитража и управления), согласно изобретению дополнен ФУ6 (блок агрегированной обработки данных), который содержит в себе ФУ18 (центральный процессор агрегированной обработки пакетов), выход которого соединен со входом ФУ19 (согласующее устройство), выход которого в свою очередь соединен с входом ФУ14 в каждом из n портов.

Новая совокупность существенных признаков, а именно функциональные свойства n введенных блоков агрегированной обработки данных, позволяет увеличить скорость обработки пакетов в случае значительных длин очередей.

Проведенный анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностью признаков, тождественных всем признакам заявленного модульного масштабируемого коммутатора Ethernet с агрегированием пакетов, отсутствуют. Следовательно, заявленное изобретение соответствует условию патентоспособности "новизна".

Заявленное устройство может быть декомпозировано до уровня известных функциональных блоков, модулей, узлов, описанных в литературе, зарегистрированных установленным порядком в патентных реестрах. Следовательно, заявленное изобретение соответствует условию "промышленная применимость".

Заявленное устройство поясняется чертежами:

фиг. 1 - функциональная схема n-портового модульного масштабируемого коммутатора Ethernet с агрегированием пакетов;

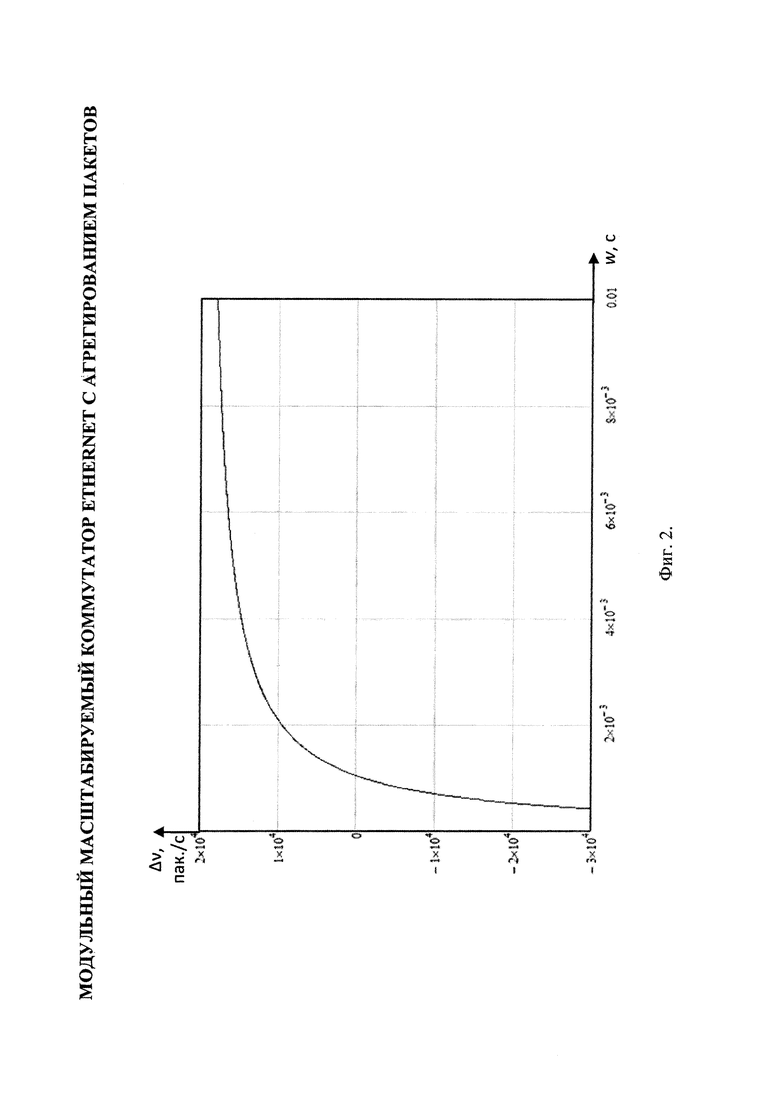

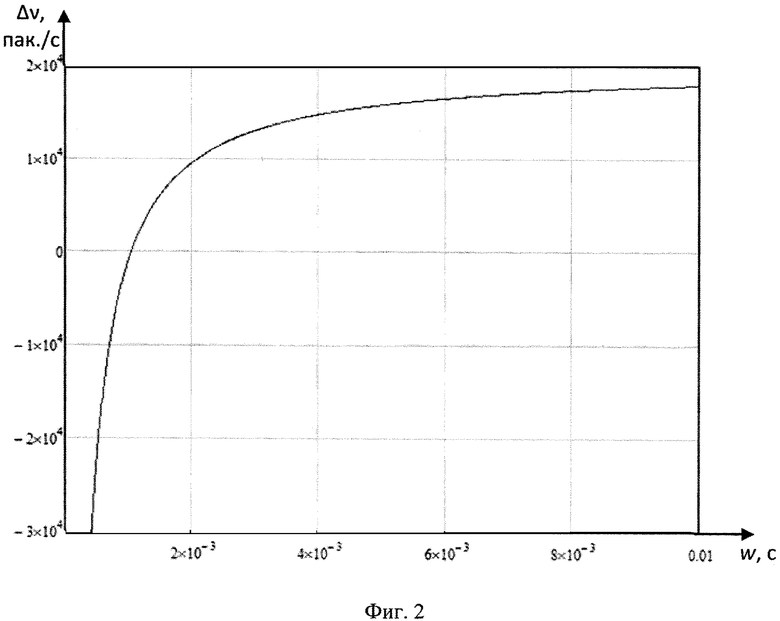

фиг. 2 - зависимость разности скоростей от среднего числа кадров в очереди.

Модульный масштабируемый коммутатор Ethernet с агрегированием пакетов содержит n портов, включающих гальваническое разделение посредством магнитной развязки в трансформаторе 1-1 - 1-n с выходом к экранированной витой паре, соединенное с приемопередатчиком 2-1 - 2-n, связанным с блоком управления доступом к передающей среде (MAC) 11-1 - 11-n, который содержит центральный процессорный элемент с сокращенным набором команд (RISC CPU) 10-1 - 10-n, MAC+RISC CPU соединен с блоком, являющимся интерфейсом согласно протоколу RS-232 9-1 - 9-n, имеющим выход к ПЭВМ, MAC+RISC CPU связан через системную шину 13-1 - 13-n с двухпортовым оперативным запоминающим устройством (DPRAM) 5-1 - 5-n, с динамическим оперативным запоминающим устройством (DRAM) 4-1 - 4-n, которое взаимодействует с функциональным модулем прямого доступа к памяти (DMA) 3-1 - 3-n, и со стираемым программным постоянным запоминающим устройством (EPROM) 12-1 - 12-n, DPRAM взаимодействует с логикой распределения кадров 14-1 - 14-n, включающей быстродействующий арбитр 15-1 - 15-n, который с одной стороны связан (7-1 - 7-n) с общей для всех портов скоростной шиной данных 16, а с другой стороны (8-1 - 8-n) через быстродействующий арбитр - с общей для всех портов шиной арбитража и управления 17, блок агрегированной обработки данных (БАОД) 6-1 - 6-n, который содержит центральный процессор агрегированной обработки пакетов 18-1 - 18-n, соединен с логикой распределения кадров с помощью согласующего устройства 19-1 - 19-n.

Модульный масштабируемый коммутатор Ethernet с агрегированием пакетов работает следующим образом.

Порт после получения и обработки корректного и полного кадра, т.е. после фильтрации потока данных, отработки стратегии, обновляет (внутренний) заголовок этого кадра вместе с соответствующей информацией об отправлении (САМ-вектор) в буфере кадра, то есть в DPRAM 5-i, i=1, …, n, так, чтобы эта структура была промаркирована для отправления. Это выполняется скоростной логикой распределения кадров коммутатора 14-i, которая имеет также доступ к DPRAM 5-i. С помощью блоков агрегированной обработки данных 6-i кадры сортируются в различные группы. Кадры, находящиеся в одной группе, имеют одинаковое направление передачи (идентичные порты отправления и получения). При этом у каждого из кадров заданной группы удаляется вектор САМ, а всей группе кадров назначается один единый модифицированный вектор САМ, содержащий дополнительно информацию о числе кадров в группе. По завершении состязания за доступ к скоростной внутренней шине распределения данных коммутатора логика распределения данных/кадра 14-i теперь передает группу кадров (пакет) к одному или нескольким выходным портам одним пакетом в соответствии с заданным модифицированным вектором САМ. Любой выходной порт независимо решает, в соответствии со статусом его выходного буфера, который вновь является портом, связанным с DPRAM 5-i, принимать или отбросить отправляемую группу кадров. В случае приема пакета блоки агрегированной обработки данных 6-i выходного порта в соответствии со значением модифицированного вектора САМ разбивают пакет на исходные кадры.

Положительный эффект от использования блока агрегированной обработки данных состоит в том, что с помощью него можно уменьшить время обработки кадров в среднем и тем самым повысить скорость обработки пакетов при существенных величинах длин очередей.

Блок агрегированной обработки данных, известное устройство, как вариант выполнено на базе TMS320C28346 с характеристиками: максимальная тактовая частота - 300 МГц, размер ОЗУ - 516 кБ, ширина шины данных - 32 бита [TMS320C28346, TMS320C28345, TMS320C28344 TMS320C28343, TMS320C28342, TMS320C28341 Delfino Microcontrollers. Data Manual TEXAS Instruments. URL: http://www.ti.com/lit/ds/symlink/tms320c28346.pdf]. Согласующее устройство реализовано с помощью модуля гальванического разделения токовой петли [Модуль гальванического разделения токовой петли МГРТП-001. Руководство по эксплуатации. URL: http://lpadevice.ru/files/documentation/61.pdf].

Предположим, что λ - интенсивность поступающего потока в направлении от одного порта к другому (кадр/с); ω - среднее время ожидания в очереди кадра; S - средняя длина заголовка в кадре (бит); В - среднее число информационных бит в кадре. Тогда объем данных неагрегированного потока, ожидающего обслуживания, будет равен:

K1=N⋅(S+В),

а агрегированного:

K2=N-B+S+Y,

где N - среднее число кадров в очереди, a Y - объем поля данных, идентифицирующих число кадров в пакете.

Следовательно, средняя скорость обработки данных агрегированного потока и неагрегированного будет равна соответственно:

.

.

Таким образом, разность между данными скоростями будет равна:

.

.

Так как N=λ⋅ω, то:

.

.

Можно сделать вывод, что при N=λ⋅ω>>1 выигрыш в скорости обработки будет составлять:

,

,

а при N=λ⋅ω<<1 будет наблюдаться проигрыш, равный:

.

.

При условии, что в коммутаторе наблюдаются значительные очереди, скорость поступающего потока данных на порт существенно превышает скорость дополнительно формируемого потока полей данных, идентифицирующих число кадров в пакете, т.е.  . В результате выигрыш в скорости обработки будет значителен, т.е. Δu>>0. Таким образом, использование блоков агрегированной обработки данных позволяет увеличить скорость передачи пакетов в случае значительных длин очередей, т.е. при N=λ⋅ω>>1 и

. В результате выигрыш в скорости обработки будет значителен, т.е. Δu>>0. Таким образом, использование блоков агрегированной обработки данных позволяет увеличить скорость передачи пакетов в случае значительных длин очередей, т.е. при N=λ⋅ω>>1 и  , что доказывает наличие положительного эффекта от использования блока агрегированной обработки данных.

, что доказывает наличие положительного эффекта от использования блока агрегированной обработки данных.

| название | год | авторы | номер документа |

|---|---|---|---|

| МОДУЛЬНЫЙ МАСШТАБИРУЕМЫЙ КОММУТАТОР И СПОСОБ РАСПРЕДЕЛЕНИЯ КАДРОВ В СЕТИ БЫСТРОГО ETHERNET | 2001 |

|

RU2257678C2 |

| СЕТЕВОЙ КОММУТАТОР МОДУЛЬНОЙ ОРГАНИЗАЦИИ (ВАРИАНТЫ) | 2023 |

|

RU2806827C1 |

| СПОСОБ АРБИТРАЖА ДОСТУПА ГРУППЫ АБОНЕНТОВ К ОБЩИМ РЕСУРСАМ | 1999 |

|

RU2153775C1 |

| СИСТЕМА СВЯЗИ | 1991 |

|

RU2111532C1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА И ПЕРЕДАЧИ ДАННЫХ С ВОЗМОЖНОСТЬЮ ОСУЩЕСТВЛЕНИЯ ВЗАИМОДЕЙСТВИЯ С OpenFlow КОНТРОЛЛЕРОМ | 2014 |

|

RU2584471C1 |

| СИСТЕМА УПРАВЛЕНИЯ СВЯЗЬЮ, КОММУТАЦИОННЫЙ УЗЕЛ И СПОСОБ УПРАВЛЕНИЯ СВЯЗЬЮ | 2012 |

|

RU2584449C2 |

| МУЛЬТИСЕРВИСНЫЙ ТЕЛЕКОММУНИКАЦИОННЫЙ КОМПЛЕКС | 2023 |

|

RU2833335C1 |

| ШЛЮЗ ПРЯМЫХ МЕЖСОЕДИНЕНИЙ | 2018 |

|

RU2740035C1 |

| СИСТЕМА СВЯЗИ | 1991 |

|

RU2117405C1 |

| ПРЕДСТАВЛЕНИЕ ФИЛЬТРАЦИИ НАБЛЮДЕНИЯ, АССОЦИИРОВАННОЙ С БУФЕРОМ ДАННЫХ | 2013 |

|

RU2608000C2 |

Изобретение относится к системам передачи данных, и в частности к коммутаторам сетей быстрого Ethernet. Технический результат заключается в увеличении скорости обработки пакетов. Модульный масштабируемый коммутатор Ethernet с агрегированием пакетов дополнен в каждый из n портов блоком агрегированной обработки данных, который содержит центральный процессор агрегированной обработки пакетов, соединенный с помощью согласующего устройства с логикой распределения кадров. Блок агрегированной обработки данных отвечает за анализ и объединение пакетов, имеющих идентичные порты отправления и получения. 2 ил.

Модульный масштабируемый коммутатор Ethernet с агрегированием пакетов, содержащий n портов, включающих гальваническое разделение посредством магнитной развязки в трансформаторе с выходом к экранированной витой паре, соединенное с приемопередатчиком, связанным с блоком управления доступом к передающей среде (MAC), который содержит центральный процессорный элемент с сокращенным набором команд (RISC CPU), MAC+RISC CPU соединен с блоком, являющимся интерфейсом согласно протоколу RS-232, имеющим выход к ПЭВМ, MAC+RISC CPU связан через системную шину с двухпортовым оперативным запоминающим устройством (DPRAM), с динамическим оперативным запоминающим устройством (DRAM), которое взаимодействует с функциональным модулем прямого доступа к памяти (DMA), и со стираемым программным постоянным запоминающим устройством (EPROM), DPRAM взаимодействует с логикой распределения кадров, включающей быстродействующий арбитр, который с одной стороны связан с общей для всех портов скоростной шиной данных, а с другой стороны через быстродействующий арбитр - с общей для всех портов шиной арбитража и управления, отличающийся тем, что введен в каждый из n портов блок агрегированной обработки данных, который содержит центральный процессор агрегированной обработки пакетов, соединенный с помощью согласующего устройства с логикой распределения кадров.

| МОДУЛЬНЫЙ МАСШТАБИРУЕМЫЙ КОММУТАТОР И СПОСОБ РАСПРЕДЕЛЕНИЯ КАДРОВ В СЕТИ БЫСТРОГО ETHERNET | 2001 |

|

RU2257678C2 |

| Способ приготовления лака | 1924 |

|

SU2011A1 |

| US 7286853 B2, 23.10.2007 | |||

| US 20140173128 A1, 19.06.2014. | |||

Авторы

Даты

2017-05-29—Публикация

2015-12-16—Подача