ПРЕДПОСЫЛКИ ДЛЯ СОЗДАНИЯ ИЗОБРЕТЕНИЯ

1. ОБЛАСТЬ ТЕХНИКИ

[0001] Настоящее раскрытие относится к технологии изготовления дисплеев и, более конкретно, к подложке матрицы и жидкокристаллическому дисплею.

2. ОПИСАНИЕ УРОВНЯ ТЕХНИКИ

[0002] Жидкокристаллические дисплеи TFT (на тонкопленочных транзисторах) включают подложки матрицы с расположенным на них некоторым числом пиксельных областей, соответствующих R, G и В (красный-зеленый-синий). Помимо этого, жидкокристаллические дисплеи TFT также включают линии развертки, линии данных, тонкопленочные транзисторы для управления пиксельными областями, запоминающие конденсаторы и жидкокристаллические конденсаторы.

[0003] В настоящее время у больших жидкокристаллических дисплеев с вертикальным выравниванием часто происходит изменение цвета при широком угле обзора.

[0004] Одним обычным решением для преодоления этой проблемы является деление одной пиксельной области на основную область А и субобласть В, и световые пучки не могут проходить через зону между основной областью А и субобластью В. Когда значения шкалы серого у видеосигналов одинаковые, напряжения, прилагаемые к этим двум областям разные, чтобы получить разные кривые γ. Разница в визуальном эффекте кривой γ, сформированной этими двумя областями, при широком угле обзора и узком угле обзора уменьшается, что в значительной степени решает вопрос изменения цвета при широком угле обзора.

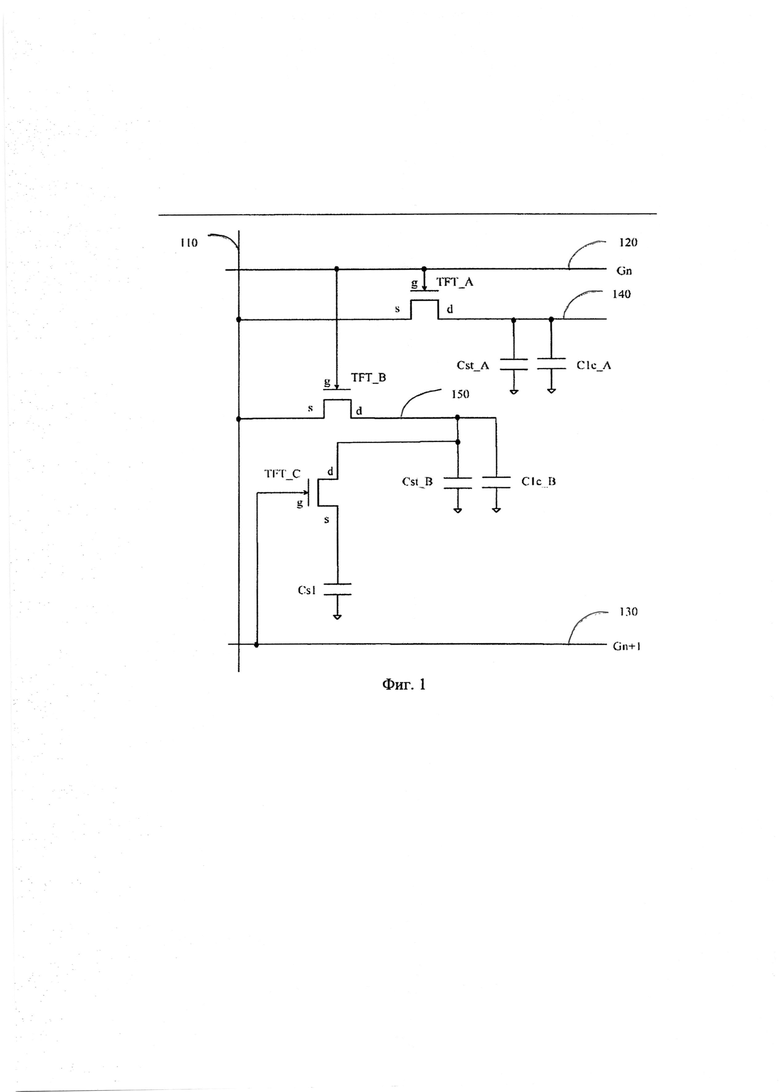

[0005] На Фиг. 1 представлен схематический вид схемы перераспределения заряда 08 (CS) подложки матрицы одного известного ЖК-дисплея TFT. Со ссылкой на Фиг. 1, каждая пиксельная область включает линию данных 110, первую линию развертки 120, вторую линию развертки 130, первый электрод 140 пикселя, второй электрод 150 пикселя, первый тонкопленочный транзистор (TFT_A), второй тонкопленочный транзистор (TFT_B) и третий тонко пленочный транзистор (TFT_C). Линия данных 110 соединяется с истоком TFT_A и TFT_B. Первый электрод 140 пикселя соединяется со стоком TFT_A. Второй электрод 150 пикселя соединяется со стоком TFT_B. Вторая линия развертки 130 соединяется с затвором TFT_C, чтобы подавать сигналы развертки. Сток TFT_C соединяется с вторым электродом 150 пикселя. Исток TFT C соединяется с общим электродом через первый конденсатор (Cs1).

[0006] Возбуждение на ЖК-дисплей TFT подается построчно. Когда сканируется n-я строка, сигналы (Vgn) первой линии развертки 120 имеют высокий уровень, и сигналы (Vgn+1) второй линии развертки 130 имеют низкий уровень. TFT_A и TFT_B включены, и TFT_C отключен. Линия данных 110 заряжает первый запоминающий конденсатор (Cst_A) и первый жидкокристаллический конденсатор (Clc_А), соединенный с первым электродом 140 пикселя, а также второй запоминающий конденсатор (Cst_B) и второй жидкокристаллический конденсатор (Clc_В). Пиксельное напряжение (VA) на первом электроде 140 пикселя и пиксельное напряжение (VB) на втором электроде 150 пикселя заряжаются до тех пор, пока они не сравняются с напряжением (Vd) линии данных 110. Когда сканируется (n+1)-я строка, сигнал (Vgn) первой линии развертки 120 переключается на низкий уровень, и сигнал (Vgn+1) второй линии развертки 130 переключается на высокий уровень. TFT_A и TFT_B отключаются, и TFT_C включается. Пиксельное напряжение (VB) второго электрода 150 пикселя разряжается на общий электрод через первый конденсатор Cs1, чтобы изменить пиксельное напряжение (VB) второго электрода 150 пикселя. Как таковое, пиксельное напряжение (VA) первого электрода 140 пикселя отличается от пиксельного напряжения (VB) второго электрода 150 пикселя, в результате чего достигается низкий эффект изменения цвета (LCS). Предполагая, что VA и VB представляют, соответственно, пиксельное напряжение "области А" и "области В", отношение VB к VA может быть представлено следующим уравнением.

[0007] VB/VA=(Cst_B+Clc_B)/(Cst_B+Clc_B+2Cs1)

[0008] Отношение VB/VA является одним из ключевых факторов, причем конденсатор (Cs1) играет важную роль в определении значения отношения VB к VA.

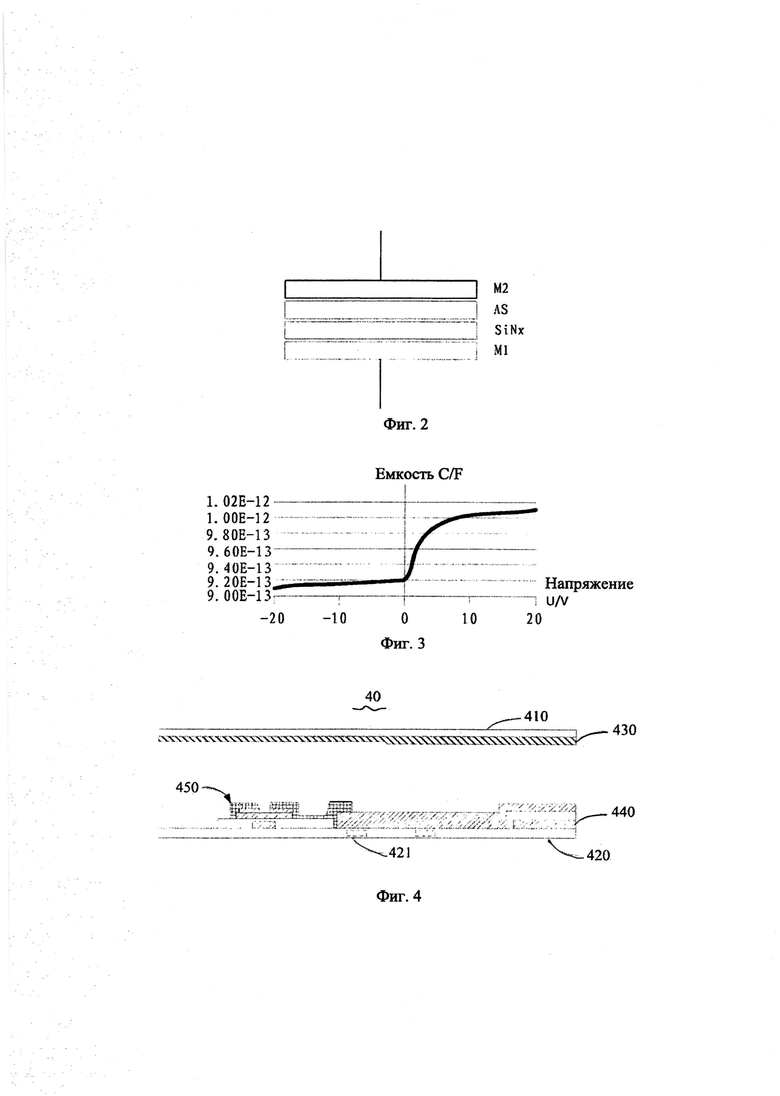

[0009] На Фиг. 2 представлен схематический вид конденсатора (Cs1) с Фиг. 1. Со ссылкой на Фиг. 2, конденсатор (Cs1) включает первый металлический слой (M1), изолирующий слой (SiNx), полупроводниковый слой (a-si) и второй металлический слой (М2). Первый металлический слой (M1) и второй металлический слой (М2) соответствуют металлическому слою затвора и металлическому слою истока подложки матрицы. То есть, металлический затвор TFT-транзистора формируют путем напыления металлического слоя затвора на подложку матрицы, и затем формируют первый металлический слой (Ml) путем травления металлического слоя затвора. Металлический исток TFT-транзистора формируют путем напыления металлического слоя истока на подложку матрицы, и затем второй металлический слой (М2) формируют путем травления металлический слой истока. Изолирующий слой (SiNx) соответствует изолирующему слою затвора на подложке матрицы. Подложка матрицы соответствует полупроводниковому слою TFT на подложке матрицы. То есть, полупроводниковый слой TFT сформирован на подложке матрицы, и для формирования полупроводникового слоя TFT применяют литографический процесс. Помимо этого, литографический процесс применяют для формирования полупроводникового слоя (AS) конденсатора. Обычно второй металлический слой (М2) соединен с напряжением электрода пикселя, и первый металлический слой (M1) соединен с линиями общего электрода.

[0010] На Фиг. 3 представлена кривая емкость-напряжение (C-V) конденсатора (Cs1). Как показано, емкость положительного полупериода больше чем емкость отрицательного полупериода. Положительный полупериод соотносится с одним периодом, в течение которого напряжение электрода пикселя, т.е., VB или VA, больше чем напряжение Vcom, и отрицательный полупериод соотносится с одним периодом, во время которого напряжение электрода пикселя меньше чем напряжение Vcom. Для каждой пиксельной области положительный полупериод и отрицательный полупериод чередуются, чтобы возбуждать ЖК-дисплей TFT. Предпочтительно, отношения VB/VA положительного и отрицательного полупериода остаются такими же. Однако емкость положительного полупериода обычно больше или меньше чем емкость отрицательного полупериода, так что отношение VB/VA положительного полупериода меньше.

[0011] Поэтому схема изменения цвета, такая как CS08, может приводить к асимметричному положительному полупериоду и отрицательному полупериоду из-за разных отношений VB/VA. Помимо эффекта влияния на изменение цвета, схема изменения цвета может приводить к "зависанию" изображения.

РАСКРЫТИЕ ИЗОБРЕТЕНИЯ

[0012] Цель изобретения заключается в том, чтобы предложить подложку матрицы и жидкокристаллический дисплей для компенсации разных отношений напряжения положительного полупериода и отрицательного полупериода двух субобластей. Таким образом улучшается эффект изменения цвета при широком угле обзора, и устраняется зависание изображения.

[0013] В одном аспекте подложка матрицы включает: некоторое число пиксельных элементов, по меньшей мере одну линию общего электрода, по меньшей мере одну линию данных, по меньшей мере одну первую линию развертки и вторую линию развертки, параллельную первой линии развертки, причем первая линия развертки и вторая линия развертки пересекаются с линией данных; соответствующая вторая линия развертки текущего пиксельного элемента такая же как и соответствующая первая линия развертки следующего пиксельного элемента; пиксельный элемент включает первый электрод пикселя, второй электрод пикселя, первый транзистор, второй транзистор, третий транзистор, и управляющая схема, первый транзистор и второй транзистор включают управляющий вывод, входной вывод, и выходной вывод, первая линия развертки соединяется с управляющими выводами первого транзистора и второго транзистора, чтобы подавать сигналы развертки, линия данных соединяется с входными выводами первого транзистора и второго транзистора, первый электрод пикселя соединяется с выходным выводом первого транзистора, второй электрод пикселя соединяется с выходным выводом второго транзистора, третий транзистор включает один управляющий вывод, первый вывод и второй вывод, вторая линия развертки соединяется с управляющим выводом третьего транзистора, чтобы подавать сигналы развертки на третий транзистор, и второй электрод пикселя соединяется с первым выводом третьего транзистора; управляющая схема включает первый конденсатор и второй конденсатор, конструкция первого конденсатора такая же как и конструкция второго конденсатора, первый конденсатор и второй конденсатор включает первый металлический слой, изолирующий слой, полупроводниковый слой и второй металлический слой, расположенные один задругам, второй металлический слой первого конденсатора и первый металлический слой второго конденсатора соединяются с вторым выводом третьего транзистора, и первый металлический слой первого конденсатора и второй металлический слой второго конденсатора соединяются с линией общего электрода; и при обращении положительной полярности и когда вторая линия развертки подводит сигналы развертки, чтобы включить третий транзистор, напряжение второго электрода пикселя снижается первым конденсатором и вторым конденсатором, когда обращается отрицательная полярность и когда вторая линия развертки подводит сигналы развертки, чтобы включить третий транзистор, напряжение второго электрода пикселя увеличивается посредством первого конденсатора и второго конденсатора, емкость первого конденсатора при обращении положительной полярности больше чем емкость первого конденсатора при обращении отрицательной полярности, и емкость второго конденсатора при обращении положительной полярности меньше чем емкость второго конденсатора при обращении отрицательной полярности, так что сумма емкости первого конденсатора и емкости второго конденсатора при обращении положительной полярности равна сумме емкости первого конденсатора и емкости второго конденсатора при обращении отрицательной полярности, при этом значение эффективной емкости управляющей схемы при обращении отрицательной полярности равна значению эффективной емкости управляющей схемы при обращении положительной полярности.

[0014] При этом первым транзистором, вторым транзистором и третьим транзистором являются, соответственно, первый тонкопленочный транзистор (TFT), второй TFT и третий TFT, управляющий вывод, входной вывод и выходной вывод первого транзистора, соответственно, соответствуют затвору, истоку и стоку первого TFT, управляющий вывод, входной вывод и выходной вывод второго транзистора, соответственно, соответствуют затвору, истоку и стоку второго TFT, и управляющий вывод, входной вывод и выходной вывод третьего транзистора, соответственно, соответствуют затвору, истоку и стоку третьего TFT.

[0015] При этом первым транзистором, вторым транзистором и третьим транзистором являются, соответственно, первая пара Дарлингтона или первый триод, вторая пара Дарлингтона или второй триод, и третья пара Дарлингтона или третий триод, управляющий вывод, входной вывод и выходной вывод первого транзистора, соответственно, соответствуют базе, коллектору и эмиттеру первой пары Дарлингтона или первого триода, управляющий вывод, входной вывод и выходной вывод второго транзистора, соответственно, соответствуют базе, коллектору и эмиттеру второй пары Дарлингтона или второго триода, и управляющий вывод, входной вывод и выходной вывод третьего транзистора, соответственно, соответствуют базе, коллектору и эмиттеру третьей пары Дарлингтона или третьего триода.

[0016] В еще одном аспекте подложка матрицы включает: некоторое число пиксельных элементов, по меньшей мере одну линию общего электрода, по меньшей мере одну линию данных, по меньшей мере одну первую линию развертки и вторую линию развертки, параллельную первой линии развертки, при этом первая линия развертки и вторая линия развертки пересекаются с линией данных; пиксельный элемент включает первый электрод пикселя, второй электрод пикселя, первый транзистор, второй транзистор, третий транзистор и управляющую схему, первый транзистор и второй транзистор включают управляющий вывод, входной вывод и выходной вывод, первая линия развертки соединяется с управляющими выводами первого транзистора и второго транзистора, чтобы подавать сигналы развертки, линия данных соединяется с входными выводами первого транзистора и второго транзистора, первый электрод пикселя соединяется с выходным выводом первого транзистора, второй электрод пикселя соединяется с выходным выводом второго транзистора, третий транзистор включает один управляющий вывод, первый вывод и второй вывод, вторая линия развертки соединяется с управляющим выводом третьего транзистора, чтобы подавать сигналы развертки на третий транзистор, второй электрод пикселя соединяется с первым выводом третьего транзистора, и управляющая схема соединяется с вторым выводом третьего транзистора; и пари обращении положительной полярности и отрицательной полярности управляющая схема действует на второй электрод пикселя, когда третий транзистор включен, чтобы изменить напряжение второго положительного полупериода, и значение эффективной емкости управляющей схемы при обращении положительной полярности равно значению эффективной емкости управляющей схемы при обращении отрицательной полярности, так что отношение разницы напряжений между вторым электродом пикселя и линией общего электрода к разнице напряжений между первым электродом пикселя и линией общего электрода при обращении положительной полярности такая же как и отношение разницы напряжений между вторым электродом пикселя и линией общего электрода к разнице напряжений между первым электродом пикселя и линией общего электрода при обращении отрицательной полярности.

[0017] При этом управляющая схема включает первый конденсатор и второй конденсатор, конструкция первого конденсатора такая же как и конструкция второго конденсатора, первый конденсатор и второй конденсатор включают первый металлический слой, изолирующий слой, полупроводниковый слой и второй металлический слой, расположенные один за другим, второй металлический слой первого конденсатора и первый металлический слой второго конденсатора соединяются с вторым выводом третьего транзистора, и первый металлический слой первого конденсатора и второй металлический слой второго конденсатора соединяются с линией общего электрода; и при обращении положительной полярности и когда вторая линия развертки подводит сигналы развертки, чтобы включить третий транзистор, напряжение второго электрода пикселя снижается первым конденсатором и вторым конденсатором, при обращении отрицательной полярности и когда вторая линия развертки подводит сигналы развертки, чтобы включить третий транзистор, напряжение второго электрода пикселя увеличивается посредством первого конденсатора и второго конденсатора, емкость первого конденсатора при обращении положительной полярности больше чем емкость первого конденсатора при обращении отрицательной полярности, и емкость второго конденсатора при обращении положительной полярности меньше чем емкость второго конденсатора при обращении отрицательной полярности, так что сумма емкости первого конденсатора и емкости второго конденсатора при обращении положительной полярности равна сумме емкости первого конденсатора и емкости второго конденсатора при обращении отрицательной полярности, при этом значение эффективной емкости управляющей схемы при обращении отрицательной полярности равно значению эффективной емкости управляющей схемы при обращении положительной полярности.

[0018] При этом первым транзистором, вторым транзистором и третьим транзистором являются, соответственно, первый TFT, второй TFT и третий TFT, управляющий вывод, входной вывод и выходной вывод первого транзистора, соответственно, соответствуют затвору, истоку и стоку первого TFT, управляющий вывод, входной вывод и выходной вывод второго транзистора, соответственно, соответствуют затвору, истоку и стоку второго TFT, и управляющий вывод, входной вывод и выходной вывод третьего транзистора, соответственно, соответствуют затвору, истоку и стоку третьего TFT.

[0019] При этом первым транзистором, вторым транзистором и третьим транзистором являются, соответственно, первая пара Дарлингтона или первый триод, вторая пара Дарлингтона или второй триод, третья пара Дарлингтона или третий триод, управляющий вывод, входной вывод и выходной вывод первого транзистора, соответственно, соответствуют базе, коллектору и эмиттеру первой пары Дарлингтона или первого триода, управляющий вывод, входной вывод и выходной вывод второго транзистора, соответственно, соответствуют базе, коллектору и эмиттеру второй пары Дарлингтона или второго триода, и управляющий вывод, входной вывод и выходной вывод третьего транзистора, соответственно, соответствуют базе, коллектору и эмиттеру третьей пары Дарлингтона или третьего триода.

[0020] При этом соответствующая вторая линия развертки текущего пиксельного элемента такая же, как и соответствующая первая линия развертки следующего пиксельного элемента.

[0021] В еще одном аспекте жидкокристаллический дисплей включает первую подложку, вторую подложку напротив первой подложки, и слой жидкого кристалла между первой подложкой и второй подложкой. Вторая подложка включает: некоторое число пиксельных элементов, по меньшей мере одну линию общего электрода, по меньшей мере одну линию данных, по меньшей мере одну первую линию развертки и вторую линию развертки, параллельную первой линии развертки, при этом первая линия развертки и вторая линия развертки пересекаются с линией данных; пиксельный элемент включает первый электрод пикселя, второй электрод пикселя, первый транзистор, второй транзистор, третий транзистор и управляющую схему, первый транзистор и второй транзистор включают управляющий вывод, входной вывод и выходной вывод, первая линия развертки соединяется с управляющими выводами первого транзистора и второго транзистора, чтобы подавать сигналы развертки, линия данных соединяется с входными выводами первого транзистора и второго транзистора, первый электрод пикселя соединяется с выходным выводом первого транзистора, второй электрод пикселя соединяется с выходным выводом второго транзистора, третий транзистор включает один управляющий вывод, первый вывод и второй вывод, вторая линия развертки соединяется с управляющим выводом третьего транзистора, чтобы подавать сигналы развертки на третий транзистор, второй электрод пикселя соединяется с первым выводом третьего транзистора, и управляющая схема соединяется с вторым выводом третьего транзистора; и при обращении положительной полярности и отрицательной полярности управляющая схема действует на второй электрод пикселя, когда третий транзистор включен, чтобы изменить напряжение второго положительного полупериода, и значение эффективной емкости управляющей схемы при обращении положительной полярности равно значению эффективной емкости управляющей схемы при обращении отрицательной полярности, так что отношение разницы напряжений между вторым электродом пикселя и линией общего электрода к разнице напряжений между первым электродом пикселя и линией общего электрода при обращении положительной полярности такая же как и отношение разницы напряжений между вторым электродом пикселя и линией общего электрода к разнице напряжений между первым электродом пикселя и линией общего электрода при обращении отрицательной полярности.

[0022] При этом управляющая схема включает первый конденсатор и второй конденсатор, конструкция первого конденсатора такая же как и конструкция второго конденсатора, первый конденсатор и второй конденсатор включают первый металлический слой, изолирующий слой, полупроводниковый слой и второй металлический слой, расположенные один за одним, второй металлический слой первого конденсатора и первый металлический слой второго конденсатора соединяются с вторым выводом третьего транзистора, первый металлический слой первого конденсатора и второй металлический слой второго конденсатора соединяются с линией общего электрода; и при обращении положительной полярности и когда вторая линия развертки подводит сигналы развертки, чтобы включить третий транзистор, напряжение второго электрода пикселя снижается первым конденсатором и вторым конденсатором, при обращении отрицательной полярности и когда вторая линия развертки подводит сигналы развертки, чтобы включить третий транзистор, напряжение второго электрода пикселя увеличивается посредством первого конденсатора и второго конденсатора, емкость первого конденсатора при обращении положительной полярности больше чем емкость первого конденсатора при обращении отрицательной полярности, и емкость второго конденсатора при обращении положительной полярности меньше чем емкость второго конденсатора при обращении отрицательной полярности, так что сумма емкости первого конденсатора и емкости второго конденсатора при обращении положительной полярности равна сумме емкости первого конденсатора и емкости второго конденсатора при обращении отрицательной полярности, при этом значение эффективной емкости управляющей схемы при обращении отрицательной полярности равно значению эффективной емкости управляющей схемы при обращении положительной полярности.

[0023] При этом первым транзистором, вторым транзистором и третьим транзистором являются, соответственно, первый TFT, второй TFT и третий TFT, управляющий вывод, входной вывод и выходной вывод первого транзистора, соответственно, соответствуют затвору, истоку и стоку первого TFT, управляющий вывод, входной вывод и выходной вывод второго транзистора, соответственно, соответствуют затвору, истоку и стоку второго TFT, и управляющий вывод, входной вывод и выходной вывод третьего транзистора, соответственно, соответствуют затвору, истоку и стоку третьего TFT.

[0024] При этом первым транзистором, вторым транзистором и третьим транзистором являются, соответственно, первая пара Дарлингтона или первый триод, вторая пара Дарлингтона или второй триод, третья пара Дарлингтона или третий триод, управляющий вывод, входной вывод и выходной вывод первого транзистора, соответственно, соответствуют базе, коллектору и эмиттеру первой пары Дарлингтона или первого триода, управляющий вывод, входной вывод и выходной вывод второго транзистора, соответственно, соответствуют базе, коллектору и эмиттеру второй пары Дарлингтона или второго триода, и управляющий вывод, входной вывод и выходной вывод третьего транзистора, соответственно, соответствуют базе, коллектору и эмиттеру третьей пары Дарлингтона или третьего триода.

[0025] При этом соответствующая вторая линия развертки текущего пиксельного элемента такая же как и соответствующая первая линия развертки следующего пиксельного элемента.

[0026] В свете вышеизложенного, путем добавления одной управляющей схемы отношения напряжений первого электрода пикселя и второго электрода пикселя остаются без изменений, так что эффект изменения цвета при широком угле обзора увеличивается, и зависание изображения устраняется.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

[0027] Фиг. 1 - схематический вид схемы перераспределения заряда подложки матрицы одного известного ЖК-дисплея TFT.

[0028] Фиг. 2 - схематический вид конденсатора (Cs1) с Фиг. 1.

[0029] Фиг. 3 - кривая емкости-напряжения (C-V) конденсатора (Cs1).

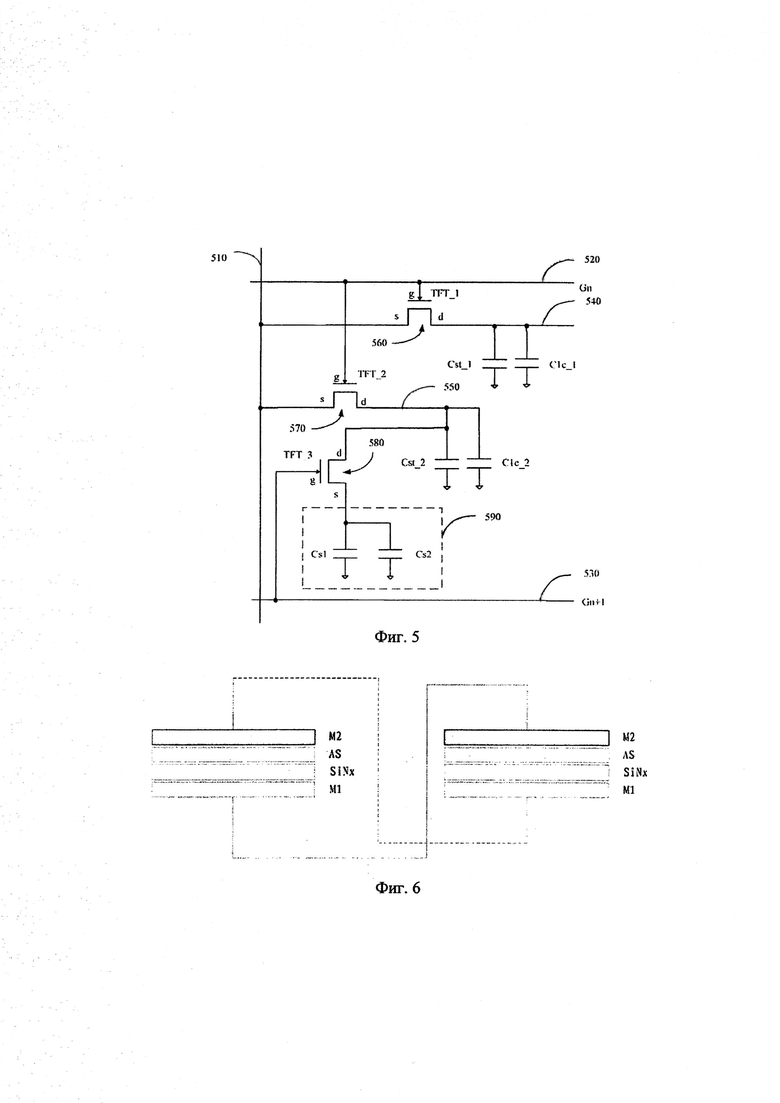

[0030] Фиг. 4 - схематический вид жидкокристаллического дисплея в соответствии с одним вариантом осуществления.

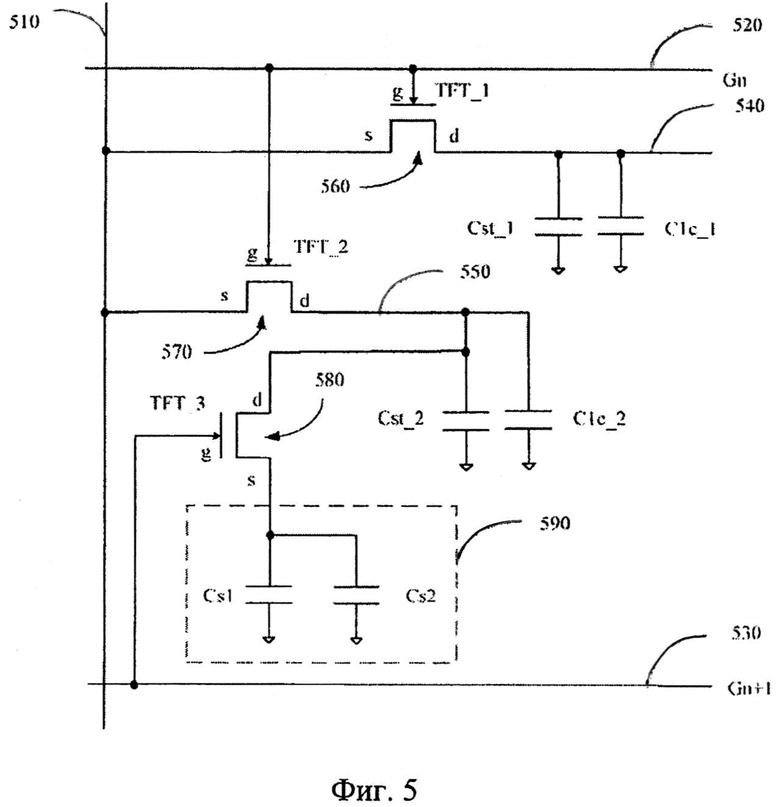

[0031] Фиг. 5 - эквивалентная схема электрода пикселя с Фиг. 4.

[0032] Фиг. 6 - схематический вид управляющей схемы с Фиг. 5.

ПОДРОБНОЕ ОПИСАНИЕ ВАРИАНТОВ ОСУЩЕСТВЛЕНИЯ

[0033] Теперь варианты осуществления изобретения будут описаны более подробно со ссылками на прилагаемые чертежи, на которых показаны эти варианты осуществления изобретения.

[0034] В одном варианте осуществления раскрыты одна подложка матрицы и жидкокристаллический дисплей с такой матрицей. Подложка матрицы включает некоторое число пиксельных элементов.

[0035] На Фиг. 4 представлен схематический вид жидкокристаллического дисплея в соответствии с одним вариантом осуществления. Жидкокристаллический дисплей 40 включает первую подложку 410, вторую подложку 420 напротив первой подложки 410, и слой жидкого кристалла (не показан) между первой подложкой 410 и второй подложкой 420. Первой подложкой 410 является подложка цветового фильтра (CF), имеющая общий электрод 430. Второй подложкой 420 является подложка матрицы с тонкопленочными транзисторами (TFT).

[0036] На Фиг. 5 показана эквивалентная схема электрода пикселя с Фиг. 4. На Фиг. 4 и 5 в качестве примера показан один пиксельный элемент. В этом варианте осуществления TFT-подложка матрицы 420 жидкокристаллического дисплея 40 включает пиксельный элемент 421, линию 440 общего электрода, линию данных 510, первую линию развертки 520 и вторую линию развертки 530, параллельную первой линии развертки 520. Первая линия развертки 520 и вторая линия развертки 530 пересекаются с линией данных 510.

[0037] Пиксельный элемент 421 включает первый электрод пикселя 540, второй электрод пикселя 550, первый транзистор 560, второй транзистор 570, третий транзистор 580 и управляющую схему 590. Первый транзистор 560 и второй транзистор 570 включают один управляющий вывод, один входной вывод и один выходной вывод.

[0038] Первая линия развертки 520 соединяется с управляющими выводами первого транзистора 560 и второго транзистора 570, чтобы подавать сигналы развертки. Линия данных 510 соединяется с входными выводами первого транзистора 560 и второго транзистора 570. Первый электрод пикселя 540 соединяется с выходным выводом первого транзистора 560. Кроме того, первый электрод пикселя 540 соединяется с первым запоминающим конденсатором (Cst_1) и первым жидкокристаллическим конденсатором (Clc_1), соединенными параллельно. Электрод 550 пикселя соединяется с выходным выводом второго транзистора 570. Также, второй электрод 550 пикселя соединяется с вторым запоминающим конденсатором (Cst_2) и вторым жидкокристаллическим конденсатором (Clc_2), соединенными параллельно. Первый жидкокристаллический конденсатор (Clc_1) является эквивалентной емкостью, сформированной жидким кристаллом между первым электродом 540 пикселя и общим электродом 430 первой подложки 410. Второй жидкокристаллический конденсатор (Clc_2) является эквивалентной емкостью, сформированной жидким кристаллом между вторым электродом 550 пикселя и общим электрод 430 первой подложки 410. Первый запоминающий конденсатор (Cst_1) сформирован первым электродом 540 пикселя и линией общего электрода 440 TFT-подложки матрицы 420. Второй запоминающий конденсатор (Cst_2) сформирован вторым электродом пикселя 550 и линией общего электрода 440 TFT-подложки матрицы 420.

[0039] Третий транзистор 580 включает один управляющий вывод, один первый вывод и один второй вывод. Вторая линия развертки 530 соединяется с управляющим выводом третьего транзистора 580, чтобы подавать сигналы развертки. Первый вывод третьего транзистора 580 соединяется с вторым электродом 550 пикселя. Второй вывод третьего транзистора 580 соединяется с управляющей схемой 590.

[0040] На Фиг. 6 представлен схематический вид управляющей схемы с Фиг. 5. Управляющая схема 590 включает первый конденсатор (Cs1) и второй конденсатор (Cs2). Конструкция первого конденсатора (Cs1) такая же как и конструкция второго конденсатора (Cs2). Первый конденсатор (Cs1) и второй конденсатор (Cs2) включают первый металлический слой (M1), изолирующий слой (SiNx), полупроводниковый слой (AS) и второй металлический слой (М2), расположенные один за одним. Второй металлический слой (М2) первого конденсатора (Cs1) и первый металлический слой (M1) второго конденсатора (Cs2) соединяются с вторым выводом третьего транзистора 580. Первый металлический слой (M1) первого конденсатора (Cs1) и второй металлический слой (М2) второго конденсатора (Cs2) соединяются с линией общего электрода 440 TFT-подложки матрицы 420. Первый металлический слой (M1) и второй металлический слой (М2) соответствуют металлическому слою затвора и металлическому слою истока подложки матрицы. То есть, металлический затвор TFT получен напылением металлического слоя затвора на подложку матрицы, и после этого первый металлический слой (M1) формируют путем травления металлического слоя затвора. Металлический исток TFT получен напылением металлического слоя истока на подложку матрицы, и после этого второй металлический слой (М2) формируют путем травления металлического слоя истока. Изолирующий слой (SiNx) соответствует изолирующему слою затвора подложки матрицы. Полупроводниковый слой (AS) соответствует полупроводниковому слою TFT-подложки матрицы. То есть, полупроводниковый слой TFT формируют на подложке матрицы, применяя литографический процесс. Помимо этого, полупроводниковый слой (AS) конденсатора также получают литографическим процессом.

[0041] При обращении положительной полярности и отрицательной полярности управляющая схема 590 действует на второй электрод 550 пикселя, когда третий транзистор 580 включен, чтобы изменить напряжение второго электрода 550 пикселя. Помимо этого, эффективная емкость управляющей схемы 590 не изменяется при обращении положительной полярности или отрицательной полярности, так что отношение разницы напряжений между вторым электродом 550 пикселя и линией общего электрода 440 к разнице напряжений между первым электродом 540 пикселя и линией общего электрода 440 такая же как и отношение разницы напряжений между вторым электродом 550 пикселя и линией общего электрода 440 к разнице напряжений между первым электродом 540 пикселя и линия общего электрода 440.

[0042] Со ссылкой на Фиг. 5, первым транзистором 560, вторым транзистором 570 и третьим транзистором 580 являются, соответственно, первый TFT, второй TFT и третий TFT. Управляющий вывод, входной вывод и выходной вывод первого транзистора 560, соответственно, соответствуют затвору, истоку и стоку первого TFT. Управляющий вывод, входной вывод и выходной вывод второго транзистора 570, соответственно, соответствуют затвору, истоку и стоку второго TFT. Управляющий вывод, входной вывод и выходной вывод третьего транзистора 580, соответственно, соответствуют затвору, истоку и стоку третьего TFT.

[0043] ЖК-дисплей TFT возбуждается построчно. Когда сканируется n-я строка, сигналы (Vgn) первой линии развертки 520 имеют высокий уровень, и сигналы (Vgn+1) второй линии развертки 530 имеют низкий уровень. Первый транзистор 560 и второй транзистор 570 включены, и третий транзистор 580 отключен. Линия данных 510 заряжает первый запоминающий конденсатор (Cst_1) и первый жидкокристаллический конденсатор (Clc_1), которые соединены параллельно, и линия данных 510 заряжает второй запоминающий конденсатор (Cst_2) и второй жидкокристаллический конденсатор (Clc_2), соединенные параллельно, так что напряжение первого электрода пикселя 540 и второго электрода 550 пикселя одинаковое. Когда сканируется (n+1)-я строка, сигналы (Vgn+1) второй линии развертки 530 имеют высокий уровень, и сигналы (Vgn) первой линии развертки 520 имеют высокий уровень. В это время первый транзистор 560 и второй транзистор 570 отключаются, и третий транзистор 580 включается. Поскольку напряжение второго электрода 550 пикселя отличается от напряжения линии общего электрода 440, второй электрод 550 пикселя разряжается на линию общего электрода 440 через первый конденсатор (Cs1) и второй конденсатор (Cs2). Напряжение второго электрода 550 пикселя изменяется. Когда третий транзистор 580 включается при обращении положительной полярности, напряжение второго электрода 550 пикселя больше чем напряжение линии общего электрода 440. Первый конденсатор (Cs1) находится в положительном полупериоде, и второй конденсатор (Cs2) находится в отрицательном полупериоде. Емкость первого конденсатора (Cs1) больше чем емкость второго конденсатора (Cs2). Напряжение второго электрода 550 пикселя снижается через первый конденсатор (Cs1) и второй конденсатор (Cs2). При обращении отрицательной полярности напряжение второго электрода 550 пикселя меньше чем напряжение линии общего электрода 440. Первый конденсатор (Cs1) находится в отрицательном полупериоде, и второй конденсатор (Cs2) находится в положительном полупериоде. Емкость первого конденсатора (Cs1) меньше чем емкость второго конденсатора (Cs2). Напряжение второго электрода 550 пикселя увеличивается посредством первого конденсатора (Cs1) и второго конденсатора (Cs2). Поскольку конструкция и емкость первого конденсатора (Cs1) и второго конденсатора (Cs2) одинаковые, сумма емкости первого конденсатора (Cs1) и емкости второго конденсатора (Cs2) не изменяется при обращении положительной полярности или отрицательной полярности. То есть, эффективная емкость управляющей схемы 590 при обращении положительной полярности равна эффективной емкости управляющей схемы 590 при обращении отрицательной полярности. Как таковое, отношение разницы напряжений между вторым электродом 550 пикселя и линией общего электрода 440 к разнице напряжений между первым электродом 540 пикселя и линией общего электрода 440 при обращении положительной полярности такое же, как и отношение разницы напряжений между вторым электродом 550 пикселя и линией общего электрода 440 к разнице напряжений между первым электродом 540 пикселя и линией общего электрода 440 при обращении отрицательной полярности.

[0044] Когда сканируется (n+2)-я строка, сигналы (Vgn+1) второй линии развертки 530 имеют низкий уровень. Третий транзистор 580 отключен. Второй электрод 550 пикселя прекращает заряжать линию общего электрода 440 через первый конденсатор (Cs1) и второй конденсатор (Cs2). Напряжение второго электрода 550 пикселя не изменяется до следующего кадра. В это время соответствующая вторая линия развертки 530 пиксельного элемента 421 такая же, как и соответствующая первая линия развертки следующего пиксельного элемента.

[0045] Следует сказать, что линия общего электрода 440 TFT-подложки матрицы 420 не должна быть соединена с общим электродом 430 первой подложки 410. В одном варианте осуществления напряжение может быть подано от двух разных источников электропитания, но такие два напряжения будут одинаковыми. Предпочтительно, напряжение, подаваемое на общий электрод 430 и линию общего электрода 440, больше 5 В и меньше 7 В, и напряжение, подаваемое на первую линию развертки 520 и вторую линию развертки 530 больше 20 В и меньше 30 В.

[0046] В одном варианте осуществления первый транзистор 560, второй транзистор 570, и третий транзистор 580 являются тонкопленочными транзисторами. В других вариантах осуществления первым транзистором 560, вторым транзистором 570 и третьим транзистором 580 являются триоды, пары Дарлингтона или другие транзисторы. Управляющий вывод, входной вывод и выходной вывод первого транзистора 560, соответственно, соответствуют базе, коллектору и эмиттеру первой пары Дарлингтона или триода. Управляющий вывод, входной вывод и выходной вывод второго транзистора 570, соответственно, соответствуют базе, коллектору и эмиттеру второй пары Дарлингтона или триода. Управляющий вывод, входной вывод и выходной вывод третьего транзистора 580, соответственно, соответствуют базе, коллектору и эмиттеру третьей пары Дарлингтона или триода.

[0047] В одном варианте осуществления управляющая схема 590 включает первый конденсатор (Cs1) и соответствующие. В других вариантах осуществления управляющая схема 590 включает два или несколько конденсаторов одинаковой конструкции, соединений, емкости с первыми конденсаторами (Cs1) и вторыми конденсаторами (Cs2) для обеспечения того, чтобы эффективная емкость управляющей схемы 590 не изменялась при обращении положительной полярности или отрицательной полярности.

[0048] На Фиг. 5 представлена эквивалентная схема пиксельного элемента с Фиг. 4. Пиксельный элемент включает первый электрод 540 пикселя, второй электрод 550 пикселя, первый транзистор 560, второй транзистор 570, третий транзистор 580 и управляющую схему 590. Первый транзистор 560 и второй транзистор 570 включают управляющий вывод, входной вывод и выходной вывод.

[0049] В свете вышеизложенного, путем добавления одной управляющей схемы отношения напряжений первого электрода пикселя и второго электрода пикселя не изменяются, так что эффект изменения цвета при широком угле обзора усиливается, и зависание изображения устраняется.

[0050] Мы полагаем, что описанные выше варианты осуществления и их преимущества будут поняты из описания, и что будет очевидно, что в них могут быть внесены разные изменения, но без нарушения сущности и объема изобретения или без ущерба для его материальных преимуществ, при этом приведенные выше примеры являются просто предпочтительными примерами вариантов осуществления изобретения.

Изобретение относится к технологиям изготовления дисплеев. Подложка матрицы включает некоторое число пиксельных элементов, по меньшей мере одну линию общего электрода, по меньшей мере одну линию данных, по меньшей мере одну первую линию развертки и одну вторую линию развертки, параллельную первой линии развертки. Первая линия развертки и вторая линия развертки пересекаются с линией данных. Пиксельный элемент включает первый электрод пикселя, второй электрод пикселя, первый транзистор, второй транзистор, третий транзистор и управляющую схему. Путем добавления одной управляющей схемы усиливается эффект изменения цвета при широком угле обзора и устраняется зависание изображения. 3 н. и 10 з.п. ф-лы, 6 ил.

1. Подложка матрицы, включающая:

некоторое число пиксельных элементов, по меньшей мере одну линию общего электрода, по меньшей мере одну линию данных, по меньшей мере одну первую линию развертки и одну вторую линию развертки, параллельную первой линии развертки, и первая линия развертки и вторая линия развертки пересекаются с линией данных;

соответствующая вторая линия развертки текущего пиксельного элемента такая же, как и соответствующая первая линия развертки следующего пиксельного элемента;

пиксельный элемент включает первый электрод пикселя, второй электрод пикселя, первый транзистор, второй транзистор, третий транзистор и управляющую схему, первый транзистор и второй транзистор включают управляющий вывод, входной вывод и выходной вывод, первая линия развертки соединяется с управляющими выводами первого транзистора и второго транзистора, чтобы подавать сигналы развертки, линия данных соединяется с входными выводами первого транзистора и второго транзистора, первый электрод пикселя соединяется с выходным выводом первого транзистора, второй электрод пикселя соединяется с выходным выводом второго транзистора, третий транзистор включает один управляющий вывод, первый вывод и второй вывод, вторая линия развертки соединяется с управляющим выводом третьего транзистора, чтобы подавать сигналы развертки на третий транзистор, и второй электрод пикселя соединяется с первым выводом третьего транзистора;

управляющая схема включает первый конденсатор и второй конденсатор, конструкция первого конденсатора такая же, как и конструкция второго конденсатора, первый конденсатор и второй конденсатор включают первый металлический слой, изолирующий слой, полупроводниковый слой и второй металлический слой, расположенные один за одним, второй металлический слой первого конденсатора и первый металлический слой второго конденсатора соединяются с вторым выводом третьего транзистора, и первый металлический слой первого конденсатора и второй металлический слой второго конденсатора соединяются с линией общего электрода; и

при обращении положительной полярности и когда вторая линия развертки подводит сигналы развертки, чтобы включить третий транзистор, напряжение второго электрода пикселя снижается первым конденсатором и вторым конденсатором, при обращении отрицательной полярности и когда вторая линия развертки подводит сигналы развертки, чтобы включить третий транзистор, напряжение второго электрода пикселя увеличивается посредством первого конденсатора и второго конденсатора, емкость первого конденсатора при обращении положительной полярности больше, чем емкость первого конденсатора при обращении отрицательной полярности, и емкость второго конденсатора при обращении положительной полярности меньше, чем емкость второго конденсатора при обращении отрицательной полярности, так что сумма емкости первого конденсатора и емкости второго конденсатора при обращении положительной полярности равна сумме емкости первого конденсатора и емкости второго конденсатора при обращении отрицательной полярности, как таковое значение эффективной емкости управляющей схемы при обращении отрицательной полярности равно значению эффективной емкости управляющей схемы при обращении положительной полярности.

2. Подложка матрицы по п. 1, отличающаяся тем, что первым транзистором, вторым транзистором и третьим транзистором являются соответственно первый тонкопленочный транзистор (TFT), второй TFT и третий TFT, управляющий вывод, входной вывод и выходной вывод первого транзистора соответственно соответствуют затвору, истоку и стоку первого TFT, управляющий вывод, входной вывод и выходной вывод второго транзистора соответственно соответствуют затвору, истоку и стоку второго TFT, и управляющий вывод, входной вывод и выходной вывод третьего транзистора соответственно соответствуют затвору, истоку и стоку третьего TFT.

3. Подложка матрицы по п. 1, отличающаяся тем, что первым транзистором, вторым транзистором и третьим транзистором являются соответственно первая пара Дарлингтона или первый триод, вторая пара Дарлингтона или второй триод и третья пара Дарлингтона или третий триод, управляющий вывод, входной вывод и выходной вывод первого транзистора соответственно соответствуют базе, коллектору и эмиттеру первой пары Дарлингтона или первого триода, управляющий вывод, входной вывод и выходной вывод второго транзистора соответственно соответствуют базе, коллектору и эмиттеру второй пары Дарлингтона или второго триода, и управляющий вывод, входной вывод и выходной вывод третьего транзистора соответственно соответствуют базе, коллектору и эмиттеру третьей пары Дарлингтона или третьего триода.

4. Подложка матрицы, включающая:

некоторое число пиксельных элементов, по меньшей мере одну линию общего электрода, по меньшей мере одну линию данных, по меньшей мере одну первую линию развертки и одну вторую линию развертки, параллельную первой линии развертки, причем первая линия развертки и вторая линия развертки пересекаются с линией данных;

пиксельный элемент включает первый электрод пикселя, второй электрод пикселя, первый транзистор, второй транзистор, третий транзистор и управляющую схему, первый транзистор и второй транзистор включают управляющий вывод, входной вывод и выходной вывод, первая линия развертки соединяется с управляющими выводами первого транзистора и второго транзистора, чтобы подавать сигналы развертки, линия данных соединяется с входными выводами первого транзистора и второго транзистора, первый электрод пикселя соединяется с выходным выводом первого транзистора, второй электрод пикселя соединяется с выходным выводом второго транзистора, третий транзистор включает один управляющий вывод, первый вывод и второй вывод, вторая линия развертки соединяется с управляющим выводом третьего транзистора, чтобы подавать сигналы развертки на третий транзистор, второй электрод пикселя соединяется с первым выводом третьего транзистора, и управляющая схема соединяется с вторым выводом третьего транзистора; и

отличающаяся тем, что при обращении положительной полярности и отрицательной полярности управляющая схема действует на второй электрод пикселя, когда третий транзистор включен, чтобы изменить напряжение второго положительного полупериода, и значение эффективной емкости управляющей схемы при обращении положительной полярности равно значению эффективной емкости управляющей схемы при обращении отрицательной полярности, так что отношение разницы напряжений между вторым электродом пикселя и линией общего электрода к разнице напряжений между первым электродом пикселя и линией общего электрода при обращении положительной полярности такая же, как и отношение разницы напряжений между вторым электродом пикселя и линией общего электрода к разнице напряжений между первым электродом пикселя и линией общего электрода при обращении отрицательной полярности.

5. Подложка матрицы по п. 4, отличающаяся тем, что управляющая схема включает первый конденсатор и второй конденсатор, конструкция первого конденсатора такая же, как и конструкция второго конденсатора, первый конденсатор и второй конденсатор включают первый металлический слой, изолирующий слой, полупроводниковый слой и второй металлический слой, расположенные один за одним, второй металлический слой первого конденсатора и первый металлический слой второго конденсатора соединяются с вторым выводом третьего транзистора, и первый металлический слой первого конденсатора и второй металлический слой второго конденсатора соединяются с линией общего электрода; и

при обращении положительной полярности и когда вторая линия развертки подводит сигналы развертки, чтобы включить третий транзистор, напряжение второго электрода пикселя снижается первым конденсатором и вторым конденсатором, при обращении отрицательной полярности и когда вторая линия развертки подводит сигналы развертки, чтобы включить третий транзистор, напряжение второго электрода пикселя увеличивается посредством первого конденсатора и второго конденсатора, емкость первого конденсатора при обращении положительной полярности больше, чем емкость первого конденсатора при обращении отрицательной полярности, и емкость второго конденсатора при обращении положительной полярности меньше, чем емкость второго конденсатора при обращении отрицательной полярности, так что сумма емкости первого конденсатора и емкости второго конденсатора при обращении положительной полярности равна сумме емкости первого конденсатора и емкости второго конденсатора при обращении отрицательной полярности, как таковое значение эффективной емкости управляющей схемы при обращении отрицательной полярности равно значению эффективной емкости управляющей схемы при обращении положительной полярности.

6. Подложка матрицы по п. 4, отличающаяся тем, что первым транзистором, вторым транзистором и третьим транзистором являются соответственно первый TFT, второй TFT и третий TFT, управляющий вывод, входной вывод и выходной вывод первого транзистора соответственно соответствуют затвору, истоку и стоку первого TFT, управляющий вывод, входной вывод и выходной вывод второго транзистора соответственно соответствуют затвору, истоку и стоку второго TFT, и управляющий вывод, входной вывод и выходной вывод третьего транзистора соответственно соответствуют затвору, истоку и стоку третьего TFT.

7. Подложка матрицы по п. 4, отличающаяся тем, что первым транзистором, вторым транзистором и третьим транзистором являются соответственно первая пара Дарлингтона или первый триод, вторая пара Дарлингтона или второй триод, третья пара Дарлингтона или третий триод, управляющий вывод, входной вывод и выходной вывод первого транзистора соответственно соответствуют базе, коллектору и эмиттеру первой пары Дарлингтона или первого триода, управляющий вывод, входной вывод и выходной вывод второго транзистора соответственно соответствуют базе, коллектору и эмиттеру второй пары Дарлингтона или второго триода, и управляющий вывод, входной вывод и выходной вывод третьего транзистора соответственно соответствуют базе, коллектору и эмиттеру третьей пары Дарлингтона или третьего триода.

8. Подложка матрицы по п. 4, отличающаяся тем, что соответствующая вторая линия развертки текущего пиксельного элемента такая же, как и соответствующая первая линия развертки следующего пиксельного элемента.

9. Жидкокристаллический дисплей, включающий первую подложку, вторую подложку напротив первой подложки и слой жидкого кристалла между первой подложкой и второй подложкой, отличающийся тем, что вторая подложка включает:

некоторое число пиксельных элементов, по меньшей мере одну линию общего электрода, по меньшей мере одну линию данных, по меньшей мере одну первую линию развертки и одну вторую линию развертки, параллельную первой линии развертки, и первая линия развертки и вторая линия развертки пересекаются с линией данных;

пиксельный элемент включает первый электрод пикселя, второй электрод пикселя, первый транзистор, второй транзистор, третий транзистор и управляющую схему, первый транзистор и второй транзистор включают управляющий вывод, входной вывод и выходной вывод, первая линия развертки соединяется с управляющими выводами первого транзистора и второго транзистора, чтобы подавать сигналы развертки, линия данных соединяется с входными выводами первого транзистора и второго транзистора, первый электрод пикселя соединяется с выходным выводом первого транзистора, второй электрод пикселя соединяется с выходным выводом второго транзистора, третий транзистор включает один управляющий вывод, первый вывод и второй вывод, вторая линия развертки соединяется с управляющим выводом третьего транзистора, чтобы подавать сигналы развертки на третий транзистор, второй электрод пикселя соединяется с первым выводом третьего транзистора, и управляющая схема соединяется с вторым выводом третьего транзистора; и

отличающийся тем, что при обращении положительной полярности и отрицательной полярности управляющая схема действует на второй электрод пикселя, когда третий транзистор включен, чтобы изменить напряжение второго положительного полупериода, и значение эффективной емкости управляющей схемы при обращении положительной полярности равно значению эффективной емкости управляющей схемы при обращении отрицательной полярности, так что отношение разницы напряжений между вторым электродом пикселя и линией общего электрода к разнице напряжений между первым электродом пикселя и линией общего электрода при обращении положительной полярности такая же, как и отношение разницы напряжений между вторым электродом пикселя и линией общего электрода к разнице напряжений между первым электродом пикселя и линией общего электрода при обращении отрицательной полярности.

10. Жидкокристаллический дисплей по п. 9, отличающийся тем, что управляющая схема включает первый конденсатор и второй конденсатор, конструкция первого конденсатора такая же, как и конструкция второго конденсатора, первый конденсатор и второй конденсатор включают первый металлический слой, изолирующий слой, полупроводниковый слой и второй металлический слой, расположенные один за одним, второй металлический слой первого конденсатора и первый металлический слой второго конденсатора соединяются с вторым выводом третьего транзистора, и первый металлический слой первого конденсатора и второй металлический слой второго конденсатора соединяются с линией общего электрода; и

при обращении положительной полярности и когда вторая линия развертки подводит сигналы развертки, чтобы включить третий транзистор, напряжение второго электрода пикселя снижается первым конденсатором и вторым конденсатором, при обращении отрицательной полярности и когда вторая линия развертки подводит сигналы развертки, чтобы включить третий транзистор, напряжение второго электрода пикселя увеличивается посредством первого конденсатора и второго конденсатора, емкость первого конденсатора при обращении положительной полярности больше, чем емкость первого конденсатора при обращении отрицательной полярности, и емкость второго конденсатора при обращении положительной полярности меньше, чем емкость второго конденсатора при обращении отрицательной полярности, так что сумма емкости первого конденсатора и емкости второго конденсатора при обращении положительной полярности равна сумме емкости первого конденсатора и емкости второго конденсатора при обращении отрицательной полярности, как таковое значение эффективной емкости управляющей схемы при обращении отрицательной полярности равно значению эффективной емкости управляющей схемы при обращении положительной полярности.

11. Жидкокристаллический дисплей по п. 9, отличающийся тем, что первым транзистором, вторым транзистором и третьим транзистором являются соответственно первый TFT, второй TFT и третий TFT, управляющий вывод, входной вывод и выходной вывод первого транзистора соответственно соответствуют затвору, истоку и стоку первого TFT, управляющий вывод, входной вывод и выходной вывод второго транзистора соответственно соответствуют затвору, истоку и стоку второго TFT, и управляющий вывод, входной вывод и выходной вывод третьего транзистора соответственно соответствуют затвору, истоку и стоку третьего TFT.

12. Жидкокристаллический дисплей по п. 9, отличающийся тем, что первым транзистором, вторым транзистором и третьим транзистором являются соответственно первая пара Дарлингтона или первый триод, вторая пара Дарлингтона или второй триод, третья пара Дарлингтона или третий триод, управляющий вывод, входной вывод и выходной вывод первого транзистора соответственно соответствуют базе, коллектору и эмиттеру первой пары Дарлингтона или первого триода, управляющий вывод, входной вывод и выходной вывод второго транзистора соответственно соответствуют базе, коллектору и эмиттеру второй пары Дарлингтона или второго триода, и управляющий вывод, входной вывод и выходной вывод третьего транзистора соответственно соответствуют базе, коллектору и эмиттеру третьей пары Дарлингтона или третьего триода.

13. Жидкокристаллический дисплей по п. 9, отличающийся тем, что соответствующая вторая линия развертки текущего пиксельного элемента такая же, как и соответствующая первая линия развертки следующего пиксельного элемента.

| ПОДЛОЖКА АКТИВНОЙ МАТРИЦЫ, ЖИДКОКРИСТАЛЛИЧЕСКАЯ ПАНЕЛЬ, ЖИДКОКРИСТАЛЛИЧЕСКОЕ УСТРОЙСТВО ОТОБРАЖЕНИЯ, ЖИДКОКРИСТАЛЛИЧЕСКИЙ МОДУЛЬ ОТОБРАЖЕНИЯ И ТЕЛЕВИЗИОННЫЙ ПРИЕМНИК | 2009 |

|

RU2475792C2 |

| US 2013141417 A1, 06.06.2013 | |||

| KR 20080036912 A, 29.04.2008 | |||

| CN 102402960 A, 04.04.2012. | |||

Авторы

Даты

2017-06-22—Публикация

2013-08-19—Подача