Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления.

Известны устройства селекции максимального из двух двоичных чисел (см., например, патент РФ 2298219, МПК G06F 7/02, G06F 7/06, 2007 г.), которое содержит два элемента И, два элемента ИЛИ, два импликатора.

К причине, препятствующей достижению указанного ниже технического результата при использовании известного устройства селекции максимального из двух двоичных чисел, относятся ограниченные функциональные возможности, обусловленные тем, что оно позволяет выполнять селекцию только максимального из двух двоичных чисел.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип компаратор двоичных чисел (патент РФ 2300131, МПК G06F 7/02, 27.05.2007 г., содержащий четыре входа устройства, два выхода устройства, два элемента НЕРАВНОЗНАЧНОСТЬ, причем первый вход устройства соединен с первым входом первого элемента НЕРАВНОЗНАЧНОСТЬ, второй вход устройства соединен с первым входом второго элемента НЕРАВНОЗНАЧНОСТЬ.

К причине, препятствующей достижению указанного ниже технического результата при использовании известного компаратора двоичных чисел, относятся ограниченные функциональные возможности, обусловленные тем, что он позволяет выполнять селекцию только минимального из двух двоичных чисел.

Техническим результатом изобретения является расширение функциональных возможностей компаратора двоичных чисел за счет обеспечения возможности выбора среднего из трех двоичных двухразрядных чисел, а также минимального или максимального из двух двоичных двухразрядных чисел.

Указанный технический результат при осуществлении изобретения достигается тем, что компаратор двоичных чисел, содержащий четыре входа устройства, два выхода устройства, два элемента НЕРАВНОЗНАЧНОСТЬ, причем первый вход устройства соединен с первым входом первого элемента НЕРАВНОЗНАЧНОСТЬ, второй вход устройства соединен с первым входом второго элемента НЕРАВНОЗНАЧНОСТЬ, дополнительно содержит пятый и шестой входы устройства, третий элемент НЕРАВНОЗНАЧНОСТЬ, два мажоритарных элемента, элемент НЕ, три мультиплексора, причем первый вход устройства соединен с первым входом первого мажоритарного элемента, второй вход устройства соединен со вторым входом первого мажоритарного элемента, третий вход устройства соединен с третьим входом первого мажоритарного элемента и первым входом третьего элемента НЕРАВНОЗНАЧНОСТЬ, четвертый вход устройства соединен с первым информационным входом первого мультиплексора, пятый вход устройства соединен с первым информационным входом второго мультиплексора, шестой вход устройства соединен с первым информационным входом третьего мультиплексора, выход первого мажоритарного элемента соединен с первым выходом устройства, вторыми входами первого, второго и третьего элементов НЕРАВНОЗНАЧНОСТЬ и через элемент НЕ - со вторыми информационными входами первого, второго и третьего мультиплексоров, выход первого элемента НЕРАВНОЗНАЧНОСТЬ соединен с управляющим входом первого мультиплексора, выход второго элемента НЕРАВНОЗНАЧНОСТЬ соединен с управляющим входом второго мультиплексора, выход третьего элемента НЕРАВНОЗНАЧНОСТЬ соединен с управляющим входом третьего мультиплексора, выход первого мультиплексора соединен с первым входом второго мажоритарного элемента, выход второго мультиплексора соединен со вторым входом второго мажоритарного элемента, выход третьего мультиплексора соединен с третьим входом второго мажоритарного элемента, выход которого соединен со вторым выходом устройства.

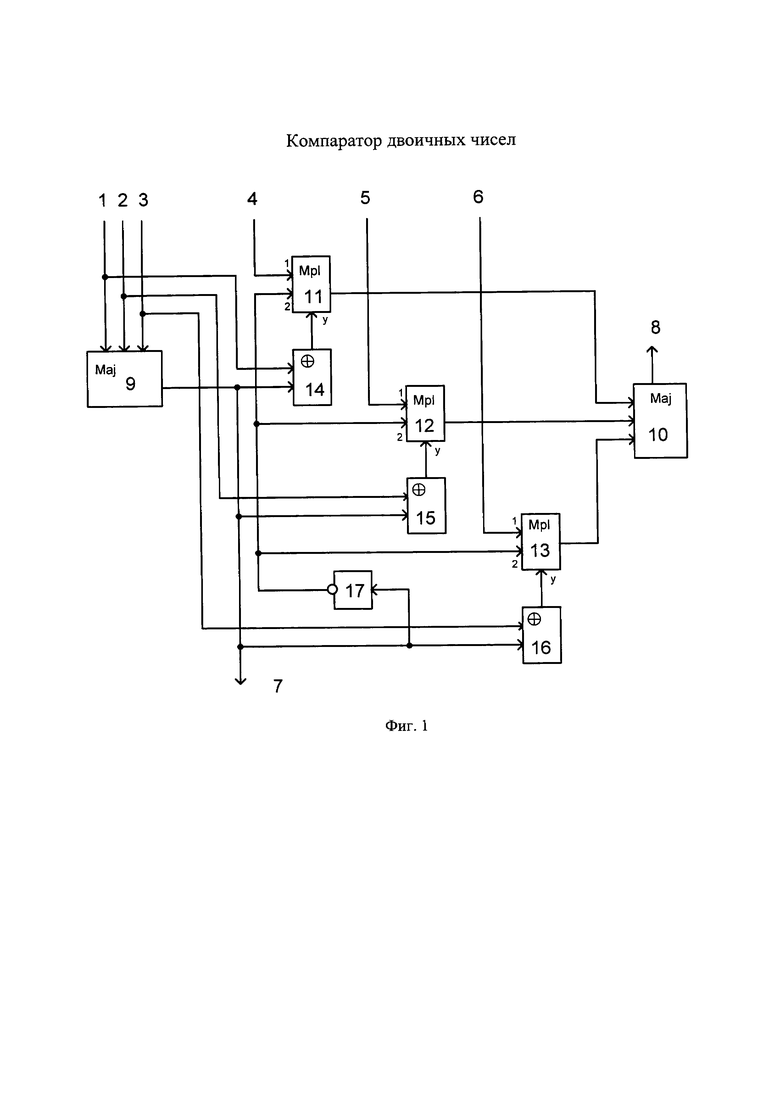

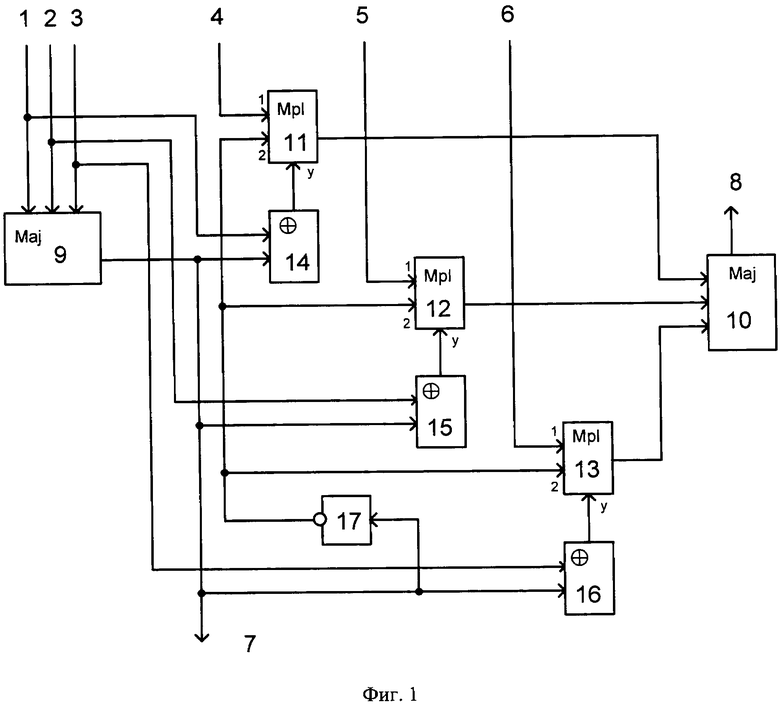

На чертеже представлена схема компаратора двоичных чисел, который содержит шесть входов устройства 1, 2, 3, 4, 5, 6, два выхода устройства 7, 8, два мажоритарных элемента 9, 10, три мультиплексора 11, 12, 13, три элемента НЕРАВНОЗНАЧНОСТЬ 14, 15, 16, элемент НЕ 17. Элементы схемы соединены следующим образом: первый вход устройства 1 соединен с первым входом первого элемента НЕРАВНОЗНАЧНОСТЬ 14 и с первым входом первого мажоритарного элемента 9, второй вход устройства 2 соединен с первым входом второго элемента НЕРАВНОЗНАЧНОСТЬ 15 и со вторым входом первого мажоритарного элемента 9, третий вход устройства 3 соединен с третьим входом первого мажоритарного элемента 9 и первым входом третьего элемента НЕРАВНОЗНАЧНОСТЬ 16, четвертый вход устройства 4 соединен с первым информационным входом первого мультиплексора 11, пятый вход устройства 5 соединен с первым информационным входом второго мультиплексора 12, шестой вход устройства 6 соединен с первым информационным входом третьего мультиплексора 13, выход первого мажоритарного элемента 9 соединен с первым выходом устройства 7, вторыми входами первого, второго и третьего элементов НЕРАВНОЗНАЧНОСТЬ 14, 15, 16 и через элемент НЕ 17 - со вторыми информационными входами первого, второго и третьего мультиплексоров 11, 12, 13, выход первого элемента НЕРАВНОЗНАЧНОСТЬ 14 соединен с управляющим входом первого мультиплексора 11, выход второго элемента НЕРАВНОЗНАЧНОСТЬ 15 соединен с управляющим входом второго мультиплексора 12, выход третьего элемента НЕРАВНОЗНАЧНОСТЬ 16 соединен с управляющим входом третьего мультиплексора 13, выход первого мультиплексора 11 соединен с первым входом второго мажоритарного элемента 10, выход второго мультиплексора 12 соединен со вторым входом второго мажоритарного элемента 10, выход третьего мультиплексора 13 соединен с третьим входом второго мажоритарного элемента 10, выход которого соединен со вторым выходом устройства 8.

Работа предлагаемого компаратора двоичных чисел осуществляется следующим образом.

Устройство сравнивает три двоичных двухразрядных числа А, В и С, двоичные двухразрядные коды которых соответственно (a1a0), (b1b0), (c1c0), где a1, b1, c1 - старшие разряды. На входы устройства эти сигналы подаются следующим образом: на вход 1 - сигнал a1, на вход 2 - сигнал b1, на вход 3 - сигнал c1, на вход 4 - сигнал а0, на вход 5 - сигнал b0, на вход 6 - сигнал с0.

Мажоритарные элементы формируют на своих выходах сигнал, которого больше на входах. Элементы НЕРАВНОЗНАЧНОСТЬ 14, 15, 16 сравнивают значение сигнала на выходе первого мажоритарного элемента 9 со значением сигнала, поступающего на его второй вход, и формируют на своем выходе сигнал «0», если сигналы, поступающие на его входы, равны, и сигнал «1», если они не равны.

Мультиплексоры 11, 12, 13 имеют два информационных входа (1 и 2) и управляющий вход (y). При y=0 на выход мультиплексора передается значение сигнала с первого информационного входа, а при y=1 - со второго информационного входа.

На выходах 7 и 8 формируется двоичный код среднего по положению среди упорядоченных значений сравниваемых чисел двоичного двухразрядного числа. Например, для значений А=1, В=2, С=0 упорядоченные значения в порядке возрастания Упор=(0,1,2), среднее значение будет 1. Для значений А=0, В=1, С=0 упорядоченные значения в порядке возрастания Упор=(0,0,1), среднее значение будет 0, и т.д.

Для выбора наименьшего из двух двоичных двухразрядных чисел А и В на входы 3 и 6 подается сигнал «0», а для выбора наибольшего из двух двоичных двухразрядных чисел А и В на входы 3 и 6 подается сигнал «1». На выходах 7 и 8 устройства формируются коды выбранного двоичного числа.

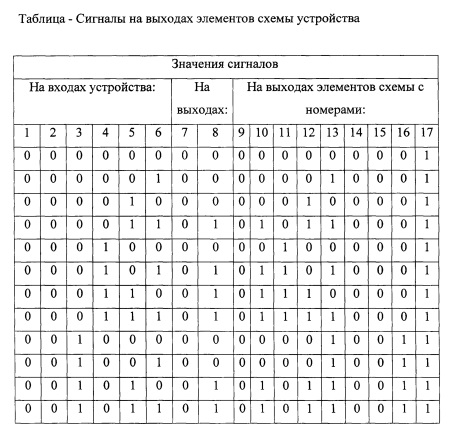

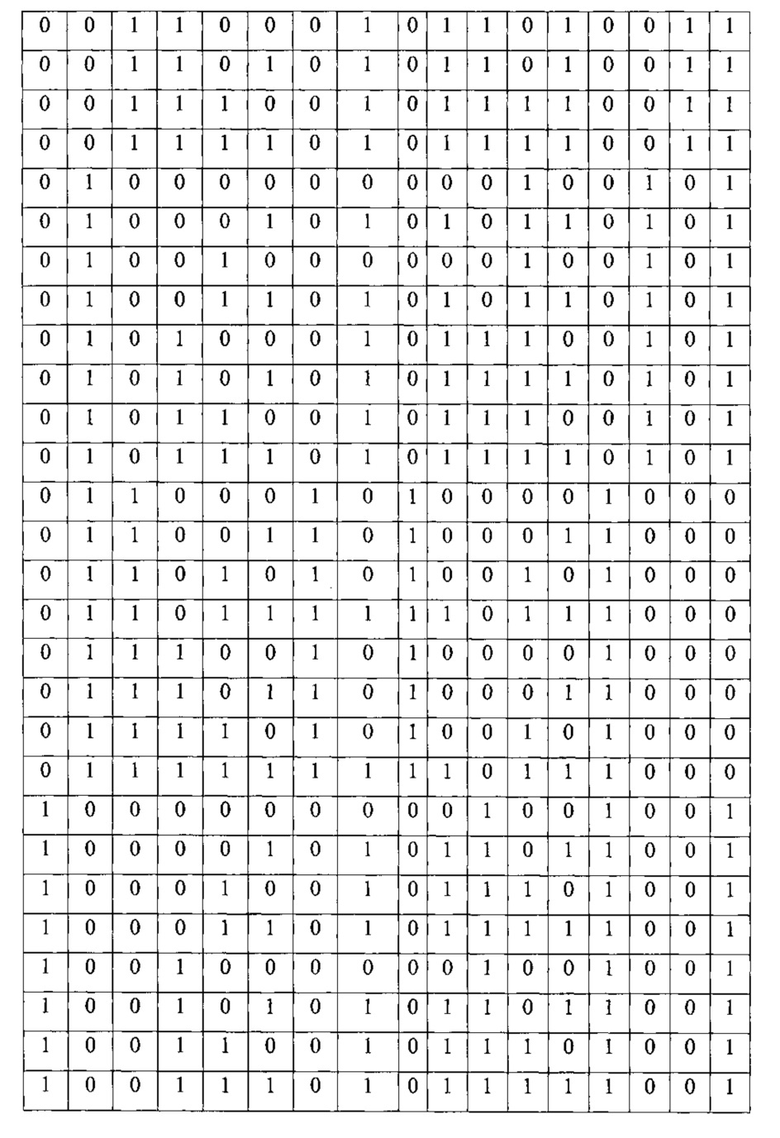

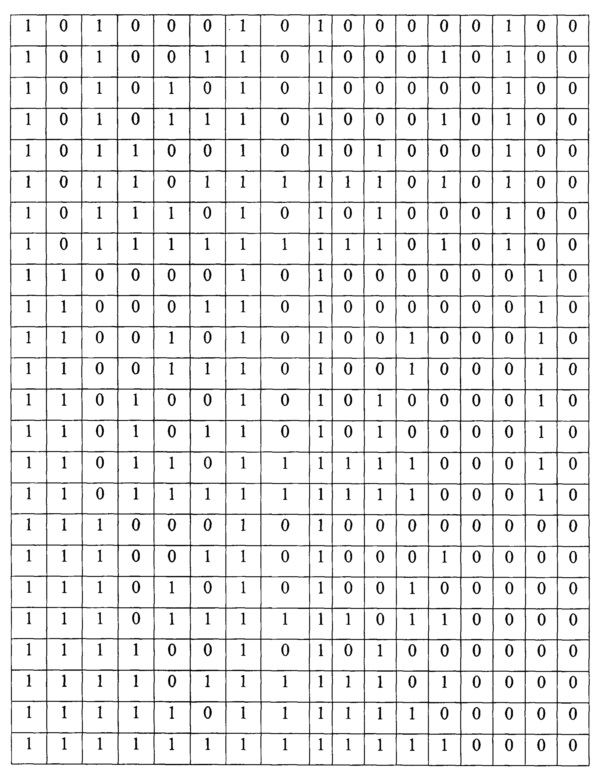

В таблице приведены значения сигналов на выходах устройства и на выходах всех элементов схемы для всех возможных значений входных сигналов.

Сравнение характеристик прототипа и заявляемого устройства показывает, что заявленное устройство имеет более широкие функциональные возможности, т.к. позволяет производить выбор среднего из трех двоичных двухразрядных чисел, а также минимального или максимального из двух двоичных двухразрядных чисел.

Использованные источники

1. Устройство селекции максимального из двух двоичных чисел. RU №2298219 С1, МПК G06F 7/02, G06F 7/06, заявлено 02.12.2005, опубликовано 27.04.2007.

2. Компаратор двоичных чисел. RU №2300131, МПК G06F 7/02, заявлено 10.01.2006, опубликовано 27.05.2007.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО СЕЛЕКЦИИ ЭКСТРЕМАЛЬНОГО ЧИСЛА ИЗ ДВУХ ДВОИЧНЫХ ЧИСЕЛ | 2016 |

|

RU2622841C1 |

| УСТРОЙСТВО СЕЛЕКЦИИ ДВОИЧНЫХ ЧИСЕЛ | 2016 |

|

RU2620991C1 |

| ЛОГИЧЕСКИЙ ПРОЦЕССОР | 2015 |

|

RU2609744C1 |

| УСТРОЙСТВО СЕЛЕКЦИИ ДВОИЧНЫХ ЧИСЕЛ | 2018 |

|

RU2678165C1 |

| УНИВЕРСАЛЬНЫЙ ЛОГИЧЕСКИЙ МОДУЛЬ | 2015 |

|

RU2610678C1 |

| МНОГОФУНКЦИОНАЛЬНЫЙ МАЖОРИТАРНЫЙ МОДУЛЬ | 2016 |

|

RU2626346C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ "ТРИ ИЗ ПЯТИ" | 2016 |

|

RU2628117C1 |

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2015 |

|

RU2609743C1 |

| УНИВЕРСАЛЬНЫЙ МАЖОРИТАРНЫЙ МОДУЛЬ | 2015 |

|

RU2610246C1 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2015 |

|

RU2602331C1 |

Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления. Техническим результатом изобретения является расширение функциональных возможностей компаратора двоичных чисел за счет обеспечения возможности выбора среднего из трех двоичных двухразрядных чисел, а также минимального или максимального из двух двоичных двухразрядных чисел. Компаратор двоичных чисел содержит шесть входов устройства 1, 2, 3, 4, 5, 6, два выхода устройства 7, 8, два мажоритарных элемента 9, 10, три мультиплексора 11, 12, 13, три элемента НЕРАВНОЗНАЧНОСТЬ 14, 15, 16, элемент НЕ 17. 1 ил., 1 табл.

Компаратор двоичных чисел, содержащий четыре входа устройства, два выхода устройства, два элемента НЕРАВНОЗНАЧНОСТЬ, причем первый вход устройства соединен с первым входом первого элемента НЕРАВНОЗНАЧНОСТЬ, второй вход устройства соединен с первым входом второго элемента НЕРАВНОЗНАЧНОСТЬ, отличающийся тем, что дополнительно содержит пятый и шестой входы устройства, третий элемент НЕРАВНОЗНАЧНОСТЬ, два мажоритарных элемента, элемент НЕ, три мультиплексора, причем первый вход устройства соединен с первым входом первого мажоритарного элемента, второй вход устройства соединен со вторым входом первого мажоритарного элемента, третий вход устройства соединен с третьим входом первого мажоритарного элемента и первым входом третьего элемента НЕРАВНОЗНАЧНОСТЬ, четвертый вход устройства соединен с первым информационным входом первого мультиплексора, пятый вход устройства соединен с первым информационным входом второго мультиплексора, шестой вход устройства соединен с первым информационным входом третьего мультиплексора, выход первого мажоритарного элемента соединен с первым выходом устройства, вторыми входами первого, второго и третьего элементов НЕРАВНОЗНАЧНОСТЬ и через элемент НЕ - со вторыми информационными входами первого, второго и третьего мультиплексоров, выход первого элемента НЕРАВНОЗНАЧНОСТЬ соединен с управляющим входом первого мультиплексора, выход второго элемента НЕРАВНОЗНАЧНОСТЬ соединен с управляющим входом второго мультиплексора, выход третьего элемента НЕРАВНОЗНАЧНОСТЬ соединен с управляющим входом третьего мультиплексора, выход первого мультиплексора соединен с первым входом второго мажоритарного элемента, выход второго мультиплексора соединен со вторым входом второго мажоритарного элемента, выход третьего мультиплексора соединен с третьим входом второго мажоритарного элемента, выход которого соединен со вторым выходом устройства.

| КОМПАРАТОР ДВОИЧНЫХ ЧИСЕЛ | 2006 |

|

RU2300131C1 |

| ГЕНЕРАТОР СЛУЧАЙНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2006 |

|

RU2313125C1 |

| ГЕНЕРАТОР СЛУЧАЙНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2003 |

|

RU2250489C1 |

| Пресс для выдавливания из деревянных дисков заготовок для ниточных катушек | 1923 |

|

SU2007A1 |

| Способ приготовления лака | 1924 |

|

SU2011A1 |

Авторы

Даты

2017-07-26—Публикация

2016-03-23—Подача