Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известен логический преобразователь (патент РФ 2281545, кл. G06F 7/57, 2006 г.), который содержит 7 мажоритарных элементов, четыре информационных входа, два настроечных входа, выход и реализует любую из четырех простых симметричных булевых функций при соответствующих настройках.

К причине, препятствующей достижению указанного ниже технического результата при использовании известного логического преобразователя, относятся ограниченные функциональные возможности, обусловленные тем, что не реализуются бесповторные булевые функции, зависящие от четырех аргументов.

Известен логический преобразователь (патент РФ 2417404, кл. G06F 7/57, 2011 г.), который содержит 6 мажоритарных элементов, четыре информационных входа, два настроечных входа, выход и реализует любую из четырех простых симметричных булевых функций при соответствующих настройках.

К причине, препятствующей достижению указанного ниже технического результата при использовании известного логического преобразователя, относятся ограниченные функциональные возможности, обусловленные тем, что не реализуются бесповторные булевые функции, зависящие от четырех аргументов.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является, принятый за прототип, логический модуль (патент РФ 2286594, кл. G06F 7/57, 2006 г.), предназначенный для реализации простых симметричных булевых функций, зависящих от четырех аргументов, содержащий четыре информационных входа модуля, два настроечных входа модуля, выход модуля, три мажоритарных элемента, два элемента И, два элемента ИЛИ.

К причине, препятствующей достижению указанного ниже технического результата при использовании известного логического преобразователя, относятся ограниченные функциональные возможности, обусловленные тем, что не реализуются бесповторные булевые функции, зависящие от четырех аргументов.

Техническим результатом изобретения является расширение функциональных возможностей за счет обеспечения реализации простых симметричных функций и бесповторных булевых функций, зависящих от четырех переменных.

Указанный технический результат при осуществлении изобретения достигается тем, что в универсальном логическом модуле, содержащем шесть входов модуля, два элемента И, два элемента ИЛИ, мажоритарный элемент, выход модуля, причем первый вход модуля соединен с первым входом мажоритарного элемента, второй вход модуля соединен с первым входом первого элемента И и первым входом первого элемента ИЛИ, третий вход модуля соединен со вторым входом первого элемента И и вторым входом первого элемента ИЛИ, введен дополнительно мультиплексор с тремя адресными входами и восемью информационными входами, причем первый вход модуля соединен с четвертым информационным входом мультиплексора, первым входом второго элемента И и первым входом второго элемента ИЛИ, второй вход модуля соединен со вторым входом мажоритарного элемента, третий вход модуля соединен с третьим входом мажоритарного элемента, выход первого элемента И соединен с первым информационным входом мультиплексора, выход мажоритарного элемента соединен со вторым и третьим информационными входами мультиплексора, выход первого элемента ИЛИ соединен со вторым входом второго элемента И и вторым входом второго элемента ИЛИ, выход второго элемента И соединен с пятым, шестым и седьмым информационными входами мультиплексора, выход второго элемента ИЛИ соединен с восьмым информационным входом мультиплексора, четвертый вход модуля соединен с первым адресным входом мультиплексора, пятый вход модуля соединен со вторым адресным входом мультиплексора, шестой вход модуля соединен с третьим адресным входом мультиплексора, выход мультиплексора соединен с выходом модуля.

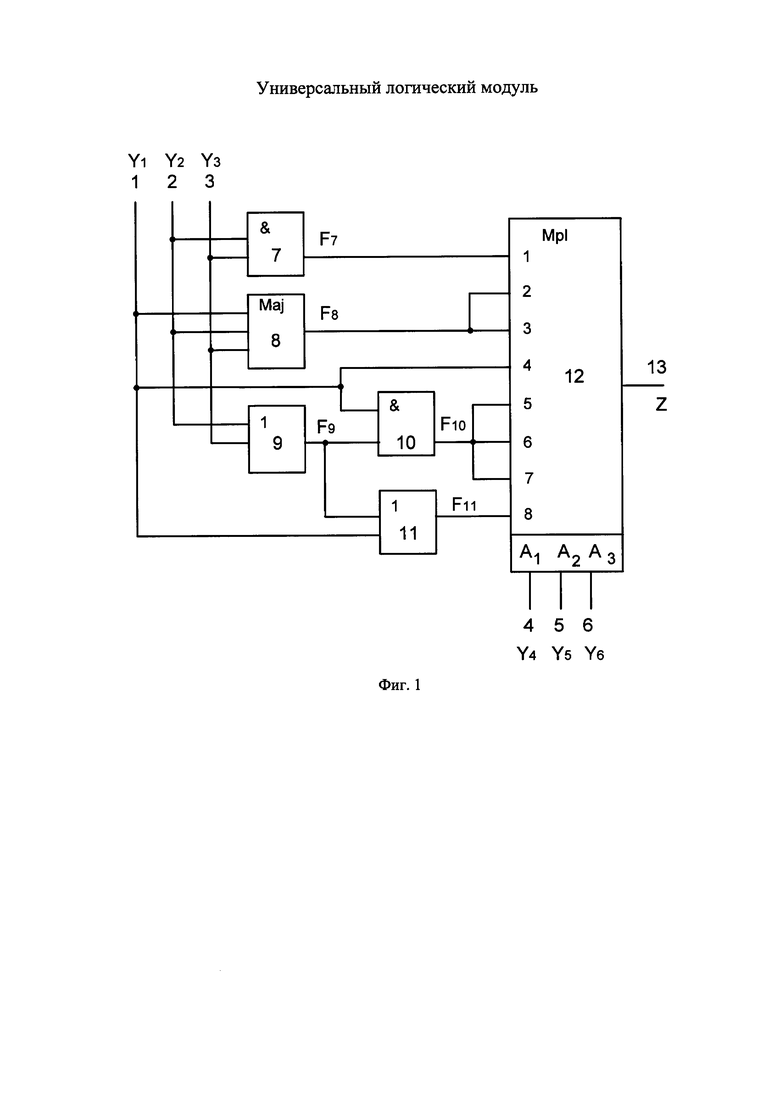

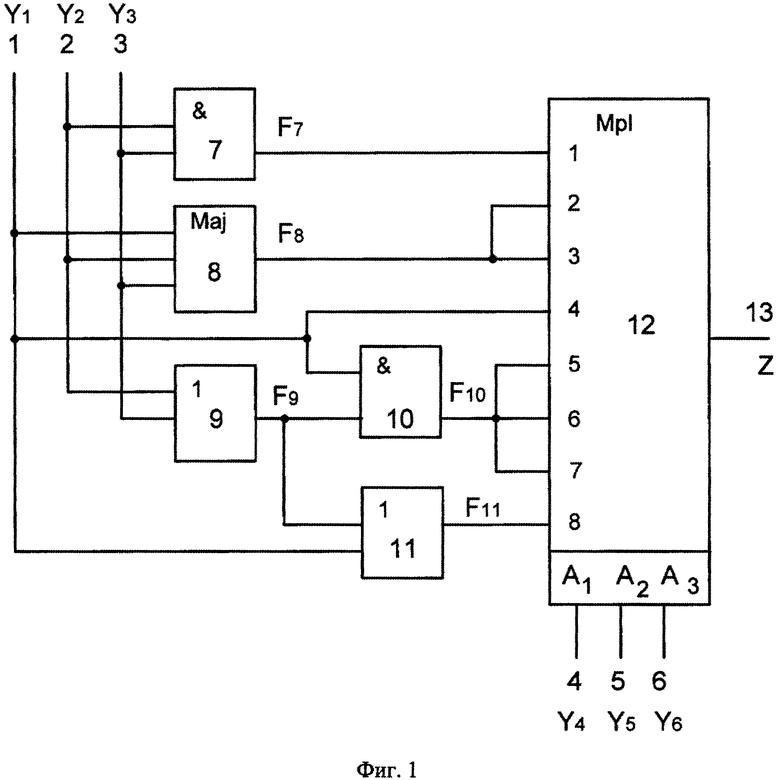

На фиг.1 представлена схема универсального логического модуля.

Универсальный логический модуль содержит шесть входов модуля 1, 2, 3, 4, 5, 6, первый элемент И 7, мажоритарный элемент 8, первый элемент ИЛИ 9, второй элемент И 10, второй элемент ИЛИ 11, мультиплексор 12 с тремя адресными входами и восемью информационными входами, выход модуля 13, причем первый вход модуля 1 соединен с первым входом мажоритарного элемента 8, с четвертым информационным входом мультиплексора 12, первым входом второго элемента И 10 и первым входом второго элемента ИЛИ 11, второй вход модуля 2 соединен с первым входом первого элемента И 7, первым входом первого элемента ИЛИ 9 и со вторым входом мажоритарного элемента 8, третий вход модуля 3 соединен со вторым входом первого элемента И 7 и вторым входом первого элемента ИЛИ 9 и с третьим входом мажоритарного элемента 8, выход первого элемента И 7 соединен с первым информационным входом мультиплексора 12, выход мажоритарного элемента 8 соединен со вторым и третьим информационными входами мультиплексора 12, выход первого элемента ИЛИ 9 соединен со вторым входом второго элемента И 10 и вторым входом второго элемента ИЛИ 11, выход второго элемента И 10 соединен с пятым, шестым и седьмым информационными входами мультиплексора 12, выход второго элемента ИЛИ 11 соединен с восьмым информационным входом мультиплексора 12, четвертый вход модуля 4 соединен с первым адресным входом мультиплексора 12, пятый вход модуля 5 соединен со вторым адресным входом мультиплексора 12, шестой вход модуля 6 соединен с третьим адресным входом мультиплексора 12, выход мультиплексора 12 соединен с выходом модуля 13.

Работа универсального логического модуля осуществляется следующим образом.

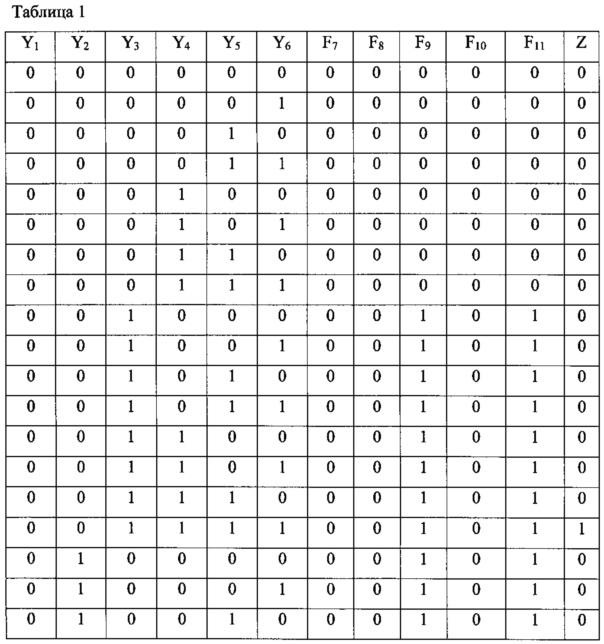

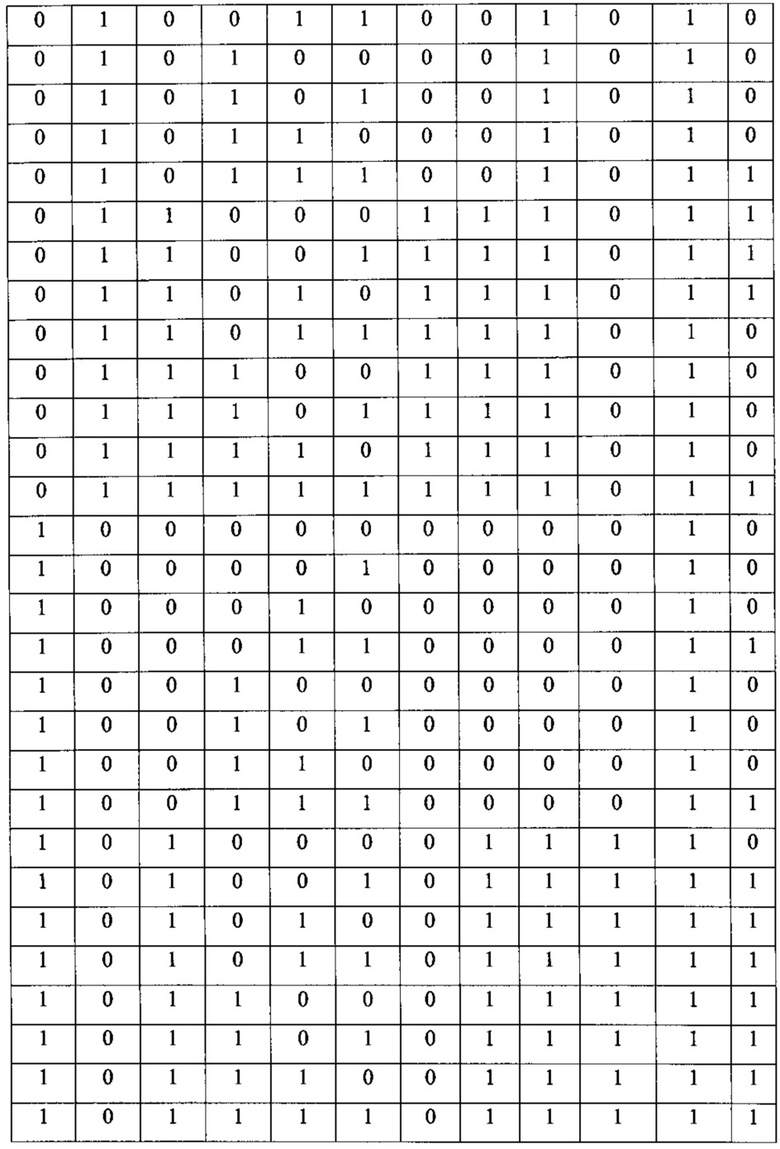

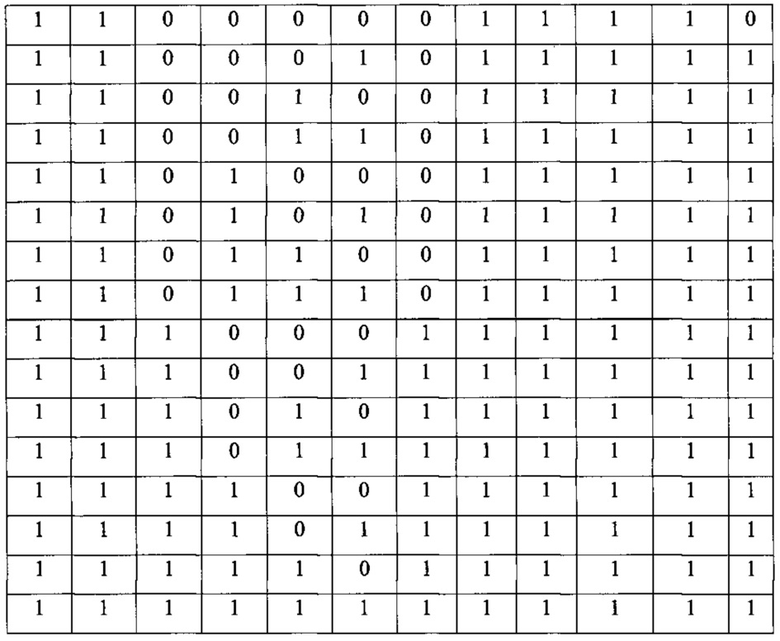

В зависимости от значений входных сигналов Y1, Y2, Y3, Y4, Y5, Y6 на входах 1, 2, 3, 4, 5, 6 модуля, на выходах его элементов и на выходе 13 модуля (Z) реализуются булевые функции, приведенные в табл. 1.

Для реализации заданных булевых функций необходимо на входы 1, 2, 3, 4, 5, 6 универсального логического модуля подать настроечные сигналы в соответствии с таблицей настроек и видом реализуемой булевой функцией.

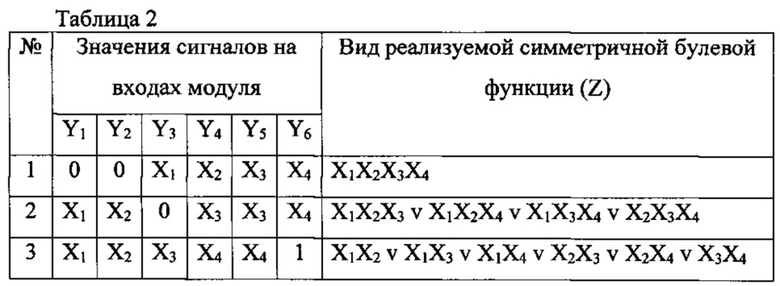

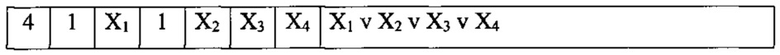

Настройка универсального логического модуля для реализации простых симметричных булевых функций, зависящих от четырех аргументов, приведена в таблице 2.

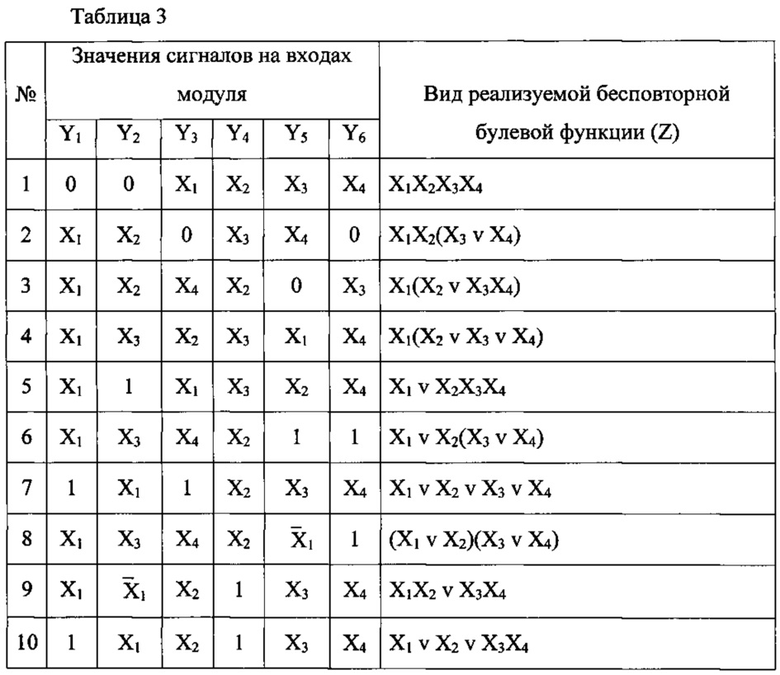

Настройка универсального логического модуля для реализации бесповторных булевых функций, зависящих от четырех аргументов, приведена в таблице 3.

Сравнение характеристики прототипа и заявляемого устройства показывает, что заявленное устройство имеет более широкие функциональные возможности, т.к. реализует не только симметричные булевые функции, но и бесповторные булевые функции.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ОБРАБОТКИ ЛОГИЧЕСКОЙ ИНФОРМАЦИИ | 2015 |

|

RU2610673C1 |

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2015 |

|

RU2609743C1 |

| НАСТРАИВАЕМЫЙ ЛОГИЧЕСКИЙ МОДУЛЬ | 2016 |

|

RU2626343C1 |

| МНОГОФУНКЦИОНАЛЬНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2015 |

|

RU2610247C1 |

| ФОРМИРОВАТЕЛЬ СИММЕТРИЧНЫХ БУЛЕВЫХ ФУНКЦИЙ | 2016 |

|

RU2616890C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2015 |

|

RU2618899C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2016 |

|

RU2626345C1 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2015 |

|

RU2602331C1 |

| ЛОГИЧЕСКИЙ ПРОЦЕССОР | 2015 |

|

RU2609744C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ ДЛЯ СИСТЕМ С РЕКОНФИГУРАЦИЕЙ | 2015 |

|

RU2610676C1 |

Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др. Техническим результатом изобретения является расширение функциональных возможностей за счет обеспечения реализации простых симметричных функций и бесповторных булевых функций, зависящих от четырех переменных. Универсальный логический модуль содержит шесть входов модуля 1, 2, 3, 4, 5, 6, первый элемент И 7, мажоритарный элемент 8, первый элемент ИЛИ 9, второй элемент И 10, второй элемент ИЛИ 11, мультиплексор 12 с тремя адресными входами и восемью информационными входами, выход модуля 13. 1 ил., 3 табл.

Универсальный логический модуль, предназначенный для реализации симметричных и бесповторных булевых функций, зависящих от четырех аргументов, содержащий шесть входов модуля, два элемента И, два элемента ИЛИ, мажоритарный элемент, выход модуля, причем первый вход модуля соединен с первым входом мажоритарного элемента, второй вход модуля соединен с первым входом первого элемента И и первым входом первого элемента ИЛИ, третий вход модуля соединен со вторым входом первого элемента И и вторым входом первого элемента ИЛИ, отличающийся тем, что содержит мультиплексор с тремя адресными входами и восемью информационными входами, причем первый вход модуля соединен с четвертым информационным входом мультиплексора, первым входом второго элемента И и первым входом второго элемента ИЛИ, второй вход модуля соединен со вторым входом мажоритарного элемента, третий вход модуля соединен с третьим входом мажоритарного элемента, выход первого элемента И соединен с первым информационным входом мультиплексора, выход мажоритарного элемента соединен со вторым и третьим информационными входами мультиплексора, выход первого элемента ИЛИ соединен со вторым входом второго элемента И и вторым входом второго элемента ИЛИ, выход второго элемента И соединен с пятым, шестым и седьмым информационными входами мультиплексора, выход второго элемента ИЛИ соединен с восьмым информационным входом мультиплексора, четвертый вход модуля соединен с первым адресным входом мультиплексора, пятый вход модуля соединен со вторым адресным входом мультиплексора, шестой вход модуля соединен с третьим адресным входом мультиплексора, выход мультиплексора соединен с выходом модуля.

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2005 |

|

RU2286594C1 |

| Многофункциональный логический модуль | 1986 |

|

SU1322254A1 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2009 |

|

RU2417404C1 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2005 |

|

RU2281545C1 |

| Пломбировальные щипцы | 1923 |

|

SU2006A1 |

Авторы

Даты

2017-02-14—Публикация

2015-11-24—Подача