Область техники

Устройства, представляющие собой электронные схемы, изготовление и структура устройств электронных схем на основе ребер.

Уровень техники

Все более улучшающиеся рабочие характеристики устройств, представляющих собой электронные схемы на подложке (например, транзисторы, резисторы, конденсаторы и т.д. в интегральных схемах (IC), на полупроводниковой (например, кремниевой) подложке) обычно представляют собой основной фактор, учитываемый во время конструирования, изготовления и работы этих устройств. Например, во время конструирования и изготовления или формирования транзисторных устройств из металлооксидного полупроводника (MOS), таких как используются в комплементарном металлооксидном полупроводнике (CMOS), часто требуется усилить движение электронов в каналах устройствах MOS N-типа (n-MOS) и усилить движение положительно заряженных дырок в каналах устройства MOS P-типа (p-MOS). Однако рабочие характеристики и движение замедляются из-за несовпадения постоянных кристаллических решеток и дефектов, возникающих между слоями материалов, используемых для формирования MOS.

Для некоторых вариантов осуществления CMOS одновременная интеграция материалов, с несовпадающими постоянными кристаллических решеток, таких как эпитаксиальное выращивание материалов III-V на кремнии, представляет собой большую проблему. В настоящее время в уровне техники отсутствуют решения для совместной интеграции эпитаксиального выращивания n- и p-MOS материалов на одной кремниевой подложке. Таким образом, в существующих в настоящее время вариантах применения, из-за большого различия между постоянными кристаллических решеток в материалах возникают дефекты, когда новые материалы (III-V, германий (Ge)) выращивают на подложке из кремниевого материала.

Краткое описание чертежей

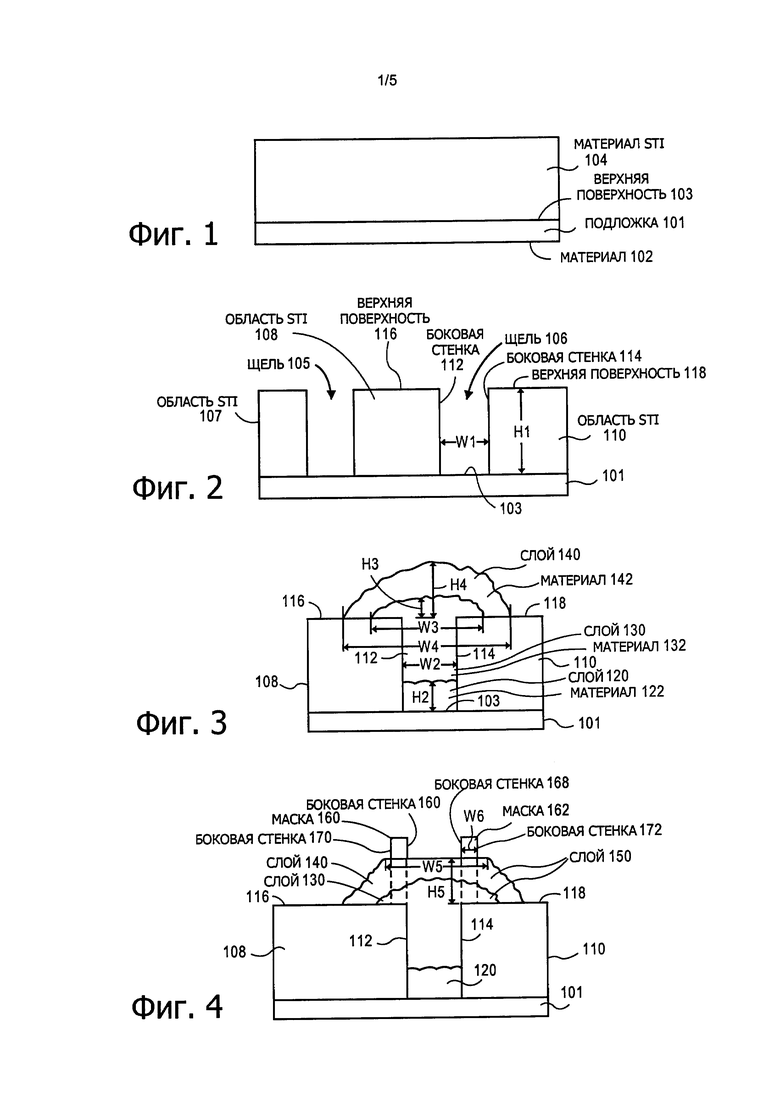

На фиг. 1 схематично показан вид в поперечном сечении участка основания в виде полупроводниковой подложки после формирования слоя материала узкощелевой изоляции (STI) на верхней стороне подложки.

На фиг. 2 представлена полупроводниковая подложка по фиг. 1 после формирования областей STI и щелей между областями STI.

На фиг. 3 представлена полупроводниковая подложка по фиг. 1 после формирования эпитаксиального материала в щелях между областями STI.

На фиг. 4 представлена полупроводниковая подложка по фиг. 1 после полировки и формирования структуры эпитаксиального материала, сформированного поверх щели и поверх области STI.

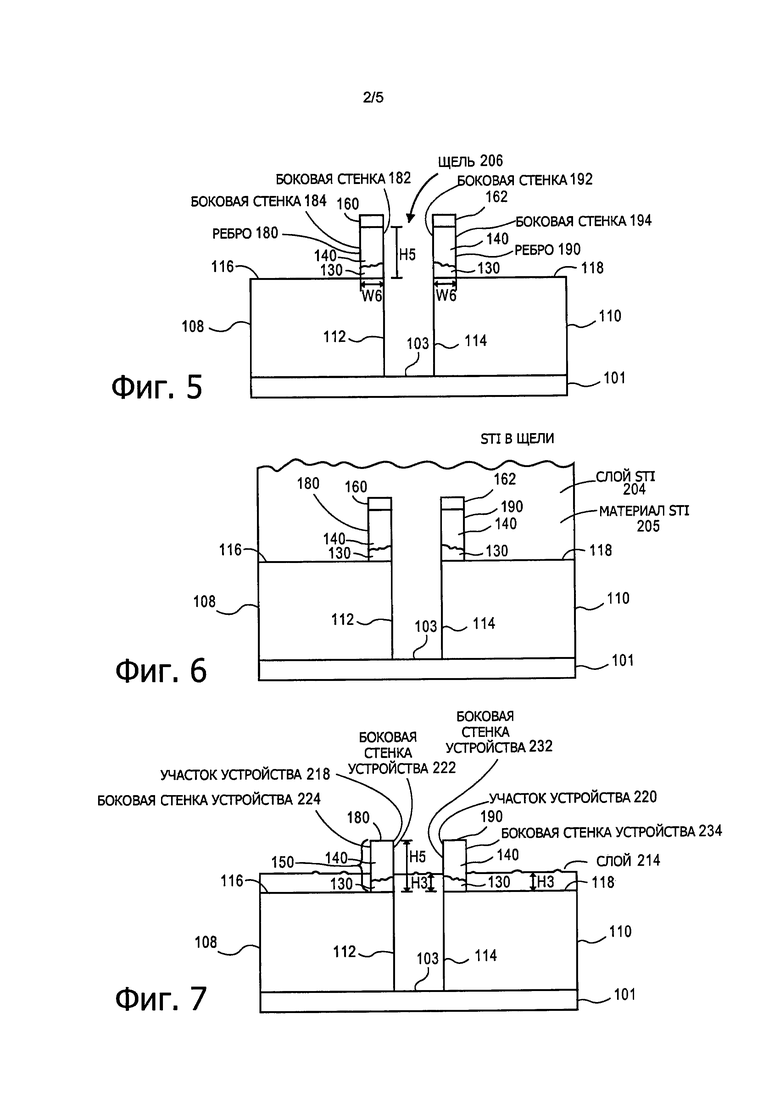

На фиг. 5 представлена полупроводниковая подложка по фиг. 1 после формирования ребер из эпитаксиального материала, сформированного поверх области STI.

На фиг. 6 представлена полупроводниковая подложка по фиг. 1 после формирования слоя материала STI поверх ребер и щели.

На фиг. 7 представлена полупроводниковая подложка по фиг. 1 после полировки слоя STI, сформированного поверх ребер, щели и области STI; и после вытравливания выемки, для того, чтобы открыть боковые стенки устройства на ребрах электронного устройства.

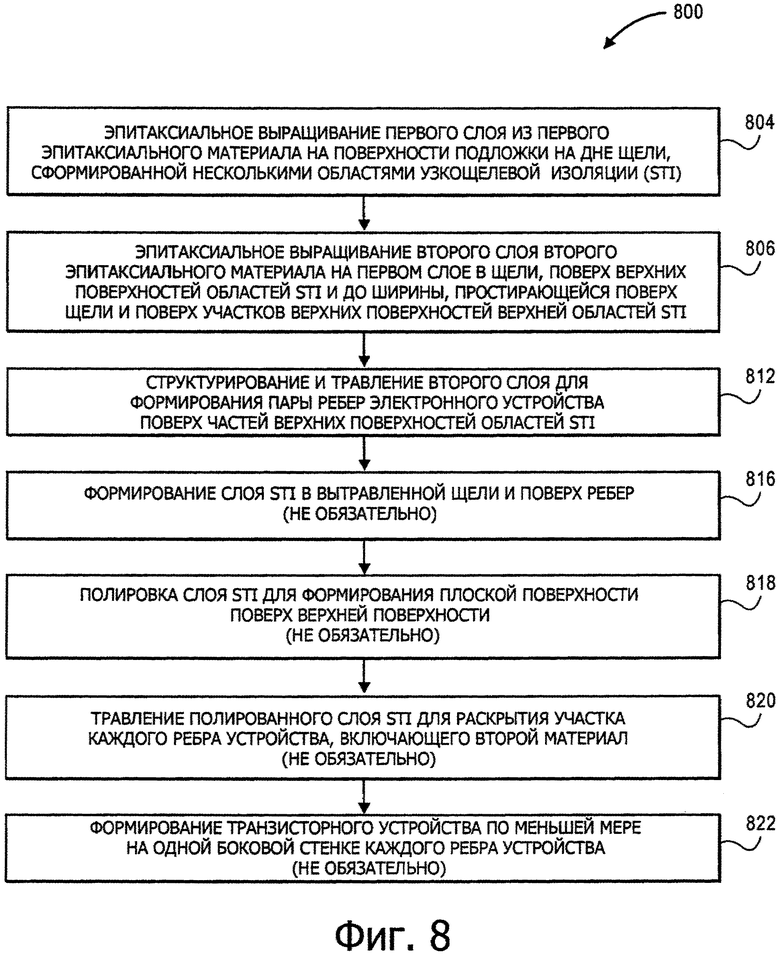

На фиг. 8 показан пример обработки для формирования пары ребер электронного устройства.

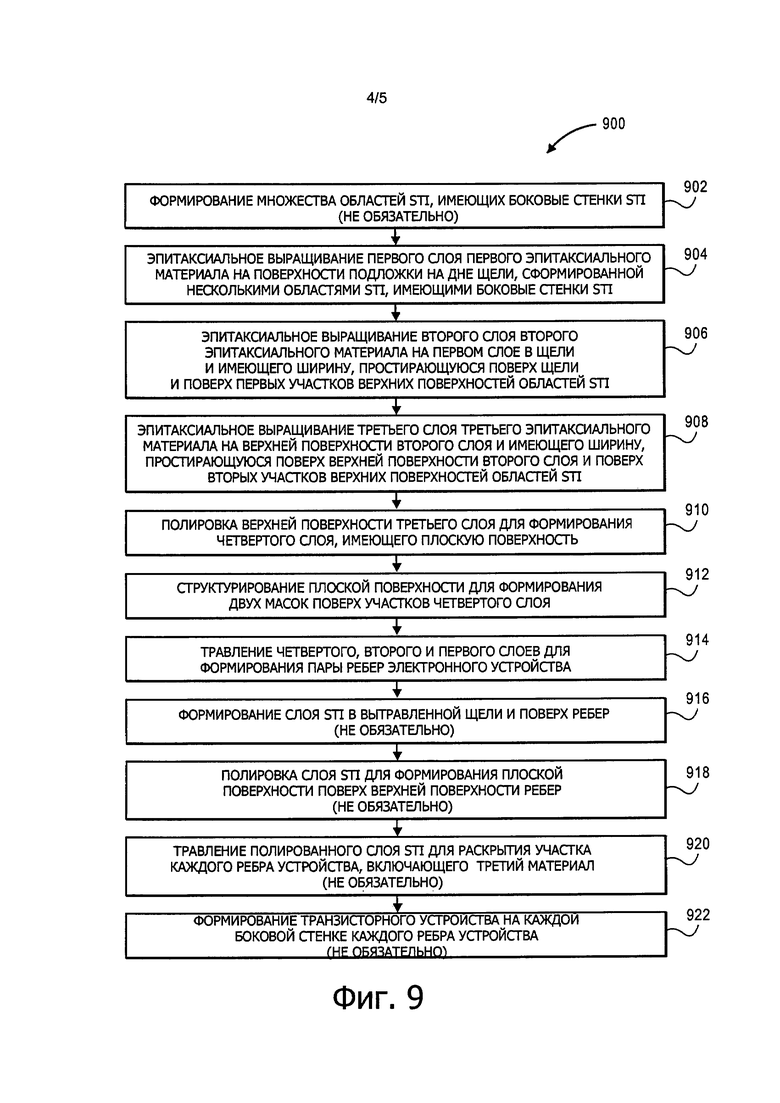

На фиг. 9 показан пример обработки для формирования пары ребер электронного устройства.

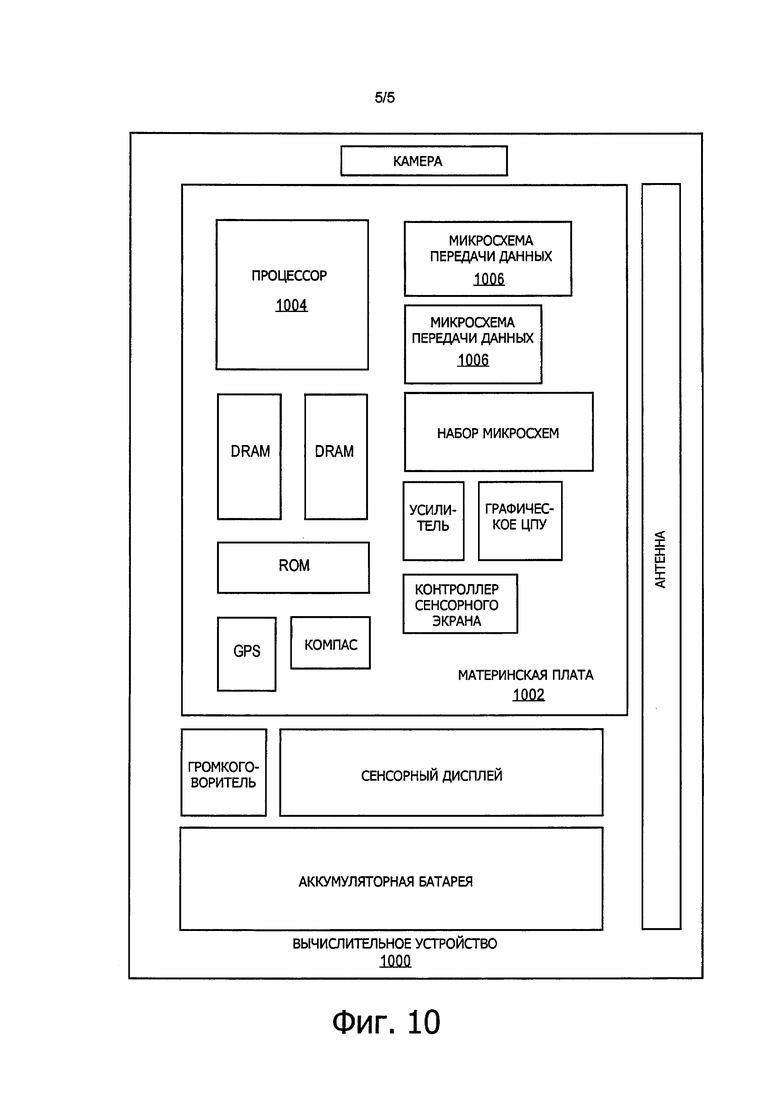

На фиг. 10 иллюстрируется вычислительное устройство, в соответствии с одним вариантом реализации.

Осуществление изобретения

Существенное различие между постоянными кристаллических решеток в материалах может генерировать дефекты, когда определенные материалы (например, материалы типа III-V или германия (Ge)) подвергают эпитаксиальному росту на подложке из кремниевого материала (например, на монокристаллическом кремнии). В некоторых случаях, материалы можно эпитаксиально выращивать из поверхности подложки, в щелях между областями узкощелевой изоляции (STI). Рост можно структурировать и подвергать травлению для формирования "ребер" материала, на которых могут быть сформированы устройства. Таким образом, могут присутствовать дефекты в "ребрах" материала, в которых или на которых могут быть сформированы устройства, после структурирования ребер и травления после выращивания.

Например, дефекты могут быть захвачены либо вдоль боковых стенок STI, формирующих щели, благодаря тому, что высота (H) щели больше, чем ширина (W) и длина (L) щели, таким образом, что отношения H/W > =1,5 и H/L > =1,5. Такое соотношение может привести к минимальному пределу отношений H/W, для блокирования множества дефектов в пределах буферного слоя, формируемого в щели. Однако существуют другие дефекты, включающие в себя дефекты упаковки, которые возникают в боковой стенке STI, которые все еще остаются в пределах щели.

Улучшение плотности дефектов могут быть выполнено с помощью оптимизации роста/специальных приемов при выращивании поверхностной пленки. Однако это не позволяет уменьшить такие дефекты внутри щели. Такие дефекты распространяются через щель и могут привести к проблемам при производстве и вариациям устройства, построенном на слое устройства, сформированном в результате эпитаксиального выращивания, продолжающегося выше щели. Такое распространение может присутствовать в устройствах на "ребрах", сформированных в ребрах, которые структурируют и которые подвергают травлению на основе эпитаксиального выращивания, продолжающегося выше щели. Такие устройства могут включать в себя транзисторы, резисторы, конденсаторы и т.д. в виде интегральной схемы (IС) на ребре, сформированные на одной или на боковых стенках "ребер", выращенных из или продолжающихся выше полупроводниковой (например, кремниевой) подложки или подложки из другого материала. Такие устройства могут включать в себя транзисторные устройства на основе металлооксидного полупроводника (MOS) на ребре, такие как используются в комплементарных металло-оксидных полупроводниках (CMOS), на основе движения электронов в каналах устройства MOS N-типа (n-MOS) и движения положительно заряженных дырок в каналах устройства MOS P-типа (p-MOS).

В соответствии с вариантами осуществления, такие дефекты могут быть исключены путем эпитаксиального выращивания первым слоем материала на поверхности подложки, на дне щели, сформированной между боковыми стенками областей узкощелевой изоляции (STI). Затем второй слой материала может быть эпитаксиально выращен на первом слое в щели и поверх верхних поверхностей областей STI. Второй слой может иметь вторую ширину, продолжающуюся поверх щели и поверх участка верхних поверхностей областей STI. Второй слой затем может быть структурирован и может быт обработан травлением для формирования пары участков, расположенных на ребрах электронного устройства на верхних поверхностях областей STI, в непосредственной близости к щели. Такая обработка позволяет исключать дефекты кристаллов в ребрах, из-за различия между постоянными кристаллических решеток на границах перехода слоев. Например, дефекты (например, дефекты кристаллов) в щели могут не расширяться или могут не существовать в областях поперечного эпитаксиального нароста (например, часть ширины второго слоя, продолжающаяся поверх участков верхних поверхностей областей STI). Таким образом, ребра, сформированные из этого материала, могут обеспечивать материал для электронного устройства (например, ямы и щели), в которых могут быть сформированы не содержащие дефекта устройства на основе ребра.

На фиг. 1 схематично показан вид в поперечном сечении участка основания для полупроводниковой подложки после формирования слоя материала STI на верхней стороне подложки. На фиг. 1 показана полупроводниковая подложка или основание 101 из материала 102, имеющее верхнюю поверхность 103. Подложка 101 может включать в себя, может быть сформирована из, на нее может быть нанесен, или она может быть выращена из кремния, поликристаллического кремния, монокристаллического кремния или используя различные другие соответствующие технологии для формирования кремниевого основания или подложки, такой как кремниевая пластина. Например, в соответствии с вариантами осуществления, подложка 101 может быть сформирована путем выращивания материала основания в виде подложки из монокристаллического кремния, имеющего толщину от 100 ангстрем до 1000 ангстрем из чистого кремния. В качестве альтернативы, подложка 101 может быть сформирована, используя достаточное химическое осаждение из паровой фазы (CVD) различных соответствующих материалов 102 из кремния или кремниевого сплава, для формирования слоя материала, имеющего толщину от одного до трех микрометров, такого как CVD, для формирования толщины два микрометра. Также учитывается, что подложка 101 может представлять собой смягченный, несмягченный, полупроводниковой частоты и/или неполупроводниковой частоты материал 102 кремниевого сплава. Материал 102 может представлять собой смягченный материал (например, имеющий ненапряженную решетку) на поверхности 103. Материал 102 может представлять собой монокристаллический кремниевый материал. Подложка 102 может быть изготовлена из кремния и может иметь верхнюю поверхность 103 с (100) кристаллически ориентированным материалом (например, в соответствии с индексом Миллера). Подложка 101 может представлять собой "неправильно срезанную" подложку.

На фиг. 1 также показан слой материала 104 изоляции с мелкими щелями (STI), сформированного или выращенного на верхней поверхности 103 подложки 101. Материал 104 STI может быть сформирован из оксида или нитрида или их комбинации. Материал 104 STI может быть сформирован из SiC или другого материала, как известно в данной области техники. Материал 104 STI может быть сформирован в результате осаждения атомарного слоя (ALD) или химического осаждения из паровой фазы (CVD). Материал 104 STI обычно наносят, используя плазмо-химическое осаждение из паровой фазы (PECVD). В некоторых случаях материал 104 STI формируют, используя ALS, CVD, PECVD для TEOS + 02 + RF при температуре 400°C. В некоторых случаях, любой из различных предшественников кислорода, силановых предшественников или общих предшественников можно использовать во время обработки (например, PECVD), для формирования материала 104 STI, как известно в данной области техники.

Нижняя поверхность материала 104 может иметь такую же (100) ориентацию кристаллов, как и у материала 102 (например, на поверхности 103). В некоторых случаях, нижняя поверхность материала 104 может иметь такой же размер кристаллической решетки, как и у материала 102 (например, на поверхности 103). Материал 104 может представлять собой ненапряженный материал (например, имеющий ненапряженную решетку) в отношении его границы перехода (например, где материал 104 химически или на атомарном уровне связан с поверхностью 103, находящейся под ним) с поверхностью 103.

На фиг. 2 показана полупроводниковая подложка по фиг. 1 после формирования областей STI и щелей между областями STI. На фиг. 2 показаны щели 105 и 106, сформированные между областями 107, 108 и 110 STI, и поверхность 103. Области 107, 108 и 110 могут быть сформированы путем структурирования и обработки травлением, как известно в данной области техники. Это может включать в себя формирование сплошного слоя из материала 104 STI, с последующей структуризацией и обработкой травлением материала 104 для формирования областей 107, 108 и 110 STI. В некоторых случаях, структурирование и обработка травлением материала 104 для формирования областей STI включают в себя использование резиста, или жесткой маски под резистом для структурирования материалов. В некоторых случаях 1, 2 или 3 слоя резиста могут использоваться для структурирования материалов. В некоторых случаях, структурирование и обработка травлением материала 104 для формирования областей STI включают в себя использование травления плазмой O2 или O2/Ar под давлением в диапазоне от 10-100 мТорр, и при комнатной температуре. Такое структурирование и обработка травлением также могут включать в себя обработку травлением оксидов, включающих в себя материал STI путем обработки травлением с флюороуглеродами (например, CF4 и/или C4F8), O2 и Ar, при давлении в диапазоне 10-100 мТорр и при комнатной температуре.

Область 108 STI имеет боковую стенку 112 и верхнюю поверхность 116. У области STI 110 есть боковая стенка 114 и верхняя поверхность 118. Боковые стенки 112 и 114 могут представлять собой вертикальные плоские поверхности, перпендикулярные (например, расположенные под прямым углом относительно) горизонтальным плоским поверхностям на поверхности 103 и горизонтальным плоским поверхностям на поверхностях 116 и 118. Боковые стенки могут содержать или могут быть изготовлены из материала 104 STI. Области 108 и 110 STI могут иметь ширину от 100 до 1000 нанометров (нм).

Щели 105 и 106 могут быть сформированы боковыми стенками областей 107,108 и 110. Более конкретно, на фиг. 2 показана щель 106, сформированная или имеющая сторону на боковой стенке 112 области 108, сторону на боковой стенке 114 области 110, с нижней частью на верхней поверхности 103, и верхней частью, расположенной рядом (например, проксимально) с верхними поверхностями 116 или 118. Щели 105 и 106 могут включать в себя поверхность 103 из материала 102, открытого на дне щели, такой как плоская или выровненная поверхность кристаллического материала. В некоторых случаях, каждая из щелей 105 и 106 определена дополнительными боковыми стенками других областей STI, таких как передняя и задняя STI, имеющие боковую стенку, аналогичную боковым стенкам 112 и 114, и верхние поверхности, аналогичные поверхностям 116 или 118, но образующих длину L щели 106.

Щель 106 может иметь ширину W1, определенную горизонтальным расстоянием между боковой стенкой 112 области 108 и сторону в боковой стенке 114 области 110. Ширина W1 может представлять собой ширину от 10 до 100 нанометров (нм). В некоторых случаях W1 составляет приблизительно 25 нм.

Щель 106 может иметь высоту H1, определенную вертикальным расстоянием между верхней поверхностью 103 и верхней поверхностью 116 или 118. Высота H1 может представлять собой высоту от 30 до 300 нанометров (нм). В некоторых случаях H1 составляет приблизительно 75 нм. H1 щели может быть больше, чем W1 щели таким образом, что отношение H1/W1 > =1,5. В некоторых случаях, отношение H1/W1 = 1,5. В некоторых случаях, отношение H1/W1 > =2,0.

Щель 106 может иметь длину L1, определенную, как длина, продолжающаяся в сторону страницы и вдоль боковой стенки 112 или боковой стенки 114. Длина L1 может представлять собой длину от 10 до 100 нанометров (нм). В некоторых случаях L1 составляет приблизительно 25 нм. В некоторых случаях L1 равна (или приблизительно является такой же как) W1. H1 щели может быть больше, чем L1 щели таким образом, что отношение H1/L1 > =1,5. В некоторых случаях, отношение H1/L1 = 1,5. В некоторых случаях, отношение H1/L1 > =2,0. В соответствии с некоторыми вариантами осуществления, W1 может составлять от 10 до 15 нанометров (нм), и H1 может составлять 350 нанометров (нм). В случае необходимости, L1 может быть равно W1.

На фиг. 2 показаны щели 105 и 106, сформированные между областями 107, 108 и 110 STI, и поверхностью 103. Однако, считается, что больше аналогичных щелей и областей может присутствовать на подложке 101 (например, по меньшей мере, сотни или сотни тысяч).

На фиг. 3 показана полупроводниковая подложка по фиг. 1 после формирования эпитаксиального материала в щелях между областями STI. На фиг. 3 показано формирование эпитаксиального материала в щели 106, однако, предусматривается, что щель 106 представляет собой любое количество щелей, сформированных в областях STI на подложке 101. На фиг. 3 показан первый слой 120 материала 122, эпитаксиально выращенного из поверхности 103 в щели 106. Материал 122 может быть эпитаксиально выращен из поверхности 103 кристалла поверхности 103 подложки. Материал 122 может быть сформирован путем эпитаксиального выращивания (например, способом гетероэпитаксии), используя осаждение атомарного слоя (ALD) или химическое осаждение из паровой фазы (CVD), и может быть выращен только из "затравочной" поверхности 103 ниже в щель, но не может быть выращен на боковых стенках STI или на верхних поверхностях STI. Выбор условий осаждения для роста, таких как температура для роста, давление потока газа и т.д., может определять избирательность эпитаксиального роста. В некоторых случаях, выращивание слоя 120 выполняется избирательно от поверхности 103 путем выбора или использования заданного диапазона температуры роста, давления диапазона потока газа и т.д., как показано для материала 122, для выращивания из материала на поверхности 103, но без выращивания из или инициирования на материале боковой стенки или на верхних поверхностях STI.

Материал 122 может представлять собой первый слой из кристаллического материала, который имеет высоту H2 от поверхности 103, которая меньше, чем H1. Материал 122 может иметь нижнюю поверхность, имеющую (100) кристаллически ориентированный материал, выращенный из поверхности 103, и боковые поверхности, имеющие (110) кристаллически ориентированный материал вдоль или рядом с боковыми стенками 112 и 114. В некоторых вариантах осуществления дефекты кристалла могут присутствовать в материале 122 рядом или вдоль боковых стенок 112 и 114 STI, формирующих щели. В некоторых вариантах осуществления дефекты кристалла могут присутствовать в материале 122 из-за дефектов, включающих в себя дефекты упаковки, которые возникают на боковых стенках 112 или 114 STI, которые все еще остаются в щели 106.

Материал 122 может иметь верхнюю поверхность, имеющую (100) ориентацию кристалла (индекс Миллера). Верхняя поверхность слоя 120 может быть отполирована или может быть подвергнута травлению для формирования плоской поверхности, имеющей (100) кристаллический индекс. Слой 120 может иметь ширину W2 между боковыми стенками 112 и 114. W2 может быть меньше чем или равна W1. В некоторых случаях, разность по ширине может возникать из-за кристаллических дефектов в материале 122. Слой 120 может иметь длину L1.

Слой 120 может иметь высоту H2, определенную вертикальным расстоянием между верхней поверхностью 103 и верхней поверхностью слоя 120. Высота H2 может представлять собой высоту от 50 до 150 нанометров (нм). В некоторых случаях H2 приблизительно составляет 70 нм. В некоторых случаях, слой 120 представляет собой слой материала InP или GaAs.

Нижняя поверхность слоя 120 может иметь такую же (100) кристаллическую ориентацию, как и у материала 102 (например, на поверхности 103). В некоторых случаях, нижняя поверхность слоя 120 может иметь такой же размер кристаллической решетки, как и у материала 102 (например, у поверхности 103). Слой 120 может представлять собой ненапряженный материал (например, имеющий ненапряженную решетку) в отношении его границы перехода с поверхностью 103. В некоторых случаях, слой 120 представляет собой ненапряженный слой (частично или полностью) в отношении подложки (например, поверхности 103).

На фиг. 3 показан второй слой 130 из материала 132, эпитаксиально выращенного из верхней поверхности слоя 120. Материал 132 может быть эпитаксиально выращенным из верхней кристаллической поверхности слоя 120. Материал 132 может быть сформирован путем эпитаксиального выращивания (например, способом гетероэпитаксии), используя химическое осаждение из паровой фазы (CVD) и может быть выращен только из "затравочной" верхней поверхности слоя 120, расположенного ниже в щель, но может не быть выращен на боковых стенках или на верхних поверхностях STI. В некоторых случаях, рост слоя 130 выполняют избирательно от верхней поверхности слоя 120 (например, из материала 122), путем выбора или использования заданного диапазона температуры, давления в диапазоне потока газов и т.д. для выращивания, как известно для материала 132, для выращивания из материала 122, но без роста из или без инициирования на материале боковой стенки или на верхних поверхностях STI.

Материал 132 может представлять собой второй слой кристаллического материала, который имеет высоту, определенную вертикальным расстоянием между верхней поверхностью слоя 120 и верхней поверхностью слоя 130. Участок высоты слоя 130 может иметь высоту H3, продолжающуюся выше или поверх верхних поверхностей 116 и 118 областей 108 и 110 STI. Материал 132 может иметь нижнюю поверхность, имеющую (100) кристаллически ориентированный материал, выращенный из слоя 120, и боковые поверхности, имеющие (110) кристаллически ориентированный материал вдоль или рядом с боковыми стенками 112 и 114. В некоторых вариантах осуществления кристаллические дефекты могут присутствовать в материале 132 рядом или вдоль боковых стенок 112 и 114 STI, формирующих щели. В некоторых вариантах осуществления кристаллические дефекты могут присутствовать в материале 132 из-за дефектов, включающих в себя дефекты упаковки, которые возникают на боковых стенках 112 или 114 STI, и которые все еще остаются в пределах щели 106. Материал 132 может иметь верхнюю поверхность, имеющую (100) кристаллическую ориентацию (индекс Миллера). Верхняя поверхность слоя 130 может быть отполирована или может быть подвергнута травлению, для формирования плоской поверхности, имеющей (100) кристаллический индекс.

Слой 130 может иметь горизонтальную ширину W3, продолжающуюся поперек или поверх щели (например, W1), и участки верхних поверхностей на поверхности 116 и 118 областей 108 и 110 STI. W3 может быть больше, чем (например, и включая в себя) W1. В некоторых случаях, кристаллические дефекты в материале 132 рядом или вдоль боковых стенок 112 и 114 STI не продолжаются на участок слоя 130, имеющего высоту H3 и ширину W3. Слой 130 может иметь длину L1.

Слой 130 может иметь вертикальную высоту H3 выше или поверх верхних поверхностей 116 и 118 областей 108 и 110 STI. Высота H3 может представлять собой высоту от 5 до 100 нанометров (нм). В некоторых случаях H3 составляет приблизительно 20 нм. В соответствии с некоторыми вариантами осуществления, разность по высоте между верхней частью слоя 120 и верхней частью слоя 130 может составлять 200 нанометров (нм).

Нижняя поверхность слоя 130 может иметь такую же (100) кристаллическую ориентацию, как и у материала 122 (например, на его верхней поверхности). В некоторых случаях, нижняя поверхность слоя 130 может иметь такой же размер кристаллической решетки, как и у материала 122 (например, на его верхней поверхности). Слой 130 может представлять собой ненапряженный материал (например, иметь ненапряженную кристаллическую решетку) в отношении его границ перехода со слоем 120 (например, на его верхней поверхности). В некоторых случаях, слой 130 представляет собой ненапряженный слой (в основном или полностью) в отношении слоя 120 (например, верхней поверхности материала 122).

На фиг. 3 показан третий слой 140 материала 142, эпитаксиально выращенный из верхней поверхности слоя 130. Слой 140 может представлять собой слой "устройства", такой как слой, на котором или в котором формируются устройства схемы, как известно в данной области техники. Такие устройства могут включать в себя устройства, описанные ниже.

Материал 142 может быть эпитаксиально выращен из кристаллической верхней поверхности слоя 130.

Материал 142 может быть сформирован путем эпитаксиального выращивания (например, используя гетероэпитаксию) с использованием химического осаждения из паровой фазы (CVD) и может быть выращен только из "затравочной" верхней поверхности слоя 130 ниже в щель, но без выращивания на боковых стенках или на верхних поверхностях STI. В некоторых случаях, рост слоя 140 представляет собой избирательный рост из верхней поверхности слоя 130 (например, из материала 132) путем выбора или использования заданного температурного диапазона для роста, давления в диапазоне потока газа и т.д., как известно для материала 142, для выращивания из материала 132, но без роста из или инициирования на материале боковой стенки или верхних поверхностях STI.

Материал 142 может представлять собой третий слой кристаллического материала, который имеет высоту, определенную вертикальным расстоянием между верхней поверхностью слоя 130 и верхней поверхностью слоя 140. Слой 140 может иметь высоту H4, продолжающуюся выше или поверх верхних поверхностей 116 и 118 из областей 108 и 110 STI. H4 может быть больше чем H3.

Материал 142 может иметь нижнюю поверхность, имеющую (100) кристаллически ориентированный материал, выращенный из слоя 130, и боковые поверхности, имеющие (110) кристаллически ориентированный материал вдоль направления, параллельного боковым стенкам 112 и 114. В некоторых вариантах осуществления дефекты кристаллов, которые присутствуют в материалах 122 или 132 рядом или вдоль боковых стенок 112 и 114 STI, могут не продолжаться в слой 140 (например, не продолжаться до высоты H4 и ширины W4). В некоторых вариантах осуществления дефекты кристалла могут присутствовать в материале 142, из-за дефектов, включающих в себя дефекты упаковки, которые возникают на боковых стенках 112 или 114 STI, которые не продолжаются в слой 140 (например, не продолжаются до высоты H4 и ширины W4).

Материал 142 может иметь верхнюю поверхность, имеющую (100) ориентацию кристалла (индекс Миллера). Верхняя поверхность слоя 140 может быть отполирована или может быть обработана травлением для формирования плоской поверхности, имеющей (100) кристаллический индекс. Слой 140 может иметь горизонтальную ширину W4, продолжающуюся через или поверх щели (например, W1) на участках верхних поверхностей 116 и 118 областей 108 и 110 STI.

W4 может быть больше чем (например, и включая в себя) W3 (например, и W1). Слой 140 может иметь длину L1. В некоторых случаях, слой 140 представляет собой одиночный слой из материала InGaAs или InAs. В некоторых случаях, слой 140 представляет собой укладку из множества слоев материала InGaAs/InP/InGaAs.

Слой 140 может иметь вертикальную высоту H4 выше или поверх верхних поверхностей 116 и 118 областей 108 и 110 STI. В некоторых случаях, когда слой 140 представляет собой укладку из множества слоев, высота H4 может представлять собой высоту от 50 до 300 нанометров (нм). В некоторых случаях, когда слой 140 представляет собой одиночный слой, высота H4 может представлять собой высоту от 20 до 300 нанометров (нм). В некоторых случаях H4 приблизительно составляет 50 нм. В соответствии с некоторыми вариантами осуществления, разница по высоте между вершиной слоя 130 и вершиной слоя 140 или слоя 150 может составлять 50 нанометров (нм).

Нижняя поверхность слоя 140 может иметь такую же (100) ориентацию кристалла, как и у материала 132 (например, на его верхней поверхности). В некоторых случаях нижняя поверхность слоя 140 может иметь такой же размер кристаллической решетки, как и у материала 132 (например, на его верхней поверхности). Слой 140 может быть выполнен из ненапряженного материала (например, может иметь ненапряженную решетку) в отношении его границы перехода со слоем 130 (например, на его верхней поверхности). В некоторых случаях, слой 140 может иметь такую же постоянную кристаллической решетки, как и на дне слоя 120 или на поверхности 103. В некоторых случаях, слой 140 согласован по решетке в отношении слоя 130 (например, верхней поверхности материала 132). В некоторых случаях, слой 140 полностью растянут относительно слоя 130 (например, верхняя поверхность материальных 132). Растяжение может представлять собой деформацию растяжения или деформацию сжатия, которая соответствует повышению мобильности носителей.

На фиг. 4 показана полупроводниковая подложка по фиг. 1 после полировки и структурирования эпитаксиального материала, сформированного поверх щели и над областями STI. На фиг. 4 показан слой 140, отполированный или выровненный для формирования слоя 150. Полировка или выравнивание слоя 140 может быть выполнено, используя химическую, физическую или механическую полировку, как известно в области техники, для формирования верхней плоской поверхности 164 материала 142. Слой 150 может быть описан, как четвертый слой, включающий в себя материал 142 и материал 132, который расположен или который существует поверх верхней поверхности щели (например, в пределах W1 и L1, выше или поверх H1) и областей STI (например, поверх поверхностей 116 и 118). Слой 150 может иметь горизонтальную ширину W4 в его основании или на верхних поверхностях, таких как поверхности 116 и 118 областей 108 и 110 STI. Слой 150 может иметь горизонтальную ширину W5 на его верхней поверхности и высоту Н5 поверх части верхних поверхностей, таких как поверхности 116 и 118 областей 108 и 110 STI. W5 может быть меньше чем W4 и больше чем W3. Н5 может быть меньше чем H4 и больше чем H3. Ширина W5 может представлять собой ширину от 15 до 100 нанометров (нм). В некоторых случаях W5 составляет приблизительно 20 нм, высота Н5 может представлять собой высоту от 10 до 150 нанометров (нм). В некоторых случаях Н5 составляет приблизительно 60 нм.

На фиг. 4 также показаны структуры или маски 160 и 162, сформированные на участках полированной или выровненной верхней поверхности 164 слоя 150. В некоторых случаях, маски 160 и 162 имеют ширину W6, которая меньше, чем половина W5. Маски 160 и 162 могут иметь длину L1. Ширина W6 может представлять собой ширину от 5 до 50 нанометров (нм). В некоторых вариантах осуществления ширина W6 может представлять собой ширину от 2 до 5 нанометров (нм). В некоторых случаях W6 составляет приблизительно 5 нм.

Маски 160 и 162 могут иметь внутренние боковые стенки 166 и 168 поверх боковых стенок 112 и 114. Внутренние боковые стенки 166 и 168 могут представлять собой плоские поверхности, параллельные и выровненные (например, непосредственно выше) с плоскими боковыми стенками 112 и 114 (например, как показано пунктирной линией). Маски 160 и 162 могут иметь внешние боковые стенки 170 и 172 поверх поверхности 116 и 118. Внешние боковые стенки 170 и 172 могут представлять собой плоские поверхности, параллельные плоским боковым стенкам 112 и 114, и могут продолжаться на длину L поверх поверхностей 116 и 118.

В соответствии с некоторыми вариантами осуществления, W1 может составлять от 10 до 15 нанометров (нм); H1 может составлять 350 нанометров (нм); H2 может составлять 70 нанометров (нм); разность по высоте между вершиной слоя 120 и вершиной слоя 130 может составлять 200 нанометров (нм); и разность по высоте между вершиной слоя 130 и вершиной слоя 140 или слоя 150 может составлять 50 нанометров (нм). Кроме того, L1 может быть равна W1.

На фиг. 5 показана полупроводниковая подложка по фиг. 1 после формирования ребер из эпитаксиального материала, сформированного поверх областей STI. На фиг. 5 показаны ребра 180 и 190, сформированные из слоя 150, используя обработку влажного или сухого травления, для удаления слоев 150, 140, 130 и 120, которые не были защищены масками или под масками 160 и 162. В некоторых вариантах осуществления ребра 180 и 190 могут быть описаны, как "ребра устройства" или "ребра электронного устройства", на которых могут быть сформированы электронные устройства.

Такое вытравливание может удалять первую ширину слоев 150, 140, 130 и 120 внутри и выше щели 106 (например, и рядом или в непосредственной близости к внутренним боковым стенкам 166 и 168), для того, чтобы открыть поверхность 103 поверхности подложки. Такое вытравливание также позволяет удалять первую ширину слоев 130 и 120 в щели 106, для того, чтобы открыть боковые стенки 112 и 114. Такое вытравливание позволяет удалять ширину слоев 120, 130 и 140, расположенных между боковыми стенками 166 и 168, до глубины, на которой открывается верхняя поверхность подложки. В некоторых случаях, такое вытравливание может включать в себя избирательное вытравливание для обработки вытравливания только поверх щели (например, не без вытравливания на верхних поверхностях 116 и 118).

Такое вытравливание формирует щель 206. Щель 206 может включать в себя щель 106, и ширина (например, W1), и длина щели 106 превышают высоту Н5 (и высоту масок 160 или 162) поверх поверхностей 116 и 118. Такое вытравливание позволяет удалять первую ширину или участки слоев 150, 140, 130 и 120, включая в себя любые дефекты, которые могли присутствовать в материале 122 или 132 рядом или вдоль боковых стенок 112 и 114; и любые кристаллические дефекты в материалах 122, 132 или 142, из-за дефектов, включающих в себя дефекты упаковки, которые возникают на боковых стенках 112 или 114 STI. В некоторых вариантах осуществления, поскольку дефекты (например, кристаллические дефекты) в щели 106 не распространились или отсутствуют в областях поперечного эпитаксиального нароста (например, W6) слоя 140 или материала 142, ребра 180 и 190 могут предоставлять материал для электронного устройства (например, ямы и каналов), в которых могут быть сформированы не содержащие дефект устройства на основе ребра (например, в этой боковой области эпитаксиального нароста, которая представляет собой слой 140 на ребрах).

В некоторых случаях, такая же или отдельная обработка влажным или сухим вытравливанием может использоваться для удаления ширины слоев 150, 140 и 130 рядом с внешними боковыми стенками 170 и 172 и поверх поверхностей 116 и 118, чтобы открыть поверхности 116 и 118. Такое вытравливание позволяет удалять ширину слоев 130 и 140, расположенных на расстоянии от щели, чтобы открыть верхние поверхности 116 и 118. В некоторых случаях, такое вытравливание может включать в себя избирательное вытравливание, для обработки вытравливанием только верхних поверхностей 116 и 118 (например, без обработки вытравливанием поверх щели). В некоторых случаях, такое вытравливание может представлять собой обработку химическим вытравливанием, для обработки вытравливания, как поверх верхней поверхностей 116 и 118, так и поверх щели 106.

На фиг. 5 показаны ребра 180 и 190, сформированные на участках верхних поверхностей 116 и 118 над и продолжающихся по боковым стенкам 112 и 114. В некоторых случаях, ребра 180 и 190 имеют ширину W6 и высоту Н5, включающую в себя материал 130 и 140 (например, как слой 150). Ребра 180 и 190 могут иметь длину L1. Ребра 180 и 190 могут иметь (например, открытые) внутренние боковые стенки 182 и 192 поверх боковых стенок 112 и 114. Внутренние боковые стенки 182 и 192 могут представлять собой плоские поверхности, параллельные и выровненные с (например, непосредственно выше) плоскими боковыми стенками 112 и 114. Внутренние боковые стенки 182 и 192 могут представлять собой плоские поверхности, параллельные и выровненные с (например, непосредственно ниже) внутренними боковыми стенками 166 и 168. Ребра 180 и 190 могут иметь (например, открытые) внешние боковые стенки 184 и 194 поверх поверхностей 116 и 118. Внешние боковые стенки 184 и 194 могут представлять собой плоские поверхности, параллельные плоским боковым стенкам 112 и 114, и могут продолжаться вдоль длины L поверх поверхностей 116 и 118. Внешние боковые стенки 184 и 194 могут представлять собой плоские поверхности, параллельные и выровненные с (например, непосредственно ниже) внешними боковыми стенками 170 и 172.

На фиг. 6 показана полупроводниковая подложка по фиг. 1 после формирования слоя из материала STI поверх ребер и щели. На фиг. 6 показан слой 204 из материала 205 изоляции с мелкими щелями (STI), сформированного или выращенного на верхней поверхности 103; верхних поверхностях масок 160 и 162; и верхних поверхностях 116 и 118. В некоторых случаях, маски 160 и 162 могут быть удалены, и слой 204 формируется на верхних поверхностях ребер 180 и 190. Слой 204 может быть сформирован в щели 206 и может заполнять ее. Слой 204 может быть сформирован до высоты H6, которая больше, чем высота Н5 (и, в случае необходимости, больше чем высота масок 160 или 162). Материал 204 STI может быть сформирован аналогично материалу 104 и может иметь такую же кристаллическую ориентацию, как и у него, может иметь такой же размер кристаллической решетки, и может быть выполнен из ненапряженного материала, аналогично материалу 104. Материал 204 STI может представлять собой конформный слой или сплошной слой, сформированный поверх верхней поверхности 103; верхних поверхностей масок 160 и 162; и верхних поверхностей 116 и 118.

На фиг. 7 показана полупроводниковая подложка по фиг. 1 после полировки слоя STI, сформированного поверх ребер, щели и областей STI; и после вытравливания выемки, чтобы открыть боковые стенки устройства ребер электронного устройства или участков ребер. На фиг. 7 показаны ребра 180 и 190 после полировки или выравнивания слоя 204 STI до высоты выше или больше, чем высота H5 верхних поверхностей ребер 180 и 190; и после последующего вытравливания выемки в слое 204 STI до высоты H3, чтобы открыть боковые стенки устройства на ребрах, и для формирования слоя 214 STI. Полировка или выравнивание слоя 204 STI могут быть выполнены, используя химическую, физическую или механическую полировку, как известно в данной области техники, для формирования верхней плоской поверхности материала 205 на высоте, большей, чем высота Н5. После полировки впоследствии можно использовать влажное вытравливание сплошного слоя для формирования выемки на верхней поверхности выровненного материала 205 до высоты H3, чтобы открыть слой 140 устройства. При таком вытравливании может использоваться разбавленная HF в течение нескольких секунд для удаления, по меньшей мере, высоты H4 материала 205. Такое вытравливание может оставлять высоту H3 материала 205 поверх или выше верхних поверхностей 116 и 118; и поверх или выше высоты H1 в щели 206. Такое вытравливание может включать в себя раскрытие боковых стенок материала 142 (например, слоя 140), без раскрытия боковых стенок материала 132 (например, слоя 130). В некоторых случаях такое травление может вытравливать материал 205 до высоты выше или равной высоте H3, с тем, чтобы открыть слой 140 устройства на ребрах, но без раскрытия буферного слоя 130. Слой 140 может превышать высоту H3 и может быть раскрыт выше слоя 214, в то время как слой 130 находится ниже высоты H3 и не будет раскрыт выше слоя 214.

На фиг. 7 показаны участки 218 и 220 устройства на ребрах 180 и 190. В некоторых случаях, участки 218 и 220 могут быть описаны, как "ребра устройства" или "ребра электронного устройства", на которых могут быть сформированы электронные устройства. Участки устройства включают в себя слой 140 устройства из материала 142. В некоторых случаях участки устройства исключают буферный слой 130 или материал 132. На фиг. 7 показаны внутренние (например, открытые) боковые стенки 222 и 232 устройства на участках 218 и 220, соответственно; и внешние (например, открытые) боковые стенки 224 и 234 устройства на участках 218 и 220, соответственно. В некоторых случаях, участки 218 и 220 имеют ширину W6 и высоту H4 из материала 142, и длину L1. Внутренние боковые стенки 222 и 232 могут представлять собой плоские поверхности, параллельные и выровненные (например, непосредственно выше) с плоскими боковыми стенками 112 и 114. Внешние боковые стенки 224 и 234 могут представлять собой плоские поверхности, параллельные плоским боковым стенкам 112 и 114, и могут продолжаться вдоль длины L поверх поверхностей 116 и 118.

Боковые стенки 222, 224, 232 и 234 могут включать в себя достаточную высоту, ширину и длину материала 242 для обеспечения возможности формирования ямы и канала электронного устройства. Боковые стенки 222, 224, 232 и 234 могут включать в себя достаточную высоту, ширину и длину материала 242, так, чтобы сформировать в них или в нем электронное устройство в "ребре". Такие электронные устройства могут включать в себя транзисторы, резисторы, конденсаторы, и т.д. в интегральной схеме (IC) на ребре внутри или на боковых стенках. Такие устройства могут включать в себя транзисторные устройства из металлооксидного полупроводника (MOS) на ребре, такие как используются в комплементарном металлооксидном полупроводнике (CMOS), на основе движения электронов в каналах устройства MOS N-типа (n-MOS) и движения положительных заряженных дырок в каналах устройства MOS P-типа (p-MOS). В некоторых вариантах осуществления, поскольку дефекты (например, дефекты кристалла) в щели 106 не продолжаются в или не присутствуют в поперечных областях эпитаксиального нароста (например, участки 218 и 220), боковые стенки 222, 224, 232 и 234 могут обеспечивать материал для электронного устройства (например, ям и каналов), в котором могут быть сформированы устройства без дефектов на основе ребра (например, в той поперечной области эпитаксиального нароста, которая представляет собой участки 218 и 220).

В некоторых вариантах осуществления материал 122 слоя 120 может представлять собой или может включать в себя материал GaAs или InP N-типа. Материал 132 слоя 130 может представлять собой или может включать в себя материал InAlAs N-типа. Материал 142 слоя 140 может представлять собой или может включать в себя материал InAs или InGaAs N-типа. Эти материалы могут обеспечивать устройство на ребре, в большей степени свободное от дефектов из материала InGaAs или InAs N-типа, которое используется, как канал электронного устройства (например, устройства PMOS).

В некоторых вариантах осуществления материал 122 слоя 120 может представлять собой или может включать в себя материал Si70Ge30 P-типа (например, 70 процентов Si и 30 процентов Ge). Материал 132 слоя 130 может представлять собой или может включать в себя материал Si30Ge70 P-типа. Материал 142 слоя 140 может представлять собой или может включать в себя материал из Ge P-типа. Эти материалы могут обеспечивать устройство, в большей степени свободное от дефектов на ребре из материала Ge P-типа, который используется, как канал электронного устройства (например, устройства NMOS).

На фиг. 8 показана примерная обработка 800 для формирования пары из ребер электронного устройства. На фиг. 8 показана обработка 800, начинающаяся в блоке 804, где первый слой первого эпитаксиального материала эпитаксиально выращивают на поверхности подложки на дне щели, сформированной множеством областей узкощелевой изоляции (STI). Области STI могут быть сформированы на подложке для определения щелей между каждой парой областей. Области STI могут иметь боковые стенки STI, формирующие первую ширину W1 и первую высоту H1 щели. Первая высота H1 может составлять, по меньшей мере, 1,5 размера первой ширины W1. Первая ширина может составлять от 10 до 100 нм, и первая высота может составлять от 30 до 300 нм. Поверхность подложки может представлять собой кремний и имеет (100) индекс ориентации кристалла. Это может включать в себя использование более чем двух областей для определения каждой щели. Это может включать в себя щель 106, которая сформирована областями 108 и 110 STI. Блок 804 может включать в себя представленное выше описание, для формирования щели 106 и слоя 120 выращивания, как описано на фиг. 1-3.

Далее, в блоке 806, второй слой второго эпитаксиального материала эпитаксиально выращивают на первом слое в щели, поверх верхних поверхностей областей STI и для продолжения ширины поверх щели и поверх областей на верхних поверхностях областей STI. Блок 806 может включать в себя выращивание второго слоя до второй высоты, выше первой высоты H1, второй слой, имеющий вторую ширину, продолжающуюся поверх щели и поверх участков верхних поверхностей областей STI. Второй слой может представлять собой буферный слой, выращенный из верхней поверхности первого слоя, и слой устройства, выращенный из верхней поверхности буферного слоя. Блок 806 может включать в себя представленное выше описание для выращивания слоя 130, как описано со ссылкой на фиг. 1-3.

Далее, в блоке 812, второй слой структурируют и подвергают травлению для формирования пары ребер электронного устройства поверх участков верхних поверхностей областей STI. Каждый участок может располагаться проксимально (например, может быть расположен рядом или по соседству с) боковой стенке щели. В некоторых случаях, перед структуризацией, верхнюю поверхность второго слоя полируют для формирования плоской поверхности, имеющей третью высоту Н5 выше первой высоты H1 и выше верхних поверхностей областей STI. Вытравливание представляет собой влажное вытравливание. Вытравливание может включать в себя вытравливание второго и первого слоев для (1) удаления первой ширины первого и второго слоев над и внутри щели, чтобы раскрыть верхнюю поверхность подложки, и (2) удаления ширины второго эпитаксиального слоя над участками верхних поверхностей областей STI из щели. Блок 812 может включать в себя описание, представленное выше, структуризации и обработки травлением слоя 150 для формирования пары ребер электронного устройства, как описано со ссылкой на фиг. 4-5 или 4-7.

Далее, в необязательном блоке 816, формируется слой STI в вытравленной щели и над ребрами (не обязательно). Этот блок не выполняется в некоторых вариантах осуществления. Блок 816 может включать в себя описание, представленное выше для формирования слоя 204 STI, как описано со ссылкой на фиг. 6.

Далее, в не обязательном блоке 818, слой STI полируют для формирования плоской поверхности, расположенной поверх верхней поверхности (не обязательно) ребер. Этот блок не выполняется в некоторых вариантах осуществления. Блок 818 может включать в себя представленное выше описание для полировки слоя 204 STI, как описано со ссылкой на фиг. 7.

Далее, в не обязательном блоке 820, полированный слой STI подвергают обработке вытравливанием, чтобы раскрыть участок устройства каждого ребра, включающий в себя второй материал (не обязательно). Этот блок не выполняется в некоторых вариантах осуществления. Блок 820 может включать в себя представленное выше описание, для обработки вытравливанием слоя 204 STI, как описано со ссылкой на фиг. 7.

Далее, в не обязательном блоке 822, устройство транзистора может быть сформировано, по меньшей мере, на одной боковой стенке устройства каждого ребра (не обязательно). В некоторых случаях блок 822 включает в себя формирование устройств транзистора на каждой боковой стенке устройства каждого ребра (не обязательно). Этот блок не выполняется в некоторых вариантах осуществления. Блок 822 может включать в себя представленное выше описание для формирования устройств транзистора на боковой стенке устройства каждого ребра, как описано со ссылкой на фиг. 7.

В некоторых вариантах осуществления блоки 816-822 не выполняются при обработке 800. В некоторых вариантах осуществления блок 822 не выполняется при обработке 800.

На фиг. 9 показана примерная обработка 900 для формирования пары ребер электронного устройства. На фиг. 9 показана обработка 900, начинающаяся с необязательного блока 902, где множество областей STI, имеющих боковые стенки STI, сформировано на поверхности подложки (не обязательно). Этот блок не выполняется в некоторых вариантах осуществления. Области STI могут быть сформированы для определения щелей между каждой парой областей. Области STI могут иметь боковые стенки STI, образующие первую ширину W1 и первую высоту H1 щели. Это может включать в себя использование более чем двух областей для определения каждой щели. Первая высота H1 может составлять, по меньшей мере, 1,5 размера первой ширины W1. Первая ширина может составлять от 10 до 100 нм, и первая высота может составлять от 30 до 300 нм. Поверхность подложки может представлять собой кремний и имеет (100) индекс ориентации кристалла. Это может включать в себя формирование сплошного слоя из материала STI с последующей структуризацией и обработкой вытравливанием этого материала, для формирования областей 108 и 110 STI. Блок 902 может включать в себя представленное выше описание для формирования щели 106, как описано со ссылкой на фиг. 1-2.

Далее, в блоке 904, первый слой первого эпитаксиального материала подвергают эпитаксиальному выращиванию на поверхности подложки на дне щели, сформированной множеством областей узкощелевой изоляции (STI), имеющих боковые стенки STI. Первый слой может иметь вторую высоту H2, которая меньше, чем первая высота H1, и вторую ширину W2, меньшую, чем или равную первой ширине W1. Блок 904 может включать в себя представленное выше описание для формирования или выращивания слоя 120, как описано со ссылкой на фиг. 1-3.

Далее, в блоке 906, второй слой второго эпитаксиального материала эпитаксиально выращивают на первом слое в щели, и поверх верхних поверхностей областей STI и так, что он продолжается через щель и через первые участки верхних поверхностей областей STI. Блок 906 может включать в себя выращивание второго слоя до третьей высоты H3, которая выше, чем первая высота H1, второй слой, имеющий третью ширину, продолжающуюся поверх щели и поверх первых участков верхних поверхностей областей STI. Второй слой может представлять собой буферный слой, выращенный из верхней поверхности первого слоя и продолжающийся поверх и над областями STI. Блок 906 может включать в себя представленное выше описание для выращивания слоя 130, как описано со ссылкой на фиг. 1-3.

Далее, в блоке 908, третий слой третьего эпитаксиального материала эпитаксиально выращивают на верхней поверхности второго слоя, так, что он имеет ширину, продолжающуюся поверх верхней поверхности второго слоя и поверх второго участка верхних поверхностей областей STI. Блок 908 может включать в себя выращивание третьего слоя до четвертой высоты H4, выше первой высоты H1, четвертая высота H4 больше, чем третья высота H3, и третий слой, имеющий четвертую ширину W4, продолжающуюся поверх верхней поверхности второго слоя и поверх вторых участков верхней поверхности областей STI. Третий слой может представлять собой слой устройства, выращенный из верхней поверхности второго слоя, и слой устройства может иметь такую же постоянную кристаллической решетки, как и дно верхней поверхности первого слоя. Блок 908 может включать в себя описание, представленное выше, для выращивания слоя 140, как описано со ссылкой на фиг. 1-3.

Далее, в блоке 910, верхняя поверхность третьего слоя отполирована так, что формируется четвертый слой, имеющий плоскую поверхность. Четвертый слой может включать в себя второй эпитаксиальный материал и третий эпитаксиальный материал. Плоская поверхность может иметь пятую ширину W5, четвертый слой может иметь пятую высоту Н5 выше первой высоты H1 и поверх верхних поверхностей областей STI, пятая высота Н5 может быть меньше, чем четвертая высота H4, и больше, чем третья высота H3. Блок 910 может включать в себя представленное выше описание для полировки слоя 140, для формирования слоя 150, как описано со ссылкой на фиг. 4.

Далее, в блоке 912, плоскую поверхность структурируют для формирования двух масок поверх участков четвертого слоя. Это может включать в себя структурирование плоской поверхности, для формирования двух масок поверх участков пятой ширины W5, каждый из этих участков, имеющих шестую ширину, меньшую, чем половина пятой ширины, каждый из участков расположен проксимально или расположен рядом с боковыми стенками щели, каждый из участков расположен поверх верхних поверхностей областей STI. Блок 912 может включать в себя описание, представленное выше, для структурирования плоской верхней поверхности слоя 150, для формирования пары ребер электронного устройства, как описано со ссылкой на фиг. 4-5.

Далее, в блоке 914, четвертый, второй и первый слои повергают вытравливанию, для формирования пары ребер электронного устройства поверх участков верхних поверхностей областей STI. Каждое ребро может быть расположено проксимально (например, рядом с или в непосредственной близости) к боковой стенке щели. Вытравливание может представлять собой влажное вытравливание. Вытравливание может включать в себя вытравливание для удаления первой ширины первого, второго и четвертого эпитаксиальных слоев в щели, для того, чтобы раскрыть верхнюю поверхность подложки 103; и для того, чтобы удалить ширину второго и четвертого эпитаксиальных слоев поверх участков четвертой ширины и на расстоянии от щели, для того, чтобы раскрыть верхние поверхности областей STI. Влажное вытравливание может включать в себя формирование пары ребер электронного устройства, включающих в себя (1) участок второго материала, имеющий третью ширину W3, продолжающуюся поверх первых участков верхних поверхностей областей STI, и (2) участок третьего материала, имеющий четвертую ширину W4, продолжающуюся поверх верхней поверхности второго слоя и поверх первых участков верхних поверхностей областей STI. Блок 914 может включать в себя представленное выше описание для вытравливания слоя 150, для формирования пары ребер электронного устройства, как описано со ссылкой на фиг. 4-5 или 4-7.

Далее, в необязательном блоке 916, формируется слой STI в вытравленной щели и поверх ребер (не обязательно). Этот блок не выполняется в некоторых вариантах осуществления. Блок 916 может включать в себя представленное выше описание для формирования слоя 204 STI, как описано со ссылкой на фиг. 6.

Далее, в необязательном блоке 918, слой STI полируют для формирования плоской поверхности, поверх верхней поверхности ребер (не обязательно). Этот блок не выполняется в некоторых вариантах осуществления. Блок 918 может включать в себя представленное выше описание для полировки слоя 204 STI, как описано со ссылкой на фиг. 7.

Далее, в необязательном блоке 920, отполированный слой STI подвергают обработке вытравливанием, для того, чтобы раскрыть участок устройства каждого ребра, включающего в себя третий материал (не обязательно). Этот блок не выполняется в некоторых вариантах осуществления. Блок 920 может включать в себя представленное выше описание для вытравливания слоя 204 STI, как описано со ссылкой на фиг. 7.

Далее, в необязательном блоке 922, транзисторное устройство может быть сформировано на каждой боковой стенке устройства каждого ребра (не обязательно). В некоторых случаях блок 922 включает в себя формирование транзисторных устройств на меньше, чем на боковых стенках каждого устройства каждого ребра (не обязательно). Этот блок не выполняется в некоторых вариантах осуществления. Блок 922 может включать в себя представленное выше описание для формирования транзисторных устройств на боковых стенках устройства каждого ребра, как описано со ссылкой на фиг. 7.

В некоторых вариантах осуществления блоки 902 и 916-922 не выполняются при обработке 900. В некоторых вариантах осуществления блоки 902 и 922 не выполняются при обработке 900. В некоторых вариантах осуществления блоки 916-922 не выполняются при обработке 900. В некоторых вариантах осуществления блок 922 не выполняется при обработке 900.

Для формирования ребер 180 и 190 электронного устройства (или участков 218 и 220), как описано здесь, возможно исключить или свести к минимуму дефекты кристаллов, которые образуются в ребрах из-за или в результате значительного различия между постоянными кристаллических решеток в материалах, когда некоторые материалы (например, типа III-V, или материалы Ge) эпитаксиально выращивают на подложке из кремниевого материала, в щелях между областями STI. Такие дефекты включают в себя те, которые захвачены, или те, которые располагаются вдоль боковой стенки STI, формирующей щели, и другие дефекты, включая в себя дефекты упаковки, которые возникают на боковой стенке STI, которые все еще остаются в пределах щели. Исключение или сведение к минимуму таких дефектов кристалла может привести к снижению проблем производительности и вариаций в устройстве, построенном на слое устройства или на боковой стенке устройства ребер. Формирование ребер 180 и 190 (или участков 218 и 220) может помочь детектировать рост дефектных свободных областей за пределами щели, которые могут использоваться для изготовления устройства, вместо попытки уменьшить ошибки упаковки (и дислокации) в пределах щели. Это также может привести к тому, что качество или дефекты в эпитаксиальных материалах в пределах щели не будут иметь отношение или не будут влиять на качество ребер 180 и 190 (или участков 218 и 220).

На фиг. 10 иллюстрируется вычислительное устройство 1000, в соответствии с одним вариантом осуществления. В вычислительном устройстве 1000 установлена печатная плата 1002. Печатная плата 1002 может включать в себя множество компонентов, включающих в себя, но без ограничений, процессор 1004 и, по меньшей мере, одну микросхему 1006 передачи данных. Процессор 1004 физически и электрически соединен с печатной платой 1002. В некоторых вариантах осуществления, по меньшей мере, одна микросхема 1006 передачи данных также физически и электрически соединена с печатной платой 1002. В дополнительных вариантах осуществления печатная плата 1006 передачи данных представляет собой часть процессора 1004.

В зависимости от вариантов его применения вычислительное устройство 1000 может включить в себя другие компоненты, которые могут быть физически соединены или могут не быть физически соединены с печатной платой 1002. Эти другие компоненты включают в себя, но без ограничений, энергозависимое запоминающее устройство (например, DRAM), энергонезависимое запоминающее устройство (например, ROM), запоминающее устройство флеш, графический процессор, цифровой сигнальный процессор, криптопроцессор, набор микросхем, антенну, дисплей, сенсорный дисплей, контроллер сенсорного дисплея, аккумуляторную батарею, аудиокодек, видеокодек, усилитель мощности, устройство системы глобальной навигации (GPS), компас, акселерометр, гироскоп, громкоговоритель, камеру и устройство массового накопителя (такое как привод жесткого диска, компактный диск (CD), цифровой универсальный диск (DVD) и т.д.).

Микросхема 1006 передачи данных обеспечивает возможность беспроводной передачи данных для передачи данных в и из вычислительного устройства 1000. Термин "беспроводный" и его производные может использоваться для описания схем, устройства, системы, способов, технологии, каналов передачи данных и т.д., которые позволяют передавать данные путем использования модулированного электромагнитного излучения через нетвердую среду. Этот термин не подразумевает, что соответствующие устройства не содержат какие-либо провода, хотя в некоторых вариантах осуществления они могут их не содержать. В микросхеме 1006 передачи данных может быть воплощено любое количество стандартов беспроводной передачи данных или протоколов, включающих в себя, но без ограничений Wi-Fi (семейство стандартов IEЕЕ 802.11), WiMAX (семейство стандартов IEEE 802.16), IEEE 802.20, долгосрочное развитие (LTE), Ev-DO, HSPA+, HSDPA+, HSUPA+, EDGE, GSM, GPR, CDMA, TDMA, DECT, Bluetooth, их производные, а также любые из других протоколов беспроводной передачи данных, которые обозначены, как 3G, 4G, 5G и так далее. Вычислительное устройство 1000 может включать в себя множество микросхем 1006 передачи данных.

Например, первая микросхема 1006 передачи данных может быть предназначена для беспроводной передачи данных на коротком расстоянии, таком как Wi-Fi и Bluetooth, и вторая микросхема 1006 передачи данных может быть предназначена для беспроводной передачи данных на большее расстояние, такое как GPS, EDGE, GPR, CDMA, WiMAX, LTE, Ev-DO и другие.

Процессор 1004 вычислительного устройства 1000 включает в себя кристалл интегральной микросхемы, упакованный внутри процессора 1004. В некоторых вариантах осуществления кристалл интегральной микросхемы включает в себя многоуровневое взаимное соединение, включающее в себя монолитное исполнение линий проводной развязки, и межслойных переходов, которые позволяют сформировать воздушные зазоры в узле взаимного соединения, как описано со ссылкой на фиг. 1-6. Термин "процессор" может относиться к любому устройству или части устройства, которое обрабатывает электронные данные из регистров и/или запоминающих устройств для преобразования этих электронных данных в другие электронные данные, которые могут быть сохранены в регистрах и/или в запоминающем устройстве.

Микросхема 1006 передачи данных также включает в себя кристаллы интегральной схемы, упакованные в микросхеме 1006 передачи данных. В соответствии с другим вариантом осуществления, пакет, включающий в себя интегральную схему передачи данных, включает один или больше конденсаторов, как описано выше.

В дополнительных вариантах осуществления другой компонент, расположенный в вычислительном устройстве 1000, может содержать микроэлектронный пакет, включающий в себя кристаллы интегральной схемы, как описано выше.

В различных вариантах осуществления вычислительное устройство 1000 может представлять собой переносной компьютер, компьютер нетбук, компьютер - записную книжку, ультрабук, смартфон, планшетный компьютер, карманный персональный компьютер (PDA), ультрамобильный персональный компьютер, мобильный телефон, настольный компьютер, сервер, принтер, сканер, монитор, телевизионную приставку, модуль управления развлечениями, цифровую камеру, портативный музыкальный проигрыватель, или цифровое устройство видеозаписи. В дополнительных вариантах осуществления вычислительное устройство 1000 может представлять собой любое другое электронное устройство, которое обрабатывает данные.

Примеры

Следующие примеры относятся к вариантам осуществления.

Пример 1 направлен на способ для формирования пары ребер электронного устройства, включающий в себя эпитаксиальное выращивание первого слоя из первого эпитаксиального материала на поверхности подложки на дне щели, сформированной множеством областей узкощелевой изоляции (STI), имеющих боковые стенки STI, образующие первую ширину и первую высоту щели; эпитаксиальное выращивание второго слоя из второго эпитаксиального материала на первом слое в щели и поверх верхних поверхностей областей STI второй высоты, которая выше, чем первая высота, второй слой, имеющий вторую ширину, продолжающуюся поверх щели и поверх участков верхних поверхностей областей STI; и структурирование и обработка травлением второго слоя для формирования пары ребер электронных устройств поверх участков верхних поверхностей областей STI, каждый из участков расположен проксимально к боковым стенкам щели.

В примере 2 обработка травлением в способе по примеру 1 включает в себя обработку травлением второго и первого слоев для (1) удаления первой ширины первого и второго слоев сверху и внутри щели для того, чтобы раскрыть верхнюю поверхность подложки, и (2) удаление ширины второго эпитаксиального слоя поверх участков верхних поверхностей областей STI на расстоянии от щели.

В примере 3 способ по примеру 1 дополнительно включает в себя формируют слой STI в обработанной травлением щели и поверх ребер; полируют слой STI для формирования плоской поверхности поверх верхней поверхности ребер; и подвергают обработке травлением отполированный слой STI для того, чтобы раскрыть участок устройства в каждом ребре, включающем в себя второй материал.

В примере 4 способ по примеру 3 дополнительно включает в себя формирование транзисторного устройства, по меньшей мере, на одной боковой стенке устройства каждого ребра.

В примере 5 первая высота по примеру 1 составляет, по меньшей мере, 1,5 размера первой ширины.

В примере 6 первая ширина по примеру 1 составляет от 10 до 100 нанометров (нм), и первая высота составляет от 30 до 300 нм.

В примере 7 поверхность подложки по примеру 1 представляет собой кремний и имеет (100) индекс кристаллической ориентации.

В примере 8 второй слой по примеру 1 включает в себя буферный слой, выращенный из верхней поверхности первого слоя, и слой устройства, выращенный из верхней поверхности буферного слоя.

В примере 9 способ по примеру 1 дополнительно включает в себя, перед структуризацией, полируют верхнюю поверхность второго слоя для формирования плоской поверхности, имеющей третью высоту над первой высотой и поверх верхних поверхностей областей STI.

В примере 10 представлен способ для формирования пары ребер электронного устройства, включающий в себя эпитаксиальное выращивание первого слоя первого эпитаксиального материала на поверхности подложки на дне щели, сформированной множеством областей узкощелевой изоляции (STI), имеющих боковые стенки STI, образующие первую ширину и первую высоту щели, в котором первый слой имеет вторую высоту, которая меньше, чем первая высота; эпитаксиальное выращивание второго слоя из второго эпитаксиального материала на первом слое щели и поверх верхних поверхностей областей STI до третьей высоты, которая выше первой высоты, второй слой, имеющий третью ширину, продолжающуюся поверх щели, и поверх первых участков верхних поверхностей областей STI; эпитаксиальное выращивание третьего слоя третьего эпитаксиального материала на верхней поверхности второго слоя до четвертой высоты, которая выше, чем первая высота, четвертая высота выше, чем третья высота, и третий слой, имеющий четвертую ширину, продолжающуюся поверх верхней поверхности второго слоя и поверх вторых участков верхних поверхностей областей STI; полировку верхней поверхности третьего слоя для формирования четвертого слоя, имеющего плоскую поверхность с пятой шириной, четвертый слой, имеющий пятую высоту, которая больше, чем первая высота, и поверх верхних поверхностей областей STI, пятая высота меньше, чем четвертая высота, и больше, чем третья высота; структурирование плоской поверхности для формирования двух масок поверх участков пятой ширины, каждый из участков, имеющий шестую ширину, которая меньше, чем половина пятой ширины, каждый из участков расположен проксимально боковым стенкам щели, каждый из участков расположен поверх верхних поверхностей областей STI; и обработку травлением четвертого, второго и первого слоев для формирования пары ребер электронного устройства: для удаления первой ширины первого, второго и четвертого эпитаксиальных слоев в щели для того, чтобы открыть верхнюю поверхность подложки; для удаления ширины второго и четвертого эпитаксиальных слоев поверх участков четвертой ширины и на расстоянии от щели, для раскрытия верхних поверхностей областей STI.

В примере 11 первая высота примера 10 составляет, по меньшей мере, 1,5 размера первой ширины, и в котором первый слой имеет вторую ширину, которая меньше чем или равна первой ширине.

В примере 12 второй слой по примеру 10 включает в себя буферный слой, выращенный из верхней поверхности первого слоя.

В примере 13 третий слой по примеру 10 включает в себя слой устройства, выращенный из верхней поверхности второго слоя.

В примере 14, слой устройства по примеру 13 имеет такую же постоянную кристаллической решетки, как и верхняя поверхность второго слоя.

В примере 15 четвертый слой по примеру 10 включает в себя второй эпитаксиальный материал и третий эпитаксиальный материал.

В примере 16 влажное травление по примеру 10 включает в себя: формируют пару ребер электронного устройства, включающих в себя (1) участок второго материала, имеющий третью ширину, продолжающуюся поверх первых участков верхних поверхностей областей STI, и (2) участок третьего материала, имеющий четвертую ширину, продолжающуюся поверх верхней поверхности второго слоя и поверх первых участков верхних поверхностей областей STI.

В примере 17 способ по примеру 10 дополнительно включает в себя: формируют слой STI в вытравленной щели и поверх ребер; полируют слой STI для формирования плоской поверхности, поверх верхней поверхности ребер; и вытравливают отполированный слой STI для того, чтобы раскрыть участок устройства каждого ребра, включающий в себя третий материал, каждый участок устройства имеет две боковых стенки устройства.

В примере 18 способ по примеру 10 дополнительно включает в себя: формируют транзисторное устройство на двух боковых стенках устройства каждого ребра.

Пример 19 представляет собой способ для формирования пары ребер электронного устройства, включающий в себя эпитаксиальное выращивание первого слоя первого эпитаксиального материала на поверхности подложки на дне щели, сформированной множеством областей узкощелевой изоляции (STI), имеющих боковые стенки STI, образующие первую ширину и первую высоту щели; эпитаксиальное выращивание второго слоя из второго эпитаксиального материала на первом слое в щели и поверх верхних поверхностей областей STI, до второй высоты, которая выше, чем первая высота, второй слой, имеющий вторую ширину, продолжающуюся поверх щели и поверх участков верхних поверхностей областей STI; структурирование и обработку вытравливанием второго слоя для формирования пары ребер электронного устройства поверх участков верхних поверхностей областей STI, каждый из участков расположен проксимально боковым стенкам щели; формирование слоя STI в вытравленной щели и поверх ребер; полируют слой STI для формирования плоской поверхности над верхней поверхностью ребер; подвергают обработке вытравливанием полированный слой STI для раскрытия участка устройства каждого ребра, включающего в себя второй материал; и формирования транзисторного устройства на двух боковых стенках устройства каждого ребра.

В примере 20 влажное травление по примеру 19 включает в себя: травление второго и первого слоев для (1) удаления первой ширины первого и второго слоев над и внутри щели для того, чтобы раскрыть верхнюю поверхность подложки, и для (2) удаления ширины второго эпитаксиального слоя над участками верхних поверхностей областей STI на расстоянии от щели.

В представленном выше описании, с целью пояснения, были представлены различные конкретные детали для обеспечения полного понимания вариантов осуществления. Однако, как должно быть понятно для специалиста в данной области техники, один или больше из других вариантов осуществления могут быть выполнены на практике без некоторых из этих конкретных деталей. Конкретные описанные варианты осуществления не предусмотрены для ограничения вариантов осуществления изобретения, но для их иллюстрации. Объем вариантов осуществления изобретения не следует определять по конкретным примерам, представленным выше, но только по представленной ниже формуле изобретения. В других случаях хорошо известные структуры, устройства и операции были показаны в форме блок-схемы или без деталей для того, чтобы исключить усложнение для понимания описания. В случае, когда это считается соответствующим, номера ссылочных позиций или оконечные участки номеров ссылочных позиций повторяются на чертежах для обозначения соответствующих или аналогичных элементов, которые, в случае необходимости, могут иметь аналогичные характеристики.

Также следует понимать, что ссылка в данном описании на "один вариант осуществления", "вариант осуществления", "один или больше вариантов осуществления" или "разные варианты осуществления", например, означает, что определенное свойство может быть включено на практике в варианты осуществления. Аналогично, также следует понимать, что в описании различные свойства иногда сгруппированы вместе в одном варианте осуществления, на одном чертеже или в его описании, с целью упрощения раскрытия и для помощи в понимании различных изобретательных аспектов. Данный подход к раскрытию, однако, не следует интерпретировать, как отражающий вариант осуществления, который требует больше свойств, чем в явном виде описано в каждой формуле изобретения. Скорее всего, как отражено в следующей формуле изобретения, изобретательные аспекты вариантов осуществления могут находиться в менее чем во всех свойствах одного раскрытого варианта осуществления. Например, хотя описания и чертежи, представленные выше, описывают формирование одой пары ребер электронного устройства, описания и чертежи, представленные выше, могут применяться для формирования одной пары ребер N-типа, с использованием щели 106, и одной пары ребер P-типа, с использованием соседней щели 5. Благодаря маскированию щелей (и, в случае необходимости, области вокруг щелей) ребра N-типа или ребра P-типа могут быть сформированы одновременно или одно за другим. Таким образом, формула изобретения, следующая после подробного описания изобретения, тем самым, явно внедрена в это подробное описание изобретения, так, что каждый пункт формулы изобретения можно рассматривать как отдельный вариант осуществления изобретения.

Изобретение относится к структурам электронных схем. Ребра электронного устройства сформированы путем эпитаксиального выращивания первого слоя материала поверх поверхности подложки на дне щели, сформированной между боковыми стенками областей узкощелевой изоляции (STI). Высота щели может составлять, по меньшей мере, 1,5 размера ее ширины, и первый слой может заполнять меньше, чем высоту щели. Затем второй слой из материала может быть эпитаксиально выращен на первом слое щели и поверх верхних поверхностей областей STI. Второй слой может иметь вторую ширину, продолжающуюся поверх щели и поверх участков верхних поверхностей областей STI. Второй слой может затем быть структурирован и может быть вытравлен для формирования пары ребер электронного устройства поверх участков верхних поверхностей областей STI, проксимально щели. Изобретение позволяет исключить дефекты кристаллов в ребрах, из-за различия между постоянными кристаллических решеток на границе перехода слоев. 3 н. и 17 з.п. ф-лы, 10 ил.

1. Способ формирования пары ребер электронного устройства, характеризующийся тем, что:

выполняют эпитаксиальное выращивание первого слоя первого эпитаксиального материала на поверхности подложки на дне щели, сформированной несколькими областями узкощелевой изоляции (STI), имеющими боковые стенки STI, определяющие первую ширину и первую высоту щели;

выполняют эпитаксиальное выращивание второго слоя второго эпитаксиального материала на первом слое в щели и поверх верхних поверхностей областей STI до второй высоты над первой высотой, причем второй слой имеет вторую ширину, простирающуюся поверх щели и поверх участков верхних поверхностей областей STI; и

структурируют и вытравливают второй слой для формирования пары ребер электронного устройства поверх участков верхних поверхностей областей STI, при этом каждый из указанных участков расположен рядом с боковыми стенками щели.

2. Способ по п. 1, в котором травление включает в себя травление второго и первого слоев для (1) удаления первого и второго слоев на первой ширине сверху и внутри щели для того, чтобы раскрыть верхнюю поверхность подложки, и для (2) удаления второго эпитаксиального слоя поверх участков верхних поверхностей областей STI на ширине, находящейся на расстоянии от щели.

3. Способ по п. 1, в котором также:

формируют слой STI в обработанной травлением щели и поверх ребер;

полируют слой STI для формирования плоской поверхности поверх верхней поверхности ребер; и подвергают обработке травлением отполированный слой STI для того, чтобы раскрыть участок каждого ребра устройства, содержащий второй материал.

4. Способ по п. 3, в котором также:

формируют транзисторное устройство по меньшей мере на одной боковой стенке устройства каждого ребра.

5. Способ по п. 1, в котором первая высота составляет по меньшей мере 1,5 размера первой ширины.

6. Способ по п. 1, в котором первая ширина составляет от 10 до 100 нанометров (нм), и первая высота составляет от 30 до 300 нм.

7. Способ по п. 1, в котором поверхность подложки является кремниевой и имеет индекс (100) ориентации кристалла.

8. Способ по п. 1, в котором второй слой содержит буферный слой, выращенный от верхней поверхности первого слоя, и слой устройства, выращенный от верхней поверхности буферного слоя.

9. Способ по п. 1, в котором также перед структуризацией полируют верхнюю поверхность второго слоя для формирования плоской поверхности, имеющей третью высоту над первой высотой и поверх верхних поверхностей областей STI.

10. Способ формирования пары ребер электронного устройства, характеризующийся тем, что:

выполняют эпитаксиальное выращивание первого слоя первого эпитаксиального материала на поверхности подложки на дне щели, сформированной несколькими областями узкощелевой изоляции (STI), имеющими боковые стенки STI, определяющие первую ширину и первую высоту указанной щели, при этом первый слой имеет вторую высоту, которая меньше, чем первая высота;

выполняют эпитаксиальное выращивание второго слоя второго эпитаксиального материала на первом слое в щели и поверх верхних поверхностей областей STI до третьей высоты над первой высотой, при этом второй слой имеет третью ширину, простирающуюся поверх щели и поверх первых участков верхних поверхностей областей STI;

выполняют эпитаксиальное выращивание третьего слоя третьего эпитаксиального материала на верхней поверхности второго слоя до четвертой высоты над первой высотой, причем четвертая высота больше, чем третья высота, и третий слой имеет четвертую ширину, простирающуюся поверх верхней поверхности второго слоя и поверх вторых участков верхних поверхностей областей STI;

полируют верхнюю поверхность третьего слоя для формирования четвертого слоя, имеющего плоскую поверхность с пятой шириной, при этом четвертый слой имеет пятую высоту над первой высотой и над верхними поверхностями областей STI, пятая высота меньше, чем четвертая высота, но больше, чем третья высота;

структурируют плоскую поверхность для формирования двух масок поверх участков указанной пятой ширины, при этом каждый из указанных участков имеет шестую ширину, которая меньше, чем половина пятой ширины, каждый из указанных участков расположен рядом с боковыми стенками щели, и поверх верхних поверхностей областей STI; и

выполняют травление четвертого, второго и первого слоев для формирования пары ребер электронного устройства таким образом, чтобы:

удалить на указанной первой ширине первый, второй и четвертый эпитаксиальные слои в щели, с тем чтобы открыть верхнюю поверхность подложки;

удалить второй и четвертый эпитаксиальные слои на участках четвертой ширины на расстоянии от щели, с тем чтобы открыть верхние поверхности областей STI.

11. Способ по п. 10, в котором первая высота составляет по меньшей мере 1,5 размера первой ширины, при этом первый слой имеет вторую ширину, которая меньше или равна указанной первой ширине.

12. Способ по п. 10, в котором второй слой содержит буферный слой, выращенный от верхней поверхности первого слоя.

13. Способ по п. 10, в котором третий слой содержит слой устройства, выращенный от верхней поверхности второго слоя.

14. Способ по п. 13, в котором слой устройства имеет такую же постоянную кристаллической решетки, как и верхняя поверхность второго слоя.

15. Способ по п. 10, в котором четвертый слой содержит второй эпитаксиальный материал и третий эпитаксиальный материал.

16. Способ по п. 10, в котором пара ребер электронного устройства, формируемая при влажном травлении, содержит (1) участок второго материала, имеющий третью ширину, простирающуюся поверх первых участков верхних поверхностей областей STI, и (2) участок третьего материала, имеющий четвертую ширину, простирающийся поверх верхней поверхности второго слоя и поверх первых участков верхних поверхностей областей STI.

17. Способ по п. 10, в котором также:

формируют слой STI в вытравленной щели и поверх ребер;

полируют слой STI для формирования плоской поверхности поверх верхней поверхности ребер; и

вытравливают полированный слой STI, чтобы раскрыть участок устройства каждого ребра, включающий третий материал, при этом каждый участок устройства имеет две боковых стенки устройства.

18. Способ по п. 17, в котором также формируют транзисторное устройство на указанных двух боковых стенках устройства каждого ребра.

19. Способ формирования пары ребер электронного устройства, характеризующийся тем, что:

выполняют эпитаксиальное выращивание первого слоя первого эпитаксиального материала на поверхности подложки на дне щели, сформированной несколькими областями узкощелевой изоляции (STI), имеющими боковые стенки STI, определяющие первую ширину и первую высоту канавки;

выполняют эпитаксиальное выращивание второго слоя второго эпитаксиального материала на первом слое в щели и поверх верхних поверхностей областей STI, до второй высоты над первой высотой, при этом второй слой имеет вторую ширину, простирающуюся поверх щели и поверх участков верхних поверхностей областей STI;