Область техники, к которой относится изобретение

Варианты осуществления, описанные в настоящем документе, относятся к области изготовления электронного устройства и, в частности, к изготовлению устройств на основе материалов III-V групп.

Предпосылки создания изобретения

Как правило, когда новые материалы, например материалы III-V групп, выращивают на кремниевой ("Si") подложке, образуются дефекты из-за несоответствия решеток. Эти дефекты могут снизить подвижность носителей (например, электронов, дырок или и тех, и других) в этих материалах III-V групп.

Из-за образования дефектов интеграция устройств на основе материалов III-V групп, устройств на основе германия или других устройств на основе материалов с несогласованной решеткой на кремниевой подложке для систем с комплементарными металлооксидными полупроводниками ("CMOS") представляет собой большую проблему.

В настоящее время для формирования устройств MOS III-V групп на кремниевой подложке используется эпитаксия в отобранных областях. Обычно, эпитаксией в отобранных областях называется локальное выращивание эпитаксиального слоя с использованием структурированной диэлектрической маски, нанесенной на полупроводниковую подложку. Из-за несогласованности решетки, когда устройства на основе III-V групп локально выращивают на структурированной кремниевой подложке, образуются дефекты. В настоящее время в уровне техники отсутствует решение для интеграции устройств MOS на основе материалов III-V групп n-типа и р-типа на кремниевой подложке.

Краткое описание чертежей

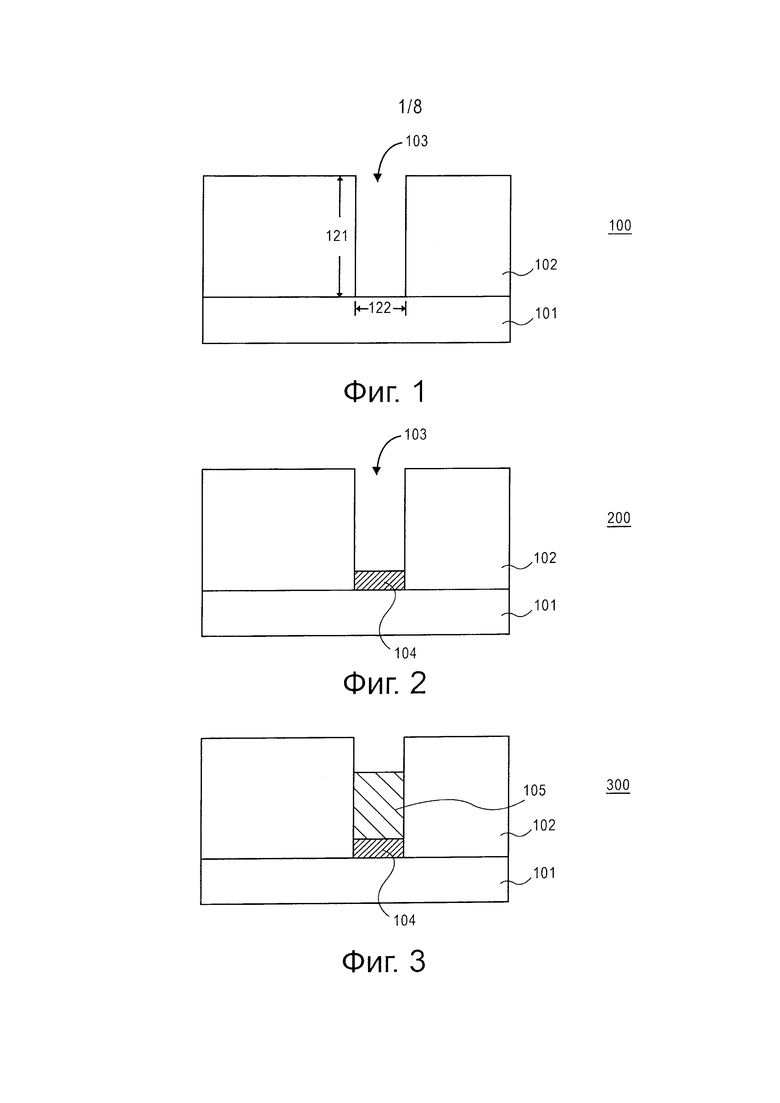

На фиг. 1 показан вид в поперечном сечении структуры электронного устройства в соответствии с одним вариантом осуществления.

На фиг. 2 показан вид в поперечном сечении, аналогичный фиг. 1, после осаждения первого буферного слоя на подложке в соответствии с одним вариантом осуществления.

На фиг. 3 показан вид в поперечном сечении, аналогичный фиг. 2, после осаждения второго буферного слоя на первый буферный слой в соответствии с одним вариантом осуществления.

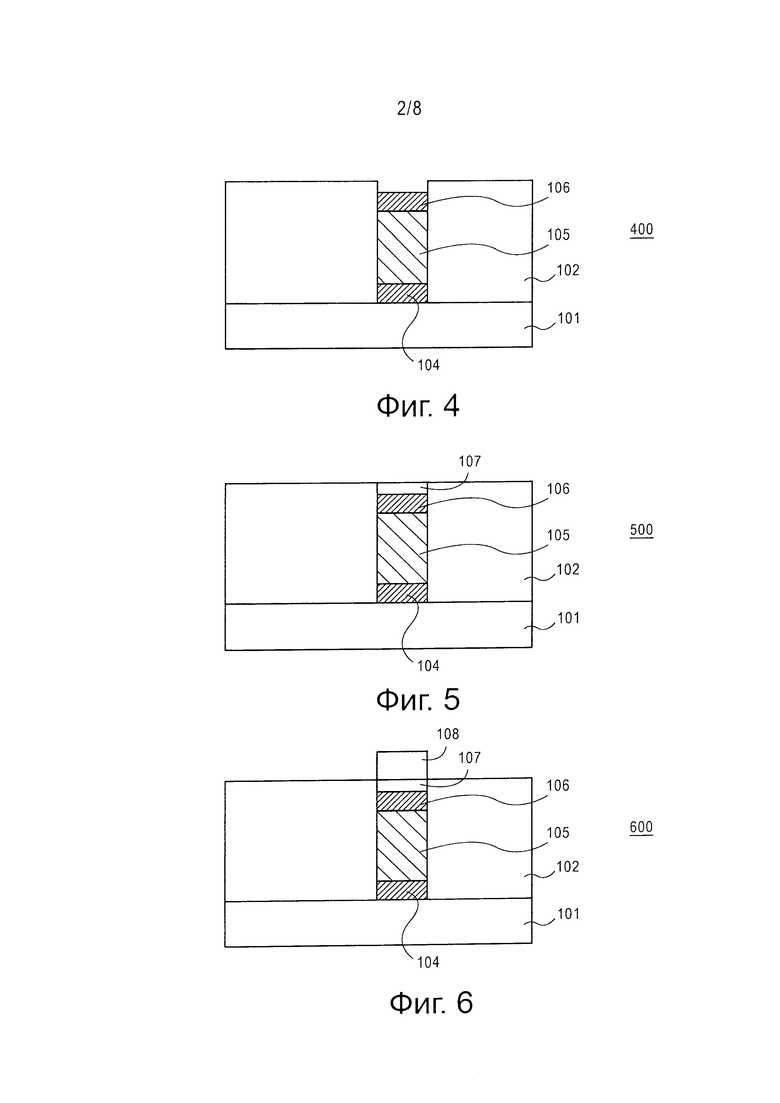

На фиг. 4 показан вид в поперечном сечении, аналогичный фиг. 3, после осаждения слоя устройства на второй буферный слой в соответствии с одним вариантом осуществления.

На фиг. 5 показан вид в поперечном сечении, аналогичный фиг. 5, после выращивания необязательного тонкого верхнего защитного слоя на слое устройства в соответствии с одним вариантом осуществления.

На фиг. 6 показан вид в поперечном сечении, аналогичный фиг. 5, после осаждения сильнолегированного слоя на слой устройства в соответствии с одним вариантом осуществления.

На фиг. 7 показан вид в поперечном сечении, аналогичный фиг. 6, после удаления сильнолегированного слоя истока/стока из области затвора устройства в соответствии с одним вариантом осуществления.

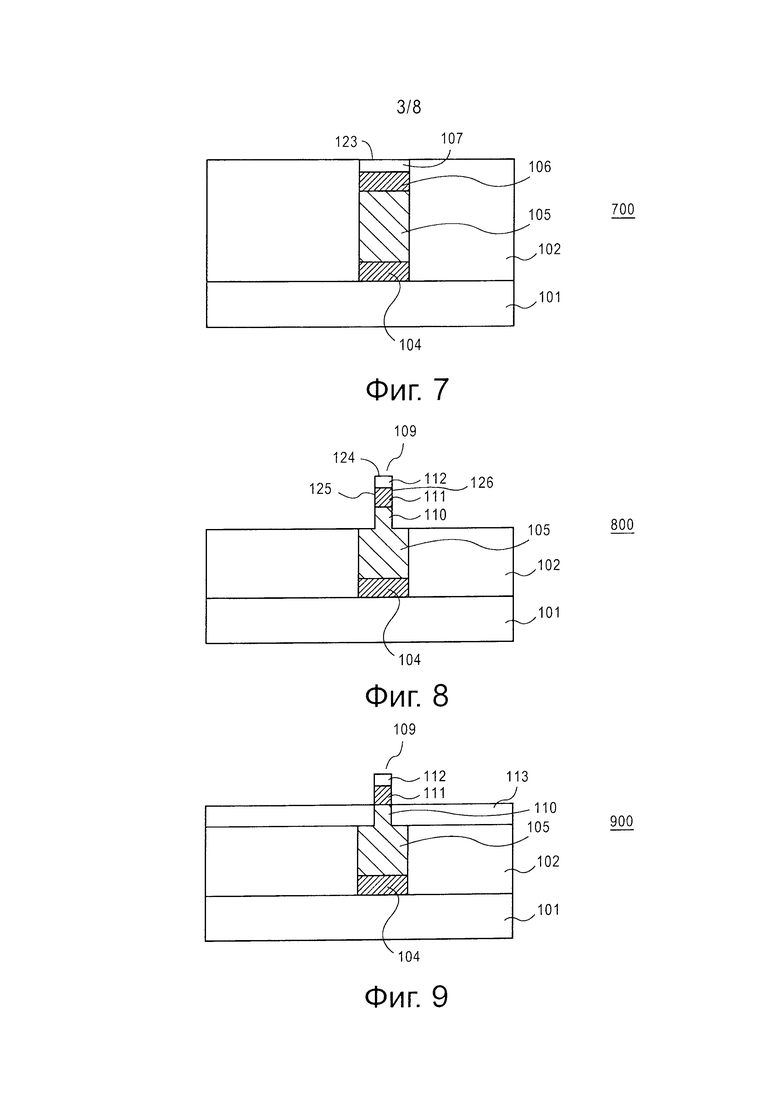

На фиг. 8 показан вид в поперечном сечении, аналогичный фиг. 7, после формирования ребра устройства в соответствии с одним вариантом осуществления.

На фиг. 9 показан вид в поперечном сечении, аналогичный фиг. 8, после осаждения изолирующего слоя на изолирующий слой, смежный с боковыми стенками участка первого буферного слоя, в соответствии с одним вариантом осуществления.

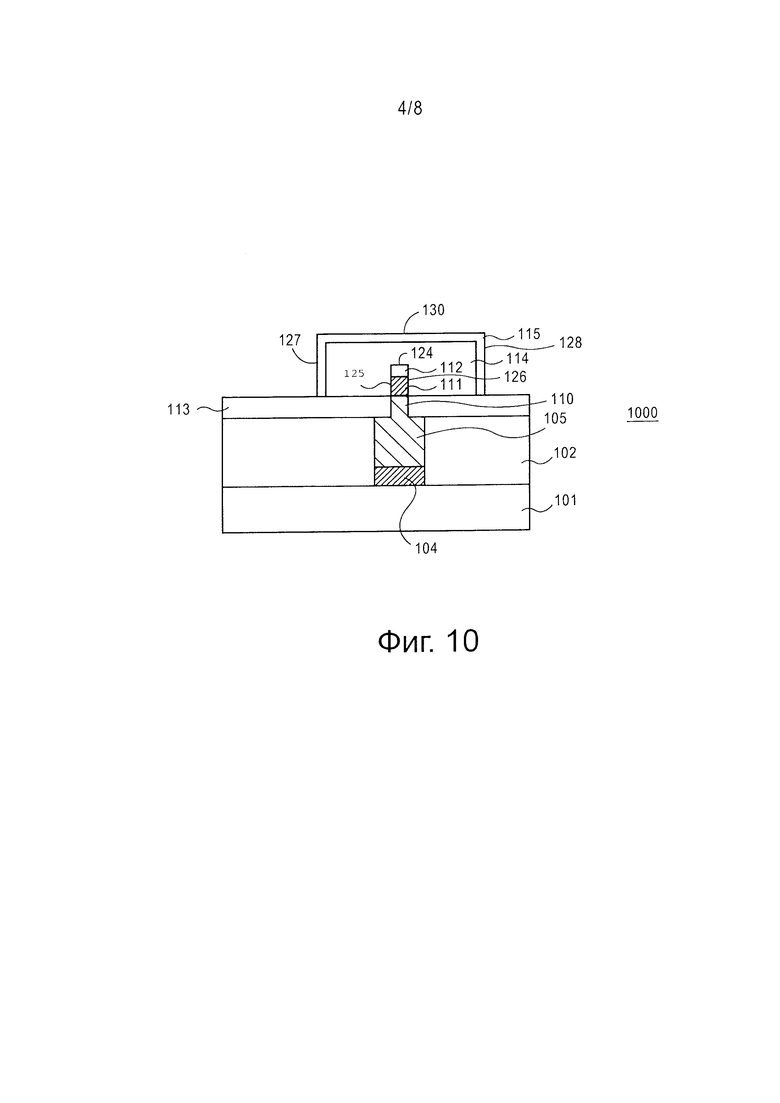

На фиг. 10 показан вид в поперечном сечении, аналогичный фиг. 9, после осаждения слоя диэлектрика затвора и слоя электрода затвора на ребро в соответствии с одним вариантом осуществления.

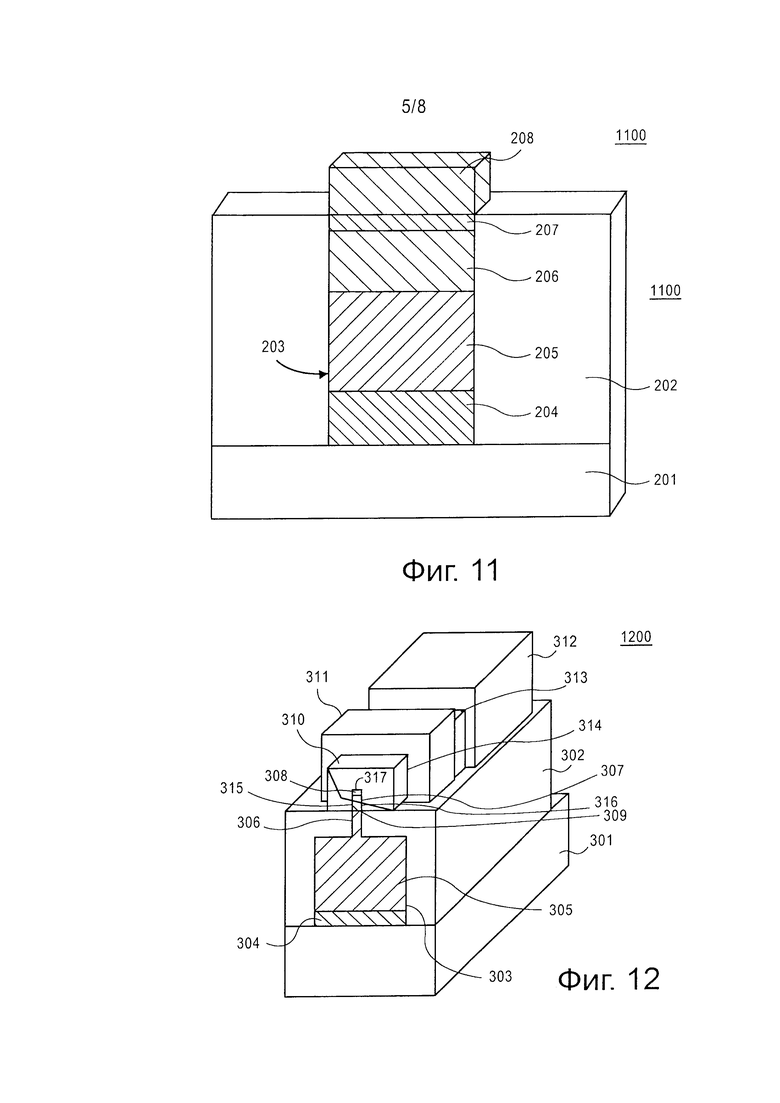

На фиг. 11 показан вид в перспективе многослойного стэка, как представлено на фиг. 6, в соответствии с одним вариантом осуществления.

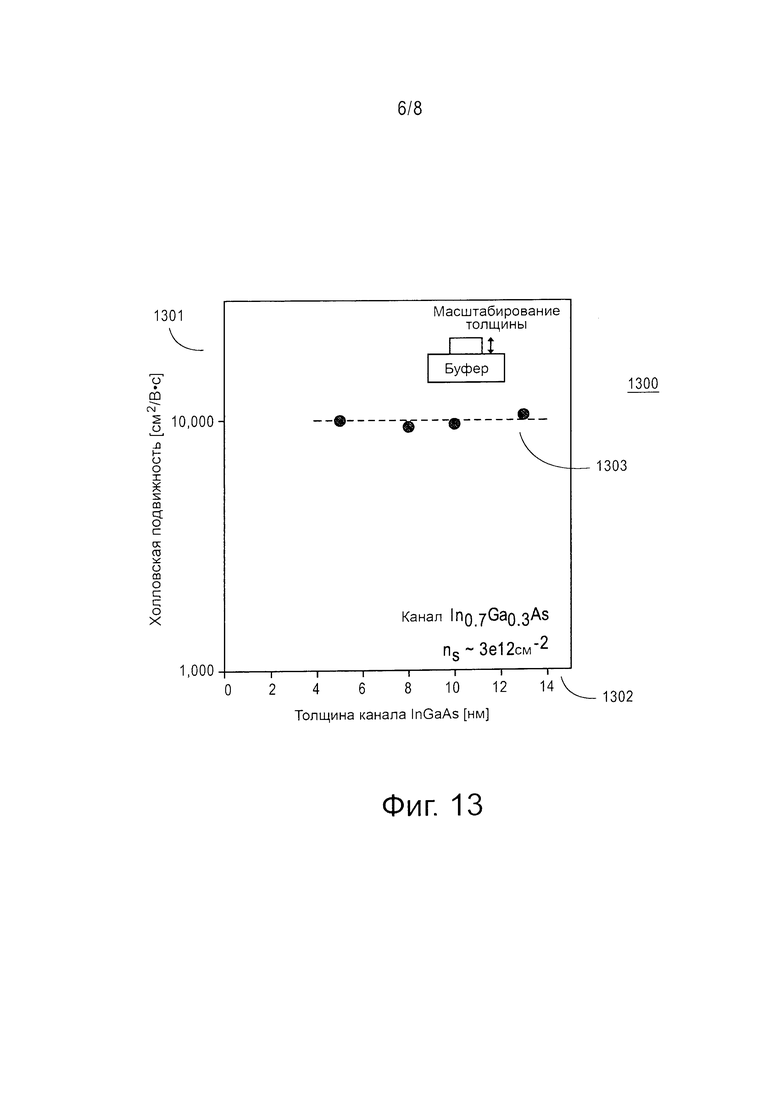

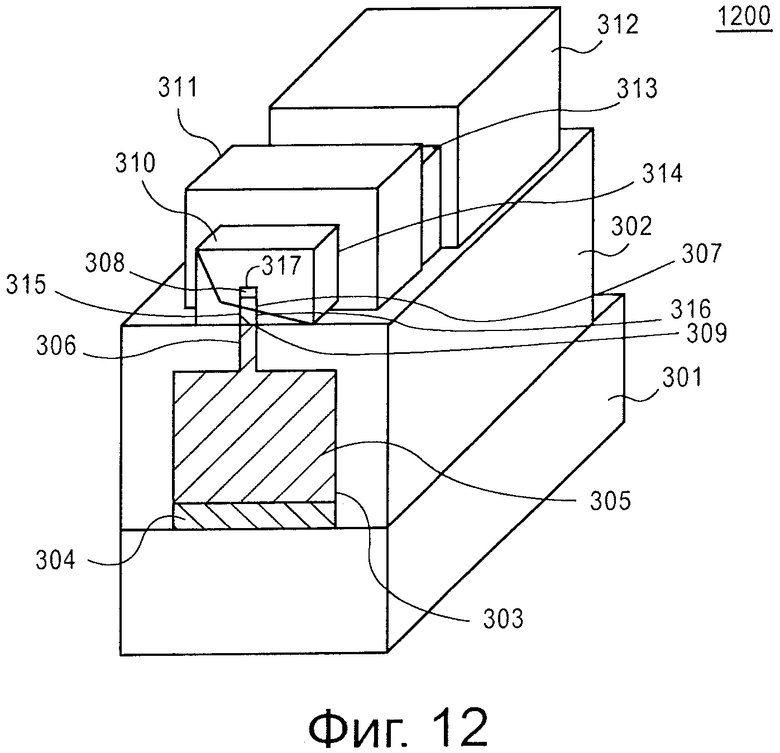

На фиг. 12 показан вид в перспективе участка транзистора с тремя затворами, как представлено на фиг. 10, в соответствии с одним вариантом осуществления.

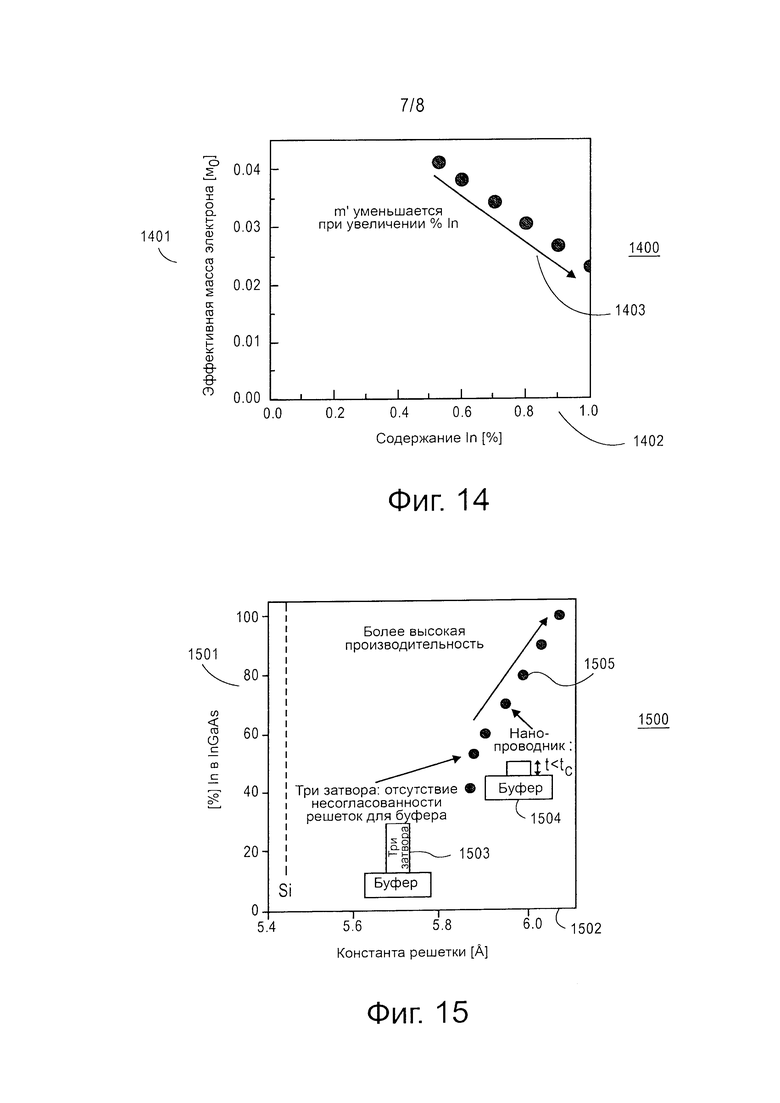

На фиг. 13 показан примерный график, представляющий холловскую подвижность, в зависимости от толщины канала InGaAs, в соответствии с одним вариантом осуществления.

На фиг. 14 показан примерный график, представляющий эффективную массу электрона (m0), в зависимости от содержания In (%), в соответствии с одним вариантом осуществления.

На фиг. 15 показан примерный график, представляющий содержание индия в InGaAs, в зависимости от константы кристаллической решетки, в соответствии с одним вариантом осуществления.

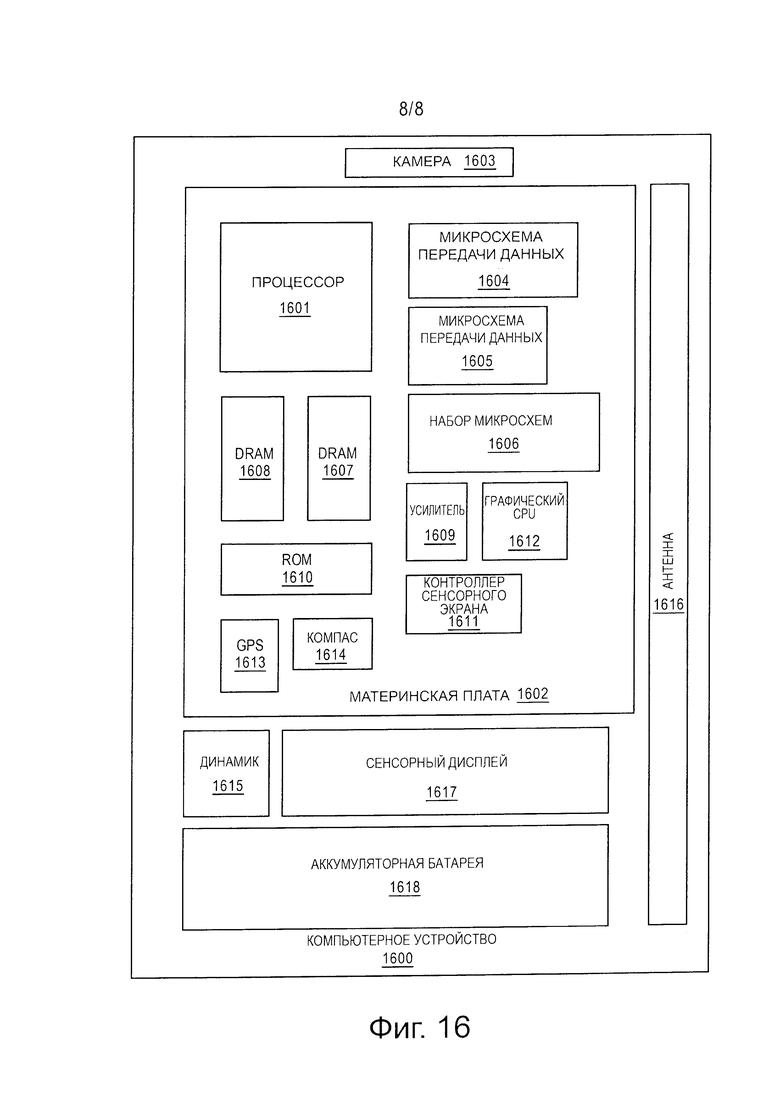

На фиг. 16 показано компьютерное устройство 1600 в соответствии с одним вариантом осуществления.

Подробное описание изобретения

В нижеследующем описании представлены различные конкретные детали, такие как конкретные материалы, размеры элементов и т.д., предназначенные для обеспечения полного понимания одного или нескольких описанных в настоящем документе вариантов осуществления. Тем не менее, специалисту в данной области техники будет понятно, что один или несколько описанных в настоящем документе вариантов осуществления могут быть осуществлены на практике и без этих конкретных деталей. В других случаях обработка при изготовлении полупроводников, технологий, материалов, оборудования и т.д., не описываются подробно, чтобы избежать чрезмерного усложнения данного описания.

Хотя определенные иллюстративные варианты осуществления описаны и представлены на приложенных чертежах, следует понимать, что такие варианты осуществления являются просто иллюстрацией, и не являются ограничительными, и что варианты осуществления не ограничены конкретными показанными и описанными конструкциями и компоновками, поскольку специалисты в данной области техники могут их модифицировать.

Ссылки в данном описании на "один вариант осуществления", "другой вариант осуществления" или "вариант осуществления" означают, что данное свойство, структура, или характеристика, описанная в связи с этим вариантом осуществления, включена в по меньшей мере один вариант осуществления. Таким образом, появление таких фраз, как "один вариант осуществления" и "вариант осуществления", в различных местах в описании не обязательно относится к одному и тому же варианту осуществления. Кроме того, эти конкретные свойства, структуры или характеристики могут быть скомбинированы любым подходящим образом в одном или нескольких вариантах осуществления.

Кроме того, изобретательные аспекты затрагивают не все свойства любого одного раскрытого варианта осуществления. Таким образом, формула изобретения, следующая после раздела «Подробное описание изобретения», тем самым, в явном виде включена в это подробное описание изобретения, и каждый пункт формулы изобретения можно рассматривать как самостоятельный отдельный вариант осуществления. Хотя в настоящем документе описаны иллюстративные варианты осуществления, специалисту в данной области техники будет понятно, что эти иллюстративные варианты осуществления могут на практике быть осуществлены с некоторыми модификациями и изменениями относительно того, что описано в данном документе. Описание, таким образом, следует рассматривать скорее как иллюстрацию, а не как ограничение изобретения.

В настоящем документе описываются способы и устройства для изготовления устройств на основе эпитаксиально выращенных материалов III-V групп. Первый буферный слой наносится в канавку в изолирующем слое на подложке. Второй буферный слой наносится на первый буферный слой. Слой устройства наносится на второй буферный слой. В одном варианте осуществления второй буферный слой имеет параметр кристаллической решетки, который соответствует параметру кристаллической решетки слоя канала устройства. В одном варианте осуществления первый буферный слой имеет параметр кристаллической решетки, лежащий между параметрами кристаллической решетки подложки и слоя канала устройства. В одном варианте осуществления по меньшей мере один из первого буферного слоя, второго буферного слоя и слоя устройства представляют собой слой на основе материалов III-V групп, и подложка представляет собой кремниевую подложку. В одном варианте осуществления верхний защитный слой наносится на слой устройства. В одном варианте осуществления ребро, содержащее слой устройства на втором буферном слое, формируется на участке первого буферного слоя. В одном варианте осуществления диэлектрик затвора наносится на ребро; и области истока и стока формируются на ребре. В одном варианте осуществления слой устройства включает в себя слой канала.

По меньшей мере в некоторых вариантах осуществления многослойный стэк содержит первый буферный слой на основе материалов III-V групп на кремниевой подложке. Второй буферный слой материалов III-V групп наносится на буферный слой на основе первого материалов III-V групп. Многослойный стэк, содержащий второй буферный слой на основе материала III-V групп, на первом буферном слое на основе материалов III-V групп, наносится в канавку в изолирующем слое на кремниевой подложке. Многослойный стэк, описанный в настоящем документе, позволяет обеспечить интеграцию материалов III-V групп на кремний, используя подход избирательной эпитаксии. Избирательное эпитаксиальное выращивание подразумевает выращивание многослойного стэка в канавке, в изолирующем слое на кремниевой подложке. Канавка в изолирующем слое на подложке имеет такое соотношение размеров (глубины к ширине (D/W), что дефекты, возникающие из-за несоответствия роста решетки, будут захвачены буферными слоями, нанесенными в канавке.

Буферные слои, избирательно выращенные между подложкой и слоем устройства, обеспечивают преимущество захвата дефектов дислокации в пределах нижних буферных слоев, уменьшая таким образом дефекты, распространяющиеся в слои устройства. Стэковая комбинация слоев, как описано в настоящем документе, обеспечивает преимущество возможности приспособления к большему несоответствию решеток между Si-подложкой и слоем устройства III-V групп. В одном варианте осуществления слой устройства III-V групп представляет собой InGaAs с высоким содержанием индия ("In") (например, по меньшей мере 53%).

Варианты осуществления стэка слоев, содержащего множество буферных слоев, как описано в настоящем документе, обеспечивают возможность приспособления к несоответствию решеток между подложкой Si и слоем канала устройства III-V групп. Гетеро-интегрированное решение, описанное в настоящем документе, может использоваться для изготовления устройства любой архитектуры, например устройства с тремя затворами, нанопроводников, нанополосок и т.п.

На фиг. 1 показан вид 100 в поперечном сечении структуры электронного устройства на основе материалов III-V групп в соответствии с одним вариантом осуществления. Канавка 103 сформирована на изолирующем слое 102 для того, чтобы обнажить подложку 101.

В одном варианте осуществления подложка 101 включает в себя полупроводниковый материал, например монокристаллический кремний ("Si"), германий ("Ge"), сплав кремния и германия ("SiGe"), материалы на основе материала III-V групп, например арсенид галлия ("GaAs"), или любую их комбинацию. В одном варианте осуществления подложка 101 включает в себя соединительные слои металлизации для интегральных схем. По меньшей мере, в некоторых вариантах осуществления подложка 101 включает в себя электронные устройства, например транзисторы, запоминающие устройства, конденсаторы, резисторы, оптоэлектронные устройства, переключатели и любые другие активные и пассивные электронные устройства, которые разделены электроизолирующим слоем, например межслойным диэлектриком, изолирующим слоем канавки или любым другим изолирующим слоем, известным специалистам в области техники изготовления электронных устройств. По меньшей мере, в некоторых вариантах осуществления подложка 101 включает в себя соединения, например переходные отверстия, выполненные с возможностью соединения слоев металлизации.

В одном варианте осуществления подложка 101 представляет собой подложку полупроводник на изоляторе (SOI), включающую в себя объемную нижнюю подложку, средний изолирующий слой и верхний монокристаллический слой. Верхний монокристаллический слой может содержать любой упомянутый выше материал, например кремний.

Изолирующий слой 102 может представлять собой любой материал, пригодный для изоляции соседних устройств и предотвращения утечек. В одном варианте осуществления электрически изолирующий слой 102 представляет собой оксидный слой, например двуокись кремния или любой другой электроизолирующий слой, определенный конструкцией электронного устройства. В одном варианте осуществления изолирующий слой 102 содержит межслойный диэлектрик (ILD), например двуокись кремния. В одном варианте осуществления изолирующий слой 102 может включать в себя полиимид, эпоксидную смолу, определяемые под действием света материалы, такие как бензоциклобутен (ВСВ), и материалы серии WPR, или спин-он стекло. В одном варианте осуществления изолирующий слой 102 представляет собой слой с низкой проницаемой способностью (с низким значением k) ILD. Как правило, низкое значение k относится к диэлектрикам, имеющим диэлектрическую постоянную (проницаемость k), меньшую, чем проницаемость двуокиси кремния.

В одном варианте осуществления изолирующий слой 102 представляет собой слой изоляции с узкощелевой изоляцией (STI) для обеспечения областей изоляции поля, которые изолируют одно ребро от других ребер на подложке 101. В одном варианте осуществления толщина слоя 102 приблизительно находится в диапазоне от 500 ангстрем (Å) до 10,000 Å. Изолирующий слой 102 может представлять собой защитное покрытие, нанесенное с использованием любой из технологий, известных специалистам в области техники изготовления электронных устройств, такую как, но без ограничения, химическое осаждение из паровой фазы (CVD) и физическое осаждение из паровой фазы (PVP).

В одном варианте осуществления изолирующий слой 102 выполнен структурированным и его подвергают травлению для формирования канавок, таких как канавка 103, используя одну из технологий структурирования и травления, известных специалисту в области изготовления электронных устройств. Канавка 103 имеет глубину D 121 и ширину W 122. Отношение размеров канавки 103 (D/W) определяет толщину буферных слоев, нанесенных через канавку. Чем выше отношение D/W канавки, тем более толстыми получаются буферные слои. В одном варианте осуществления буферные слои, нанесенные через канавку на подложку, являются достаточно толстыми, так что большая часть дефектов, возникающих из-за несоответствия решеток, захватываются в буферных слоях, и предотвращается их распространение в слой устройства, сформированный поверх буферных слоев. В одном варианте осуществления соотношение размеров канавки (D/W) составляет по меньшей мере 1,5 и более конкретно по меньшей мере 3. В одном варианте осуществления ширина канавки определяется шириной электронного устройства. Электронное устройство может, например, представлять собой устройство с тремя затворами, устройство на основе нанопроводников, устройство на основе нанополосок или любое другое электронное устройство. Например, ширина канавки 103 для транзистора с тремя затворами может составлять от приблизительно 5 нм до приблизительно 80 нм. Например, ширина канавки 103 для устройства на основе нанотрубки или устройства на основе нанопроводника может составлять от приблизительно 5 нм до приблизительно 80 нм. В одном варианте осуществления глубина канавки по меньшей мере в три раза больше, чем ширина канавки. Например, для транзистора с тремя затворами глубина канавки 103 может составлять от приблизительно 250 нанометров ("нм") до приблизительно 400 нм и более конкретно от приблизительно 300 нм до приблизительно 350 нм.

Канавка 103 в изолирующем слое 102 может иметь квадратную, прямоугольную, круглую, овальную или любую другую форму, которая открывает лежащую под ней подложку 101. По меньшей мере, в некоторых вариантах осуществления ширина канавки составляет от приблизительно 20 нм до приблизительно 300 нм. По меньшей мере в некоторых вариантах осуществления глубина канавки составляет от приблизительно 60 нм до приблизительно 600 нм.

На фиг. 2 показан вид 200 в поперечном сечении, аналогичный фиг. 1, после нанесения первого буферного слоя на подложку в соответствии с одним вариантом осуществления. Первый буферный слой 104 избирательно наносят через канавку 103 на открытый участок подложки 101. В одном варианте осуществления буферный слой 104 имеет параметр кристаллической решетки, лежащий в диапазоне между параметрами кристаллической решетки подложки 101 и слоя устройства, сформированного на нем. Обычно, константа кристаллической решетки представляет собой параметр решетки, который обычно определяется расстоянием между элементарными ячейками в кристаллической решетке. Параметр кристаллической решетки представляет собой меру структурной совместимости между разными материалами.

Материал для буферного слоя 104 выбирают таким образом, чтобы константа кристаллической решетки первого буферного слоя 104 ("LC1") находилась в диапазоне между константами решетки Si ("LCsi") и слоя канала устройства ("LCdc"). В одном варианте осуществления подложка 101 представляет собой кремниевую подложку, и буферный слой 104 содержит материал III-V групп. Как правило, материал III-V групп относится к компаундному полупроводниковому материалу, который содержит по меньшей мере один из элементов группы III Периодической таблицы, такой как алюминий ("Al"), галлий ("Ga"), индий ("В"), и по меньшей мере один из элементов V группы Периодической таблицы, такой как азот ("N"), фосфор ("Р"), мышьяк ("As"), сурьма ("Sb"). В одном варианте осуществления буферный слой 104 представляет собой InP, GaAs, InAlAs, другой материал III-V групп или любую их комбинацию. В одном варианте осуществления константа кристаллической решетки первого буферного слоя 104 является такой, что отношение R=(LCI-LCSi)/LCSi составляет от приблизительно 4% до приблизительно 8%.

В одном варианте осуществления толщина первого буферного слоя 104 составляет по меньшей мере приблизительно 50 нанометров ("нм") и, более конкретно по меньшей мере приблизительно 70 нм.

В одном варианте осуществления буферный слой 104 наносится через канавку 103 на открытый участок подложки 101 с использованием эпитаксии в выбранной области. Как показано на фиг. 2, эпитаксиальный буферный слой 104 локально выращивают на открытом участке полупроводниковой подложки 101 через канавку 103. Эпитаксиальный буферный слой 104 может быть избирательно нанесен через канавку 103 на открытый участок подложки 101 с использованием одной из эпитаксиальных технологий, известных специалистам в области техники изготовления электронного устройства, например с использованием химического осаждения из паровой фазы ("CVD"), металлоорганического химического осаждения из паровой фазы ("MOCVD"), осаждения атомарного слоя ("ALD") или другой технологии эпитаксиального выращивания, известной в области изготовления электронных устройств. В одном варианте осуществления первый эпитаксиальный буферный слой из InP наносят через канавку 103 на открытый участок подложки 101, используя технологию MOCVD, при температуре от приблизительно 400°C до приблизительно 650°C и более конкретно приблизительно 500°C.

На фиг. 3 показан вид 300 в поперечном сечении, аналогичный фиг. 2, после нанесения второго буферного слоя на первый буферный слой, в соответствии с одним вариантом осуществления. Второй буферный слой 105 избирательно наносят через канавку 103 на буферный слой 104. В одном варианте осуществления второй буферный слой 105 содержит материал III-V групп. В одном варианте осуществления второй буферный слой 105 представляет собой сплав арсенид индия и алюминия ("InxAl1-xAs"), антимонид и арсенид индия и галлия ("InxGa1-xAsSb"), другой материал III-V групп или любую их комбинацию. В одном варианте осуществления второй буферный слой 105, основанный на одном из материала III-V групп, нанесен на первый буферный слой 104 другого материала III-V групп. В одном варианте осуществления буферный слой 105 на основе второго материала III-V групп имеет параметр решетки, который соответствует параметру решетки слоя канала устройства на основе материала III-V групп. В одном варианте осуществления буферный слой 105 на основе второго материала III-V групп имеет параметр решетки, который соответствует параметру решетки слоя устройства из материала III-V групп, который имеет высокое содержание индия (по меньшей мере 53% мас.), например слоя InxAl1-xAs, слоя InxGa1-xAsSb, где х составляет по меньшей мере 0,53. В более конкретном варианте осуществления второй буферный слой 105 имеет параметр решетки, который соответствует параметру решетки слоя устройства из материала III-V групп, который имеет по меньшей мере 70% атомарную долю индия, например ("InxAl1-xAs", InxGa1-xAsSb"), где х равен по меньшей мере 0,7.

В одном варианте осуществления слой канала устройства представляет собой арсенид индия и галлия ("InGaAs"), и буферный слой 105 представляет собой InAlAs, InGaAsSb или любую их комбинацию. В одном варианте осуществления выбор второго буферного материала, который имеет нижнюю границу перехода с первым буферным слоем и верхнюю границу перехода со слоем канала устройства, выполняют так, чтобы константа решетки второго буферного слоя соответствовала константе решетки слоя канала InGaAs. В одном варианте осуществления толщина второго буферного слоя 105 составляет по меньшей мере приблизительно 200 нм.

В одном варианте осуществления буферный слой 105 наносят через канавку 103 на буферный слой 104, используя эпитаксию в отобранной области. Как показано на фиг. 2, эпитаксиальный буферный слой 105 локально выращивают на первом буферном слое 104 через канавку 103. Эпитаксиальный буферный слой 105 может быть избирательно нанесен через канавку 103 на первый буферный слой 104, используя одну из эпитаксиальных технологий, известных специалисту в области изготовления электронных устройств, например химическое осаждение из паровой фазы ("CVD"), металлоорганическое химическое осаждение из паровой фазы ("MOCVD"), нанесение атомарного слоя ("ALD"), или другую технологию эпитаксиального выращивания, известную специалисту в области изготовления электронных устройств. В одном варианте осуществления второй эпитаксиальный буферный слой InAlAs наносят через канавку 103 на первый буферный слой 104, используя технологию MOCVD при температуре от приблизительно 425°C до приблизительно 650°C, и более конкретно, от приблизительно 450°C до приблизительно 650°C.

На фиг. 4 показан вид 400 в поперечном сечении, аналогичный фиг. 3, после нанесения слоя устройства на второй буферный слой, в соответствии с одним вариантом осуществления. Слой 106 устройства избирательно наносят через канавку 103 на второй буферный слой 105. В одном варианте осуществления слой 106 устройства содержит слой канала устройства. Второй буферный слой 105 имеет параметр решетки, который соответствует параметру решетки слоя 106 устройства. В одном варианте осуществления слой 106 устройства содержит материал III-V групп, например InGaAs, InGaAsSb, который имеет высокое содержание индия (например, по меньшей мере 53% мас. (например, InxGa1-xAs, InxGa1-xAsSb, где х составляет по меньшей мере 0,53). В одном варианте осуществления слой 105 устройства содержит InGaAs, InGaAsSb, который содержит по меньшей мере 70% индия (например, InxGa1-xAs, InxGa1-xAsSb, где х составляет по меньшей мере 0,7).

В одном варианте осуществления слой 106 канала устройства представляет собой InGaAs, и второй буферный слой 105 представляет собой InAlAs, InGaAsSb или любую их комбинацию. В одном варианте осуществления константа решетки материала III-V групп второго буферного слоя соответствует константе решетки материала III-V групп слоя 106 устройства, как описано выше. Толщина слоя 106 устройства определяется конструкцией устройства. В одном варианте осуществления толщина слоя 106 устройства составляет от приблизительно 5 нм до приблизительно 100 нм.

В одном варианте осуществления слой 106 устройства наносят через канавку 103 на буферный слой 105, используя эпитаксию в отобранной области. Как показано на фиг. 4, слой 106 устройства локально выращивают на буферном слое 105 через канавку 103. Слой 106 эпитаксиального устройства может быть нанесен через канавку 103 на буферный слой 105 с использованием одной из эпитаксиальных технологий, известных специалистам в области изготовления электронных устройств, например химического осаждения из паровой фазы ("CVD"), металлоорганического химического осаждения из паровой фазы ("MOCVD"), осаждения атомарного слоя ("ALD") или другой технологии эпитаксиального выращивания, известной специалистам в области изготовления электронных устройств. В одном варианте осуществления слой устройства InGaAs наносят через канавку 103 на буферный слой 105, используя технологию MOCVD, при температуре от приблизительно 400°C до приблизительно 650°C.

На фиг. 5 показан вид 500 в поперечном сечении, аналогичный фиг. 5, после необязательного выращивания тонкого верхнего защитного слоя на слое устройства, в соответствии с одним вариантом выполнения. При необходимости на слой 106 устройства может быть нанесен тонкий верхний защитный слой в качестве переходной области (интерфейса) к диэлектрику затвора с высоким значением k, например TaSiOx, для улучшения управления затвором. Тонкий верхний защитный слой 107 может быть избирательно нанесен через канавку 103 на слой 106 устройства. В одном варианте осуществления тонкий верхний защитный слой 107 содержит материал III-V групп. В одном варианте осуществления верхний защитный слой 107 представляет собой InP. В одном варианте осуществления толщина верхнего защитного слоя 107 составляет от приблизительно 0,5 нм до приблизительно 3 нм.

В одном варианте осуществления верхний защитный слой 107 наносят через канавку 103 на слой 106 устройства, используя эпитаксию в выбранной области. Как показано на фиг. 5, верхний защитный слой 107 локально выращивают на слое 107 устройства через канавку 103. Верхний защитный слой 107 может быть избирательно нанесен через канавку 103 на слой 106 устройства с использованием эпитаксиальной технологии, известной специалистам в области изготовления электронных устройств, например химического осаждения из паровой фазы ("CVD"), металлоорганического химического осаждения из паровой фазы ("MOCVD"), осаждения атомарного слоя ("ALD") или другой технологии эпитаксиального выращивания, известной специалисту в области изготовления электронных устройств.

На фиг. 6 показан вид 600 в поперечном сечении, аналогичный представленному на фиг. 5, после нанесения сильнолегированного слоя поверх слоя устройства, в соответствии с одним вариантом осуществления. В одном варианте осуществления сильнолегированный слой 108 наносят поверх слоя устройства для получения истока и стока для устройства транзистора. Как показано на фиг. 6, многослойный стэк избирательно выращивают в канавке 103 на подложке 101, которая содержит сильнолегированный слой 108 на верхнем защитном слое 107, на слое 106 устройства, на втором буферном слое 105, на первом буферном слое 104, на подложке 101. В одном варианте осуществления сильно легированный слой 108 истока/стока затем удаляют из области затвора при обработке и оставляют в областях истока/стока во время приготовления транзистора.

В одном варианте осуществления сильнолегированный слой 108 истока/стока содержит материал III-V групп. В одном варианте осуществления сильнолегированный слой 108 имеет концентрацию легирующих добавок от 1×1019 до 1×1021 атомов/см3 и содержит материал III-V групп, который аналогичен материалу III-V групп слоя 107 устройства. В одном варианте осуществления толщина слоя 108 истока/стока определяется конструкцией устройства. В одном варианте осуществления толщина слоя 108 истока/стока составляет приблизительно от 10 нм до приблизительно 100 нм. В более конкретном варианте осуществления толщина слоя 108 истока/стока составляет приблизительно 20 нм. В одном варианте осуществления слой 108 истока/стока наносят через канавку 103 на верхний защитный слой 107, используя эпитаксию в выбранной области, слой 108 истока/стока может быть избирательно нанесен через канавку 103 на верхний защитный слой 107 с использованием одной из эпитаксиальных технологий, известных специалистам в области изготовления электронных устройств, например химического осаждения из паровой фазы ("CVD"), металлоорганического химического осаждения из паровой фазы ("MOCVD"), осаждения атомарного слоя ("ALD") или другой технологии эпитаксиального выращивания, известной специалисту в области изготовления электронных устройств.

На фиг. 11 показан вид 1100 в перспективе многослойного стэка, как представлено на фиг. 6, в соответствии с одним вариантом осуществления. Многослойный стэк для изготовления электронных устройств содержит первый буферный слой 204 в канавке, сформированный в изолирующем слое 202 на подложке 201. Второй буферный слой 205 нанесен на первый буферный слой 204 и слой 206 канала устройства - на второй буферный слой. Второй буферный слой 205 имеет параметр решетки, который соответствует параметру решетки слоя 206 канала устройства. Первый буферный слой 204 имеет параметр решетки в диапазоне между параметрами решетки подложки 201 и слоя 206 канала устройства, как описано выше.

В одном варианте осуществления каждый из первого буферного слоя 204, второго буферного слоя 205 и слоя 206 канала устройства представляет собой слой на основе материала III-V групп, и подложка 201 представляет собой кремниевую подложку, как описано выше. Верхний защитный слой 207, в случае необходимости, наносят на слой 206 канала устройства, как описано выше. В одном варианте осуществления каждый из первого буферного слоя 204, второго буферного слоя 205, слоя 206 канала устройства и верхнего защитного слоя 207 наносят, используя химическое осаждение из паровой фазы, как описано выше.

Как правило, когда встраивают несогласованные по решетке пленки, формируются дефекты. Эти дефекты после формирования распространяются вверх по решетке под определенным углом. Многослойный стэк для изготовления электронных устройств, содержащий первый буферный слой 204 в канавке 203, в изолирующем слое 202 на подложке 201, второй буферный слой 205 на первом буферном слое 204; и слой 206 канала устройства на втором буферном слое 205, в котором второй буферный слой 205 имеет параметр решетки, который соответствует параметру решетки слоя 206 канала устройства, и в котором первый буферный слой 204 имеет параметр решетки в диапазоне между параметрами решеток подложки 201 и слоя 206 канала устройства, позволяет разместить границу перехода окончания дефекта далеко под слоем 206 канала фактического устройства, так что дефект не влияет на характеристики устройства.

На фиг. 7 показан вид 700 в поперечном сечении, аналогичный фиг. 6, после удаления сильнолегированного слоя истока/стока из области 123 затвора устройства, в соответствии с одним вариантом осуществления. Сильнолегированный слой 108 истока/стока оставляют ненарушенным в областях истока/стока (не показаны) слоя 106 устройства.

На фиг. 8 показан вид 800 в поперечном сечении, аналогичный фиг. 7, после того, как было сформировано ребро устройства, в соответствии с одним вариантом осуществления. Как показано на фиг. 8, ребро 109 устройства содержит участок необязательного верхнего защитного слоя 112 на участке слоя 111 устройства, на участке второго буферного слоя 110. Как показано на фиг. 8, ребро 108 имеет верхнюю поверхность 124 и противоположные боковые стенки 125 и 126. В одном варианте осуществления формирование ребра 109 подразумевает нанесение структурированной твердой маски на верхний защитный слой 107 с последующим формированием выемки в изолирующем слое 102 вплоть до глубины, определенной конструкцией устройства, как известно специалисту в области изготовления электронных устройств. В одном варианте осуществления в изолирующем слое 102 формируют выемку, используя технологию избирательного вытравливания, оставляя ребро 109 без нарушений. Например, выемка в изолирующем слое 102 может быть сформирована с использованием технологии избирательного вытравливания, известной специалистам в области изготовления электронных устройств, но при этом она не ограничена влажным вытравливанием и сухим вытравливанием химическим составом, имеющим, по существу, высокую избирательную способность в отношении ребра на подложке 101. Это означает, что химический состав, в основном, вытравливает изолирующий слой 102, а не ребро на подложке 101. В одном варианте осуществления отношение скоростей вытравливания изолирующего слоя 102 к ребру составляет по меньшей мере 10:1.

Как показано на фиг. 8, структурированную твердую маску удаляют с ребра 109. Слой структурированной твердой маски может быть удален с верхней части ребра 109 с использованием обработки полировкой, такой как СМР, как известно специалисту в области изготовления электронных устройств. Как показано на фиг. 8, на изолирующем слое 102 формируют выемку вплоть до определенной глубины, которая определяет высоту ребра 109 устройства относительно верхней поверхности изолирующего слоя 102. Высота и ширина ребра 109 обычно определены проектом. В одном варианте осуществления высота ребра составляет от приблизительно 10 нм до приблизительно 100 нм, и ширина ребра 109 составляет от приблизительно 5 нм до приблизительно 20 нм.

На фиг. 9 показан вид 900 в поперечном сечении, аналогичный фиг. 8, после нанесения изолирующего слоя 113 на изолирующий слой 102 рядом с боковыми стенками части первого буферного слоя 110, в соответствии с одним вариантом осуществления. В одном варианте осуществления изолирующий слой 113 может представлять собой любой материал, пригодный для изоляции соседних устройств и предотвращения утечек из ребер. В одном варианте осуществления электрически изолирующий слой 113 представляет собой оксидный слой, например двуокись кремния или любой другой электроизолирующий слой, как задано проектом. В одном варианте осуществления изолирующий слой 113 представляет собой слой STI для обеспечения полевой изоляции областей, которые изолируют одно ребро от других ребер на подложке 101. В одном варианте осуществления толщина изолирующего слоя 113 соответствует толщине участка второго буферного слоя 110, который определяется конструкцией устройства на ребре. В одном варианте осуществления толщина изолирующего слоя 113 находится приблизительном в диапазоне от 1 нм до приблизительно 30 нм. Изолирующий слой 113 может представлять собой защитное покрытие, нанесенное с использованием любой из технологий, известных специалисту в области техники изготовления электронных устройств, такой как, но без ограничений, химическое осаждение из паровой фазы (CVD), и физическое осаждение из паровой фазы (PVP).

На фиг. 10 показан вид 1000 в поперечном сечении, аналогичный фиг. 9, после нанесения диэлектрического слоя затвора и слоя электрода затвора на ребро, в соответствии с одним вариантом осуществления. Диэлектрический слой 114 затвора сформирован на и вокруг трех сторон полупроводникового ребра 109. Как показано на фиг. 10, диэлектрический слой 114 затвора формируется на или рядом с верхней поверхностью 124 и на или рядом с боковой стенкой 125, и на или рядом с боковой стенкой 126 ребра 109. Диэлектрический слой 114 затвора может представлять собой любой хорошо известный диэлектрический слой затвора.

В одном варианте осуществления диэлектрический слой 103 затвора представляет собой диэлектрический материал с высоким значением к, имеющий диэлектрическую постоянную, большую, чем диэлектрическая постоянная двуокиси кремния. В одном варианте осуществления электрически изолирующий слой 103 содержит диэлектрический материал с высоким значением k, такой как металлооксидный диэлектрик. Например, диэлектрический слой 103 затвора может представлять собой, но не ограничен этим, окись кремния и тантала (TaSiOx); пентаокись (Ta2O5), и окись титана (TiO2), окись циркония (ZrO2), окись гафния (HfO2), окись лантана (La2O4), титанат циркония и свинца (PZT), другой диэлектрический материал с высоким значением к или их комбинации. В одном варианте осуществления диэлектрик 114 затвора представляет собой диэлектрический слой из двуокиси кремния (SiO2), оксинитрида кремния (SiOxNy) или нитрида кремния (Si3N4). В одном варианте осуществления толщина диэлектрического слоя 103 затвора находится в диапазоне от приблизительно 1 нм до приблизительно 20 нм и более конкретно от приблизительно 5 нм до приблизительно 10 нм.

Как показано на фиг. 10, слой 115 электрода затвора нанесен на диэлектрик 114 затвора на ребре 109. Электрод 115 затвора сформирован на и вокруг диэлектрического затвора 114 слоя, как показано на фиг. 10. Электрод 115 затвора сформирован на или рядом с диэлектриком 114 затвора на боковой стенке 125 полупроводникового ребра 109, сформирован на диэлектрике 114 затвора на верхней поверхности 124 полупроводникового ребра 109 и сформирован рядом с или на диэлектрическом слое 114 затвора, на боковой стенке 125 полупроводникового ребра 109.

Как показано на фиг. 10, электрод 115 затвора имеет верхнюю часть 130 и пару поперечно противоположных боковых стенок, таких как боковая стенка 127 и боковая стенка 128, разделенные расстоянием, которое задает длину канала устройства на ребре. Электрод 115 затвора может быть сформирован из любого подходящего материала электрода затвора. В одном варианте осуществления электрод 115 затвора представляет собой электрод затвора из металла, такой как, но без ограничений, вольфрам, тантал, титан и их нитриды. Следует понимать, что электрод 115 затвора не обязательно должен представлять собой единый материал и может представлять собой композитный стэк тонких пленок, таких как (без ограничения) электрод из поликристаллического кремния/металлический электрод или электрод из металла/поликристаллического кремния. В одном варианте осуществления электрод 115 затвора содержит поликристаллический кремний, легированный до плотности концентрации от 1×1019 атомов/см3 до 1×1020 атомов/см3.

На фиг. 12 показан вид 1200 в перспективе части транзистора с тремя затворами, как представлено на фиг. 10, в соответствии с одним вариантом осуществления. Как показано на фиг. 12, транзистор с тремя затворами включает в себя электроизолирующий слой 302 на подложке 301 рядом с ребром 309. В одном варианте осуществления транзистор с тремя затворами соединен с одним или более слоями металлизации (не показаны). Один или больше слоев металлизации могут быть отделены от соседних слоев металлизации диэлектрическим материалом, например межслойным диэлектриком (ILD) (не показан). Соседние слои металлизации могут быть электрически соединены через переходные отверстия (не показаны).

Как показано на фиг. 12, ребро 309 выступает из верхней поверхности изолирующего слоя 302. Ребро 309 содержит необязательный слой 308 верхнего защитного слоя на основе материала III-V групп, на слое 307 канала на основе материала III-V групп на участке 306 второго буферного слоя 305 на основе материала III-V групп, на первом буферном слое 304 на основе материала III-V групп. Электрод 311 затвора сформирован на и вокруг диэлектрика 310 затвора.

Ребро 309, содержащее необязательный слой 308 верхнего защитного слоя на основе материала III-V групп, на слое 307 канала устройства на основе материала III-V групп, на участке 306 второго буферного слоя 305 на основе материала III-V групп, на первом буферном слое 304 на основе материала III-V групп, в котором второй буферный слой имеет параметр решетки, который соответствует параметру решетки слоя канала устройства, и в котором первый буферный слой имеет параметр решетки в диапазоне между параметрами решеток подложки и слоя устройства, обеспечивает возможность приспособления к несоответствию решеток подложки 301 и слоя 307 канала устройства, так что дефекты могут быть захвачены между толщиной буферных слоев 304 и 305.

Как показано на фиг. 12, ребро 309 имеет пару противоположных боковых стенок, разделенных расстоянием, которое задает ширину полупроводникового ребра. В одном варианте осуществления ширина ребра приблизительно составляет в диапазоне от приблизительно 5 нм до приблизительно 50 нм. В одном варианте осуществления длина ребер больше, чем ширина и определена конструкцией. В одном варианте осуществления длина ребер составляет от приблизительно 50 нм до сотен микрон. В одном варианте осуществления высота ребра над верхней поверхностью изолирующего слоя 302 находится приблизительно в диапазоне от приблизительно 5 нм до приблизительно 500 нм.

Как показано на фиг. 12, электрод 311 затвора нанесен на диэлектрик 310 затвора на ребре 309. Электрод 311 затвора сформирован на и вокруг диэлектрика 310 затвора. Область истока и область стока сформированы на противоположных сторонах электрода 311 затвора, на участке 313 слоя устройства ребра 313. Один из электрода 312 истока/стока сформирован на области истока/стока, на одной стороне электрода 311 затвора, и другой один из электрода истока/стока (не показан) сформирован на области истока/стока на противоположной стороне электрода 311 затвора с использованием одной из технологий, известных специалисту области изготовления электронных устройств.

Области истока и стока сформированы из одного и того же типа удельной проводимости, такой как проводимость N-типа или Р-типа. В одном варианте осуществления области истока и стока имеют концентрацию легирования от 1×1019 до 1×1021 атомов/см3. Области истока и стока могут быть сформированы с однородной концентрацией или могут включать в себя подобласти с разными концентрациями или профилями легирования, такими как области кончика (например, расширения истока/стока). В одном варианте осуществления области истока и стока имеют одинаковую концентрацию легирования и профиль. В одном варианте осуществления концентрация и профиль легирования областей истока и стока, таких как область 104 истока и область 106 стока, могут изменяться для получения определенной электрической характеристики. Участок ребра 309, расположенный между областью истока и областями стока, образует область 314 канала транзистора.

Область 314 канала также может быть определена как область полупроводникового ребра 309, окруженного электродом 311 затвора. Однако иногда область истока/стока может продолжаться несколько за пределы электрода затвора, например из-за диффузии, для определения несколько меньшей области канала, чем длина электрода затвора (Lg). В одном варианте осуществления область 314 канала является областью с собственной электропроводностью или нелегированной областью. В одном варианте осуществления область 314 канала является легированной, например, до уровня электропроводности от 1×1016 до 1×1019 атомов/см3. В одном варианте осуществления, когда область в канале является легированной, она обычно легирована до противоположного типа удельной проводимости области истока/стока. Например, когда области истока и стока имеют проводимость n-типа, область канала может быть легирована до проводимости р-типа. Аналогично, когда области истока и стока имеют проводимость р-типа, область канала могла бы иметь проводимость n-типа. Таким образом, транзистор 100 с тремя затворами может быть сформирован с получением либо транзистора NMOS, или транзистора PMOS соответственно.

Области канала, такие как область 314 канала, могут быть равномерно легированы или могут быть легированы неравномерно или с разными концентрациями для получения определенных электрических и рабочих характеристик. Например, области канала, такие как область 314 канала, могут включать в себя хорошо известные области ореола, если это требуется. Как показано на фиг. 12, транзистор с тремя затворами имеет диэлектрик 310 и электрод 311 затвора, окружающий полупроводниковое ребро 309 с трех сторон, что обеспечивает три канала на ребре 309, один канал продолжается между областями истока и стока на одной боковой стенке ребра, такой как боковая стенка 315, второй канал продолжается между областями истока и стока на верхней поверхности ребра, такой как поверхность 317, и третий канал продолжается между областями истока и стока на другой боковой стенке ребра, такой как боковая стенка 316.

В одном варианте осуществления, области истока транзистора 1200 электрически соединены с более высокими уровнями металлизации (например, металл 1, металл 2, металл 3 и так далее) для взаимного электрического соединения различных транзисторов массива в функциональные схемы. В одном варианте осуществления области стока транзистора 1200 соединены с более высоким слоем металлизации (например, металл 1, металл 2, металл 3 и так далее) для взаимного электрического соединения различных транзисторов массива вместе в функциональные схемы.

На фиг. 13 показан примерный график 1300 холловской подвижности носителей (например, электронов, дырок) 1301 в зависимости от толщины 1302 канала InGaAs, в соответствии с одним вариантом осуществления. Материал InGaAs с высоким содержанием (например, по меньшей мере 70%) индия, такой как In0,7Ga0,3As, имеет высокую подвижность носителей, что делает его привлекательным вариантом выбора материала канала для устройства на основе III-V групп. При использовании InGaAs с высоким содержанием (например, по меньшей мере 70%) индия, такого как In0,7Ga0,3As, в качестве слоя канала устройства, повышается рабочая характеристика устройства и увеличивается коэффициент усиления устройства. Данные 1303 показывают, что холловская подвижность поддерживается на высоком уровне приблизительно 10000 см2/(В⋅с) вплоть до тонкого корпуса устройства 5 нм. При этом отсутствует влияние неровностей поверхности на подвижность носителей.

На фиг. 14 показан примерный график 1400, представляющий эффективную массу (m0) электрона 1401 в зависимости от содержания In (%) 1402, в соответствии с одним вариантом осуществления. Данные 1403 означают, что m0 уменьшается при более высоком содержании индия (%). Как показано на фиг. 12, для увеличения высоты ребра ("Hsi") ребра в устройстве с тремя затворами, изготовленном с использованием InGaAs, имеющего высокое содержание (например, 70%) индия (например, In0,7Ga0,3As), несоответствие решеток между каналом (например, слоя 307) и нижним буфером, расположенным рядом с каналом (например, буферным слоем 305), необходимо минимизировать. Если несоответствие решеток будет большим, для предотвращения образования новых дефектов толщина In0,7Ga0,3As (и, следовательно, Hsi) должна быть ограничена критической толщиной слоя. В результате, нижний буферный слой, расположенный рядом со слоем канала устройства In0,7Ga0,3As, должен иметь константу решетки, по существу, такую же (или близкую), как у канала In0,7Ga0,3As. Аналогичным образом, константы решеток слоя канала устройства, такого как слой 307 канала устройства, и расположенной под ним части буферного слоя, такой как часть 306 второго буферного слоя 305, позволяют (1) сделать неограниченным тройной затвор HSi, 2) предотвратить образование каких-либо новых дефектов в канале/рядом с нижним буфером и (3) захватить все дефекты, которые образуются в интерфейсе между вторым буферным слоем и первым буферным слоем, как, например, между буферным слоем 305 и буферным слоем 303, и все дефекты, которые формируются на границе перехода между первым буферным слоем и подложкой Si, как, например, между буферным слоем 303 и подложкой 301 в канавке, такой как канавка 303, вдалеке от слоя канала устройства, такого как слой 307 канала устройства.

На фиг. 15 показан примерный график 1500, представляющий содержание индия в InGaAs 1501, в зависимости от константы 1502 решетки, в соответствии с одним вариантом осуществления. Как показано на фиг. 15, более высокие концентрации индия в устройстве InGaAs позволяют легче получить затвор, окружающий со всех сторон кремниевые архитектуры ("GAA"). Увеличение содержания индия увеличивает константу решетки InGaAs. Как показано на фиг. 15, для устройства 1503 с тремя затворами требуется новый буфер для In0,7Ga0,3As из-за критической толщины слоя. Устройство 1504 из нанопроводников имеет толщину t, меньшую, чем критическая толщина слоя tc (t<tc).

Данные 1505 показывают, что изготовление слоя канала устройства на основе материала III-V групп на втором буферном слое на основе материала III-V групп, на первом буферном слое на основе материала III-V групп, где второй буферный слой имеет параметр решетки, соответствующий параметру решетки слоя канала устройства, и где первый буферный слой имеет параметр решетки в диапазоне между параметрами решеток подложки и слоя устройства (например, три затвора на буферном устройстве 1503, нанопроводникники на буферном устройстве 1504), позволяют повысить рабочие характеристики устройства.

На фиг. 16 иллюстрируется компьютерное устройство 1600 в соответствии с одним вариантом осуществления. В компьютерном устройстве 1600 содержится плата 1602. Плата 1602 может включать в себя множество компонентов, включающих в себя, но без ограничения, процессор 1601 и по меньшей мере одну микросхему 1604 передачи данных. Процессор 1601 физически и электрически соединен с платой 1602. В некоторых вариантах осуществления по меньшей мере одна микросхема передачи данных также физически и электрически соединена с платой 1602. В дополнительных вариантах осуществления по меньшей мере одна микросхема 1604 передачи данных составляет часть процессора 1601.

В зависимости от области применения компьютерное устройство 1600 может включать в себя другие компоненты, которые могут быть или могут не быть физически и электрически соединены с платой 1602. Эти другие компоненты включают в себя, но не ограничены этим, память, такую как энергозависимая память 1608 (например, DRAM), энергонезависимая память 1610 (например, ROM), флэш-память, графический процессор 1612, цифровой сигнальный процессор (не показан), криптопроцессор (не показан), набор 1614 микросхем, антенна 1616, дисплей, например сенсорный дисплей 1617, контроллер дисплея, например контроллер 1611 сенсорного дисплея, аккумуляторную батарею 1618, аудиокодек (не показан), видеокодек (не показан), усилитель, например усилитель 1609 мощности, устройство 1613 глобальной системы позиционирования (GPS), компас 1614, акселерометр (не показан), гироскоп (не показан), громкоговоритель 1615, камеру 1603 и устройство накопителя большой емкости (такое как привод жесткого диска, компакт-диск (CD), цифровой универсальный диск (DVD) и т.д.) (не показан).

Микросхема передачи данных, например микросхема 1604 передачи данных, обеспечивает возможность беспроводной передачи данных для передачи данных в и из компьютерного устройства 1600. Термин "беспроводной" и его производные может использоваться для описания схем, устройства, системы, способов, технологий, канала передачи и т.д., которые могут передавать данные в результате использования модулированного электромагнитного излучения через нетвердую среду. Этот термин не подразумевает, что ассоциированные устройства не содержат никаких проводников, хотя в некоторых вариантах осуществления они действительно могут их не содержать. Микросхема 1604 передачи данных может воплощать любое количество стандартов или протоколов беспроводной передачи данных, включая, но без ограничения, Wi-Fi (семейство IEEE 802.11), WiMAX (семейство IEEE 802.16), IEEE 802.20, long-term evolution (LTE), Ev-DO, HSPA+, HSDPA+, HSUPA+, EDGE, GSM, GPRS, CDMA, TDMA, DECT, Bluetooth, их производные, а также любые другие протоколы беспроводной передачи данных, которые обозначаются 3G, 4G, 5G и так далее. Компьютерное устройство 1600 может включать в себя множество микросхем передачи данных. Например, микросхема 1604 передачи данных может быть специализированной для беспроводной передачи данных на коротком расстоянии, такой как Wi-Fi и Bluetooth, и микросхема 1636 передачи данных может быть специализированной для беспроводной передачи данных на большом расстоянии, такой как GPS, EDGE, GPRS, CDMA, WiMAX, LTE, Ev-DO и другие.

По меньшей мере в некоторых вариантах осуществления по меньшей мере некоторые из компонентов компьютерного устройства 1600 (например, процессор 1601, микросхема 1604 передачи данных, графический CPU 1612) включает в себя многослойный стэк, содержащий первый буферный слой на основе материала III-V групп в канавке в изолирующем слое или на кремниевой подложке, второй буферный слой на основе материала III-V групп на первом буферном слое на основе материала III-V групп; и слой устройства на основе материала III-V групп на втором буферном слое, в котором второй буферный слой на основе материала III-V групп имеет параметр решетки, который соответствует параметру решетки слоя канала устройства на основе материала III-V групп и в котором первый буферный слой на основе материала III-V групп имеет параметр решетки в диапазоне между параметрами решеток кремниевой подложки и слоя устройства на основе материала III-V групп, как описано в настоящем документе.

Интегрированная микросхема по меньшей мере некоторых компонентов вычислительного устройства 1600 (например, процессора 1601, графического CPU 1612) включает в себя одно или больше из устройств на основе материала III-V групп, таких как транзисторы с тремя затворами, нанопроводники, нанополоски, изготовленные с использованием способов, описанных в настоящем документе. Термин "процессор" может относиться к любому устройству или части устройства, которое обрабатывает электронные данные из регистров и/или памяти для преобразования этих электронных данных в другие электронные данные, которые могут быть сохранены в регистрах и/или в памяти.

Микросхема 1604 передачи данных также может включать в себя многослойный стэк, содержащий первый буферный слой на основе материала III-V групп в канавке в изолирующем слое на кремниевой подложке, второй буферный слой на основе материала III-V групп на первом буферном слое на основе материала III-V групп; и слой устройства на основе материала III-V групп на втором буферном слое, в котором второй буферный слой на основе материала III-V групп имеет параметр решетки, который соответствует параметру решетки слоя канала устройства на основе материала III-V групп и в котором первый буферный слой на основе материала III-V групп имеет параметр решетки в диапазоне между параметрами решеток кремниевой подложки и слоя устройства на основе материала III-V групп, в соответствии с описанными в настоящем документе вариантами осуществления.

В дополнительных вариантах осуществления другой компонент, размещенный внутри компьютерного устройства 1600, может содержать многослойный стэк, содержащий первый буферный слой на основе материала III-V групп в канавке в изолирующем слое на кремниевой подложке, второй буферный слой основе материала III-V групп на первом буферном слое на основе материала III-V групп; слой устройства на основе материала III-V групп на втором буферном слое, где второй буферный слой на основе материала III-V групп имеет параметр решетки, который соответствует параметру решетки слой канала устройства на основе материала III-V групп и в котором первый буферный слой на основе материала III-V групп имеет параметр решетки в диапазоне между параметрами решеток кремниевой подложки и слоя устройства на основе материала III-V групп, в соответствии с описанными в настоящем документе вариантами осуществления.

В соответствии с одним вариантом осуществления кристалл интегральной микросхемы для передачи данных включает в себя одно или несколько устройств, таких как транзисторы с тремя затворами, нанопроводники и устройства нанополоски, как описано в настоящем документе. В различных вариантах осуществления компьютерное устройство 1600 может представлять собой переносной компьютер, нетбук, ноутбук, ультрабук, смартфон, планшетный компьютер, карманный персональный компьютер (PDA), ультрамобильный персональный компьютер, мобильный телефон, настольный компьютер, сервер, принтер, сканер, монитор, телевизионную приставку, модуль управления развлечениями, цифровую камеру, портативный музыкальный проигрыватель, или устройство цифровой видеозаписи. В дополнительных вариантах осуществления компьютерное устройство 1600 может представлять собой любое другое электронное устройство, которое обрабатывает данные.

Следующие примеры относятся к дополнительным вариантам осуществления.

Способ изготовления устройства на основе материала III-V групп, включающий стадии, на которых наносят первый буферный слой на основе материала III-V групп на кремниевую подложку; наносят второй буферный слой на основе материала III-V групп на первый буферный слой на основе материала III-V групп; и наносят слой канала устройства на основе материала III-V групп на второй буферный слой на основе материала III-V групп.

Способ изготовления устройства на основе материала III-V групп, включающий стадии, на которых наносят первый буферный слой на основе материала III-V групп на кремниевую подложку; наносят второй буферный слой на основе материала III-V групп на первый буферный слой на основе материала III-V групп; и наносят слой канала устройства на основе материала III-V групп на второй буферный слой на основе материала III-V групп, где второй буферный слой на основе материала III-V групп имеет параметр решетки, который соответствует параметру решетки слоя канала устройства на основе материала III-V групп.

Способ изготовления устройства на основе материала III-V групп, включающий стадии, на которых наносят первый буферный слой на основе материала III-V групп на кремниевую подложку; наносят второй буферный слой на основе материала III-V групп на первый буферный слой на основе материала III-V групп; и наносят слой канала устройства на основе материала III-V групп на второй буферный слой на основе материала III-V групп, где первый буферный слой на основе материала III-V групп имеет параметр решетки в диапазоне между параметрами решеток кремниевой подложки и слоя канала устройства на основе материала III-V групп.

Способ изготовления устройства на основе материала III-V групп, включающий стадии, на которых наносят первый буферный слой на основе материала III-V групп на кремниевую подложку; наносят второй буферный слой на основе материала III-V групп на первый буферный слой на основе материала III-V групп; и наносят слой канала устройства на основе материала III-V групп на второй буферный слой на основе материала III-V групп, и наносят верхний защитный слой на слой канала устройства на основе материала III-V групп.

Способ изготовления устройства на основе материала III-V групп, включающий стадии, на которых формируют канавку в изолирующем слое на кремниевой подложке, наносят первый буферный слой на основе материала III-V групп в канавку на кремниевой подложке; наносят второй буферный слой на основе материала III-V групп на первый буферный слой на основе материала III-V групп; и наносят слой канала устройства на основе материала III-V групп на второй буферный слой на основе материала III-V групп.

Способ изготовления устройства на основе материала III-V групп, включающий стадии, на которых наносят первый буферный слой на основе материала III-V групп в канавку в изолирующем слое на кремниевой подложке; наносят второй буферный слой на основе материала III-V групп на первый буферный слой на основе материала III-V групп; наносят слой канала устройства на основе материала III-V групп на второй буферный слой на основе материала III-V групп, и наносят слой диэлектрика затвора на слой канала устройства на основе материала III-V групп.

Способ изготовления устройства на основе материала III-V групп, включающий стадии, на которых наносят первый буферный слой на основе материала III-V групп в канавку в изолирующем слое на кремниевой подложке; наносят второй буферный слой на основе материала III-V групп на первый буферный слой на основе материала III-V групп; наносят слой канала устройства на основе материала III-V групп на второй буферный слой на основе материала III-V групп; формируют ребро, содержащее слой канала устройства на основе материала III-V групп на втором буферном слое на основе материала III-V групп на участке первого буферного слоя на основе материала III-V групп; и наносят слой диэлектрика затвора на ребре.

Способ изготовления устройства на основе материала III-V групп, включающий стадии, на которых наносят первый буферный слой на основе материала III-V групп в канавку в изолирующем слое на кремниевой подложке; наносят второй буферный слой на основе материала III-V групп на первый буферный слой на основе материала III-V групп; наносят слой канала устройства на основе материала III-V групп на второй буферный слой на основе материала III-V групп и наносят легированный слой материала III-V групп на слой канала устройства на основе материала III-V групп.

Способ изготовления устройства на основе материала III-V групп, включающий стадии, на которых наносят первый буферный слой на основе материала III-V групп в канавку в изолирующем слое на кремниевой подложке; наносят второй буферный слой на основе материала III-V групп на первый буферный слой на основе материала III-V групп; наносят слой канала устройства на основе материала III-V групп на второй буферный слой на основе материала III-V групп, в котором концентрация индия в слое канала устройства на основе материала III-V групп составляет по меньшей мере 53%.

Способ изготовления устройства на основе материала III-V групп, включающий стадии, на которых наносят первый буферный слой на основе материала III-V групп в канавку в изолирующем слое на кремниевой подложке; наносят второй буферный слой на основе материала III-V групп на первый буферный слой на основе материала III-V групп; наносят слой канала устройства на основе материала III-V групп на второй буферный слой на основе материала III-V групп, где по меньшей мере один из первого буферного слоя на основе материала III-V групп, второго буферного слоя на основе материала III-V групп и слоя канала устройства на основе материалов III-V групп осаждают способом химического осаждения из паровой фазы.

Устройство на основе материала III-V групп, содержащее первый буферный слой на основе материала III-V групп на кремниевой подложке; второй буферный слой на основе материала III-V групп на первом буферном слое на основе материала III-V групп; и слой канала устройства на основе материала III-V групп на втором буферном слое на основе материала III-V групп.

Устройство на основе материала III-V групп, содержащее первый буферный слой на основе материала III-V групп на кремниевой подложке; второй буферный слой на основе материала III-V групп на первом буферном слое на основе материала III-V групп; и слой канала устройства на основе материала III-V групп на втором буферном слое на основе материала III-V групп, где у второго буферного слоя на основе материалов III-V групп есть параметр кристаллической решетки, соответствующий параметру кристаллической решетки слоя канала устройства на основе материала III-V групп.

Устройство на основе материала III-V групп, содержащее первый буферный слой на основе материала III-V групп на кремниевой подложке; второй буферный слой на основе материала III-V групп на первом буферном слое на основе материала III-V групп; и слой канала устройства на основе материала III-V групп на втором буферном слое на основе материала III-V групп, где у первого буферного слоя на основе материалов III-V групп есть параметр кристаллической решетки, лежащий в диапазоне между параметрами кристаллической решетки кремниевой подложки и слоя канала устройства на основе материала III-V групп.

Устройство на основе материала III-V групп, содержащее первый буферный слой на основе материала III-V групп на кремниевой подложке; второй буферный слой на основе материала III-V групп на первом буферном слое на основе материала III-V групп; и слой канала устройства на основе материала III-V групп на втором буферном слое на основе материала III-V групп, где по меньшей мере один из первого буферного слоя на основе материала III-V групп, второго буферного слоя на основе материала III-V и слоя канала устройства на основе материала III-V групп осаждают химическим осаждением из паровой фазы.

Устройство на основе материала III-V групп, содержащее первый буферный слой на основе материала III-V групп на кремниевой подложке; второй буферный слой на основе материала III-V групп на первом буферном слое на основе материала III-V групп; и слой канала устройства на основе материала III-V групп на втором буферном слое на основе материала III-V групп, где верхний защитный слой осаждают на слой канала устройства на основе материала III-V групп.

Устройство на основе материала III-V групп, содержащее канавку в изолирующем слое на подложке; первый буферный слой на основе материала III-V групп в канавке на кремниевой подложке; второй буферный слой на основе материала III-V групп на первом буферном слое на основе материала III-V групп; и слой канала устройства на основе материала III-V групп на втором буферном слое на основе материала III-V групп.

Устройство на основе материала III-V групп, содержащее первый буферный слой на основе материала III-V групп на кремниевой подложке; второй буферный слой на основе материала III-V групп на первом буферном слое на основе материала III-V групп; и слой канала устройства на основе материала III-V групп на втором буферном слое на основе материала III-V групп; и слой диэлектрика затвора поверх слоя канала устройства на основе материала III-V групп.

Устройство на основе материала III-V групп, содержащее первый буферный слой на основе материала III-V групп на кремниевой подложке; второй буферный слой на основе материала III-V групп на первом буферном слое на основе материала III-V групп; и слой канала устройства на основе материала III-V групп на втором буферном слое на основе материала III-V групп, где ребро сформировано из слоя канала устройства на основе материала III-V групп, второго буферного слоя на основе материалов III-V групп и первого буферного слоя на основе материалов III-V групп.

Устройство на основе материала III-V групп, содержащее первый буферный слой на основе материала III-V групп на кремниевой подложке; второй буферный слой на основе материала III-V групп на первом буферном слое на основе материала III-V групп; и слой канала устройства на основе материала III-V групп на втором буферном слое на основе материала III-V групп; и легированный слой на основе материала III-V групп на участке слоя канала устройства на основе материалов III-V групп.

Устройство на основе материала III-V групп, содержащее первый буферный слой на основе материала III-V групп на кремниевой подложке; второй буферный слой на основе материала III-V групп на первом буферном слое на основе материала III-V групп; и слой канала устройства на основе материала III-V групп на втором буферном слое на основе материала III-V групп, в котором концентрация индия в слое канала устройства в материале на основе III-V групп составляет по меньшей мере 53%.

Способ изготовления электронных устройств, включающий этапы, на которых наносят первый буферный слой в канавку в изолирующем слое на подложке; наносят второй буферный слой на первый буферный слой; и наносят слой устройства на второй буферный слой, где второй буферный слой имеет параметр решетки, соответствующий параметру решетки слоя канала устройства.

Способ изготовления электронных устройств, включающий этапы, на которых наносят первый буферный слой в канавку в изолирующем слое на подложке; наносят второй буферный слой на первый буферный слой; и наносят слой устройства на второй буферный слой, где у второго буферного слоя есть параметр кристаллической решетки, соответствующий параметру кристаллической решетки слоя канала устройства, и где у первого буферного слоя есть параметр кристаллической решетки, лежащий в диапазоне между параметрами кристаллической решетки подложки и слоя устройства.

Способ изготовления электронных устройств, включающий этапы, на которых наносят первый буферный слой в канавку в изолирующем слое на подложке; наносят второй буферный слой на первый буферный слой; и наносят слой устройства на второй буферный слой, где у второго буферного слоя есть параметр кристаллической решетки, соответствующий параметру кристаллической решетки слоя канала устройства, где у первого буферного слоя есть параметр кристаллической решетки, лежащий в диапазоне между параметрами кристаллической решетки подложки и слоя устройства, и где по меньшей мере один из первого буферного слоя, второго буферного слоя и слоя устройства представляет собой слой на основе материала III-V групп, и подложка представляет собой кремниевую подложку.

Способ изготовления электронных устройств, включающий этапы, на которых наносят первый буферный слой в канавку в изолирующем слое на подложке; наносят второй буферный слой на первый буферный слой; и наносят слой устройства на второй буферный слой, где у второго буферного слоя есть параметр кристаллической решетки, соответствующий параметру кристаллической решетки слоя канала устройства, и где у первого буферного слоя есть параметр кристаллической решетки, лежащий в диапазоне между параметрами кристаллической решетки подложки и слоя устройства, где по меньшей мере один из первого буферного слоя, второго буферного слоя и слоя устройства представляет собой слой на основе материала III-V групп, и подложка представляет собой кремниевую подложку.

Способ изготовления электронных устройств, включающий этапы, на которых наносят первый буферный слой в канавку в изолирующем слое на подложке; наносят второй буферный слой на первый буферный слой; и наносят слой устройства на второй буферный слой, где у второго буферного слоя есть параметр кристаллической решетки, соответствующий параметру кристаллической решетки слоя канала устройства, и где у первого буферного слоя есть параметр кристаллической решетки, лежащий в диапазоне между параметрами кристаллической решетки подложки и слоя устройства, и где на слой устройства наносят верхний защитный слой.

Электронное устройство, содержащее первый буферный слой в канавке в изолирующем слое на подложке, второй буферный слой на первом буферном слое; и слой устройства на втором буферном слое, где второй буферный слой имеет параметр решетки, соответствующий параметру решетки слоя канала устройства, и где первый буферный слой имеет параметр решетки, лежащий в диапазоне между параметром кристаллической решетки подложки и слоя устройства.

Электронное устройство, содержащее первый буферный слой в канавке в изолирующем слое на подложке, второй буферный слой на первом буферном слое; и слой устройства на втором буферном слое, где у второго буферного слоя есть параметр кристаллической решетки, соответствующий параметру кристаллической решетки слоя канала устройства, и где у первого буферного слоя есть параметр кристаллической решетки, лежащий в диапазоне между параметрами кристаллической решетки подложки и слоя устройства, и где по меньшей мере один из первого буферного слоя, второго буферного слоя и слоя устройства представляет собой слой на основе материала III-V групп, и подложка представляет собой кремниевую подложку.

Электронное устройство, содержащее первый буферный слой в канавке в изолирующем слое на подложке, второй буферный слой на первом буферном слое; и слой устройства на втором буферном слое, где у второго буферного слоя есть параметр кристаллической решетки, соответствующий параметру кристаллической решетки слоя канала устройства, и где у первого буферного слоя есть параметр кристаллической решетки, лежащий в диапазоне между параметрами кристаллической решетки подложки и слоя устройства, и где верхний защитный слой нанесен на слой устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВА, ОСНОВАННЫЕ НА ИЗБИРАТЕЛЬНО ЭПИТАКСИАЛЬНО ВЫРАЩЕННЫХ МАТЕРИАЛАХ III-V ГРУПП | 2018 |

|

RU2752291C2 |

| КМОП УСТРОЙСТВА НА ОСНОВЕ СУРЬМЫ | 2007 |

|

RU2419916C2 |

| ПОЛУПРОВОДНИКОВЫЙ ПРИБОР И СПОСОБ ЕГО ИЗГОТОВЛЕНИЯ | 2012 |

|

RU2507634C1 |

| УСТРОЙСТВО ОТОБРАЖЕНИЯ | 2011 |

|

RU2515588C1 |

| ПОЛУПРОВОДНИКОВОЕ УСТРОЙСТВО И СПОСОБ ЕГО ИЗГОТОВЛЕНИЯ | 2017 |

|

RU2719569C1 |

| ПОЛЕВОЙ ТРАНЗИСТОР, ИСПОЛЬЗУЮЩИЙ ОКСИДНУЮ ПЛЕНКУ ДЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ, И СПОСОБ ЕГО ИЗГОТОВЛЕНИЯ | 2007 |

|

RU2400865C2 |

| СПОСОБ ФОРМИРОВАНИЯ БУФЕРНОЙ АРХИТЕКТУРЫ (ВАРИАНТЫ), МИКРОЭЛЕКТРОННАЯ СТРУКТУРА, СФОРМИРОВАННАЯ ТАКИМ ОБРАЗОМ | 2009 |

|

RU2468466C2 |

| ПОЛУПРОВОДНИКОВАЯ СТРУКТУРА И СПОСОБ ЕЕ ИЗГОТОВЛЕНИЯ | 2021 |

|

RU2817107C1 |

| Пленочный полевой транзистор с металлическим каналом | 2017 |

|

RU2654296C1 |

| ПОЛУПРОВОДНИКОВОЕ УСТРОЙСТВО | 2016 |

|

RU2705761C1 |

Изобретение относится к области изготовления электронных устройств, в частности устройств на основе материалов III-V групп. Способ изготовления устройства на основе материала III-V групп включает этапы, на которых в изолирующем слое на кремниевой подложке формируют канавку, в канавку наносят первый буферный слой на основе материала III-V групп на кремниевую подложку, на первый буферный слой наносят второй буферный слой на основе материала III-V групп, слой канала устройства на основе материала III-V групп наносят на второй буферный слой на основе материала III-V групп. Изобретение обеспечивает интеграцию устройств на основе материалов III-V групп n-типа и p-типа на кремниевой подложке. 3 н. и 15 з.п. ф-лы, 16 ил.

1. Способ изготовления устройства на основе материала III-V групп, включающий этапы, на которых:

в изолирующем слое на кремниевой подложке формируют канавку;

в канавку на подложке наносят первый буферный слой на основе материала III-V групп;

на первый буферный слой на основе материала III-V групп наносят второй буферный слой на основе материала III-V групп и

на второй буферный слой на основе материала III-V групп наносят слой канала устройства на основе материала III-V групп.

2. Способ по п. 1, в котором второй буферный слой на основе материала III-V групп имеет параметр решетки, соответствующий параметру решетки слоя канала устройства на основе материала III-V групп.

3. Способ по п. 1, в котором первый буферный слой на основе материала III-V групп имеет параметр решетки, лежащий в диапазоне между параметрами решеток кремниевой подложки и слоя канала устройства на основе материала III-V групп.

4. Способ по п. 1, дополнительно включающий этап, на котором

на слой канала устройства на основе материала III-V групп наносят верхний защитный слой.

5. Способ по п. 1, дополнительно включающий этап, на котором:

формируют ребро, содержащее слой канала устройства на основе материала III-V групп на втором буферном слое на основе материала III-V групп на участке первого буферного слоя на основе материала III-V групп и

на ребро наносят слой диэлектрика затвора.

6. Способ по п. 1, дополнительно включающий этап, на котором

на слой канала устройства на основе материала III-V групп наносят легированный слой материала III-V групп.

7. Устройство на основе материала III-V групп, содержащее:

канавку в изолирующем слое на кремниевой подложке;

первый буферный слой на основе материала III-V групп, осажденный в канавке в изолирующем слое на подложке;

второй буферный слой на основе материала III-V групп на первом буферном слое на основе материала III-V групп и

слой канала устройства на основе материала III-V групп на втором буферном слое на основе материала III-V групп.

8. Устройство на основе материала III-V групп по п. 7, в котором второй буферный слой на основе материала III-V групп имеет параметр решетки, соответствующий параметру решетки слоя канала устройства на основе материала III-V групп.

9. Устройство на основе материала III-V групп по п. 7, в котором первый буферный слой на основе материала III-V групп имеет параметр решетки, лежащий в диапазоне между параметрами решеток кремниевой подложки и слоя канала устройства на основе материала III-V групп.

10. Устройство на основе материала III-V групп по п. 7, в котором

на слое канала устройства на основе материала III-V групп осажден слой верхнего защитного слоя.

11. Устройство на основе материала III-V групп по п. 7, в котором

сформировано ребро из слоя канала устройства на основе материала III-V групп, второго буферного слоя на основе материала III-V групп и первого буферного слоя на основе материала III-V групп.

12. Устройство на основе материала III-V групп по п. 7, дополнительно содержащее слой на основе легированного материала III-V групп поверх участка слоя канала устройства на основе материала III-V групп.

13. Устройство на основе материала III-V групп по п. 7, в котором концентрация индия в слое канала устройства на основе материала III-V групп составляет по меньшей мере 53%.

14. Способ изготовления электронного устройства, включающий этапы, на которых:

в канавку в изолирующем слое на подложке наносят первый буферный слой;

на первый буферный слой наносят второй буферный слой и

на второй буферный слой наносят слой устройства, где второй буферный слой имеет параметр решетки, соответствующий параметру решетки слоя канала устройства.

15. Способ по п. 14, в котором первый буферный слой имеет параметр решетки, лежащий в диапазоне между параметрами решеток подложки и слоя устройства.

16. Способ по п. 14, в котором по меньшей мере один из первого буферного слоя, второго буферного слоя и слоя устройства является слоем на основе материала III-V групп, и подложка является кремниевой подложкой.

17. Способ по п. 14, в котором на слой устройства наносят верхний защитный слой.

18. Способ по п. 14, в котором по меньшей мере один из первого буферного слоя на основе материала III-V групп, второго буферного слоя на основе материала III-V групп и слоя канала устройства на основе материала III-V групп осаждают, используя химическое осаждение из паровой фазы.

| Перекатываемый затвор для водоемов | 1922 |

|

SU2001A1 |

| Перекатываемый затвор для водоемов | 1922 |

|

SU2001A1 |

| Способ приготовления лака | 1924 |

|

SU2011A1 |

| Способ и приспособление для нагревания хлебопекарных камер | 1923 |

|

SU2003A1 |

| Колосоуборка | 1923 |

|

SU2009A1 |

| Приспособление для суммирования отрезков прямых линий | 1923 |

|

SU2010A1 |

| Приспособление для суммирования отрезков прямых линий | 1923 |

|

SU2010A1 |

| Изложница с суживающимся книзу сечением и с вертикально перемещающимся днищем | 1924 |

|

SU2012A1 |

| Изложница с суживающимся книзу сечением и с вертикально перемещающимся днищем | 1924 |

|

SU2012A1 |

| Изложница с суживающимся книзу сечением и с вертикально перемещающимся днищем | 1924 |

|

SU2012A1 |

| Способ изготовления электроизоляционной, массы для гальванических батарей галетного типа | 1953 |

|

SU100336A1 |

Авторы

Даты

2018-02-06—Публикация

2013-06-28—Подача