Изобретение относится к области вычислительной техники и может быть использовано для арбитража в системах обработки информации при организации обмена данными между устройствами.

Известен указатель старшей единицы (Угрюмов Е.П. Цифровая схемотехника: учеб. пособие для вузов. - СПб.: БХВ-Петербург, 2010. - 816 с., рис. 2.9, с. 87-90), содержащий группу элементов И и группу элементов запрета И с одним инверсным входом. В данном устройстве реализована цепочечная схема передачи сигнала опроса путем последовательного опроса, начиная со старшего разряда, и прекращения дальнейшего опроса при выявлении первой же единицы.

Известен указатель старшей единицы (Схемотехника ЭВМ. Сборник задач: учебное пособие. М.: НИЯУ МИФИ, 2012. - 240 с., рис. 53, с. 55-56), содержащий группу элементов ИЛИ объединенных в цепочку и группу элементов запрета И с одним инверсным входом.

Недостатком данных устройств является определение одного старшего приоритета только одного ранга.

Известно многоканальное устройство приоритета (RU №2415465 С2, МПК G06F 9/46, заявлен 01.06.2009, опубл. 27.03.2011, Бюл. №9), содержащее М каналов, каждый из которых содержит дешифратор, группу элементов И, первый и второй элементы ИЛИ, элемент И с прямым и инверсными входами, элемент задержки, группу кодовых входов приоритете, вход запроса и выход ответа, причем в каждом канале вход запроса соединен с входом элемента задержки, выход которого соединен со вторыми входами всех элементов И группы элементов И своего канала, группа кодовых входов канала соединена с группой входов дешифратора канала, а выход первого элемента ИЛИ является выходом ответа канала.

В данном устройстве введена дисциплина обслуживания запросов абонентов с абсолютными приоритетами, которые могут оперативно изменяться при перенастройке вычислительной системы. Недостатком данного устройства является задание только не одинаковых приоритетов и невозможность одновременного задания нескольких уровней (рангов) приоритетов в каждом канале.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является, принятый за прототип, многовыходной указатель старшей единицы (RU №2591017 C1, МПК Н03М 7/22, G06F 13/37, G06F 9/46, заявлен 23.07.2015, опубл. 10.07.2016, Бюл. №19), содержащий группу из N внешних входов запроса Z1, Z2,…, ZN (высший приоритет имеет вход ZN), К каскадов (К - количество формируемых указателей старших единиц) и К групп внешних выходов U указателей старшей единицы, при этом каждый i-й каскад (i=1, 2, …, К) содержит группу из (N-i-1) элементов ИЛИ 1i1, 1i2, …, 1i(N-i-1) и группу из (N-i) элементов запрета И с одним инверсным входом 2i1, 2i2, …, 2i(N-i), а также группу из (N+1-i) входов запроса в i-й каскад Аi1, Ai2, …, Ai(N+1-i) и группу из (N+1-i) внешних выходов указателей старшей единицы i-го ранга Ui1, Ui2, …, Ui(N+1-i) (1-й ранг имеет высший приоритет), каждый из первых (К-1) каскадов, кроме последнего К-го каскада содержит также группу из (N-i) элементов И 3i1, 3i2, …, 3i(N-i) и группу из (N-i) выходов запроса Si1, Si2, …, Si(N-i) в следующий (i+1)-й каскад, причем в каждом i-м каскаде (i=1, 2, …, К) первые (N-i) входов Аi1, Аi2, …, Аi(N-i) из группы входов запроса, кроме последнего входа запроса Ai(N-i+1), соединены со вторыми прямыми входами соответствующих элементов 2i1, 2i2, …, 2i(N-i) из группы элементов запрета И с одним инверсным входом, выходы всех элементов группы из (N-i-1) элементов ИЛИ 1i1, 1i2, …, 1i(N-i-1) соединены с первыми инверсными входами соответствующих первых (N-i-1) элементов 2i1, 2i2, … 2i(N-i-1) группы из элементов запрета И с одним инверсным входом, кроме последнего элемента 2i(N-i), у которого первый инверсный вход соединен с последним (N-i+1) входом Ai(N-i+1) группы запроса i-го каскада и первым входом последнего элемента 1i(N-i-1) из группы элементов ИЛИ, кроме того, в каждом i-м каскаде (i=1, 2, …, К) вторые входы (N-i-1) элементов 1i1, 1i2, …, 1i(N-i-1) из группы элементов ИЛИ соединены с соответствующими (N-i-1) входами Ai2, Ai2, …, Ai(N-i) запроса в i-й канал, начиная со второго входа запроса, кроме последнего входа запроса Ai(N-i+1), а первые входы первых (N-i-2) элементов 1i1, 1i2, …, 1i(N-i-2) из группы элементов ИЛИ соединены с выходами соответствующих последующих элементов 1i2, 1i3, …, 1i(N-i-1) из группы элементов ИЛИ, кроме того, в каждом i-м каскаде (i=1, 2, …,К) выходы (N-i) элементов 2i1, 2i2, …, 2i(N-i) из группы элементов И являются первыми (N-i) внешними выходами из группы внешних выходов указателей старшей единицы i-го ранга Ui1, Ui2, …, Ui(N-i), а последний (N-i+1) внешний выход Ui(N+1-i) соединен с последним (N-i+1) входом запроса в i-й канал Ai(N-i+1).

Недостатком данного устройства является определение старшинства приоритетов только одного ранга.

К причинам, препятствующим достижению указанного ниже технического результата, относится отсутствие средств для анализа ранга многоприоритетных запросов и указания номера ранга приоритетного запроса.

Техническим результатом изобретения является расширение функциональных возможностей в части возможности анализа ранга многоприоритетных запросов и указания номера ранга приоритетного запроса в виде унитарного кода «1 из М».

Указанный технический результат при осуществлении изобретения достигается тем, что в арбитр приоритетов многоранговых запросов, содержащий первую группу из N внешних выходов указателей группы старшего приоритета U1, U2, …, UN, группу из (N-2) элементов ИЛИ 41, 42, …, 4(N-2) и первую группу из (N-1) элементов запрета И с одним инверсным входом 51, 52, …, 5(N-1), выходы которых являются первыми (N-1) внешними выходами U1, U2, …, U(N-1) из первой группы внешних выходов указателей группы старшего приоритета, причем выходы всех элементов группы из (N-2) элементов ИЛИ 41, 42, …, 4(N-2) соединены со вторыми инверсными входами соответствующих первых (N-2) элементов 51, 52, …, 5(N-2) первой группы из элементов запрета И с одним инверсным входом, а также первые и вторые входы первых (N-2) элементов 41, 42, …, 4(N-2) из группы элементов ИЛИ подключены соответственно к первым прямым и ко вторым инверсным входам соответствующих (N-2) элементов 52, 53, …, 5(N-1), начиная со второго элемента до последнего (N-1) элемента, первой группы элементов запрета И с одним инверсным входом,

дополнительно введены N групп внешних входов запросов IZ1, IZ2, …, IZN, каждая из которых содержит М разрядов ранга приоритета (высший ранг приоритета имеет старший М-й разряд, старший приоритет имеет старшая группа IZN), вторая группа из М внешних выходов указателей высшего ранга приоритета в группе OZ1, OZ2, …, OZM, группа из М элементов ИЛИ-НЕ 61, 62, …, 6M, вторая группа из (М-1) элементов запрета И с одним инверсным входом 71, 72, …, 7(M-1), инвертор 8 и группа из N блоков каналов анализа приоритета 11, 12, …, 1N, каждый из которых содержит элемент ИЛИ 3 и группу из (М-1) элементов И 21, 22, …, 2(M-1), при этом каждый v-й элемент И 2v (v=1, 2, …, (М-1)) содержит (М-v+1) входов,

причем все М разрядов приоритета каждой из N групп внешних входов запросов IZ1, IZ2, …, IZN соединены с соответствующими одноименными входами одноименных N блоков анализа приоритета 11, 12, …, 1N, а также каждый i-й разряд (i=1, 2, …, М) приоритета каждой из N групп внешних входов запросов IZ1, IZ2, …, IZN соединен с соответствующим входом одноименного i-го элемента из группы из М элементов ИЛИ-НЕ 61, 62, …, 6M,

одноименные входы (М+1), (М+2), …, (2М-1) каждого из N блоков каналов анализа приоритета 11, 12, …, 1N соединены между собой, а также подключены к соответствующим выходам (М-1) элементов, начиная с последнего М-го до второго элемента, из группы элементов ИЛИ-НЕ 6M, 6(M-1), …, 62,

кроме того, выход j-го элемента (j=М, М-1, …, 2) из группы элементов ИЛИ-НЕ 6M, 6(M-1), …, 62 соединен соответственно с прямым (M-j+1)-м входом k-го элемента (k=1, 2, …, (j-1)) второй группы из (М-1) элементов запрета И с одним инверсным входом 71, 72, …, 7(M-1), а также выход (М-1) элементов, начиная с первого элемента до предпоследнего (M-1)-го элемента, из группы элементов ИЛИ-НЕ 61, 62), …, 6(M-1), соединен с инверсным входом соответствующего одноименного (М-1) элемента, начиная с первого элемента до последнего (M-1)-го элемента, 71, 72, …, 7(М-1) второй группы из (М-1) элементов запрета И с одним инверсным входом, а выход последнего М-го элемента 6М из группы из М элементов ИЛИ-НЕ 61, 62, …, 6М соединен с входом инвертора 8,

выходы элементов второй группы из (М-1) элементов запрета И с одним инверсным входом 71, 72, …, 7(М-1) являются соответственно первыми (М-1) выходами OZ1, OZ2, …, OZ(M-1) второй группы из М внешних выходов указателей высшего ранга приоритета в группе, а выход инвертора 8 является последним М-м выходом OZM второй группы из М внешних выходов указателей высшего ранга приоритета в группе,

в каждом из N блоков каналов анализа приоритета 11, 12, …, 1N первые (М-1) входов блока, начиная с первого входа до (М-1) входа, соединены с соответствующими первыми входами элементов из группы из (М-1) элементов И 21, 22, …, 2(M-1) блока, а с (М+1)-го до (2М-1)-го входы блока соединены соответственно со вторыми, третьими, …, (М-1)-ми входами элементов из группы из (М-1) элементов И 21, 22, …, 2(M-1) блока, выходы которых соединены с соответствующими входами элемента ИЛИ 3, последний М-й вход которого соединен в М-м входом блока, а выход элемента ИЛИ 3 является выходом соответствующего блока каналов анализа приоритета 11, 12, …, 1N,

причем выходы первых (N-1) блоков каналов анализа приоритета 11, 12, …, 1(N-1), начиная с первого блока до предпоследнего (N-1) блока, соединены с первыми прямыми входами соответствующих первых (N-1) элементов 51, 52, …, 5(N-1) первой группы из элементов запрета И с одним инверсным входом, а выход последнего N-го блока каналов анализа приоритета 1N, соединен со вторым инверсным входом соответствующего (N-1) элемента 5(N-1) первой группы из элементов запрета И с одним инверсным входом и является последним N-м внешним выходом UN из первой группы внешних выходов указателей группы старшего приоритета.

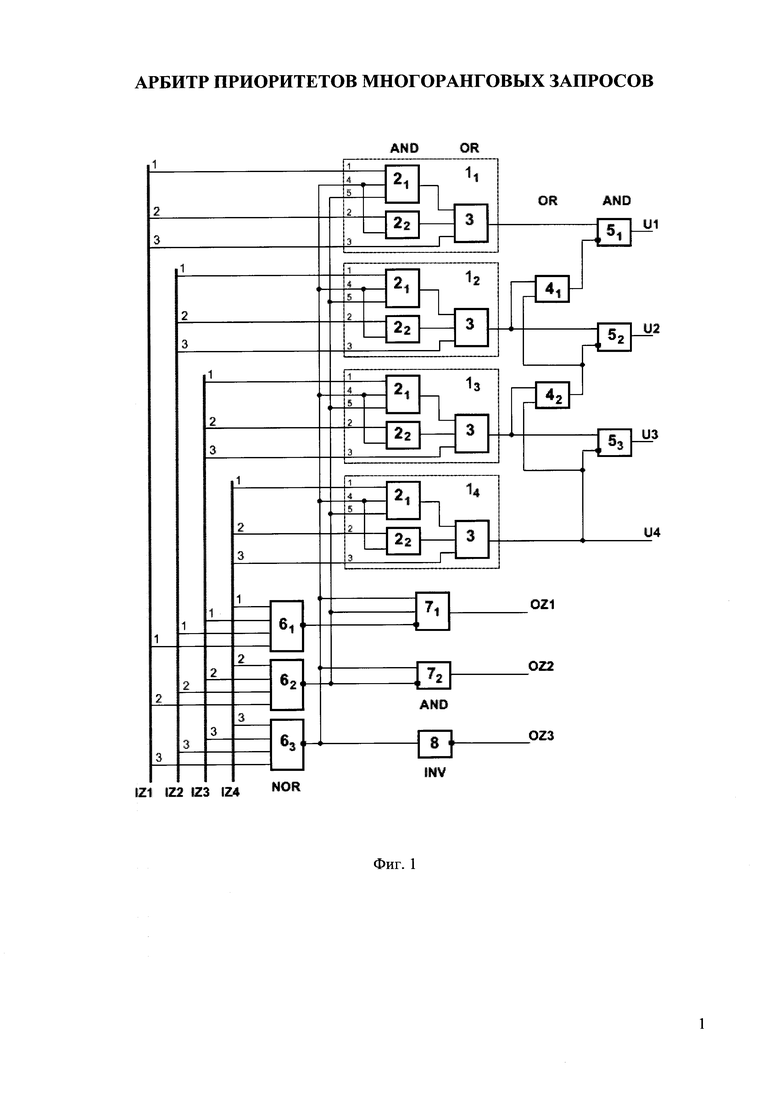

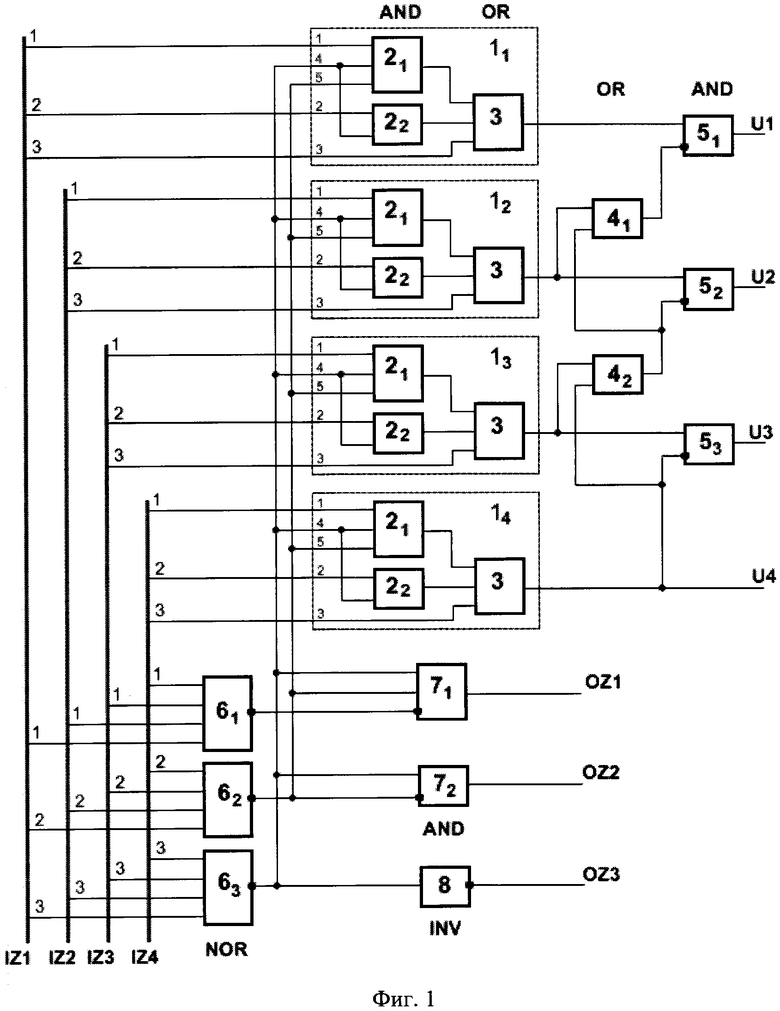

На фиг. 1 представлена схема предлагаемого арбитра приоритетов многоранговых запросов для N=4 групп внешних входов запросов IZ1, IZ2, …, IZ4 (IZN), и каждая из которых содержит М=3 разрядов ранга приоритета (высший ранг приоритета имеет старший 3-й разряд, старший приоритет имеет старшая группа IZ4).

На фиг. 1 введены следующие обозначения:

IZ1, IZ2, …, IZ4 (IZN) - N=4 групп внешних входов запросов, каждая из которых содержит М=3 разрядов ранга приоритета (высший ранг приоритета имеет

М=3 разряд, старший приоритет имеет группа IZ4 (IZN)),

U1, U2, …, U4 (UN) - первая группа из N=4 внешних выходов указателей группы старшего приоритета,

OZ1, OZ2, …, OZ3 (OZM) - вторая группа из М=3 внешних выходов указателей высшего ранга приоритета в группе,

11, 12, …, 1N - группа из N=4 блоков каналов анализа приоритета,

21, 22, …, 2(M-1) - группа из (М-1)=2 элементов И каждого блока каналов анализа приоритета 11, 12, …, 1N, при этом каждый v-й элемент И 2v (v=1, 2, …, (М-1)) содержит (М-v+1) входов,

3 - элемент ИЛИ каждого блока каналов анализа приоритета 11, 12, …, 1N,

41, 42, …, 4(N-2) - группа из (N-2)=2 элементов ИЛИ,

51, 52, …, 5(N-1) - первая группа из (N-1)=3 элементов запрета И с одним инверсным входом,

61, 62, …, 6M - группа из М=3 элементов ИЛИ-НЕ,

71, 72, 7(M-1) - вторая группа из (М-1)=2 элементов запрета И с одним инверсным входом,

8 - инвертор.

Предлагаемый арбитр приоритетов многоранговых запросов содержит N групп внешних входов запросов IZ1, IZ2, …, IZN, каждая из которых содержит М разрядов ранга приоритета (высший ранг приоритета имеет старший М-й разряд, старший приоритет имеет старшая группа IZN), первую группу из N внешних выходов указателей группы старшего приоритета U1, U2, …, UN и вторую группу из М внешних выходов указателей высшего ранга приоритета в группе OZ1, OZ2, …, OZM.

Предлагаемый арбитр приоритетов многоранговых запросов также содержит группу из (N-2) элементов ИЛИ 41, 42, …, 4(N-2), первую группу из (N-1) элементов запрета И с одним инверсным входом 51, 52, …, 5(N-1), группу из М элементов ИЛИ-НЕ 61, 62, …, 6M, вторую группу из (М-1) элементов запрета И с одним инверсным входом 71, 72, …, 7(M-1), инвертор 8 и группу из N блоков каналов анализа приоритета 11, 12, …, 1N, каждый из которых содержит элемент ИЛИ 3 и группу из (М-1) элементов И 21, 22, …, 2(M-1), при этом каждый v-й элемент И 2v (v=1, 2, …, (М-1)) содержит (М-v+1) входов.

Причем все М разрядов ранга приоритета каждой из N групп внешних входов запросов IZ1, IZ2, …, IZN соединены с соответствующими одноименными входами одноименных N блоков анализа приоритета 11, 12, …, 1N, а также каждый i-й разряд (i=1, 2, …, М) приоритета каждой из N групп внешних входов запросов IZ1, IZ2, …, IZN соединен с соответствующим входом одноименного i-го элемента из группы из М элементов ИЛИ-НЕ 61, 62, …, 6M. Одноименные входы (М+1), (М+2), …, (2М-1) каждого из N блоков каналов анализа приоритета 11, 12, …, 1N соединены между собой, а также подключены к соответствующим выходам (М-1) элементов, начиная с последнего М-го до второго элемента, из группы элементов ИЛИ-НЕ 6M, 6(M-1), …, 62.

Кроме того, выход j-го элемента (j=М, М-1, …, 2) из группы элементов ИЛИ-НЕ 6M, 6(M-1), …, 62 соединен соответственно с прямым (M-j+1)-м входом k-го элемента (k=1, 2, …, (j-1)) второй группы из (М-1) элементов запрета И с одним инверсным входом 71, 72, …, 7(M-1), а также выход (М-1) элементов, начиная с первого элемента до предпоследнего (M-1)-го элемента, из группы элементов ИЛИ-НЕ 61, 62), …, 6(M-1), соединен с инверсным входом соответствующего одноименного (М-1) элемента, начиная с первого элемента до последнего (M-1)-го элемента, 71, 72, …, 7(M-1) второй группы из (М-1) элементов запрета И с одним инверсным входом, а выход последнего М-го элемента 6M из группы из М элементов ИЛИ-НЕ 61, 62, …, 6M соединен с входом инвертора 8.

Выходы элементов второй группы из (М-1) элементов запрета И с одним инверсным входом 71, 72, …, 7(M-1) являются соответственно первыми (М-1) выходами OZ1, OZ2, …, OZ(M-1) второй группы из М внешних выходов указателей высшего ранга приоритета в группе, а выход инвертора 8 является последним М-м выходом OZM второй группы из М внешних выходов указателей высшего ранга приоритета в группе.

В каждом из N блоков каналов анализа приоритета 11, 12, …, 1N первые (М-1) входов блока, начиная с первого входа до (М-1) входа, соединены с соответствующими первыми входами элементов из группы из (М-1) элементов И 21, 22, …, 2(M-1) блока, а с (М+1)-го до (2М-1)-го входы блока соединены соответственно со вторыми, третьими, (М-1)-ми входами элементов из группы из (М-1) элементов И 21, 22, …, 2(M-1) блока, выходы которых соединены с соответствующими входами элемента ИЛИ 3, последний М-й вход которого соединен в М-м входом блока, а выход элемента ИЛИ 3 является выходом соответствующего блока каналов анализа приоритета 11, 12, …, 1N.

Кроме того, выходы первых (N-1) блоков каналов анализа приоритета 11, 12, …, 1(N-1), начиная с первого блока до предпоследнего (N-1) блока, соединены с первыми прямыми входами соответствующих первых (N-1) элементов 51, 52, …, 5(N-1) первой группы из элементов запрета И с одним инверсным входом, а выход последнего N-го блока каналов анализа приоритета 1N, соединен со вторым инверсным входом соответствующего (N-1) элемента 5(N-1) первой группы из элементов запрета И с одним инверсным входом.

Причем выходы всех элементов группы из (N-2) элементов ИЛИ 41, 42, …, 4(N-2) соединены со вторыми инверсными входами соответствующих первых (N-2) элементов 51, 52, …, 5(N-2) первой группы из элементов запрета И с одним инверсным входом, а также первые и вторые входы первых (N-2) элементов 41, 42, …, 4(N-2) из группы элементов ИЛИ подключены соответственно к первым прямым и ко вторым инверсным входам соответствующих (N-2) элементов 52, 53, …, 5(N-1), начиная со второго элемента до последнего (N-1) элемента, первой группы элементов запрета И с одним инверсным входом.

Выходы группы из (N-1) элементов запрета И с одним инверсным входом 51, 52, …, 5(N-1) являются первыми (N-1) внешними выходами U1, U2, …, U(N-1) из первой группы внешних выходов указателей группы старшего приоритета, а выход последнего N-го блока каналов анализа приоритета 1N является последним N-м внешним выходом UN из первой группы внешних выходов указателей группы старшего приоритета.

Принцип работы предлагаемого устройства состоит в следующем.

Предлагаемый арбитр приоритетов многоранговых запросов позволяет определить для высшего приоритетного запроса номер ранга и номер группы запросов (канала), соответствующей этому рангу. При этом при анализе запросов ранг запроса имеет высший приоритет и для этого ранга уже определяется соответствующий ему номер канала группы запросов. На выходах первой группы из N внешних выходов указателей группы старшего приоритета U1, U2, …, UN и второй группы из М внешних выходов указателей высшего приоритета OZ1, OZ2, …, OZM формируются результаты в виде унитарного кода соответственно «1 из N» и «1 из М».

На входы устройства одновременно поступают сигналы запроса по N группам внешних входов запросов IZ1, IZ2, …, IZN. При этом каждой группе запросов присваивается фиксированный приоритет. В устройстве старший приоритет присвоен группе запросов со старшим номером IZN, а далее приоритет уменьшается от номера к номеру. Младший приоритет задан у первой группы запросов IZ1. Кроме того, каждая группа запросов содержит М разрядов ранга приоритета. При этом каждому разряду присваивается фиксированный ранг. В предлагаемом устройстве высший ранг приоритета присвоен разряду со старшим номером М, а далее приоритет уменьшается от номера к номеру. Младший ранг приоритета присвоен первому разряду запросов.

При поступлении нескольких сигналов запроса в группе из М элементов ИЛИ-НЕ 61, 62, …, 6M определяется наличие запросов по каждому из М рангов. При наличии запроса, соответствующего ранга, на выходах соответствующих элементов ИЛИ-НЕ 61, 62, …, 6M устанавливаются нулевые сигналы, которые поступают на соответствующие входы блоков группы из N блоков каналов анализа приоритета блоков 11, 12, …, 1N, в которых по данным нулевым сигналам запрещаются сигналы запросов рангов более низких приоритетов. По сигналам с выходов элементов из группы из М элементов ИЛИ-НЕ 61, 62, …, 6M на выходах второй группы из (М-1) элементов запрета И с одним инверсным входом 71, 72, …, 7(M-1) и инверторе 8 формируется номер ранга приоритета из М разрядов в коде «1 из М», который поступает на вторую группу из М внешних выходов указателей высшего ранга приоритета в группе OZ1, OZ2, …, OZM.

Кроме того, по нулевым сигналам с выходов элементов из группы из М элементов ИЛИ-НЕ 61, 62, …, 6M в группе из N блоков каналов анализа приоритета 11, 12, …, 1N запрещаются запросы более низких приоритетов и передача на выходы блоков каналов анализа приоритета 11, 12, …, 1N соответствующих сигналов запросов высшего приоритета. По выходным сигналам приоритетов, на выходах блоков каналов анализа приоритета 11, 12, …, 1N, проводится поиск запроса группы канала с наивысшим приоритетом, и на выходах первой группы из (N-1) элементов 51, 52, …, 5(N-1) запрета И с одним инверсным входом единичный сигнал будет установлен только на одном выходе соответствующем группе старшего приоритета запроса. Таким образом, на соответствующих выходах предлагаемого устройства формируется результат в виде унитарного коде «1 из N».

Предлагаемый арбитр приоритетов многоранговых запросов работает следующим образом.

Ha N групп внешних входов запросов IZ1, IZ2, …, IZN, каждая из которых содержит М разрядов ранга приоритета (высший ранг приоритета имеет М-й разряд, старший приоритет имеет группа IZN), одновременно поступают сигналы запросов. Данные сигналы поступают на соответствующие входы блоков из группы из N блоков каналов анализа приоритета 11, 12, …, 1N группу из М элементов ИЛИ-НЕ 61, 62, …, 6M.

В группе из М элементов ИЛИ-НЕ 61, 62, …, 6M определяется наличие запросов по каждому из М рангов приоритетов и при наличии запросов соответствующих рангов формирование нулевого значения на выходах, соответствующих М элементов ИЛИ-НЕ 61, 62, …, 6M, которые затем поступают на входы элементов второй группы из (М-1) элементов запрета И с одним инверсным входом 71, 72, …, 7(M-1) и инвертор 8. При наличии высшего запроса М-го ранга будет установлено нулевое значение на выходе старшего последнего М-го элемента ИЛИ-НЕ 6M, которое поступает на первые прямые входы элементов второй группы из (М-1) элементов запрета И с одним инверсным входом 71, 72, …, 7(M-1), поэтому на их выходах будут установлены нулевые значения, а единичное значение будет установлено на выходе инвертора 8. При наличии запроса (M-1)-го ранга будет установлено нулевое значение на выходе (M-1)-го элемента ИЛИ-НЕ 6(M-1), которое поступает на инверсный вход элемента 7(M-1), и единичном значении на выходе М-го элемента ИЛИ-НЕ 6M, при отсутствии запросов М-го ранга, единичное значение будет установлено на выходе элемента 7(M-1). Аналогично будут формироваться единичные значения на выходах последующих (М-2) элементов второй группы элементов запрета И с одним инверсным входом 71, 72, …, 7(M-2). Таким образом на выходах элементов второй группы из (М-1) элементов запрета И с одним инверсным входом 71, 72, …, 7(M-1) и инверторе 8 формируется номер ранга приоритета из М разрядов в коде «1 из М», который поступает на вторую группу из М внешних выходов указателей высшего ранга приоритета в группе OZ1, OZ2, …, OZM.

Кроме того, одновременно сигналы с выходов М элементов ИЛИ-НЕ 61, 62, …, 6M поступают на соответствующие входы каждого блока группы из N блоков каналов анализа приоритета 11, 12, …, 1N, в которых по соответствующим нулевым значениям запрещаются запросы более низких приоритетов в группе из (М-1) элементов И 21, 22, …, 2(M-1). Таким образом, на выходах элементов ИЛИ 3 блоков 11, 12, …, 1N будут установлены единичные значения, соответствующие высшему рангу запроса, при этом на выходах N блоков каналов анализа приоритета 11, 12, …, 1N может быть установлено несколько единичных значений. Далее по выходным сигналам соответствующего ранга приоритетов запросов, на выходах блоков каналов анализа приоритета 11, 12, …, 1N, проводится поиск группы канала с наивысшим приоритетом запроса. На выходах группы элементов ИЛИ 41, 42, …, 4(N-2), объединенных в цепочку, входной код запросов преобразуется в код «00…011…1», где левая (старшая) единица соответствует старшей группе приоритета. Далее на выходе только одного элемента из первой группы элементов запрета И с одним инверсным входом 51, 52, …, 5(N-1), на входы которого поданы значения «01», формируется единичное значение, указывающее на группу запроса со старшим приоритетом, а на остальных выходах будет установлено нулевое значение. Данные значения передаются на (N-1) внешних выходов первой группы U1, U2, …, U(N-1). Если запрос высшего ранга приоритета соответствует старшей группе запросов IZN, то единичное значение устанавливается только на выходе старшего указателя группы UN.

Таким образом, в предлагаемом устройстве на выходах первой группы из N внешних выходов указателей группы старшего приоритета U1, U2, …, UN будут установлены сигналы, соответствующие номеру группы старшего приоритета в унитарном коде «1 из N», а на выходах второй группы из М внешних выходов указателей высшего ранга приоритета в группе OZ1, OZ2, …, OZM будет установлено значение, соответствующее номеру высшего ранга приоритета в унитарном коде «1 из М».

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый арбитр приоритетов многоранговых запросов обладает регулярностью узлов и связей и соответствует заявляемому техническому результату - расширение функциональных возможностей в части возможности анализа ранга многоприоритетных запросов и указания номера ранга приоритетного запроса в виде унитарного кода «1 из М».

| название | год | авторы | номер документа |

|---|---|---|---|

| АРБИТР ПРИОРИТЕТОВ МНОГОКАНАЛЬНЫХ ЗАПРОСОВ | 2017 |

|

RU2649953C1 |

| АРБИТР ДИСПЕТЧЕРА ЗАДАЧ | 2020 |

|

RU2749151C1 |

| МНОГОКАНАЛЬНЫЙ АРБИТР ДИСПЕТЧЕРА ЗАДАЧ | 2021 |

|

RU2777841C1 |

| МНОГОВЫХОДНОЙ АРБИТР ПРИОРИТЕТОВ | 2017 |

|

RU2649943C1 |

| КРУГОВОЙ АРБИТР ДИСПЕТЧЕРА ЗАДАЧ | 2022 |

|

RU2785771C1 |

| АРБИТР ДИСПЕТЧЕРА ЗАДАЧ ПАРАЛЛЕЛЬНОЙ СТРУКТУРЫ | 2022 |

|

RU2799386C1 |

| АРБИТР ДИСПЕТЧЕРА ЗАДАЧ КАСКАДНОЙ СТРУКТУРЫ | 2022 |

|

RU2799990C1 |

| МНОГОВЫХОДНОЙ УКАЗАТЕЛЬ СТАРШЕЙ ЕДИНИЦЫ | 2015 |

|

RU2591017C1 |

| УСТРОЙСТВО ДЛЯ КОМПРЕССИИ ДАННЫХ | 2019 |

|

RU2710987C1 |

| УСТРОЙСТВО ДЛЯ КОМПРЕССИИ ДАННЫХ | 2017 |

|

RU2672625C1 |

Изобретение относится к технологиям сетевой связи. Технический результат заключается в повышении скорости передачи данных. Арбитр приоритетов многоранговых запросов содержит N групп внешних входов запросов IZ1, IZ2, …, IZN, каждая из которых содержит М разрядов ранга приоритета (высший ранг приоритета имеет старший М-й разряд, старший приоритет имеет старшая группа IZN), первую группу из N внешних выходов указателей группы старшего приоритета U1, U2, …, UN, вторую группу из М внешних выходов указателей высшего ранга приоритета в группе OZ1, OZ2, …, OZM, группу из (N-2) элементов ИЛИ 41, 42, …, 4(N-2), первую группу из (N-1) элементов запрета И с одним инверсным входом 51, 52, …, 5(N-1), группу из М элементов ИЛИ-НЕ 61, 62, …, 6M, вторую группу из (М-1) элементов запрета И с одним инверсным входом 71, 72, …, 7(M-1), инвертор 8 и группу из N блоков каналов анализа приоритета 11, 12, …, 1N, каждый из которых содержит элемент ИЛИ 3 и группу из (М-1) элементов И 21, 22, …, 2(M-1), при этом каждый v-й элемент И 2v (v=1, 2, …, (М-1)) содержит (М-v+1) входов. 1 ил.

Арбитр приоритетов многоранговых запросов, содержащий первую группу из N внешних выходов указателей группы старшего приоритета U1, U2, …, UN, группу из (N-2) элементов ИЛИ 41, 42, …, 4(N-2) и первую группу из (N-1) элементов запрета И с одним инверсным входом 51, 52, …, 5(N-1), выходы которых являются первыми (N-1) внешними выходами U1, U2, …, U(N-1) из первой группы внешних выходов указателей группы старшего приоритета, причем выходы всех элементов группы из (N-2) элементов ИЛИ 41, 42, …, 4(N-2) соединены со вторыми инверсными входами соответствующих первых (N-2) элементов 51, 52, …, 5(N-2) первой группы из элементов запрета И с одним инверсным входом, а также первые и вторые входы первых (N-2) элементов 41, 42, …, 4(N-2) из группы элементов ИЛИ подключены соответственно к первым прямым и ко вторым инверсным входам соответствующих (N-2) элементов 52, 53, …, 5(N-1), начиная со второго элемента до последнего (N-1) элемента, первой группы элементов запрета И с одним инверсным входом,

отличающийся тем, что в него дополнительно введены N групп внешних входов запросов IZ1, IZ2, …, IZN, каждая из которых содержит М разрядов ранга приоритета (высший ранг приоритета имеет старший М-й разряд, старший приоритет имеет старшая группа IZN), вторая группа из М внешних выходов указателей высшего ранга приоритета в группе OZ1, OZ2, …, OZM, группа из М элементов ИЛИ-НЕ 61, 62, …, 6M, вторая группа из (М-1) элементов запрета И с одним инверсным входом 71, 72, …, 7(M-1), инвертор 8 и группа из N блоков каналов анализа приоритета 11, 12, …, 1N, каждый из которых содержит элемент ИЛИ 3 и группу из (М-1) элементов И 21, 22, …, 2(M-1), при этом каждый v-й элемент И 2v (v=1, 2, …, (М-1)) содержит (М-v+1) входов,

причем все М разрядов приоритета каждой из N групп внешних входов запросов IZ1, IZ2, …, IZN соединены с соответствующими одноименными входами одноименных N блоков анализа приоритета 11, 12, …, IN, а также каждый i-й разряд (i=1, 2, …, М) приоритета каждой из N групп внешних входов запросов IZ1, IZ2, …, IZN соединен с соответствующим входом одноименного i-го элемента из группы из М элементов ИЛИ-НЕ 61, 62, …, 6М,

одноименные входы (М+1), (М+2), …, (2М-1) каждого из N блоков каналов анализа приоритета 11, 12, …, 1N соединены между собой, а также подключены к соответствующим выходам (М-1) элементов, начиная с последнего М-го до второго элемента, из группы элементов ИЛИ-НЕ 6M, 6(M-1), …, 62,

кроме того, выход j-го элемента (j=М, М-1, …, 2) из группы элементов ИЛИ-НЕ 6M, 6(M-1), …, 62 соединен соответственно с прямым (M-j+1)-м входом k-го элемента (k=1, 2, …, (j-1)) второй группы из (М-1) элементов запрета И с одним инверсным входом 71, 72, …, 7(M-1), а также выход (М-1) элементов, начиная с первого элемента до предпоследнего (M-1)-го элемента, из группы элементов ИЛИ-НЕ 61, 62), …, 6(M-1), соединен с инверсным входом соответствующего одноименного (М-1) элемента, начиная с первого элемента до последнего (M-1)-го элемента, 71, 72, …, 7(M-1) второй группы из (М-1) элементов запрета И с одним инверсным входом, а выход последнего М-го элемента 6М из группы из М элементов ИЛИ-НЕ 61, 62, …, 6M соединен с входом инвертора 8,

выходы элементов второй группы из (М-1) элементов запрета И с одним инверсным входом 71, 72, …, 7(M-1) являются соответственно первыми (М-1) выходами OZ1, OZ2, …, OZ(M-1) второй группы из М внешних выходов указателей высшего ранга приоритета в группе, а выход инвертора 8 является последним М-м выходом OZM второй группы из М внешних выходов указателей высшего ранга приоритета в группе,

в каждом из N блоков каналов анализа приоритета 11, 12, …, 1N первые (М-1) входов блока, начиная с первого входа до (М-1) входа, соединены с соответствующими первыми входами элементов из группы из (М-1) элементов И 21, 22, …, 2(M-1) блока, а с (М+1)-го до (2М-1)-го входы блока соединены соответственно со вторыми, третьими, …, (М-1)-ми входами элементов из группы из (М-1) элементов И 21, 22, …, 2(M-1) блока, выходы которых соединены с соответствующими входами элемента ИЛИ 3, последний М-й вход которого соединен в М-м входом блока, а выход элемента ИЛИ 3 является выходом соответствующего блока каналов анализа приоритета 11, 12, …, 1N,

причем выходы первых (N-1) блоков каналов анализа приоритета 11, 12, …, 1(N-1), начиная с первого блока до предпоследнего (N-1) блока, соединены с первыми прямыми входами соответствующих первых (N-1) элементов 51, 52, …, 5(N-1) первой группы из элементов запрета И с одним инверсным входом, а выход последнего N-го блока каналов анализа приоритета 1N соединен со вторым инверсным входом соответствующего (N-1) элемента 5(N-1) первой группы из элементов запрета И с одним инверсным входом и является последним N-м внешним выходом UN из первой группы внешних выходов указателей группы старшего приоритета.

| МНОГОВЫХОДНОЙ УКАЗАТЕЛЬ СТАРШЕЙ ЕДИНИЦЫ | 2015 |

|

RU2591017C1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ПРИОРИТЕТА | 2009 |

|

RU2415465C2 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ПРИОРИТЕТА | 1991 |

|

RU2013804C1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ПРИОРИТЕТА | 2002 |

|

RU2231111C2 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ПРИОРИТЕТА | 2007 |

|

RU2364920C2 |

Авторы

Даты

2018-04-05—Публикация

2017-05-15—Подача