Заявленное изобретение относится к шифровальным устройствам на основе стандарта шифрования данных, а именно к устройствам раунда шифрования данных по алгоритму «Магма» и стандарту ГОСТ Р 34.12-2015 и может применяться в системах шифрования данных.

В 2015 году в России вышел новый стандарт блочного шифрования ГОСТ Р 34.12-2015. В данном стандарте введены два алгоритма блочного шифрования «Кузнечик» и «Магма». Второй в значительной степени повторяет введенный еще в 1990 году стандарт ГОСТ 28147-89. По сравнению с алгоритмом «Кузнечик» алгоритм «Магма» обладает гораздо большей компактностью и простотой при аппаратной реализации и, соответственно, в некоторых устройствах, при которых требуется компактность, алгоритм «Магма» более предпочтителен. Однако главным его недостатком по сравнению с современными алгоритмами шифрования является низкая производительность главным образом из-за трудоемких, с точки зрения аппаратной реализации, операций преобразования данных.

Шифрацию/дешифрацию данных в алгоритме «Магма» осуществляют за 32 однотипных циклов (раундов), в ходе каждого из которых выполняют определенную последовательность действий, определяемых стандартом. Последовательность действий согласно стандарту определяется функцией преобразования:

где Vs - множество всех двоичных строк длины s, где s - целое неотрицательное число; нумерацию подстрок и компонент строки осуществляют справа налево, начиная с нуля.

Вычисление значения функции g выполняют в три этапа. На первом этапе ее 32-битовый аргумент а складывают с подключем k по модулю 232. Далее на втором этапе данные при поступлении на блок подстановки t разбивают на восемь последовательных 4-битовых вектора, каждый из которых преобразуют в 4-битовый вектор соответствующим узлом замены π.

t(а)=t(а7||…||а0)=π7(а7)||…||π0(а0),где а=а7||…||а0 ∈ V32, ai ∈ V4, i=0, 1,…,7.

На третьем этапе с помощью регистра сдвига производят циклический сдвиг влево на 11 позиций.

Для аппаратной реализации шифрования по ГОСТ Р 34.12-2015 и ГОСТ 28147-89 используют устройство шифрования данных (Фиг. 1), содержащее устройство раунда, регистры для хранения различной информации, а также устройство управления, которое управляет всеми процессами устройства шифрования данных. Данные, такие как ключ и блок данных для шифрования с указанием адресов для размещения, подают в устройство шифрования по шине данных, при этом устройство управления размещает входные данные по соответствующим им регистрам. Блоки подстановки фиксированы и реализованы на регистрах в виде таблицы замен. Далее осуществляют пересылку служебной информации, такой как режим шифрации и команда старт, которая свидетельствует о том, что все данные загружены и можно начинать шифровать блок входных данных.

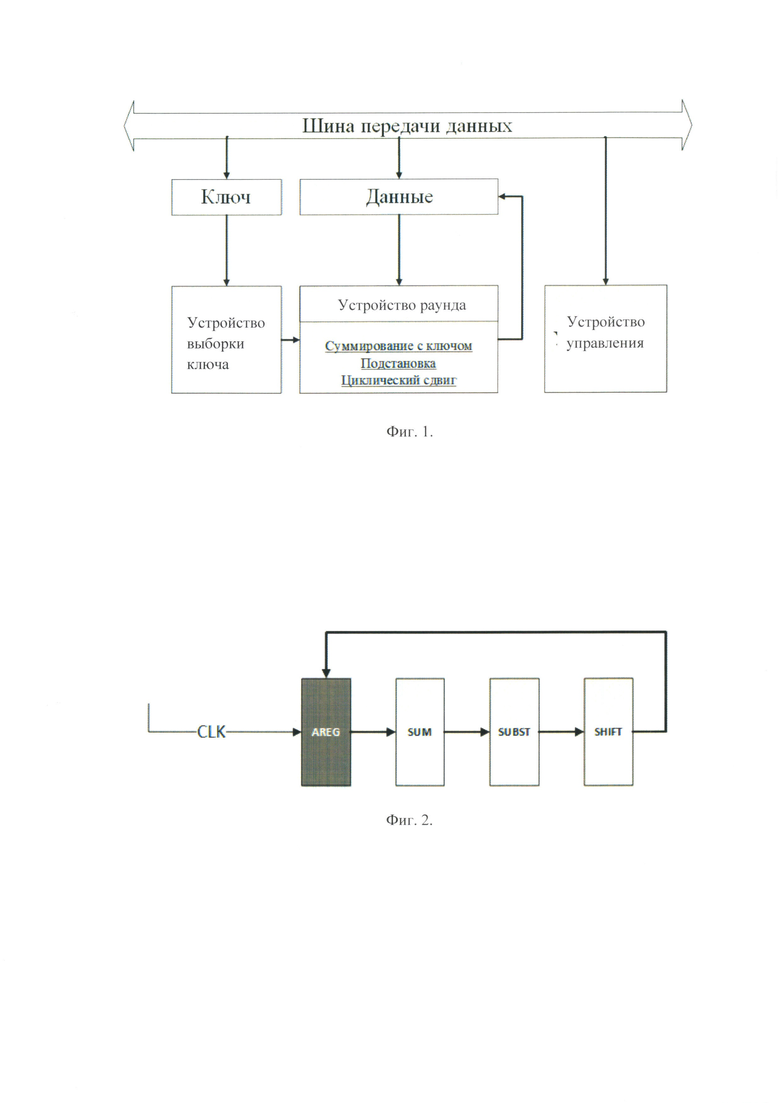

Наиболее близким к заявленному изобретению является устройство раунда шифрования данных, описанное в патенте RU 2498416, в котором 32-битный фрагмент данных из блока данных (AREG) последовательно проходит стадию суммирования в блоке суммирования (SUM), подстановки в блоке подстановки (SUBST) и сдвига в блоке сдвига (SHIFT) и снова возвращается в блок данных (AREG) (Фиг. 2). Данное устройство раунда выбрано в качестве прототипа заявленного изобретения.

Недостатком устройства раунда прототипа является малая величина тактовой частоты, определяемая суммой задержек данных в каждом блоке преобразования.

Техническим результатом заявленного изобретения является создание устройства раунда шифрования данных по алгоритму «Магма» и стандарту ГОСТ Р 34.12-2015 с увеличенной тактовой частотой без увеличения длительности раунда в тактах (длительность раунда в тактах исходная и равна единице), за счет использования трех блоков суммирования, мультиплексора и трех блоков подстановки, которые позволяют увеличить тактовую частоту до величины F=1/((Т1/2+Т4)+Т2+Т3), где T1, Т2 и Т3 - времена работы блоков подстановки, а Т4 - время задержки мультиплексора.

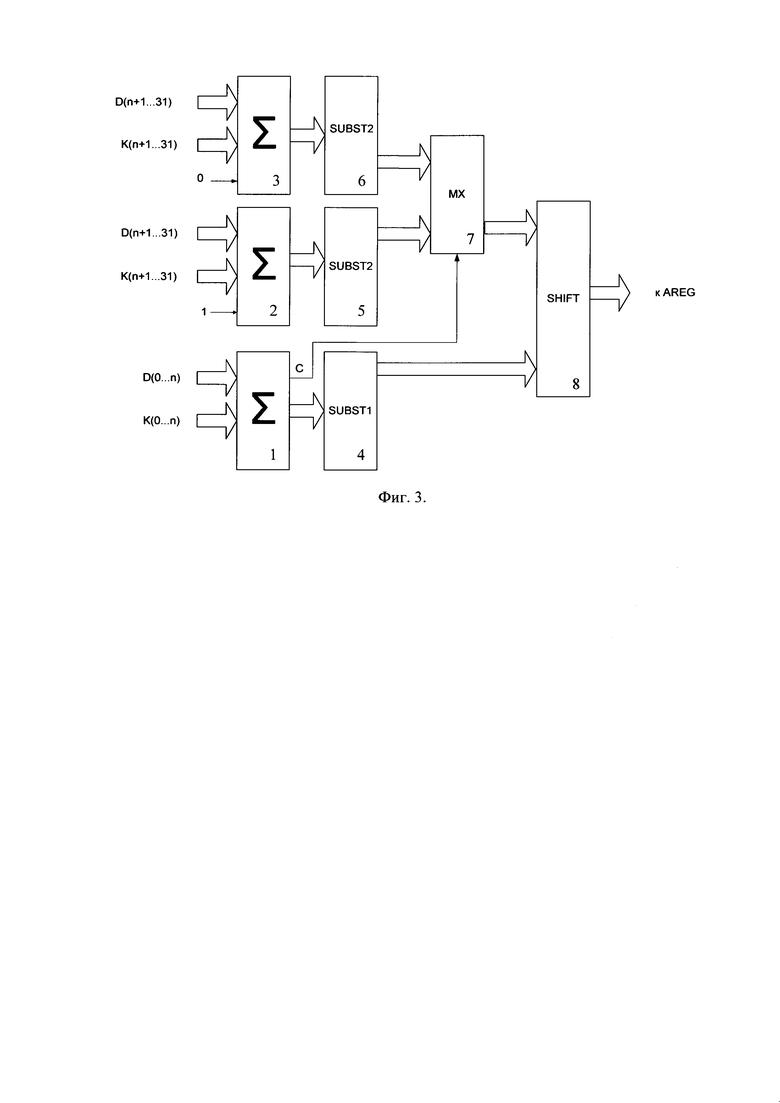

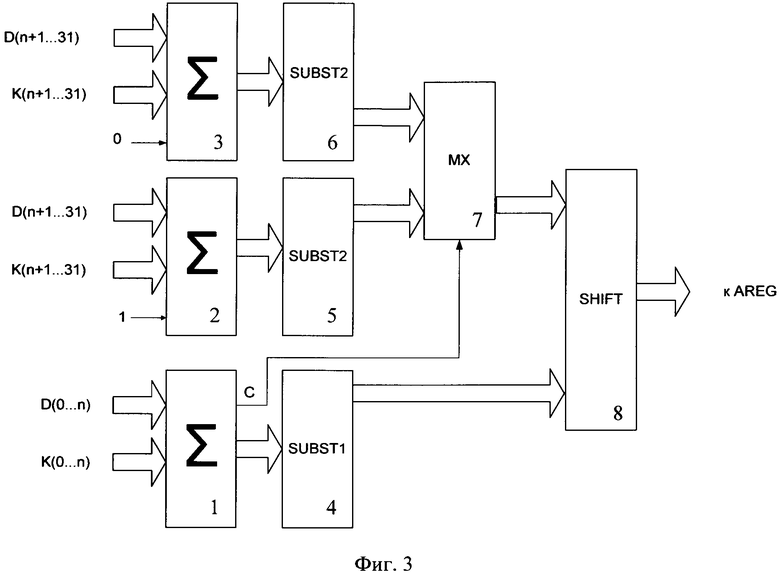

Поставленный технический результат выполнен путем создания устройства раунда шифрования данных по алгоритму «Магма» стандарта ГОСТ Р 34.12-2015, содержащего три блока суммирования, три блока подстановки, мультиплексор и блок сдвига, причем входы блоков суммирования соединены с внешним блоком данных, а выходы соединены со входами блоков подстановки, входы мультиплексора соединены с выходом первого сумматора, с выходом второго блока подстановки и с выходом третьего блока подстановки, входы блока сдвига соединены с выходом первого блока подстановки и с выходом мультиплексора, а выход блока сдвига соединен с внешним блоком данных.

Для лучшего понимания заявленного изобретения далее приводится его подробное описание с соответствующими графическими материалами.

Фиг. 1. Схема устройства шифрования данных, выполненная согласно изобретению и прототипу.

Фиг. 2. Схема устройства раунда шифрования данных, выполненная согласно прототипу.

Фиг. 3. Схема устройства раунда шифрования данных, выполненная согласно изобретению.

Элементы:

1 - первый блок суммирования;

2 - второй блок суммирования;

3 - третий блок суммирования;

4 - первый блок подстановки;

5 - второй блок подстановки;

6 - третий блок подстановки;

7 - мультиплексор;

8 - блок сдвига.

Рассмотрим более подробно функционирование заявленного устройства раунда с задержкой, сбалансированной за счет расщепления операции сложения (Фиг. 3). Сумматор по модулю 232 SUM разбит на две части, в которых производят суммирование младших разрядов слагаемых (первый сумматор 1) и старшую часть, в которой производят суммирование старших разрядов слагаемых и переноса из младшей части. Поскольку заранее неизвестно, будет ли перенос равен 0 или 1, то старшая часть выполнена в виде двух блоков (второй сумматор 2 и третий сумматор 3), один из которых выполняет суммирование старших разрядов слагаемых и 0 (переноса нет), а другой - суммирование старших разрядов слагаемых и 1 (перенос есть). Блок подстановки также разбит на две части, причем старшая часть дублируется для каждого варианта суммы (первый, второй и третий блоки подстановки 4, 5 и 6). Это возможно сделать, так как блок подстановки оперирует нибблами (4 бита) независимо друг от друга.

Первый сумматор 1 размерностью (0…n) суммирует младшую часть данных и ключа, а второй и третий сумматоры 2 и 3 суммируют старшие части данных и ключа. Перенос из младшего первого сумматора 1 управляет работой мультиплексора 7 MX, который выбирает путь прохождения данных через второй и третий сумматоры 2 и 3.

Поскольку задержка данных в блоках подстановки 4, 5 и 6 SUBST одинакова и не зависит от размерности данных (подстановка работает с четырьмя битами независимо друг от друга) и задержки данных через первый блок подстановки 4 SUBST1 и второй блок подстановки 5 SUBST2 или третий блок подстановки 6 SUBST3 (в зависимости от пути прохождения данных) приблизительно равны, то, варьируя параметр n (он может меняться от 15 до 27 с шагом 4 (размер ниббла в битах), можно добиться компенсации задержки в мультиплексоре 7. В результате задержки в прохождении данных через первый сумматор 1 и второй и третий сумматоры 2 и 3 (в зависимости от выбора по состоянию переноса из первого сумматора 1) приблизительно равны.

Пусть время работы каждого блока соответствует T1, Т2 и Т3. Таким образом, тактовая частота всего заявленного устройства раунда равна F=1/(Т1+Т2+Т3). Введение расщепления операции суммирования позволяет увеличить тактовую частоту до величины F=1/((Т1/2+Т4)+Т2+Т3), где Т4 - задержка мультиплексора 7. Поскольку задержка в мультиплексоре 7 относительно небольшая по сравнению с задержкой в сумматорах 1-3, можно считать, что задержка будет приблизительно равна F=1/((Т1/2)+Т2+Т3).

По сравнению с решением, предложенным в прототипе RU 2498416, схема заявленного устройства раунда позволяет увеличить тактовую частоту без увеличения длительности раунда в тактах (то есть она будет исходной, равной единице).

Хотя описанный выше вариант выполнения изобретения был изложен с целью иллюстрации заявленного изобретения, специалистам ясно, что возможны разные модификации, добавления и замены, не выходящие из объема и смысла заявленного изобретения, раскрытого в прилагаемой формуле изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство шифрования данных алгоритма "Магма" по стандарту ГОСТ 34.12-2015 | 2022 |

|

RU2801707C1 |

| Устройство итерации шифрования данных алгоритма "Магма" по стандарту ГОСТ Р 34.12-2015 | 2021 |

|

RU2775254C1 |

| УСТРОЙСТВО ШИФРОВАНИЯ ДАННЫХ ПО СТАНДАРТУ ГОСТ Р 34.12-2015 И АЛГОРИТМАМ "МАГМА" И AES | 2017 |

|

RU2649429C1 |

| СПОСОБ БЛОЧНОГО ПРЕОБРАЗОВАНИЯ ЦИФРОВЫХ ДАННЫХ НА ОСНОВЕ РЕГИСТРА СДВИГА ДЛИНЫ ВОСЕМЬ С 32-БИТОВЫМИ ЯЧЕЙКАМИ И С ТРЕМЯ ОБРАТНЫМИ СВЯЗЯМИ | 2022 |

|

RU2796629C1 |

| УСТРОЙСТВО ДЛЯ РЕАЛИЗАЦИИ АЛГОРИТМА ШИФРОВАНИЯ «КУЗНЕЧИК» СТАНДАРТА ГОСТ Р 34.12-2015 И АЛГОРИТМА ХЭШ-ФУНКЦИИ «СТРИБОГ» СТАНДАРТА ГОСТ Р 34.11-2012 | 2020 |

|

RU2743412C1 |

| Способ шифрования данных | 2020 |

|

RU2759862C1 |

| УСТРОЙСТВО ШИФРОВАНИЯ ДАННЫХ ПО СТАНДАРТУ ГОСТ 28147-89 | 2012 |

|

RU2498416C1 |

| Способ шифрования данных | 2018 |

|

RU2710669C1 |

| ИТЕРАТИВНЫЙ СПОСОБ БЛОЧНОГО ШИФРОВАНИЯ | 1999 |

|

RU2172075C1 |

| СПОСОБ КРИПТОГРАФИЧЕСКОГО ПРЕОБРАЗОВАНИЯ L-БИТОВЫХ ВХОДНЫХ БЛОКОВ ЦИФРОВЫХ ДАННЫХ В L-БИТОВЫЕ ВЫХОДНЫЕ БЛОКИ | 1997 |

|

RU2188513C2 |

Изобретение относится к области шифровальных устройств на основе стандарта шифрования данных. Техническим результатом заявленного изобретения является создание устройства раунда шифрования данных по алгоритму «Магма» и стандарту ГОСТ Р 34.12-2015 с увеличенной тактовой частотой без увеличения длительности раунда в тактах (длительность раунда в тактах исходная и равна единице), за счет использования трех блоков суммирования, мультиплексора и трех блоков подстановки, которые позволяют увеличить тактовую частоту до величины F=1/((Т1/2+Т4)+Т2+Т3), где T1, Т2 и Т3 - времена работы блоков подстановки, а Т4 - время задержки мультиплексора. Раскрыто устройство раунда шифрования данных по алгоритму «Магма» стандарта ГОСТ Р 34.12-2015, содержащее три блока суммирования, три блока подстановки, мультиплексор и блок сдвига, причем входы блоков суммирования соединены с внешним блоком данных, а выходы соединены со входами блоков подстановки, входы мультиплексора соединены с выходом первого сумматора, с выходом второго блока подстановки и с выходом третьего блока подстановки, входы блока сдвига соединены с выходом первого блока подстановки и с выходом мультиплексора, а выход блока сдвига соединен с внешним блоком данных. 3 ил.

Устройство раунда шифрования данных по алгоритму «Магма» стандарта ГОСТ Р 34.12-2015, содержащее три блока суммирования, три блока подстановки, мультиплексор и блок сдвига, причем входы блоков суммирования соединены с внешним блоком данных, а выходы соединены со входами блоков подстановки, входы мультиплексора соединены с выходом первого сумматора, с выходом второго блока подстановки и с выходом третьего блока подстановки, входы блока сдвига соединены с выходом первого блока подстановки и с выходом мультиплексора, а выход блока сдвига соединен с внешним блоком данных.

| УСТРОЙСТВО ШИФРОВАНИЯ ДАННЫХ ПО СТАНДАРТУ ГОСТ 28147-89 | 2012 |

|

RU2498416C1 |

| СПОСОБ НЕЛИНЕЙНОГО ТРЕХМЕРНОГО МНОГОРАУНДОВОГО ПРЕОБРАЗОВАНИЯ ДАННЫХ RDOZEN | 2015 |

|

RU2591015C1 |

| СПОСОБ БЛОЧНОГО ИТЕРАТИВНОГО ШИФРОВАНИЯ | 2000 |

|

RU2186467C2 |

| US 8306217 B2, 06.11.2012 | |||

| EP 1829276 B1, 20.03.2013. | |||

Даты

2018-05-16—Публикация

2017-03-06—Подача