Область техники, к которой относится изобретение

Изобретение относится к измерительной технике, в частности к аналого-цифровым преобразователям, и может быть использовано в цифровых системах для измерения и контроля аналоговых величин.

Уровень техники

Известен аналого-цифровой преобразователь последовательного приближения, содержащий схему сравнения, регистр последовательной аппроксимации, цифро-аналоговый преобразователь, элемент И, генератор тактовых импульсов ([1]. Чернов В.Г. Устройства ввода-вывода аналоговой информации для цифровых систем сбора и обработки данных. - М.: Машиностроение, 1988. - С. 85, рис. 57. Функциональная схема и временные диаграммы АЦП последовательной аппроксимации).

Недостатком устройства является низкое быстродействие, поскольку не учитывается время установления напряжения на выходе цифро-аналогового преобразователя и поиск производится среди всех возможных кодов, а также то, что устройство может быть использовано для измерения и контроля лишь однополярных аналоговых сигналов (сигналов положительной полярности).

Наиболее близким аналогом-прототипом к заявляемому техническому решению является аналого-цифровой преобразователь ([2]. Патент RU 2204884, МПК Н03М 1/26).

Аналого-цифровой преобразователь (АЦП) содержит: схему сравнения; цифро-аналоговый преобразователь (ЦАП); триггер; генератор импульсов; счетчик; регистр; постоянное запоминающее устройство (ПЗУ); АЦП считывания, причем на первые входы АЦП считывания и схему сравнения подается входное преобразуемое напряжение с первого входа устройства, а ко второму входу схемы сравнения подключен выход ЦАП, первые и вторые входы которого являются первыми выходами устройства, вторые входы ЦАП соединены с третьими входами ПЗУ и с выходами регистра, первый вход которого соединен со вторым входом устройства и первым входом триггера, выход которого является вторым выходом устройства и подключен ко второму входу АЦП считывания и входу генератора импульсов, выход которого соединен со вторым входом триггера и первым входом счетчика, выход которого соединен со своим вторым входом и третьими входами триггера и схемы сравнения, а также со вторым входом регистра; выходы АЦП считывания подключены к первым входам ЦАП и ПЗУ, второй вход ПЗУ соединен с выходом схемы сравнения, первые выходы ПЗУ соединены с третьими входами регистра, вторые выходы - с третьими входами счетчика, а третий выход - с четвертым входом триггера.

Недостатком устройства является возможность осуществления аналого-цифрового преобразования сигналов только положительной полярности.

Раскрытие изобретения

Технический результат, который может быть достигнут с помощью предлагаемого изобретения, сводится к обеспечению возможности аналого-цифрового преобразования не только однополярных положительных, но так же однополярных отрицательных и двуполярных сигналов, повышению точности и быстродействия и снижению сложности схемы.

Технический результат достигается тем, что в аналого-цифровой преобразователь содержащий: схему сравнения; цифро-аналоговый преобразователь (ЦАП); триггер; генератор импульсов; счетчик; регистр; постоянное запоминающее устройство (ПЗУ); АЦП считывания, первый вход которого соединен с первым входом схемы сравнения, а ко второму входу схемы сравнения подключен выход ЦАП, вторые входы ЦАП соединены с третьими входами ПЗУ и с выходами регистра, первый вход которого соединен со вторым входом устройства и первым входом триггера, выход которого подключен ко второму входу АЦП считывания и входу генератора импульсов, выход которого соединен со вторым входом триггера и первым входом счетчика, выход которого соединен со своим вторым входом и третьими входами триггера и схемы сравнения, а также со вторым входом регистра; выходы АЦП считывания подключены к первым входам ЦАП и ПЗУ, второй вход ПЗУ соединен с выходом схемы сравнения, первые выходы ПЗУ соединены с третьими входами регистра, вторые выходы - с третьими входами счетчика, а третий выход - с четвертым входом триггера, введен блок определения знака и инвертирования отрицательных напряжений (БОЗ и ИОН), причем вход БОЗ и ИОН служит входом устройства, первый выход БОЗ и ИОН служит первым выходом устройства, второй выход БОЗ и ИОН подключен к первым входам схемы сравнения и АЦП считывания; первые и вторые входы ЦАП являются вторыми выходами устройства, а выход триггера является третьим выходом устройства.

БОЗ и ИОН содержит аналоговый инвертор, компаратор, первый (нормально замкнутый) аналоговый ключ, второй (нормально разомкнутый) аналоговый ключ; вход БОЗ и ИОН подключен одновременно к входу аналогового инвертора, первому (неинвертирующему) входу компаратора, сигнальному входу второго (нормально разомкнутого) аналогового ключа; второй (инвертирующий) вход компаратора «заземлен»; выход компаратора одновременно подключен к первому выходу БОЗ и ИОН и входам управления аналоговых ключей, выходы которых соединены со вторым выходом БОЗ и ИОН; выход аналогового инвертора подключен к сигнальному входу первого (нормально замкнутого) аналогового ключа.

Краткое описание чертежей

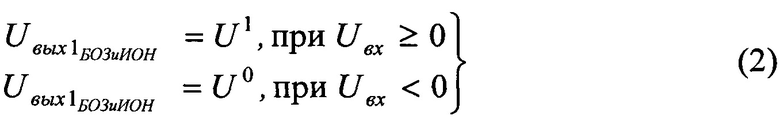

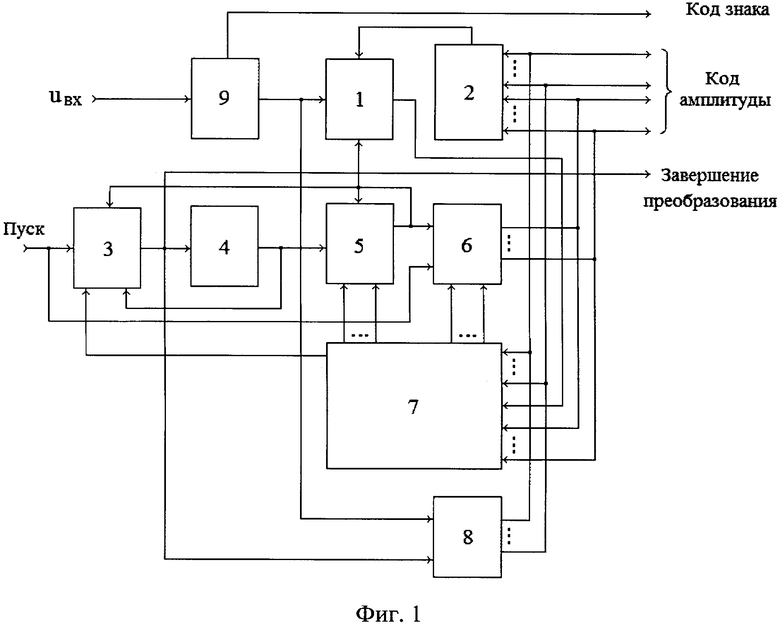

На фиг. 1 приведена структурная схема аналого-цифрового преобразователя.

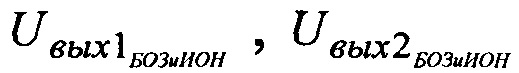

На фиг. 2 приведена структурная схема блока определения знака и инвертирования отрицательных напряжений.

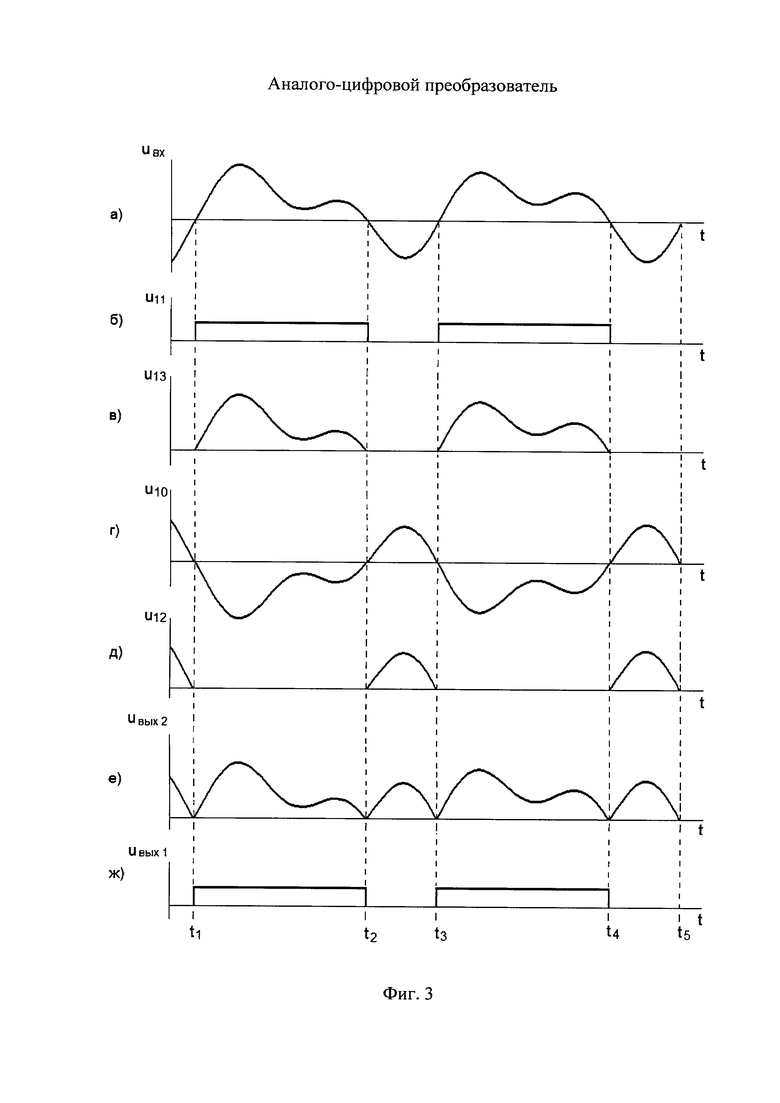

На фиг. 3 приведены временные диаграммы, поясняющие работу блока определения знака и инвертирования отрицательных напряжений.

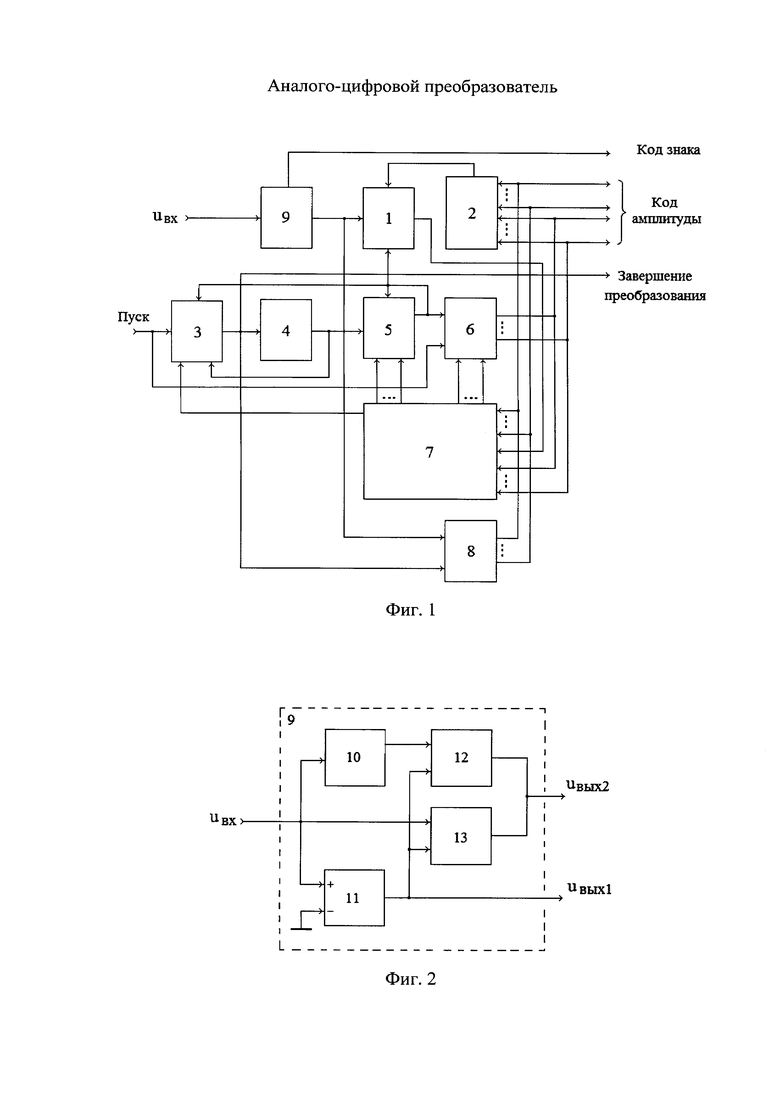

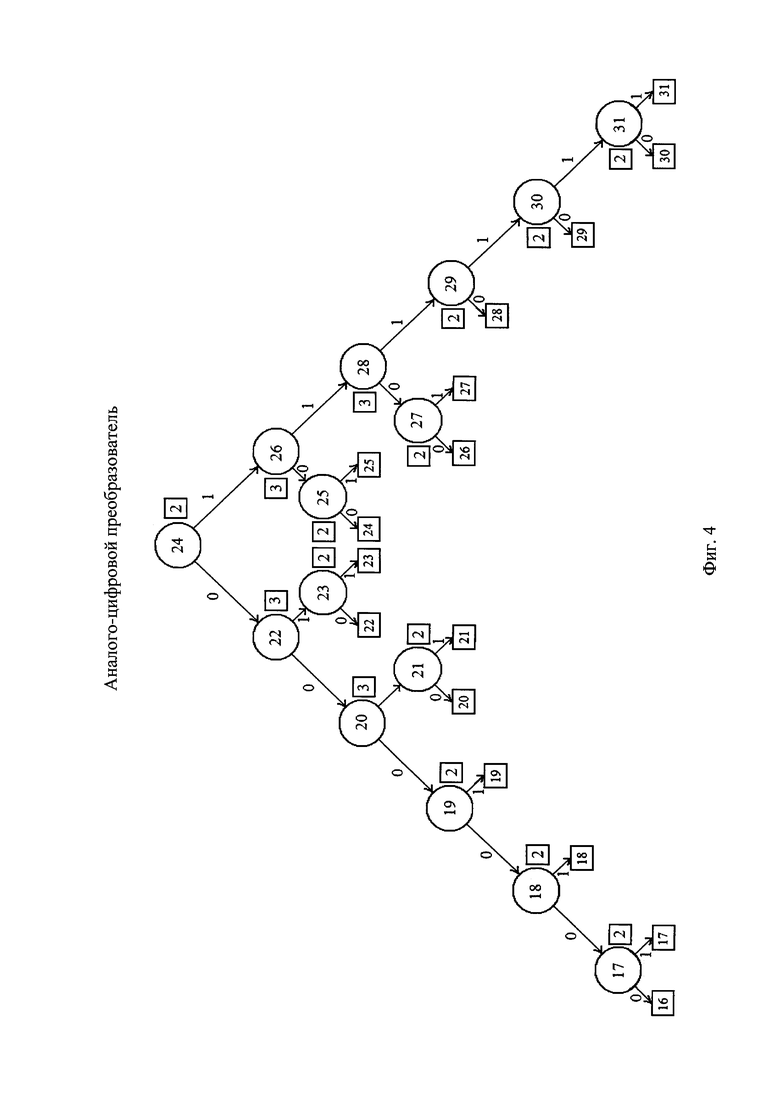

На фиг. 4 приведен алгоритм процедуры подбора кода.

Осуществление изобретения

Аналого-цифровой преобразователь содержит схему сравнения 1, цифро-аналоговый преобразователь (ЦАП) 2, триггер 3, генератор импульсов 4, счетчик 5, регистр 6, постоянное запоминающее устройство (ПЗУ) 7, АЦП считывания 8, блок определения знака и инвертирования отрицательных напряжений (БОЗ и ИОН) 9, причем вход БОЗ и ИОН 9 служит входом устройства («Uвх»), первый выход БОЗ и ИОН 9 служит первым выходом устройства («код знака»), второй выход БОЗ и ИОН 9 подключен к первым входам АЦП считывания 8 и схемы сравнения 1; ко второму входу схемы сравнения 1 подключен выход ЦАП 2, первые входы (старшие разряды) и вторые входы (младшие разряды) которого являются вторыми выходами устройства («код амплитуды»), вторые входы ЦАП 2 соединены с третьими входами ПЗУ 7 и с выходами регистра 6, первый вход которого соединен со вторым входом устройства («пуск») и первым входом триггера 3, выход которого является третьим выходом устройства («завершение преобразования») и подключен ко второму входу АЦП считывания 8 и входу генератора импульсов 4, выход которого соединен со вторым входом триггера 3 и первым входом счетчика 5, выход которого соединен со своим вторым входом и третьими входами триггера 3 и схемы сравнения 1, а также со вторым входом регистра 6; выходы АЦП считывания 8 подключены к первым входам ЦАП 2 и ПЗУ 7, второй вход ПЗУ 7 соединен с выходом схемы сравнения 1, первые выходы ПЗУ 7 соединены с третьими входами регистра 6, вторые выходы - с третьими входами счетчика 5, а третий выход - с четвертым входом триггера 3.

БОЗ и ИОН 9 содержит аналоговый инвертор 10, компаратор 11, первый (нормально замкнутый) аналоговый ключ 12, второй (нормально разомкнутый) аналоговый ключ 13; вход БОЗ и ИОН 9 подключен одновременно к входу аналогового инвертора 10, первому (неинвертирующему) входу компаратора 11, сигнальному входу второго (нормально разомкнутого) аналогового ключа 13; второй (инвертирующий) вход компаратора 11 «заземлен»; выход компаратора 11 одновременно подключен к первому выходу БОЗ и ИОН 9 и входам управления аналоговых ключей 12 и 13, выходы которых соединены со вторым выходом БОЗ и ИОН 9; выход аналогового инвертора 10 подключен к сигнальному входу первого (нормально замкнутого) аналогового ключа 12.

Аналого-цифровой преобразователь работает следующим образом.

БОЗ и ИОН 9 призван определить знак (полярность) уровня напряжения входного сигнала и ретранслировать входной сигнал далее с единичным коэффициентом передачи, а в случае отрицательной полярности подвергнуть транслируемый сигнал инверсии, то есть сформировать модуль входного сигнала. ([3]. Патент RU 2356163, МПК Н03М 1/34; [4]. Хорольский В.Я., Бондарь С.Н, Бондарь М.С. Повышение эффективности высокоскоростных аналого-цифровых преобразователей за счет введения блока определения знака и инвертирования отрицательных напряжений // Известия высших учебных заведений. Северо-Кавказский регион. Технические науки. - 2007. - №3. - С. 15-17.) В частности:

1) в случае поступления на вход БОЗ и ИОН 9 (устройства) сигнала положительной полярности (интервалы времени [t1; t2], [t3; t4] (фиг. 3)):

- компаратор 11 формирует сигнал с уровнем логической единицы (фиг. 3б);

- на первом выходе БОЗ и ИОН 9 (первом выходе устройства («код знака»)) формируется сигнал с уровнем логической единицы (фиг. 3ж);

- (нормально разомкнутый) аналоговый ключ 13 переводится в замкнутое состояние;

- (нормально замкнутый) аналоговый ключ 12 переводится в разомкнутое состояние;

- входной сигнал транслируется, через замкнутый аналоговый ключ 13 (фиг. 3в), на второй выход БОЗ и ИОН 9 (фиг. 3е);

2) в случае поступления на вход БОЗ и ИОН 9 (устройства) сигнала отрицательной полярности (интервалы времени [t2; t3], [t4; t5] (фиг. 3)):

- компаратор И формирует сигнал с уровнем логического нуля (фиг. 3б);

- на первом выходе БОЗ и ИОН 9 (первом выходе устройства («код знака»)) формируется сигнал с уровнем логического нуля (фиг. 3ж);

- (нормально разомкнутый) аналоговый ключ 13 переводится в разомкнутое состояние;

- (нормально замкнутый) аналоговый ключ 12 переводится в замкнутое состояние;

- входной сигнал, инвертированный посредством аналогового инвертора 10 (фиг. 3г), транслируется, через замкнутый аналоговый ключ 12 (фиг. 3д), на второй выход БОЗ и ИОН 9 (фиг. 3е).

Таким образом, БОЗ и ИОН 9 фактически формирует модуль (1) (фиг. 3е) и знак (2) (фиг. 3ж) транслируемого сигнала.

где  - выходное напряжение БОЗ и ИОН 9 на первом и втором выходах (Uвых 1,Uвых 2 - фиг. 3е, 3ж);

- выходное напряжение БОЗ и ИОН 9 на первом и втором выходах (Uвых 1,Uвых 2 - фиг. 3е, 3ж);

U1 и U0 - высокий и низкий уровни напряжения - уровни логической единицы и нуля.

Схема сравнения 1 предназначена для сравнения модуля входного преобразуемого напряжения |Uвх| и напряжения с выхода ЦАП 2 - UЦАП. В случае |UВХ|>UЦАП на выходе схемы сравнения 1 появится сигнал, соответствующий логической единице, в противном случае - логическому нулю. В качестве схемы сравнения 1 используется стробируемый компаратор. При подаче нулевого уровня на его третий (стробирующий) вход, напряжение на выходе схемы сравнения 1 фиксируется.

ЦАП 2 предназначен для преобразования цифрового кода, подаваемого на его вход, в соответствующий уровень выходного аналогового напряжения. При этом на первые входы (старшие разряды) ЦАП 2 подается код с выхода АЦП считывания 8, а на вторые входы (младшие разряды) подается код с выхода регистра 6.

Триггер 3 предназначен для фиксации начала и конца процесса преобразования. При подаче на его первый вход импульса триггер 3 переходит в единичное состояние и начинается процесс преобразования. По окончании процесса преобразования триггер 3 сбрасывается в нулевое состояние импульсом с выхода генератора импульсов 4 (поступающего на второй вход триггера 3) при поступлении на третий вход триггера 3 нулевого логического уровня с выхода счетчика 5 и единичного сигнала с третьего выхода ПЗУ 7.

Генератор импульсов 4 предназначен для синхронизации работы устройства. Он запускается при подаче на его управляющий вход напряжения, соответствующего логической единице, с выхода триггера 3.

Счетчик 5 предназначен для формирования интервала времени, соответствующего времени установления напряжения на выходе ЦАП 2 для текущего кода. Для этого в счетчик 5 записывается некоторое число, а счетчик 5 переводится в режим вычитания. При подаче на его первый вход импульсов содержимое счетчика 5 уменьшается. По достижении содержимым счетчика 5 нулевого значения на его выходе устанавливается уровень логического нуля, сигнализирующий об окончании заданного интервала времени. Уровень логического нуля с выхода счетчика 5 поступает на его второй вход, и он переходит в режим записи. С приходом положительного фронта на первый вход счетчика 5 в него записывается информация, поданная на его третьи (информационные) входы. При этом на выходе счетчика 5 устанавливается уровень логической единицы, он переходит в режим вычитания и формирования следующего временного отрезка. Если для данного кода Ki (поданного на вход ЦАП 2) время установления выходного напряжения ЦАП 2 составляет Тi, а период импульсов, поступающих с генератора 4, составляет Δt, то для формирования временного интервала Ti в счетчик необходимо записать код, равный NСЧi=Ti/Δt. При описании работы устройства будем считать, что величина задержки пропорциональна разнице между предыдущим кодом и следующим (задержка установления напряжения на выходе ЦАП 2) плюс один импульс на время срабатывания схемы сравнения 1. Например, если после кода 8 (1000) на вход ЦАП 2 подается код 6 (0110), то в счетчик 5 необходимо записать число 3 (3=8-6+1).

Регистр 6 предназначен для хранения младших разрядов текущего значения выходного кода. При подаче импульса на первый вход регистра 6 в его старший разряд записывается единица, а остальные разряды обнуляются. По положительному фронту импульса, поданного на второй вход регистра 6, в него записывается информация, поданная на его третьи входы с первых выходов ПЗУ 7.

ПЗУ 7 предназначено для хранения цифровых кодов, используемых в процессе выполнения процедуры подбора выходного кода, соответствующего модулю входного аналоговому напряжению |UВХ|. В ПЗУ 7 также хранятся значения задержек для всех используемых кодов (соответствующих времени установления напряжения на выходе ЦАП 2).

АЦП считывания 8 предназначен для предварительного "грубого" преобразования модуля входного аналогового напряжения, чтобы уменьшить область поиска на втором этапе подбора кода. При этом используется АЦП считывания небольшой разрядности, характеризуемый невысокой сложностью и стоимостью.

Задача построения оптимальной процедуры подбора кода в процессе аналого-цифрового преобразования соответствует известной задаче построения оптимальных программ диагностирования, т.е. поиску в объекте контроля единственного неисправного элемента ([5]. Пашковский Г.С. Задачи оптимального обнаружения и поиска отказов в РЭА / Под. ред. И.А. Ушакова. - М.: Радио и связь, 1981. - с. 50-84). В данном случае необходимо найти единственное значение кода, наиболее соответствующее входному преобразуемому напряжению. Допустим, разрядность АЦП (предлагаемого устройства) равна 6, причем с помощью АЦП считывания 8 формируются два старших разряда устройства. Пусть на первом этапе (с помощью АЦП считывания 8) определено, что выходной код, соответствующий входному напряжению, находится в диапазоне от 16 до 31 (т.е. код на выходе АЦП считывания 8 равен 01). Тогда оптимальная процедура подбора кода может иметь вид, показанный на фиг. 4.

В соответствии с фиг. 4 первым должен быть проверен код, равный 24, или в двоичной форме - 01 1000 (старшие два разряда, формируемые с помощью АЦП считывания 8, отделены пробелом). Если напряжение на выходе ЦАП 2 будет больше модуля входного напряжения (|UВХ|<UЦАП), то следующим должен быть проверен код 22 (01 0110) - переход производится по левой ветви графа, выходящей из первой вершины и помеченной цифрой 0. Если напряжение на выходе ЦАП 2 будет меньше модуля входного напряжения (|UВХ|>UЦАП), то следующим должен быть проверен код 26 (01 1010) - переход производится по правой ветви графа, выходящей из первой вершины и помеченной цифрой 1. При достижении висячей вершины или вершины, у которой отсутствует левая или правая ветвь, процесс подбора кода заканчивается. При этом в качестве результата преобразования берется код, указанный на фиг. 4 в прямоугольнике (к которому подходят стрелки). В прямоугольниках справа от вершин графа указана задержка для данного кода. Заметим, что некоторые коды, например 24, 22, 26, могут быть получены за меньшее число шагов, чем значения некоторых других кодов, например 16, 17, 30, 31. Т.е. существует возможность строить процедуру подбора кода таким образом, чтобы коды, вероятность появления которых выше, находились за меньшее число шагов.

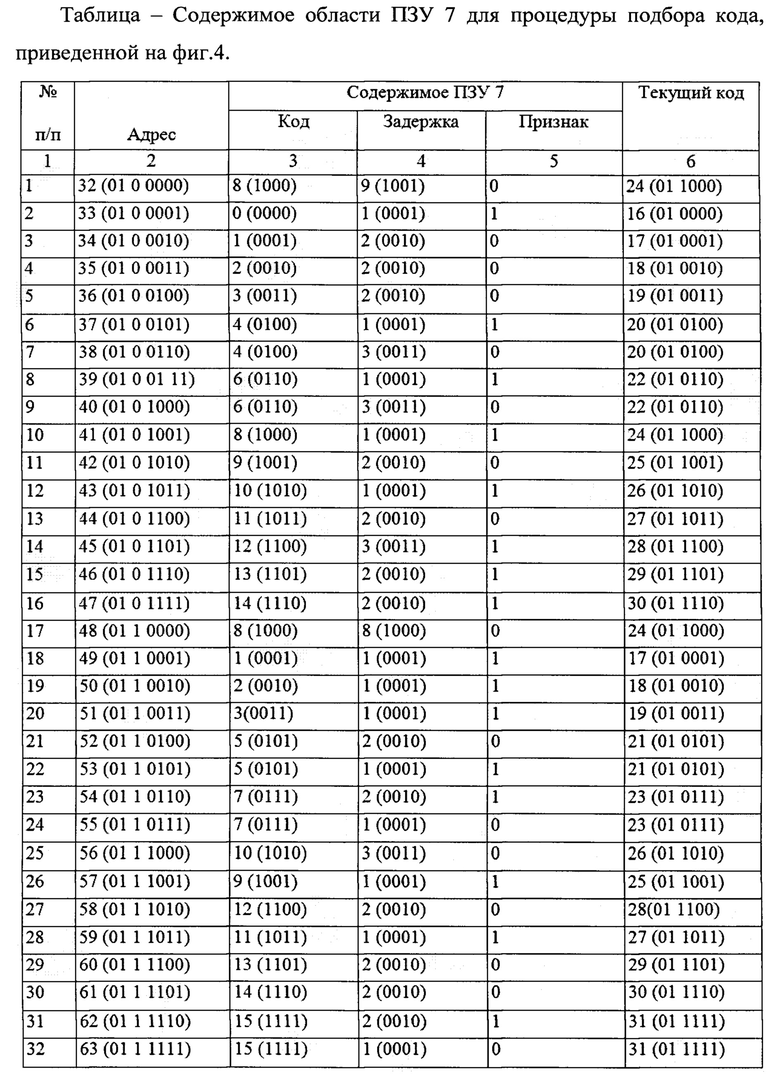

Содержимое области ПЗУ 7 для этой процедуры подбора кода приведено в таблице.

Процедура подбора кода записана в ПЗУ 7 в виде последовательности слов. Адреса слов приведены в столбце №2 "Адрес". Значение адреса приведено как в десятичной форме, так и в двоичной (в скобках). Адрес состоит из трех частей. В двоичном представлении адреса в таблице отдельные части отделены пробелами. Два старших разряда адреса поступают с выхода АЦП считывания 8, и для данной процедуры подбора кода они имеют одно и то же значение - 01. Средняя часть адреса (1 бит) формируется сигналом с выхода схемы сравнения 1. Младшая часть адреса определяется кодом, поступающим с выхода регистра 6.

Каждое слово, хранящееся в ПЗУ 7, имеет три поля. Первое поле "Код" (столбец №3) содержит младшие разряды текущего кода, используемого на данном шаге подбора выходного кода (в таблице приведено десятичное значение этого кода и в скобках - его двоичное представление). Поле "Задержка" (столбец №4) содержит число, пропорциональное времени установления ЦАП 2 и срабатывания схемы сравнения 1 для соответствующего кода из поля "Код" (столбец №3). Поле "Признак окончания" (столбец №5) определяет момент времени окончания процедуры подбора кода. Выполнение процедуры подбора кода заканчивается, если это поле будет содержать единицу.

В столбце №6 таблицы приведены текущие значения кода, используемые в процессе подбора выходного кода. Каждый код состоит из двух частей, они отделены друг от друга пробелами. Старшие два разряда формируются с помощью АЦП считывания 8, а младшие четыре разряда хранятся в регистре 6.

Рассмотрим работу устройства при следующих исходных данных. Разрядность АЦП - 6. Разрядность АЦП считывания 8 равна двум. Диапазон для модуля двуполярного входного напряжения составляет 10 В (в случае симметричности двуполярного входного напряжения диапазон входных сигналов может достигать 20 В). Для 6-разрядного АЦП в этом случае ступень квантования равна ΔU=10 В/26=10 В/64=0,15625 В. Это означает, что при подаче на вход ЦАП 2 кода, например, равного 24, на его выходе будет напряжение UЦАП=24⋅0,15625=3,75 В. Предположим, что модуль входного напряжения (напряжение поступающее со второго выхода БОЗ и ИОН 9 на вход схемы сравнения 1) составляет 3,2 В (|UВХ|=3,2B).

В исходном состоянии триггер 3 находится в нулевом состоянии. Для запуска очередного цикла аналого-цифрового преобразования на второй вход устройства "Пуск" подают кратковременный импульс, который поступает на первый вход регистра 6, и в его старший разряд записывается единица, а остальные разряды обнуляются. В данном случае, поскольку разрядность регистра 6 равна четырем, в него будет записан код 1000.

Импульс запуска со второго входа устройства "Пуск" также поступит на первый вход триггера 3, под воздействием которого триггер 3 перейдет в единичное состояние. На выходе триггера 3 установится уровень логической единицы, который поступит на третий выход устройства, сигнализируя о начале очередного цикла преобразования.

Положительный перепад напряжения с выхода триггера 3 поступит также на второй вход АЦП считывания 8, благодаря чему на его выходе зафиксируется код, соответствующий модулю входного напряжения, поданному на первый вход АЦП считывания 8. Это соответствует первому этапу преобразования: с помощью АЦП считывания 8 малой разрядности осуществляется "грубое" преобразование и находятся два старших разряда выходного кода, в данном случае они равны 01 (коду 01 0000 соответствует напряжение 16⋅0,15625=2,5 В, коду 01 1111 соответствует напряжение 31⋅0,15625=4,84 В, а по принятому выше предположению модуль входного напряжения составляет 3,2 В (|UBX|=3,2B)).

При этом на вход ЦАП 2 будет подан код числа 24 (01 1000): два разряда с выхода АЦП считывания 8-01 и четыре разряда с выхода регистра 6-1000. На выходе ЦАП 2 установится напряжение UЦАП=24⋅0,15625=3,75 В. Это напряжение поступит на второй вход схемы сравнения 1, на первый вход которой подан модуль входного преобразуемого напряжения (для примера принято |UBХ|=3,2 В). Поскольку |UВХ|UЦАП, на выходе схемы сравнения 1 появится уровень, соответствующий логическому нулю.

Единичный сигнал с выхода триггера 3 поступит также на управляющий вход генератора импульсов 4, который начнет генерировать прямоугольные импульсы. Импульсы с выхода генератора импульсов 4 начнут поступать на первый вход счетчика 5. Содержимое счетчика 5 первоначально должно быть равным 1 (при включении устройства, это обеспечивается специальными схемами предварительной установки, на фигуре 1 не показанными). Поскольку содержимое счетчика 5 отлично от нуля, сигнал логической единицы с его выхода поступает на его второй вход, т.е. для счетчика 5 установлен режим вычитания. После поступления одного импульса на первый вход счетчика 5 его содержимое станет равным нулю. В течение этого времени переходные процессы в схеме сравнения 1 закончатся. Нулевой уровень с выхода счетчика 5 поступит на третий (стробирующий) вход схемы сравнения 1, фиксируя значение сигнала на его выходе с тем, чтобы исключить его изменение при перезаписи информации из ПЗУ 7 в регистр 6 и счетчик 5.

При этом на адресных входах ПЗУ 7 будет сформирован код 40 (01 0 1000). Соответственно, на первых выходах ПЗУ 7 появится код числа 6 (0110), на вторых выходах - код числа 3 (0011) и на третьем выходе - нулевой уровень (9-я строка в таблице). Поскольку при обнулении счетчика 5 он переходит в режим записи, с приходом очередного импульса с первого выхода генератора импульсов 4 на первый вход счетчика в него будет записан код числа 3 (0011) со вторых выходов ПЗУ 7. Содержимое счетчика 5 станет отличным от нуля и на его выходе сформируется положительный перепад напряжения, по которому в регистр 6 будет записан код числа 6 с первых выходов ПЗУ 7. На фиг. 4 это соответствует переходу от кода 24 к коду 22 (01 0110) при |UВХ|<UЦАП.

На входе ЦАП 2 будет код числа 22 (01 0110), соответственно, на выходе ЦАП установится напряжение UЦАП=22⋅0,15625=3,4375 В, и, поскольку |UВХ|<UЦАП, на выходе схемы сравнения 1 установится уровень логического нуля. На адресных входах ПЗУ 7 установится код числа 38 (01 0 0110), и на первых выходах ПЗУ 7 появится код 4 (0100), а на вторых выходах - код 3 (0011) (7-я строка в таблице). После обнуления счетчика 5 код 4 (0100) будет записан в регистр 6, а содержимое счетчика 5 станет равным 3 (0011).

На входе ЦАП 2 будет код числа 20 (01 0100), соответственно, на выходе ЦАП установится напряжение UЦАП=20⋅0,15625=3,125 В. Поскольку в данном случае |UВХ|UЦАП, на выходе схемы сравнения 1 установится уровень логической единицы. На адресных входах ПЗУ 7 установится код числа 52 (01 1 0100) и на первых выходах ПЗУ 7 появится код 5 (0101), а на вторых выходах - код 2 (0010) (21-я строка в таблице). После обнуления счетчика 5 код 5 (0101) будет записан в регистр 6, а содержимое счетчика 5 станет равным 1 (0001).

Теперь на входе ЦАП 2 будет код числа 21 (01 0101), соответственно, на выходе ЦАП 2 при этом появится напряжение UЦАП=21⋅0,15625=3,28125 В. Поскольку в данном случае |UВХ|<UЦАП, на выходе схемы сравнения 1 установится уровень логического нуля. На адресных входах ПЗУ 7 установится код числа 37 (01 00101), и на первых выходах ПЗУ 7 появится код 4 (0100), а на вторых выходах код 1 (0001) (6-я строка в таблице). После обнуления счетчика 5 код 4 (0100) будет записан в регистр 6, а содержимое счетчика 5 станет равным 1 (0001).

При этом на третьем выходе ПЗУ 3 установится уровень логической единицы (6-я строка в таблице, столбец №5 "Признак окончания"), который поступит на четвертый вход триггера 3, на третьем входе которого будет уровень логического нуля с выхода счетчика 5. С приходом импульса с выхода генератора импульсов 4 триггер 3 перейдет в нулевое состояние. На выходе триггера 3 установится нулевой логический уровень, который поступит на третий выход устройства, сигнализируя об окончании очередного цикла аналого-цифрового преобразования. На первых выходах устройства установится окончательный выходной код числа 20 (01 0100). Нулевой уровень с выхода триггера 3 также приостановит работу генератора импульсов 4. При этом содержимое счетчика 5 будет равно 1 (0001), т.е. устройство будет подготовлено к следующему циклу аналого-цифрового преобразования.

Таким образом, в предложенном АЦП на первом этапе производится "грубое" преобразование с помощью АЦП считывания 8 (имеющего высокое быстродействие), что позволяет уменьшить число анализируемых кодов на втором этапе подбора кода. При использовании двухразрядного АЦП считывания 8 количество анализируемых кодов на втором этапе уменьшается в 22=4 раза. Соответственно, не менее чем в 4 раза уменьшается время преобразования. Кроме того, в предложенном устройстве учитывается время установления напряжения на выходе ЦАП 2. Предложенное устройство позволяет также для каждой области кодов (выделяемых на первом этапе) задавать свою процедуру подбора кодов, эта область в ПЗУ 7 адресуется кодом с выхода АЦП считывания 8, поступающим на старшие адресные разряды ПЗУ 7.

Устройство АЦП, служащее прототипом, ориентировано на работу с однополярными сигналами (сигналами положительной полярности). Благодаря введению в состав устройства БОЗ и ИОН 9, предлагаемое устройство АЦП может работать как с однополярными сигналами (причем как положительной, так и отрицательной полярности), так и двуполярными сигналами, то есть имеет место расширение функциональных возможностей предлагаемого устройства АЦП относительно прототипа.

Введение в состав устройства БОЗ и ИОН 9, при аналого-цифровой обработке двуполярных сигналов, в отличие от типовых схем включения для преобразования двуполярного входного сигнала в диапазон одной полярности ([6]. Звонарев Е. Драйвера для АЦП на основе операционного усилителя компании Texas Instruments // Компоненты и технологии. 2007. №11, рис. 3, 4. [Электронный ресурс] http://kit-e.ru/articles/usil/2007_11_33.php (дата обращения: 10.02.2017)) приводит:

а) к увеличению разрядности АЦП на один разряд (старший разряд кода, несущий информацию о полярности входного сигнала, формирует БОЗ и ИОН 9);

б) к возможности пересчета динамического диапазона входных сигналов и шага квантования (увеличению их в два раза), что способствует существенному увеличению точности аналого-цифрового преобразования входных сигналов в связи с повышением помехоустойчивости АЦП.

Другими словами, для обеспечения одинаковых требований к точности преобразования в прототипе и предлагаемом устройстве АЦП вместо N-разрядного ЦАП 2 и (3+N) разрядного ПЗУ 7, используемых в прототипе, в предлагаемом устройстве требуются (N-1)-разрядный ЦАП 2 и (2+N) разрядное ПЗУ 7, в силу чего предлагаемое устройство АЦП будет проще, при одновременном повышении быстродействия, в силу снижения задержки импульсов, обусловленной упрощением процедуры подбора.

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2002 |

|

RU2204884C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2001 |

|

RU2187884C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2001 |

|

RU2205500C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ЛОГИЧЕСКОГО РАЗВЕРТЫВАНИЯ | 2000 |

|

RU2178948C2 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2001 |

|

RU2187885C1 |

| МНОГОКАНАЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2001 |

|

RU2183382C1 |

| Аналого-цифровой преобразователь | 2017 |

|

RU2646356C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2000 |

|

RU2171543C1 |

| УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 1991 |

|

RU2013863C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2010 |

|

RU2441317C1 |

Изобретение относится к измерительной технике, в частности к аналого-цифровым преобразователям, и может быть использовано в цифровых системах для измерения и контроля аналоговых величин. Техническим результатом является обеспечение возможности аналого-цифрового преобразования не только однополярных положительных, но также однополярных отрицательных и двуполярных сигналов, повышение точности и быстродействия и снижение сложности схемы. Устройство содержит схему сравнения, цифро-аналоговый преобразователь, триггер, генератор импульсов, счетчик, регистр, постоянное запоминающее устройство, АЦП считывания, блок определения знака и инвертирования отрицательных напряжений, в состав которого входят аналоговый инвертор, компаратор, два аналоговых ключа. 4 ил., 1 табл.

Аналого-цифровой преобразователь, содержащий: схему сравнения; цифро-аналоговый преобразователь (ЦАП); триггер; генератор импульсов; счетчик; регистр; постоянное запоминающее устройство (ПЗУ); АЦП считывания, первый вход которого соединен с первым входом схемы сравнения, а ко второму входу схемы сравнения подключен выход ЦАП, вторые входы ЦАП соединены с третьими входами ПЗУ и с выходами регистра, первый вход которого соединен со вторым входом устройства и первым входом триггера, выход которого подключен ко второму входу АЦП считывания и входу генератора импульсов, выход которого соединен со вторым входом триггера и первым входом счетчика, выход которого соединен со своим вторым входом и третьими входами триггера и схемы сравнения, а также со вторым входом регистра; выходы АЦП считывания подключены к первым входам ЦАП и ПЗУ, второй вход ПЗУ соединен с выходом схемы сравнения, первые выходы ПЗУ соединены с третьими входами регистра, вторые выходы - с третьими входами счетчика, а третий выход - с четвертым входом триггера, отличающийся тем, что в устройство введен блок определения знака и инвертирования отрицательных напряжений (БОЗ и ИОН), причем вход БОЗ и ИОН служит входом устройства, первый выход БОЗ и ИОН служит первым выходом устройства, второй выход БОЗ и ИОН подключен к первым входам схемы сравнения и АЦП считывания; первые и вторые входы ЦАП являются вторыми выходами устройства, а выход триггера является третьим выходом устройства; БОЗ и ИОН содержит аналоговый инвертор, компаратор, первый (нормально замкнутый) аналоговый ключ, второй (нормально разомкнутый) аналоговый ключ; вход БОЗ и ИОН подключен одновременно к входу аналогового инвертора, первому (неинвертирующему) входу компаратора, сигнальному входу второго (нормально разомкнутого) аналогового ключа; второй (инвертирующий) вход компаратора «заземлен»; выход компаратора одновременно подключен к первому выходу БОЗ и ИОН и входам управления аналоговых ключей, выходы которых соединены со вторым выходом БОЗ и ИОН; выход аналогового инвертора подключен к сигнальному входу первого (нормально замкнутого) аналогового ключа.

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2002 |

|

RU2204884C1 |

| СПОСОБ ФОРМИРОВАНИЯ АБСОЛЮТНОГО ЗНАЧЕНИЯ СИГНАЛА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2007 |

|

RU2356163C1 |

| Колосоуборка | 1923 |

|

SU2009A1 |

| Приспособление для суммирования отрезков прямых линий | 1923 |

|

SU2010A1 |

| Способ и приспособление для нагревания хлебопекарных камер | 1923 |

|

SU2003A1 |

Авторы

Даты

2018-06-07—Публикация

2017-05-02—Подача